DS07-16310-1E

FUJITSU SEMICONDUCTOR

DATA SHEET

32-Bit Microcontroller

CMOS

FR30 Series

MB91F127/F128

s

DESCRIPTION

This model, designed on the basis of 32-bit RISC CPU (FR30 series), is a standard single-chip micro controller

with built-in I/O resources and bus control functions. The functions are suitable for built-in control that requires

high-speed CPU processing.

MB91F127 includes 256 Kbytes built-in flash memory and 14 Kbytes built-in RAM. MB91F128 includes 510 Kbytes

built-in flash memory and 14 Kbytes built-in RAM.

The specifications of the devices are best suited for applications requiring high-level CPU processing capabilities,

such as navigation system, high-performance FAX, and printer controller.

s

FEATURES

FR-CPU

· 32-bit RISC (FR30), load/store architecture, 5-step pipeline

· Operating frequency : Internal 25 MHz

· General register : 32bit x 16 registers

· 16-bit fixed-length instructions (primitives), 1 instruction/1 cycle

· Instructions of memory-to-memory transfer, bit processing, and barrel shift : Instructions suitable for built-in

control

(Continued)

s

PACKAGE

100 pin, Plastic LQFP

(FPT-100P-M05)

MB91F127/F128

2

· Function entry/exit instructions, multi load/store instruction for register data : High-level language compatible

instructions

· Register interlock functions : Simple description of assembler language

· Branch instructions with delay slot : Reduced overhead on branching process

· Built-in multiplier/ Supporting at instruction level

Signed 32-bit multiplying : 5 cycles

Signed 16-bit multiplying : 3 cycles

· Interrupt (saving PC and PS) : 6 cycles, 16 priority levels

Bus interface

· Maximum of 25 MHz internal operation rate

· 25-bit address bus (32 MB space)

· 16-bit address output, 8/16-bit data input/output

· Basic bus cycle : 2-clock cycle

· Chip selection outputs specifiable in a minimum of 64 Kbytes steps : 6 outputs

· Automatic wait cycle : Specifiable flexibly from 0 cycle to 7 cycles for each area

· Supporting time-division input/output interface for address/data (for area 1 only)

· Unassigned data/address terminals are available as input/output ports

· Supporting little endian mode (selecting one area from area 1 to area 5)

DMAC (DMA controller)

· 8 channels

· Transfer factor : Interrupt request of built-in resources

· Transfer sequence : Step transfer/Block transfer/Burst transfer/Consecutive transfer

· Transfer data length : Selectable among 8 bits, 16 bits, and 32 bits

· Pausing is allowed by interrupt request

UART

· 3 channels

· Full-duplex double buffer

· Data length : 7 to 9 bits (no parity), 6 to 8 bits (with parity)

· Asynchronous (start-stop synchronization) or CLK synchronous communication is selectable

· Multi processor mode

· Built-in 16-bit timer (U-Timer) used as a baud-rate generator : Generates an arbitrary baud rate

· External clock is available as a transfer clock

· Error detection : parity, frame, and overrun

A/D converter (sequential transducer)

· 8/10-bit resolution, 8 channels

· Sequential comparison and transducer : At 25 MHz, 5.2

µ

s

· Built-in sample and hold circuit

· Conversion mode : Selectable among single conversion, scan conversion, and repeat conversion

· Activation : Selectable among software, external trigger, and built-in timer

Reload timer

· 16-bit timer : 3 channels

· Internal clock : 2-clock cycle resolution, selectable among 2/8/32 dividing and external clock

(Continued)

MB91F127/F128

3

(Continued)

Other interval timers

· 16-bit timer : 3 channels (U-Timer)

· PPG timer : 4 channels

· 16-bit OCU : 4 channels, ICU : 4 channels, Free-run timer : 1 channel

· Watchdog timer: 1 channel

Flash memory 510 KB

· 510 KB FLASH ROM: Read/Write/Erase is allowed with a same power

Built- in RAM 14 KB

· D-bus RAM 12 KB, C-bus RAM 2 KB

Bit search module

· Position of a first bit that changes between "1" and "0" is searched in one cycle, within an MSB of one word.

Interrupt controller

· External interrupt input : Normal interrupt

×

6 (INT0 to INT5)

· Internal interrupt factors : UART, DMAC, A/D, Reload timer, UTIMER, delay interrupt, PPG, ICU, and OCU

· Priority levels are programmable (16 levels)

Reset factors

· Power-on reset/watchdog timer/software reset/external reset

Low power consumption mode

· Sleep/stop mode

Clock control

· Built-in PLL circuit, selectable among 1-multiplication, and 2-multiplication

· Gearing function : Operation clock frequencies are freely and independently specifiable for CPU and

peripherals.

Gear clocks are selectable among 1/1, 1/2, 1/4, and 1/8 (or among 1/2, 1/4, 1/8, and 1/16).

Upper limit of peripheral operations is 25 MHz.

Others

· Package : LQFP-100

· CMOS technology : 0.35

µ

m

· Power supply voltage : 3.3 V

±

0.3 V

s

SERIES CONFIGURATION

Model name

MB91F127

MB91F128

MB91FV129

Outline

Quantity production

Quantity production

Evaluation product

FLASH memory

256 KB

510 KB

510 KB

D-bus RAM

12 KB

12 KB

16 KB

C-bus RAM

2 KB

2 KB

2 KB

MB91F127/F128

4

s

PIN ASSIGNMENT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

PG5/OC1

PG6/OC2

PG7/OC3

VCC

PA6/CLK

PA5/CS5/SC1

PA4/CS4/SI1

PA3/CS3/SO1

PA2/CS2

PA1/CS1

PA0/CS0

P86/ALE

HST

RST

VSS

MD0

MD1

MD2

P80/RDY

P81/BGRNT/IN0

P82/BRQ/IN1

P83/RD

P84/WR0

P85/WR1

P20/D16

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

PJ3/AN3

PJ2/AN2

PJ1/AN1

PJ0/AN0

AVSS/AVRL

AVRH

AVCC

P70/A24/FRCK/TCI2

P67/A23/IN3

P66/A22/IN2

VSS

P65/A21

P64/A20

P63/A19

P62/A18

P61/A17

P60/A16

P57/A15

P56/A14

P55/A13

P54/A12

P53/A11

P52/A10

P51/A09

P50/A08

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

PG4/OC0

PG3/OCPA3

PG2/OCPA2

PG1/OCPA1

PG0/OCPA0

PE0/INT0

PE1/INT1

VCC

X0

X1

VSS

PE2/INT2

PE3/INT3

PE4/INT4/TCI1

PE5/INT5/SC0

PE6/SI0

PE7/SO0

PF3/SC2/ATG

PF2/SO2

PF1/SI2

PF0/TCI0

PJ7/AN7

PJ6/AN6

PJ5/AN5

PJ4/AN4

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

P30/D24

P31/D25

P32/D26

P33/D27

P34/D28

P35/D29

P36/D30

VSS

P37/D31

P40/A00

VCC

P41/A01

P42/A02

P43/A03

P44/A04

P45/A05

P46/A06

P47/A07

(TOP VIEW)

(FPT-100P-M05)

MB91F127/F128

5

s

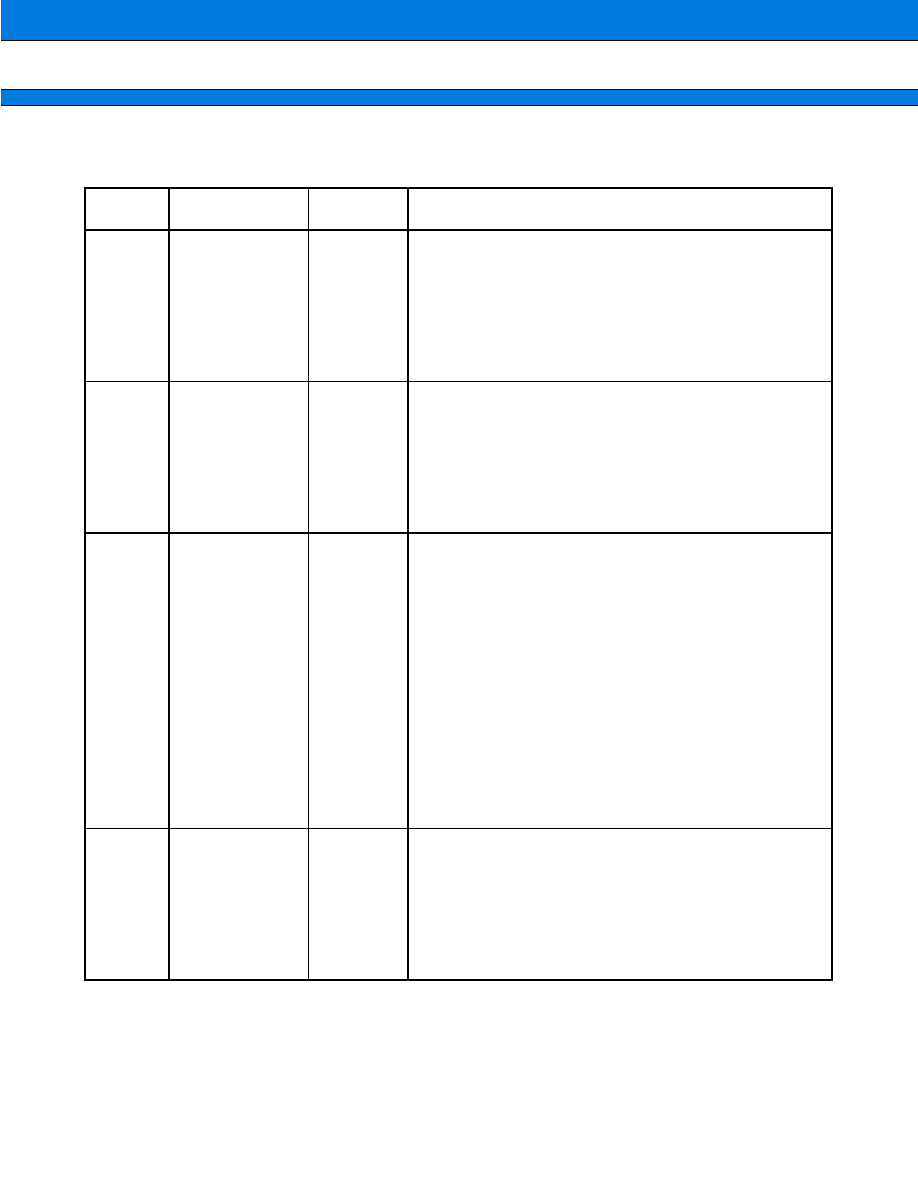

PIN DESCRIPTION

Note that the numbers in the table are not pin numbers on a package.

(Continued)

No.

Pin name

Input/output

circuit type

Description

1

2

3

4

5

6

7

8

D16/P20

D17/P21

D18/P22

D19/P23

D20/P24

D21/P25

D22/P26

D23/P27

D

Bit 16 through bit 23 of external data bus.

The terminals are available as general I/O ports (P20 through

P27) when external bus width is specified at 8 bits or in single-

chip mode.

9

10

11

12

13

14

15

16

D24/P30

D25/P31

D26/P32

D27/P33

D28/P34

D29/P35

D30/P36

D31/P37

D

Bit 24 through bit 31 of external data bus.

The terminals are available as general I/O ports (P30 through

P37) when the terminals are not used.

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

A00/P40

A01/P41

A02/P42

A03/P43

A04/P44

A05/P45

A06/P46

A07/P47

A08/P50

A09/P51

A10/P52

A11/P53

A12/P54

A13/P55

A14/P56

A15/P57

D

Bit 00 through bit 15 of external address bus.

The terminals are available as general I/O ports (P40 through

P47 and P50 through P57) when the terminals are not used as

address buses.

33

34

35

36

37

38

39

40

A16/P60

A17/P61

A18/P62

A19/P63

A20/P64

A21/P65

A22/P66/IN2

A23/P67/IN3

D

Bit 16 through bit 23 of external address bus.

The terminals are available as general I/O ports (P60 through

P67) when the terminals are not used as address busses.

[IN2,IN3]: Input terminals of input capture.

This function is active when input capture is operating.

MB91F127/F128

6

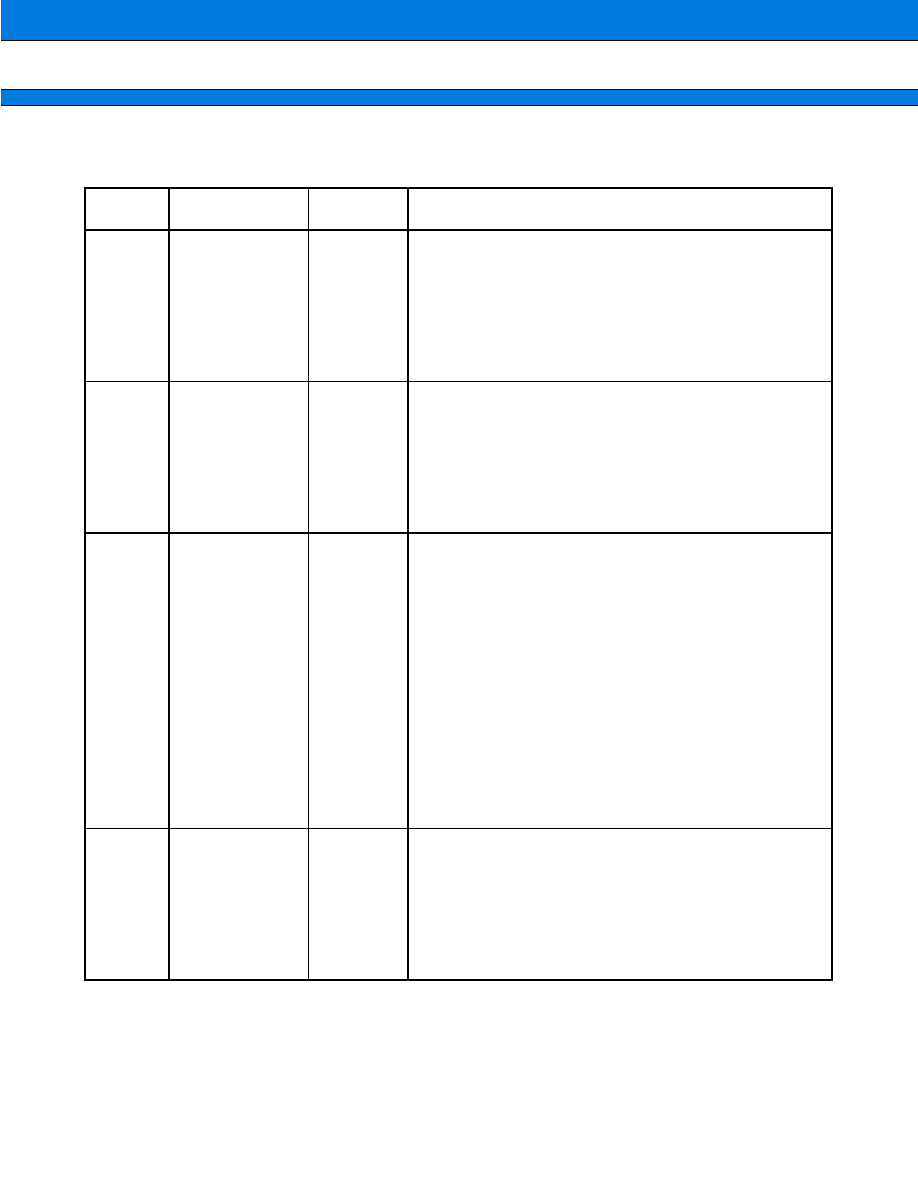

(Continued)

No.

Pin name

Input/output

circuit type

Description

41

A24/P70/FRCK/

TCI2

D

Bit 24 of external address bus.

[P70] A24, FRCK and TCI2 are available as general input ports

when they are not used.

[FRCK] External clock input of free-run timer. This function is

active when external clock input of free-run timer is used.

[TCI2] External clock input of timer 2. This function is active

when external clock input of timer 2 is used.

42

RDY/P80

D

External ready input. Enter "0" when bus cycle under execution

does not complete. This terminal is available as general input/

output port when it is not used.

43

BGRNT/P81/IN0

D

External bus open receive output. This terminal outputs "L"

when an external bus is released. This terminal is available as

general input/output port when it is not used.

[IN0] Input capture input.

This function is active when input capture is under input opera-

tion.

44

BRQ/P82/IN1

D

External bus open request input. Enter "1" when releasing exter-

nal bus. This terminal is available as general input/output port

when it is not used.

[IN1] Input capture input.

This function is active when input capture is under input opera-

tion.

45

RD/P83

D

External bus read strobe.

This terminal is available as general input/output port when it is

not used.

46

WR0/P84

D

External bus write strobe.Control signals and data bus byte po-

sitions are related as the following :

47

WR1/P85

D

48

49

50

CS0/PA0

CS1/PA1

CS2/PA2

D

Chip select 0 output (Low active)

Chip select 1 output (Low active)

Chip select 2 output (Low active)

[PA0,1,or 2] Available as general input/output ports when CS0,

CS1 and CS2 are not used.

Note : WR1 is set to Hi-z during resetting.

For using with 16-bit bus width, use an external pull-up

resistor.

[P84 or P85] Available as general input/output ports when WR0

and WR1 are not used.

16-bit bus

width

8-bit bus width

Single chip

mode

D31 to D24

WR0

WR0

(port allowed)

D23 to D16

WR1

(port allowed)

(port allowed)

MB91F127/F128

7

(Continued)

No.

Pin name

Input/output

circuit type

Description

51

52

53

CS3/PA3/SO1

CS4/PA4/SI1

CS5/PA5/SC1

D

Chip select 3, 4, 5 output (Low active).

[PA3,4,5] Available as general input/output ports when channel

1 of chip select UART is not used.

[SO1,SI1,SC1] Data output, data input, and clock terminals of

UART1. Active when UART1 operation is allowed.

54

CLK/PA6

D

System clock output. Outputs a same clock as the same fre-

quency of external bus operation.

[PA6] Available as general input/output ports it is not used.

55

56

57

58

59

60

61

62

OCPA0/PG0

OCPA1/PG1

OCPA2/PG2

OCPA3/PG3

OC0/PG4

OC1/PG5

OC2/PG6

OC3/PG7

D

[OCPA0 to 3] PPG timer outputs. The function is active when

PPG timer output is allowed.

[OC0 to 3] Output comparison output. The function is active

when output comparison output is allowed. [PB0-7] Available as

general input/output ports it is not used.

63

64

65

MD0

MD1

MD2

B

Mode terminals 0 through 2. The terminals specify basic opera-

tion mode of MCU.

Use the terminals by connecting them directly to VCC or VSS.

66

67

X0

X1

A

Clock (oscillation) input.

Clock (oscillation) output.

68

RST

C

External reset input.

69

HST

C

Hardware standby input.

70

P86/ALE

D

[ALE] Address latch signal output. The function is active when

ALE output of EPCR is allowed.

71

72

INT0/PE0

INT1/PE1

INT2/PE2

INT3/PE3

D

[INT0,1,2,3] External interrupt request inputs. The input is used

whenever necessary if external interrupt is allowed. Output of

other functions must be suspended if not on purpose.

[PE0,1,2,3] General input/output port

75

76

INT4/PE4/TCI1

INT5/PE5/SC0

D

[INT4,5] External interrupt request inputs.The input is used

whenever necessary if concerned external interrupt is allowed.

Output of other functions must be suspended if not on purpose.

[TCI1] External clock input of timer 1. [SC0] Clock input of

UART0.

[PE4,5] General input/output port

77

SI0/PE6

D

[SI0] Data input of UART0.This function is active when data in-

put of UART0 is allowed.

[PE6]General input/output port

78

SO0/PE7

D

[SO0] Data output of UART0.This function is active when data

output of UART0 is allowed.

[PE7] General input/output port

MB91F127/F128

8

(Continued)

Note : Most of the above terminals multiplex inputs and outputs of I/O ports and resources, as indicated as "XXXX/

PXX". If the outputs of ports and resources conflict with each other on the terminals, resources take prefer-

ences.

No.

Pin name

Input/output

circuit type

Description

79

PF0/TCI0

D

[TCI0] External clock input of timer 0.

[PF0] General input/output port

80

SI2/PF1

D

[SI2] Data input of UART2.This function is active when data in-

put of UART2 is allowed.

[PF1] General input/output port

81

SO2/PF2

D

[SO2] Data output of UART2.This function is active when data

output of UART2 is allowed.

[PF2] General input/output port. This function is active when

data output of UART2 is disallowed.

82

SC2/PF3/ATG

D

[SC2] Clock input of UART2

[ATG]External trigger input of A/D converter The input is used

whenever necessary if a function concerned is selected.

Output of other functions must be suspended if not on purpose.

[PF3] General input/output port

83 to 90

AN0/PJ0

AN1/PJ1

AN2/PJ2

AN3/PJ3

AN4/PJ4

AN5/PJ5

AN6/PJ6

AN7/PJ7

E

[AN0 to AN7] Analog input of A/D converter.

This function is active when analog input is specified in AIC reg-

ister.

[PJ0 through PJ7] General input/output ports

91

AVCC

VCC power supply for A/D converter

92

AVRH

Reference voltage of A/D converter (high potential side). Be

sure to turn on or off this terminal with a potential higher than

AVRH applied to VCC.

93

AVSS/AVRL

A/D converter VSS power source and reference voltage (low po-

tential side).

94 to 96

VCC

Power sources of digital circuits. Be sure to connect power

source to all terminals when the device is used.

97 to 100

VSS

Ground level of digital circuits.

MB91F127/F128

9

s

INPUT/OUTPUT CIRCUIT TYPE

Type

Circuit

Remarks

A

· For 25 MHz system

· Oscillation feedback register :

Approx. 1M

· Standby control is available.

B

· CMOS level input

· High-voltage control is avail-

able for FLASH test.

C

· CMOS level hysteresis input

· Standby control is not avail-

able.

D

· CMOS level output

· CMOS level hysteresis input

· Standby control is available

E

· Standby control is available

· CMOS level output

· CMOS level hysteresis input

· Analog input

X1

X0

Clock input

STANDBY

Diffused resistor

Control

signal

Mode input

P-channel transistor

N-channel transistor

CMOS

Digital input

Diffused

resistor

Digital output

Digital output

Digital input

Diffused

resistor

STANDBY

Digital output

Digital output

Digital input

Diffused

resistor

Analog input

STANDBY

MB91F127/F128

10

s

HANDLING DEVICES

1.

Preventing latch up

On a CMOS IC, latch up may occur when a voltage higher than VCC or a voltage lower than VSS is applied to

input terminal or output terminal, or when a voltage exceeding rated level is applied across VCC and VSS. Latch

up causes drastic increase of power source current, which may result in destruction of the element by heat.

Take extra care not to exceed maximum rating in use. Also, take extra care so that analog terminal does not

exceed digital power source.

2.

Treatment of unused input terminals

Leaving unused terminals open may cause malfunction. Apply pull-up or pull-down treatment on unused

terminals.

3.

External reset input

Complete resetting of internal system requires inputting "L" level signal to RST terminal for a minimum of

5 machine cycles.

4.

Notes on using external clock

When using an external clock, supply a clock signal to X0 terminal and supply its antiphase clock to X1 terminal

simultaneously. In this case, do not use STOP mode (oscillation stop mode). (Because X1 terminal halts with

"H" output under STOP status.)

Under a 12.5 MHz frequency, the device operates with a clock supplied to X0 terminal only.

Figures show examples of using an external clock.

Example of using external clock (normal)

Note : STOP mode (oscillation stop mode) is not available.

Example of using external clock (allowed under operation at 12.5 MHz or lower frequency)

X0

X1

X0

X1

OPEN

MB91F127/F128

11

5.

Connecting power supply terminals (VCC, VSS)

If two or more VCC, VSS terminals are used, the terminals to be placed under the same potentials are connected

with each other internally for preventing malfunctions such as latch up. However, for reducing unwanted radiation,

preventing malfunctions of strobe signals and observing total power and current ratings, be sure to connect all

of these terminals to power supply and ground externally.

Connecting power supply to VCC - VSS in impedance as low as possible is desirable.

6.

Crystal oscillator circuit

Noises around X0 and X1 terminals causes malfunction of the device. Design printed wiring so that X0, X1,

and crystal oscillator (or ceramic oscillator), and bypass capacitor to the ground are aligned as close as possible

one another. Also the wiring of those elements should not cross with other wiring if possible. Printed wiring

with ground wires around X0 and X1 terminals ensures more stable operations. Such designing is strongly

recommended.

7.

Treating NC terminals

Be sure to leave NC terminals open.

8.

Mode terminals (MD0 through MD2)

Do not connect the mode terminals directly to VCC or VSS.

For preventing malfunctions caused by noises, make printed traces between the mode terminals and VCC or

VSS as short as possible, and connect the elements in lower impedance.

9.

Turning power on

Be sure to turn on the power of the device with RST terminal placed under "L" level. Ensure a period at a

minimum of 5 cycles of internal operation clock before placing the terminal under "H" level.

10. Terminal status upon turning on power

Status upon turning on the power is indefinite. Upon turning on the power, oscillation starts and the circuit is

initialized.

11. Oscillation input upon turning on power

Upon turning on the power, be sure to input a clock signal until oscillation stabilizing wait status is released.

12. Initializing power-on reset

The device includes some built-in registers that are initialized only with power-on reset operation. For initializing

the registers, perform power-on reset by turning on the power again.

13. Recovery from Sleep/Stop status

For recovering from Sleep/Stop status initiated by a program in C-Bus RAM, reset the device instead of

recovering by an interrupt process.

MB91F127/F128

12

s

BLOCK DIAGRAM

FR CPU

RAM (12 Kbytes)

DMA controller

(8 ch.)

Bit search module

Clock control unit

(Watchdog timer)

Interrupt control unit

UART (3 ch)

Reload timer (3 ch)

PPG

ICU, OCU

Free run timer

Port E, F, G, J

10-bit

A/D converter

(8 ch.)

Bus converter (32 bits - 16 bits)

Bus converter

(Harvard - Princeton)

Bus

controller

Port2, 3, 4, 5, 6,

7, 8, A

RAM (2 Kbytes)

Flash memory

MB91F127:256 KB

MB91F128:510 KB

D-b

us (32 bits)

R-b

us (16 bits)

C-b

us (32 bits)

I-b

us (16 bits)

X0

X1

RST

HST

INT0 to

INT5

AN0 to AN7

AVCC

AVSS/AVRL

AVRH

ATG

SI0 to SI2

SO0 to SO2

SC0 to SC2

TCI0 to TCI2

OC0 to OC3

IN0 to IN3

FRCK

OCPA0 to OCPA3

D16 to D31

A00 to A24

RD

WR0, WR1

RDY

CLK

BRQ

BGRNT

CS0 to CS5

ALE

6

8

3

3

3

3

4

4

4

16

25

2

6

Notes :

·

Terminals are described in functional groups (actual terminals are partially multiplexed).

·

For using REALOS, perform time management by external interrupt or built-in timer.

MB91F127/F128

13

s

CPU CORE MEMORY SPACE

· MB91F127

0000 0000

H

0000 0400

H

0000 0800

H

0000 1000

H

0000 4000

H

0001 0000

H

FFFF FFFF

H

0001 0000

H

0008 0000

H

0008 0800

H

0010 0000

H

FFFF FFFF

H

I/O

I/O

I/O

I/O

I/O

I/O

FLASH ROM

256 KB

FLASH ROM

256 KB

000C 0000

H

External ROM

External bus mode

Internal ROM

External bus mode

Single-chip mode

Access inhibit

Internal RAM

12 KB

Access inhibit

External area

Access inhibit

Internal RAM

12 KB

Access inhibit

Access inhibit

Internal RAM

12 KB

Access inhibit

External area

Internal RAM

2 KB

Internal RAM

2 KB

Access inhibit

Direct

addressing

areas

I/O map

External area

Access inhibit

Note : External area is not accessible in single-chip mode. When accessing to external areas, select the internal

ROM external bus mode in mode register.

Direct addressing areas

The areas described below are used for I/O processes. The areas, referred to as "direct addressing areas,"

allow specifying an operand address directly by an instruction. The direct addressing areas varies as the

following, depending on size of the data to be accessed.

· Byte-data access : 0 to 0FF

H

· Half-word data access : 0 to 1FF

H

· Word-data access : 0 to 3FF

H

Access inhibit

Access inhibit

MB91F127/F128

14

· MB91F128

0000 0000

H

0000 0400

H

0000 0800

H

0000 1000

H

0000 4000

H

0001 0000

H

FFFF FFFF

H

0001 0000

H

0008 0000

H

0008 0800

H

0010 0000

H

FFFF FFFF

H

I/O

I/O

I/O

I/O

I/O

I/O

FLASH ROM

510 KB

FLASH ROM

510 KB

External ROM

External bus mode

Internal ROM

External bus mode

Single-chip mode

Access inhibit

Internal RAM

12 KB

Access inhibit

External area

Access inhibit

Internal RAM

12 KB

Access inhibit

Access inhibit

Internal RAM

12 KB

Access inhibit

External area

Internal RAM

2 KB

Internal RAM

2 KB

Access inhibit

Direct

addressing

areas

I/O map

External area

Access inhibit

Note : External area is not accessible in single-chip mode. When accessing to external areas, select the internal

ROM external bus mode in mode register.

Direct addressing areas

The areas described below are used for I/O processes. The areas, referred to as "direct addressing areas,"

allow specifying an operand address directly by an instruction. The direct addressing areas varies as the

following, depending on size of the data to be accessed.

· Byte-data access : 0 to 0FF

H

· Half-word data access : 0 to 1FF

H

· Word-data access : 0 to 3FF

H

MB91F127/F128

15

s

LEGEND OF I/O MAP

Note : Register bit values indicate initial values as shown below :

"1" : Initial value"1"

"0" : Initial value"0"

"X" : Initial value "X"

"-"

: Register does not exist physically in this position.

address

Register

Internal resource

+

0

+

1

+

2

+

3

000000

H

PDR3 [R/W]

XXXXXXXX

PDR2 [R/W]

XXXXXXXX

- - - - - - - -

- - - - - - - -

Port Data Register

Read/write attribute

Initial register value after reset

Register name (the register listed in the first column is at address 4n, the register listed in

the second column is at address 4n

+

1, - - - )

Leftmost register address (the first column register is on the MSB side of data in word access mode)

MB91F127/F128

16

s

I/O MAP

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000000

H

PDR3 [R/W]

XXXXXXXX

PDR2 [R/W]

XXXXXXXX

Port data Register

000004

H

PDR7 [R/W]

- - - - - - - X

PDR6 [R/W]

XXXXXXXX

PDR5 [R/W]

XXXXXXXX

PDR4 [R/W]

XXXXXXXX

000008

H

PDRA [R/W]

XXXXXXXX

PDR8[R/W]

- - XXXXXX

00000C

H

000010

H

PDRE [R/W]

XXXXXXXX

PDRF [R/W]

XXXXXXXX

000014

H

PDRG [R/W]

XXXXXXXX

PDRJ [R/W]

XXXXXXXX

000018

H

Reserved

00001C

H

SSR [R/W]

00001- 00

SIDR [R/W]

XXXXXXXX

SCR [R/W]

00000100

SMR [R/W]

00 - - 0 - 00

UART0

000020

H

SSR [R/W]

00001- 00

SIDR [R/W]

XXXXXXXX

SCR [R/W]

00000100

SMR [R/W]

00 - - 0 - 00

UART1

000024

H

SSR [R/W]

00001- 00

SIDR [R/W]

XXXXXXXX

SCR [R/W]

00000100

SMR [R/W]

00 - - 0 - 00

UART2

000028

H

TMRLR [W]

XXXXXXXX XXXXXXXX

TMR [W]

XXXXXXXX XXXXXXXX

Reload Timer 0

00002C

H

TMCSR [R/W]

- - - - 0000 00000000

000030

H

TMRLR [W]

XXXXXXXX XXXXXXXX

TMR [W]

XXXXXXXX XXXXXXXX

Reload Timer 1

000034

H

TMCSR [R/W]

- - - - 0000 00000000

000038

H

Reserved

00003C

H

TMRLR [W]

XXXXXXXX XXXXXXXX

TMR [W]

XXXXXXXX XXXXXXXX

Reload Timer 2

000040

H

TMCSR [R/W]

- - - - 0000 00000000

000044

H

IPCP1[R]

XXXXXXXX XXXXXXXX

IPCP0[R]

XXXXXXXX XXXXXXXX

16 bit ICU

000048

H

IPCP3[R]

XXXXXXXX XXXXXXXX

IPCP2[R]

XXXXXXXX XXXXXXXX

00004C

H

ICS23[R/W]

00000000

ICS01[R/W]

00000000

000050

H

ADCR [W]

00101-XX XXXXXXXX

ADCS [R/W]

000000000 00000000

A/D converter

(Serially com-

pared)

MB91F127/F128

17

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000054

H

OCCP1[R/W]

XXXXXXXX XXXXXXXX

OCCP0[R/W]

XXXXXXXX XXXXXXXX

16 bit OCU

000058

H

OCCP3[R/W]

XXXXXXXX XXXXXXXX

OCCP2[R/W]

XXXXXXXX XXXXXXXX

00005C

H

Reserved

000060

H

000064

H

OCS2, 3[R/W]

XXX00000 0000XX00

OCS0, 1[R/W]

XXX00000 0000XX00

16 bit OCU

000068

H

Reserved

00006C

H

TCDT [R/W]

00000000 00000000

TCCS [R/W]

0 - - - - - - - 00000000

Free run timer

000070

H

Reserved

000074

H

Reserved

000078

H

UTM/UTIMR [R/W]

00000000 00000000

UTIMC[R/W]

0 - - 00001

U-Timer0

00007C

H

UTM/UTIMR [R/W]

00000000 00000000

UTIMC[R/W]

0 - - 00001

U-Timer1

000080

H

UTM/UTIMR [R/W]

00000000 00000000

UTIMC[R/W]

0 - - 00001

U-Timer2

000084

H

Reserved

000088

H

00008C

H

Reserved

000090

H

000094

H

EIRR [R/W]

00000000

ENIR [R/W]

00000000

External interrupt/

NMI

000098

H

EHVR [R/W]

- - - - 0000

ELVR [R/W]

00000000

MB91F127/F128

18

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

00009C

H

Reserved

0000A0

H

0000A4

H

0000A8

H

0000AC

H

0000B0

H

0000B4

H

0000B8

H

0000BC

H

0000C0

H

0000C4

H

0000C8

H

0000CC

H

0000D0

H

DDRE [W]

00000000

DDRF [W]

00000000

Port direction

register

0000D4

H

AIC3[W]

11111111

A/D converter

0000D8

H

DDRG [W]

00000000

DDRJ [W]

00000000

Port direction reg-

ister

0000DC

H

GCN1 [R/W]

00110010 00010000

- - - - - - - -

GCN2[R/W]

00000000

PPG ctl

0000E0

H

PTMR0 [R]

11111111 11111111

PCSR0 [W]

XXXXXXXX XXXXXXXX

PPG0

0000E4

H

PDUT0 [W]

XXXXXXXX XXXXXXXX

PCNH0[R/W]

0000000 -

PCNL0[R/W]

00000000

0000E8

H

PTMR1 [R]

11111111 11111111

PCSR1 [W]

XXXXXXXX XXXXXXXX

PPG1

0000EC

H

PDUT1 [W]

XXXXXXXX XXXXXXXX

PCNH1[R/W]

0000000 -

PCNL1[R/W]

00000000

0000F0

H

PTMR2 [R]

11111111 11111111

PCSR2 [W]

XXXXXXXX XXXXXXXX

PPG2

0000F4

H

PDUT2 [W]

XXXXXXXX XXXXXXXX

PCNH2[R/W]

0000000 -

PCNL2[R/W]

00000000

0000F8

H

PTMR3 [R]

11111111 11111111

PCSR3 [W]

XXXXXXXX XXXXXXXX

PPG3

0000FC

H

PDUT3 [W]

XXXXXXXX XXXXXXXX

PCNH3[R/W]

0000000 -

PCNL3[R/W]

00000000

MB91F127/F128

19

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000100

H

to

0001FC

H

Reserved

000200

H

DPDP [R/W]

- - - - - - - - - - - - - - - - - - - - - - - - -0000000

DMAC

000204

H

DACSR [R/W]

00000000 00000000 00000000 00000000

000208

H

DATCR [R/W]

- - - - - - - - - - XX0000 - - XX0000 - - XX0000

00020C

H

000210

H

to

0002FC

H

Reserved

000300

H

to

0003EC

H

Reserved

0003F0

H

BSD0 [W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

Bit search module

0003F4

H

BSD1 [R/W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

0003F8

H

BSDC [W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

0003FC

H

BSRR [R/W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

MB91F127/F128

20

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000400

H

ICR00 [R/W]

- - -11111

ICR01[R/W]

- - -11111

ICR02[R/W]

- - -11111

ICR03[R/W]

- - -11111

Interrupt controller

000404

H

ICR04[R/W]

- - -11111

ICR05[R/W]

- - -11111

ICR06[R/W]

- - -11111

ICR07[R/W]

- - -11111

000408

H

ICR08 [R/W]

- - -11111

ICR09[R/W]

- - -11111

ICR10[R/W]

- - -11111

ICR11[R/W]

- - -11111

00040C

H

ICR12[R/W]

- - -11111

ICR13[R/W]

- - -11111

ICR14[R/W]

- - -11111

ICR15[R/W]

- - -11111

000410

H

ICR16[R/W]

- - -11111

ICR17[R/W]

- - -11111

ICR18[R/W]

- - -11111

ICR19[R/W]

- - -11111

000414

H

ICR20[R/W]

- - -11111

ICR21[R/W]

- - -11111

ICR22[R/W]

- - -11111

ICR23[R/W]

- - -11111

000418

H

ICR24 [R/W]

- - -11111

ICR25[R/W]

- - -11111

ICR26[R/W]

- - -11111

ICR27[R/W]

- - -11111

00041C

H

ICR28[R/W]

- - -11111

ICR29[R/W]

- - -11111

ICR30[R/W]

- - -11111

ICR31[R/W]

- - -11111

000420

H

ICR32[R/W]

- - -11111

ICR33[R/W]

- - -11111

ICR34[R/W]

- - -11111

ICR35[R/W]

- - -11111

000424

H

ICR36[R/W]

- - -11111

ICR37[R/W]

- - -11111

ICR38[R/W]

- - -11111

ICR39[R/W]

- - -11111

000428

H

ICR40[R/W]

- - -11111

ICR41[R/W]

- - -11111

ICR42[R/W]

- - -11111

ICR43[R/W]

- - -11111

00042C

H

ICR44[R/W]

- - -11111

ICR45[R/W]

- - -11111

ICR46[R/W]

- - -11111

ICR47[R/W]

- - -11111

000430

H

DICR [R/W]

- - - - - - - 0

HRCL [R/W]

- - -11111

Delay interrupt

000434

H

to

00047C

H

Reserved

000480

H

RSRR/WTCR

[R/W]

1XXXX - 00

STCR [R/W]

000111- -

PDDR [R/W]

- - - - 0000

CTBR [W]

XXXXXXXX

Clock controller

block

000484

H

GCR [R/W]

110011 - 1

WPR [W]

XXXXXXXX

000488

H

PTCR [R/W]

00 - - 0 - - -

PLL controller

block

00048C

H

to

0005FC

H

Reserved

MB91F127/F128

21

(Continued)

Note : Do not issue RMW instructions to a register with write-only bit.

Data in "Reserved" or "-" area is indefinite.

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000600

H

DDR3 [W]

00000000

DDR2 [W]

00000000

Data direction reg-

ister

000604

H

DDR7 [W]

- - - - - - - 0

DDR6 [W]

00000000

DDR5 [W]

00000000

DDR4 [W]

00000000

000608

H

DDRA [W]

-0000000

DDR8 [W]

- - 000000

00060C

H

ASR1 [W]

00000000 00000001

AMR1 [W]

00000000 00000000

External bus inter-

face

000610

H

ASR2 [W]

00000000 00000010

AMR2 [W]

00000000 00000000

000614

H

ASR3 [W]

00000000 00000011

AMR3 [W]

00000000 00000000

000618

H

ASR4 [W]

00000000 00000100

AMR4 [W]

00000000 00000000

00061C

H

ASR5 [W]

00000000 00000101

AMR5 [W]

00000000 00000000

000620

H

AMD0 [R/W]

- - - XX111

AMD1 [R/W]

0 - - 00000

AMD32[R/W]

00000000

AMD4 [R/W]

0 - - 00000

000624

H

AMD5[R/W]

0 - - 00000

DSCR [W]

00000000

RFCR [R/W]

--XXXXXX 00 - - - 000

000628

H

EPCR0 [W]

- - 1 - 1100 -1111111

EPCR1 [W]

- - - - - - - 1 11111111

00062C

H

DMCR4 [R/W]

00000000 0000000-

DMCR5 [R/W]

00000000 0000000-

000630

H

to

0007BC

H

Reserved

0007C0

H

FSTR [R/W]

000XXXX0

Flash memory

0007C4

H

to

0007F8

H

Reserved

0007FC

H

LER [W]

- - - - - 000

MODR [W]

XXXXXXXX

Little endian regis-

ter mode register

RMW instructions (RMW : Read modify write)

AND Rj, @Ri

OR Rj, @Ri

EOR Rj, @Ri

ANDH Rj, @Ri

ORH Rj, @Ri

EORH Rj, @Ri

ANDB Rj, @Ri

ORB Rj, @Ri

EORB Rj, @Ri

BANDL #u4, @Ri BORL #u4, @Ri

BEORL #u4, @Ri

BANDH #u4, @Ri BORH #u4, @Ri

BEORH #u4, @Ri

MB91F127/F128

22

s

INTERRUPT CAUSES, INTERRUPT VECTORS AND INTERRUPT CONTROL REGISTER ALLOCATIONS

(Continued)

Interrupt causes

Interrupt number

Interrupt level

TBR default

Address*

2

Decimal

Hexadecimal

Register*

1

Offset

Reset

0

00

3FC

H

000FFFFC

H

Reserved by system

1

01

3F8

H

000FFFF8

H

Reserved by system

2

02

3F4

H

000FFFF4

H

Reserved by system

3

03

3F0

H

000FFFF0

H

Reserved by system

4

04

3EC

H

000FFFEC

H

Reserved by system

5

05

3E8

H

000FFFE8

H

Reserved by system

6

06

3E4

H

000FFFE4

H

Reserved by system

7

07

3E0

H

000FFFE0

H

Reserved by system

8

08

3DC

H

000FFFDC

H

Reserved by system

9

09

3D8

H

000FFFD8

H

Reserved by system

10

0A

3D4

H

000FFFD4

H

Reserved by system

11

0B

3D0

H

000FFFD0

H

Reserved by system

12

0C

3CC

H

000FFFCC

H

Reserved by system

13

0D

3C8

H

000FFFC8

H

Undefined instruction exception

14

0E

3C4

H

000FFFC4

H

NMI request

15

0F

15 (F

H

)

fixed

3C0

H

000FFFC0

H

External interrupt 0

16

10

ICR00

3BC

H

000FFFBC

H

External interrupt 1

17

11

ICR01

3B8

H

000FFFB8

H

External interrupt 2

18

12

ICR02

3B4

H

000FFFB4

H

External interrupt 3

19

13

ICR03

3B0

H

000FFFB0

H

UART 0 reception complete

20

14

ICR04

3AC

H

000FFFAC

H

UART 1 reception complete

21

15

ICR05

3A8

H

000FFFA8

H

UART 2 reception complete

22

16

ICR06

3A4

H

000FFFA4

H

UART 0 transmission complete

23

17

ICR07

3A0

H

000FFFA0

H

UART 1 transmission complete

24

18

ICR08

39C

H

000FFF9C

H

UART 2 transmission complete

25

19

ICR09

398

H

000FFF98

H

MB91F127/F128

23

(Continued)

Interrupt causes

Interrupt number

Interrupt level

TBR default

Address*

2

Decimal

Hexadecimal

Register*

1

Offset

DMAC 0 (end, error)

26

1A

ICR10

394

H

000FFF94

H

DMAC 1 (end, erro)

27

1B

ICR11

390

H

000FFF90

H

DMAC 2 (end, erro)

28

1C

ICR12

38C

H

000FFF8C

H

DMAC 3 (end, erro)

29

1D

ICR13

388

H

000FFF88

H

DMAC 4 (end, erro)

30

1E

ICR14

384

H

000FFF84

H

DMAC 5 (end, erro)

31

1F

ICR15

380

H

000FFF80

H

DMAC 6 (end, erro)

32

20

ICR16

37C

H

000FFF7C

H

DMAC 7 (end, erro)

33

21

ICR17

378

H

000FFF78

H

A/D (sequential type)

34

22

ICR18

374

H

000FFF74

H

Reload timer 0

35

23

ICR19

370

H

000FFF70

H

Reload timer 1

36

24

ICR20

36C

H

000FFF6C

H

Reload timer 2

37

25

ICR21

368

H

000FFF68

H

External interrupt 4

38

26

ICR22

364

H

000FFF64

H

External interrupt 5

39

27

ICR23

360

H

000FFF60

H

Reserved by system

40

28

ICR24

35C

H

000FFF5C

H

Reserved by system

41

29

ICR25

358

H

000FFF58

H

U-TIMER 0

42

2A

ICR26

354

H

000FFF54

H

U-TIMER 1

43

2B

ICR27

350

H

000FFF50

H

U-TIMER 2

44

2C

ICR28

34C

H

000FFF4C

H

FLASH memory

45

2D

ICR29

348

H

000FFF48

H

Reserved by system

46

2E

ICR30

344

H

000FFF44

H

Reserved by system

47

2F

ICR31

340

H

000FFF40

H

PPG0

48

30

ICR32

33C

H

000FFF3C

H

PPG1

49

31

ICR33

338

H

000FFF38

H

PPG2

50

32

ICR34

334

H

000FFF34

H

PPG3

51

33

ICR35

330

H

000FFF30

H

ICU0 (capture)

52

34

ICR36

32C

H

000FFF2C

H

ICU1 (capture)

53

35

ICR37

328

H

000FFF28

H

ICU2 (capture)

54

36

ICR38

324

H

000FFF24

H

ICU3 (capture)

55

37

ICR39

320

H

000FFF20

H

MB91F127/F128

24

(Continued)

*1 : ICR specifies interrupt levels for interrupt requests, using the registers in interrupt controller.

ICR is provided for each interrupt request.

*2 : TBR is a register that indicates a head address of the vector table for EIT.

An address that is found by adding offset values defined by TBR and EIT cause, is a vector address.

*3 : If REALOS/FR is used, 0x40 and 0x41 interrupts are used for system code.

Information : An 1 Kbyte area starting with an address indicated by TBR is the vector area for EIT. Size of the area

for one vector is 4 byte. Relation between a vector number and a vector address is as follows:

Interrupt causes

Interrupt number

Interrupt level

TBR default

Address*

2

Decimal

Hexadecimal

Register*

1

Offset

OCU0 (match)

56

38

ICR40

31C

H

000FFF1C

H

OCU1 (match)

57

39

ICR41

318

H

000FFF18

H

OCU2 (match)

58

3A

ICR42

314

H

000FFF14

H

OCU3 (match)

59

3B

ICR43

310

H

000FFF10

H

Reserved by system

60

3C

ICR44

30C

H

000FFF0C

H

16 bit free-run timer

61

3D

ICR45

308

H

000FFF08

H

Reserved by system

62

3E

ICR46

304

H

000FFF04

H

Delay interrupt cause bit

63

3F

ICR47

300

H

000FFF00

H

Reserved by system

(used by REALOS)

*3

64

40

2FC

H

000FFEFC

H

Reserved by system

(used by REALOS)

*3

65

41

2F8

H

000FFEF8

H

Used by INT

66

to

255

42

to

FF

2F4

H

to

000

H

000FFEF4

H

to

000FFC00

H

vctadr

=

TBR

+

vctofs

=

TBR

+

( 3FC

H

-

4

×

vct)

Vctadr

Vector address, vctofs: Vector offset, vct: Vector number

MB91F127/F128

25

s

ELECTRICAL CHARACTERISTICS

1.

Absolute Maximum Ratings

(V

SS

=

AV

SS

=

0 V)

*1 : Care must be taken that AV

CC

, AVRH do not exceed V

CC

+ 0.3 V. Also, care must be taken that AVRH do not

exceed AV

CC

.

*2 : Maximum output current defines a peak value of a specific terminal.

*3 : Average output current defines a mean value of current flow within a period of 100 ms in a specific terminal.

*4 : Average total output current defines a mean value of current flow within a period of 100 ms in all terminals.

*5 :

·

Aplicable to pins : D16 to D31, A00 to A24, RDY, BGRNT, BRQ, RD, WR0, WR1, CS0 to CS5, CLK, OCPA0

to OCPA3, OC0 to OC3, ALE, INT0 to INT5, SI0, SI2, SO0, SO2, TCI0, SC2

·

Use within recommended operating conditions.

·

Use at DC voltage (current) .

·

The

+

B signal should always be applied with a limiting resistance placed between the

+

B signal and the

microcontroller.

(Continued)

Parameter

Symbol

Rating

Unit

Remarks

Min

Max

Power supply voltage

V

CC

V

SS

-

0.3

V

SS

+

4.0

V

Analog supply voltage

AV

CC

V

SS

-

0.3

V

SS

+

4.0

V

*1

Analog reference voltage

AVRH

V

SS

-

0.3

V

SS

+

4.0

V

*1

Input voltage

V

I

V

SS

-

0.3

V

CC

+

0.3

V

Analog input voltage

V

IA

V

SS

-

0.3

A

VCC

+

0.3

V

Output voltage

V

O

V

SS

-

0.3

V

CC

+

0.3

V

Maximum clamp current

I

CLAMP

-

2.0

+

2.0

mA

*5

Total maximum clamp current

|

I

CLAMP

|

20

mA

*5

"L" level maximum output current

I

OL

10

mA

*2

"L" level average output current

I

OLAV

4

mA

*3

"L" level maximum total output cur-

rent

I

OL

100

mA

"L" level average total output cur-

rent

I

OLAV

50

mA

*4

"H" level maximum output current

I

OH

-

10

mA

*2

"H" level average output current

I

OHAV

-

4

mA

*3

"H" level maximum total output cur-

rent

I

OH

-

50

mA

"H" level average total output cur-

rent

I

OHAV

-

20

mA

*4

Power consumption

Pd

500

mW

Operating temperature

T

A

-

30

+

70

°

C

Storage temperature

Tstg

-

55

+

150

°

C

MB91F127/F128

26

(Continued)

·

The value of the limiting resistance should be set so that when the signal is applied the input current to the

microcontroller pins does not exceed rated values, either instantaneously or for prolonged periods.

·

Note that when the microcontroller drive current is low, such as in the power saving modes, the

+

B input

potential may pass through the protective diode and increase the potential at the VCC pin, and this may affect

other devices.

·

Note that if a

+

B signal is input when the microcontroller power supply is off (not fixed at 0 V) , the power supply is

provided from the pins, so that incomplete operation may result.

·

Note that if the

+

B input is applied during power-on, the power suplly is provided from the pins and the resulting

supply voltage may not be sufficient to operate the power-on reset.

·

Care must be taken not to leave the input pin open.

·

Sample recommended circuits

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current,

temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

·

Input/Output equivalent circuits

P-ch

N-ch

V

CC

R

+

B input (0 V to 16 V)

Limiting

resistance

Protective diode

MB91F127/F128

27

2.

Recommended Operating Conditions

(V

SS

=

AV

SS

=

0 V)

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the

semiconductor device. All of the device's electrical characteristics are warranted when the device is

operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation

outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on

the data sheet. Users considering application outside the listed conditions are advised to contact their

FUJITSU representatives beforehand.

Parameter

Symbol

Value

Unit

Remarks

Min

Max

Power supply

V

CC

3.0

3.6

V

Normal operation

2.0

3.6

Retain RAM data

under "stop" condition

Analog supply voltage

Av

CC

V

SS

-

0.3

V

SS

+

3.6

V

Analog reference voltage

AVRH

AV

SS

AV

CC

V

Operating temperature

T

A

-

30

+

70

°

C

MB91F127/F128

28

3.

DC Characteristics

(AV

CC

=

V

CC

=

3.3 V

±

0.3 V, AV

SS

=

V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

* : Refer to "

s

INPUT/OUTPUT CIRCUIT TYPE".

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Typ

Max

"H" level input

voltage

V

IHS

Hysteresis

input terminal

0.8

×

V

CC

V

CC

+

0.3

V

*

"L" level input

voltage

V

ILS

Hysteresis

input terminal

V

SS

-

0.3

0.2

×

V

CC

V

*

"H" level output

voltage

V

OH

Port2 to PortJ

V

CC

=

3.3 V

I

OH

=

-

4.0 mA

V

CC

-

0.5

V

"L" level output

voltage

V

OL

Port2 to PortJ

V

CC

=

3.3 V

I

OL

=

4.0 mA

0.4

V

Input leak

current

I

LI

Port2 to PortJ

V

CC

=

3.6 V

V

SS

<

VI

<

V

CC

±

5

µ

A

Power supply

current

I

CC

VCC

25 MHz

V

CC

=

3.3 V

75

100

mA

I

CC

25 MHz

V

CC

=

3.3 V

85

120

mA

FLASH

writing

I

CCS

25 MHz

V

CC

=

3.3 V

60

85

mA

Sleeping

I

CCH

T

A

=

25

°

C

V

CC

=

3.3 V

10

150

µ

A

Stopping

Input capacity

C

IN

Other than

AVCC, AVSS,

AVRH, VCC,

VSS

10

pF

MB91F127/F128

29

4.

AC Characteristics

(1) Clock Timing Ratings

(V

CC

=

3.3 V

±

0.3 V, AV

SS

=

V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

*1 : Although PLL allows selection among x1 and x2 multiplication modes, the selection is limited by oscillation

frequency as follows:

Specifying "x2 multiplication" is not allowed if oscillation frequency exceeds 12.5 MHz.

*2 : Frequency regulation indicates a maximum fluctuation from a specified center frequency under locked frequency

multiplication.

Parameter

Symbol

Condition

Value

Unit

Remarks

Min

Max

Clock frequency

(High speed, automatic oscil-

lation)

f

C

10

25

MHz

Self oscillation allowable

range

Clock frequency

(High speed, PLL used)

10

25

MHz

PLL-use allowable area for

self oscillation and external

clock input

*1

Clock frequency

(High speed, 1/2 division in-

put)

10

25

MHz

External clock input

allowable range

Clock cycle time

t

C

40

100

ns

Frequency regulation

(when locked)

f

10

%

*2

Input clock pulse width

P

WH

, P

WL

9.5

ns

Input clock rise and fall time

t

CR

t

CF

8

ns

(t

CR

+

t

CF

)

Internal operation

clock frequency

CPU

system

f

CP

0.625 *

3

25

MHz

Peripheral

system

f

CPP

0.625 *

3

25

MHz

Internal operation

clock cycle time

CPU

system

t

CP

40

1600 *

3

ns

Peripheral

system

t

LCPP

40

1600 *

3

ns

+

f

O

f

O

-

f

=

×

100 (%)

MB91F127/F128

30

*3 : This is a value in the case where 10 MHz signal, a minimum value of clock frequency, is input to X0 and where

1/2-division in oscillation circuit and 1/8-gear are used.

0.8 V

CC

0.2 V

CC

tcf

tcr

t

C

P

WH

P

WL

3.6

3.0

25

Frequency (MHz)

Source voltage (V)

Operation-guaranteed area

(T

A

=

-

30

°

C to

+

70

°

C)

MB91F127/F128

31

(2) Clock Output Timing

(V

CC

=

3.3 V

±

0.3 V, AV

SS

=

V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

*1 : t

CYC

is a frequency of 1 clock cycle indicating gear cycle.

*2 : The values indicate specifications where x1 gear cycle is used.

If gear cycle of 1/2, 1/4, or 1/8 is specified, calculate in the formula below by substituting 1/2, 1/4, or 1/8 into n.

Min : (1

-

n

/

2)

×

t

CYC

-

10

Max : (1

-

n

/

2)

×

t

CYC

+

10

*3 : The values indicate specifications where x1 gear cycle is used.

If gear cycle of 1/2, 1/4, or 1/8 is specified, calculate in the formula below by substituting 1/2, 1/4, or 1/8 into n.

Min : n

/

2

×

t

CYC

-

10

Max : n

/

2

×

t

CYC

+

10

Clock output timing

(3) Reset Input Ratings

(V

CC

=

3.3 V

±

0.3 V, AV

SS

=

V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Max

Cycle time

t

CYC

CLK

t

CP

ns

*1

CLK

CLK

t

CHCL

CLK

1

/

2

×

t

CYC

-

10 1

/

2

×

t

CYC

+

10

ns

*2

CLK

CLK

t

CLCH

CLK

1

/

2

×

t

CYC

-

10 1

/

2

×

t

CYC

+

10

ns

*3

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Max

Reset input time

t

RSTL

RST

t

CP

×

5

ns

CLK

V

OH

V

OL

V

OH

t

CYC

tc

LCH

t

CHCL

RST

0.2 V

CC

t

RSTL

MB91F127/F128

32

(4) Power-on Reset

(V

CC

=

3.3 V

±

0.3 V, V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

Parameter

Symbol

Pin

name

Condition

Value

Unit

Remarks

Min

Max

Power supply rise

time

t

R

VCC

V

CC

=

3.3 V

20

ms

V

CC

<

0.2 V

before turning on

power

Power supply shut

off time

t

OFF

VCC

2

ms

Oscillation stabiliz-

ing wait time

t

OSC

2

×

t

C

×

2

21

+

100

µ

s

ns

0.2 V

t

R

0.9 V

CC

VCC

VSS

2.0 V

3.3 V

VCC

RST

VCC

t

OFF

t

OSC

t

RSTL

A sudden change of supply voltage may activate the power-on reset function. It is recommended that

power voltage should be changed smoothly with less fluctuation of voltages.

Retaining RAM data

The rising slope is recommended

to be less than 50 mV

/

ms.

Be sure to turn on the power while keeping

RST terminal at L level first. When the power

becomes V

CC

level, rise the voltage to H level

after a period of t

RSTL

.

MB91F127/F128

33

(5) Normal Bus Access Read/Write Operation

(V

CC

=

3.3 V

±

0.3 V, V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

*1 : If the bus is expanded by automatic wait insertion or RDY input, add time (tcyc

×

the number of expanded

cycles) to the rated value.

*2 : The ratings are based on conditions with "gear cycle

×

1". If gear cycle of 1/2, 1/4, or 1/8 is specified, calculate

in the formula below by substituting 1/2, 1/4, or 1/8 into n.

Formula : (2

-

n

/

2)

×

t

CYC

-

25

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Max

CS0 to CS5 delay

time

t

CHCSL

CLK

CS0 to CS5

15

ns

CS0 to CS5 delay

time

t

CHCSH

15

ns

Address delay time

t

CHAV

CLK

A24 to A00

15

ns

Data delay time

t

CHDV

CLK

D31 to D16

15

ns

RD delay time

t

CLRL

CLK

RD

15

ns

RD delay time

t

CLRH

15

ns

WR0, 1 delay time

t

CLWL

CLK

WR0, 1

15

ns

WR0, 1 delay time

t

CLWH

15

ns

Valid address

Valid data input time

t

AVDV

A24 to A00

D31 to D16

3

/

2

×

tcyc

-

25

ns

*1

*2

RD

Valid data input time

t

RLDV

RD

D31 to D16

tcyc

-

25

ns

*1

Data setup

RD

Time

t

DSRH

25

ns

RD

Data hold time

t

RHDX

0

ns

MB91F127/F128

34

t

CYC

t

CHCSH

t

CHCSL

t

CHAV

t

CLRL

t

CLRH

t

RLDV

t

AVDV

t

RHDX

2.4 V

2.4 V

2.4 V

0.8 V

0.8 V

2.4 V

t

DSRH

CLK

CS0 ~ CS5

A24 ~ A00

RD

D31 ~ D16

0.8 V

0.8 V

2.4 V

0.8 V

2.4 V

0.8 V

2.4 V

2.4 V

Read

2.4 V

0.8 V

0.8 V

write data

2.4 V

CLK

WR

A24 ~ A00

0.8 V

2.4 V

0.8 V

2.4 V

D31 ~ D16

0.8 V

2.4 V

0.8 V

2.4 V

t

CLWH

t

CLWL

t

CHDV

(WR0 ~ WR1)

MB91F127/F128

35

(6) Timeshared Bus Access Read/Write Operations

(V

CC

=

3.3 V

±

0.3 V, V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

* : If the bus is expanded by automatic wait insertion or RDY input, add time (tcyc x the number of expanded cycles)

to the rated value.

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Max

ALE delay time

t

CLLH2

CLK

ALE

10

ALE delay time

t

CLLL2

10

CS1 delay time

t

CHCSL2

CLK

CS1

15

CS1 delay time

t

CHCSH2

15

ns

Address delay time

t

CHAV2

CLK

D31 to D16

15

ns

Data delay time

t

CHDV2

15

ns

RD delay time

t

CLRL2

CLK

RD

10

ns

RD delay time

t

CLRH2

10

ns

WR0, 1 delay time

t

CLWL2

CLK

WR0

WR1

10

ns

WR0, 1 pulse width

t

CLWH2

10

ns

RD

Valid data input time

t

RLDV2

RD

D31 to D16

t

CYC

-

25

*

Data setup

RD

time

t

DSRH2

25

ns

RD

Data hold time

t

RHDX2

0

ns

MB91F127/F128

36

t

CYC

t

CLLH2

t

CHCSL2

t

CHAV2

t

CHCSH2

t

RLDV2

MA1

MA1

BA1

BA1

t

RHDX2

t

CLRH2

t

CLRL2

t

CHDV2

t

CLWL2

t

CLWH2

t

CHAV2

t

CHAV2

t

DSRH2

t

CLLL2

2.4 V

0.8 V

2.4 V

2.4 V

2.4 V

0.8 V

2.4 V

0.8 V

2.4 V

0.8 V

0.8 V

0.8 V

0.8 V

2.4 V

0.8 V

2.4 V

0.8 V

2.4 V

0.8 V

2.4 V

0.8 V

2.4 V

0.8 V

2.4 V

2.4 V

0.8 V

2.4 V

0.8 V

0.8 V

2.4 V

CLK

ALE

CS1

RD

WR0 - WR1

D31-D16

Multiplex bus

for reading

D31-D16

Multiplex bus

for writing

A15-A08

for

non-multi

Address

Read

Address

Write

MB91F127/F128

37

(7) Ready Input Timing

(V

CC

=

3.3 V

±

0.3 V, AV

SS

=

V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Max

RDY setup time

RCLK

t

RDYS

RDY

CLK

15

ns

CLK

RDY hold time

t

RDYH

CLK

RDY

0

ns

CLK

RDY

RDY

2.4 V

0.8 V

2.4 V

2.4 V

0.8 V

0.8 V

2.4 V

0.8 V

t

RDYH

t

RDYS

t

RDYH

t

RDYS

t

CYC

With

waiting

Without

waiting

MB91F127/F128

38

(8) Hold Timing

(V

CC

=

3.0 V

±

0.3 V, AV

SS

=

V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

Note : More than one cycle is required for BGRNT to change after BRQ is input.

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Max

BGRNT delay time

t

CHBGL

CLK

BGRNT

10

ns

BGRNT delay time

t

CHBGH

10

ns

Terminal floating

BGRNT

time

t

XHAL

BGRNT

t

CYC

-

10

t

CYC

+

10

ns

BGRNT

Terminal valid time

t

HAHV

t

CYC

-

10

t

CYC

+

10

ns

0.8 V

2.4 V

t

CHBGL

t

XHAL

t

HAHV

t

CHBGH

t

CYC

BRQ

BGRNT

CLK

2.4 V

2.4 V

2.4 V

2.4 V

Each pin

High-Z

MB91F127/F128

39

(9) UART Timing

(V

CC

=

3.3 V

±

0.3 V, V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

* : t

CYCP

is a cycle time of peripheral system clock.

Internal shift clock mode

External shift clock mode

Parameter

Symbol Pin name

Condition

Value

Unit

Remarks

Min

Max

Serial clock cycle time

t

SCYC

Internal shift

clock mode

8 t

CYCP

*

ns

SC

SO delay time

t

SLOV

-

10

+

50

ns

Valid SI

SC

t

IVSH

50

ns

SC

Valid SI hold time

t

SHIX

50

ns

Serial clock "H" pulse width

t

SHSL

External shift

clock mode

4 t

CYCP

*

-

10

ns

Serial clock "L" pulse width

t

SLSH

4 t

CYCP

*

-

10

ns

SC

SO delay time

t

SLOV

0

50

ns

Valid SI

SC

t

IVSH

50

ns

SC

Valid SI hold time

t

SHIX

50

ns

Serial busy time

t

BUSY

6 t

CYCP

*

ns

CS

SC, SO delay time

t

CLZO

50

ns

CS

SC input mask time

t

CLSL

3 t

CYCP

*

ns

SC

SC, SO Hi-z time

t

CHOZ

50

ns

SC

SO

SI

t

SHIX

t

IVSH

t

SLOV

t

SCYC

SC

SO

SI

CS

t

CHOZ

t

BUSY

t

CLSL

t

IVSH

t

SHIX

t

SLOV

t

SLSH

t

CLZO

t

SHSL

MB91F127/F128

40

(10) Trigger Input Timing

(V

CC

=

3.3 V

±

0.3 V, V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

* : t

CYCP

is a cycle time of peripheral system clock.

Parameter

Symbol

Pin name

Condition

Value

Unit

Remarks

Min

Max

Input pulse width

t

TRGH

t

TRGL

ATG,

INT0, 1, 2, 3

INT4, 5

5 t

CYCP

*

ns

ATG

INT0, 1, 2, 3

INT4, 5

t

TRGH

t

TRGL

MB91F127/F128

41

(11) A/D Converter Block Electrical Characteristics

(V

CC

=

3.3 V

±

0.3 V, AV

SS

=

V

SS

=

0 V, T

A

=

-

30

°

C to

+

70

°

C)

Notes :

·

Relatively, the errors increase as |AVRH| value becomes smaller.

·

Define an output impedance of external circuit analog input under the following conditions :

Output impedance of external circuit

2 (k

)

If an output impedance of external circuit is exceedingly high, sampling time for analog voltage may run

short.

Parameter

Symbol

Pin name

Value

Unit

Remarks

Min

Typ

Max

Resolution

10

10

BIT

Total error

±

4.0

LSB

Linearity error

±

3.5

LSB

Differential linearity error

±

2.0

LSB

Zero transition voltage

V

0t

AN0 to AN7

AVSS

-

1.5 LSB

AVSS

+

0.5 LSB

AVSS

+

2.5 LSB

mV

Full-scale transition voltage

V

FST

AN0 to AN7

AVRH

-

5.5 LSB

AVRH

-

1.5 LSB

AVRH

+

0.5 LSB

mV

Conversion time

5.3

µ

s

Analog input current

I

AIN

AN0 to AN7

0.1

10

µ

A

Analog input voltage

V

AIN

AN0 to AN7

AV

SS

AVRH

V

Reference voltage

AVRH

AV

SS

AV

CC

V

Power supply current

I

A

AVCC

3.0

5.0

mA

I

AH

5.0

µ

A

Reference voltage supply

current

I

R

AVRH

100

150

µ

A

I

RH

10

µ

A

Variation among channels

AN0 to AN7

4

LSB

MB91F127/F128

42

Analog input circuit model diagram

Analog

input

AVRH

AVSS/

AVRL

Rin

Approx.

3.6 k

Be switched on,

only while A/D

conversion is

performed.

Cin

=

Approx 30 pF

Comparator

Comparator

Comparator

Note : Use the values shows as guides only.

MB91F127/F128

43

5.

A/D Converter Block Electrical Characteristics

·

Resolution

Analog variations recognized by an A/D converter.

·

Linearity error

Deviation of actual conversion characteristics from an ideal line, which is across zero-transition point ("00 0000

0000"

"00 0000 0001") and full-scale transition point ("11 1111 1110"

"11 1111 1111")

·

Differential linearity error

Deviation from ideal value of input voltage, which is required for changing output code by 1 LSB.

·

Total error

Difference between actual value and ideal value. The error includes zero-transition error, full-scale transition

error, and linearity error.

(Continued)

3FF

3FE

3FD

004

003

002

001

AV

SS

AVRH

0.5 LSB'

{1 LSB' ( N

-

1 )

+

0.5 LSB'}

1.5 LSB'

Total error

Actual

characteristics

(Actual mea-

sured value)

Actual

characteristics