## 32-Bit Microcontroller **CMOS**

# FR30 Series

# MB91F127/F128

#### **■** DESCRIPTION

This model, designed on the basis of 32-bit RISC CPU (FR30 series), is a standard single-chip micro controller with built-in I/O resources and bus control functions. The functions are suitable for built-in control that requires high-speed CPU processing.

MB91F127 includes 256 Kbytes built-in flash memory and 14 Kbytes built-in RAM. MB91F128 includes 510 Kbytes built-in flash memory and 14 Kbytes built-in RAM.

The specifications of the devices are best suited for applications requiring high-level CPU processing capabilities, such as navigation system, high-performance FAX, and printer controller.

#### **■ FEATURES**

#### FR-CPU

- 32-bit RISC (FR30), load/store architecture, 5-step pipeline

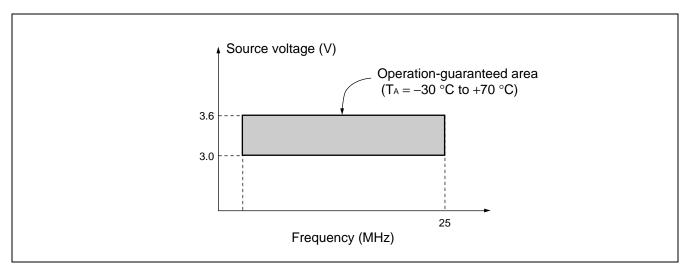

- Operating frequency: Internal 25 MHz

- General register: 32bit x 16 registers

- 16-bit fixed-length instructions (primitives), 1 instruction/1 cycle

- · Instructions of memory-to-memory transfer, bit processing, and barrel shift: Instructions suitable for built-in control

(Continued)

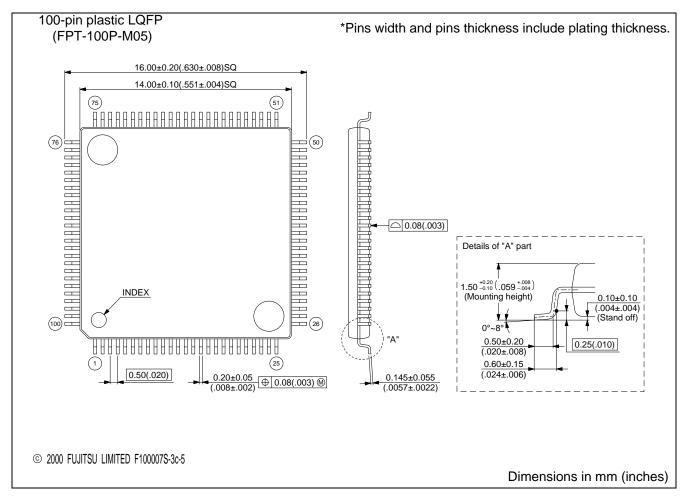

#### ■ PACKAGE

- Function entry/exit instructions, multi load/store instruction for register data: High-level language compatible instructions

- Register interlock functions: Simple description of assembler language

- Branch instructions with delay slot: Reduced overhead on branching process

- · Built-in multiplier/ Supporting at instruction level

Signed 32-bit multiplying: 5 cycles Signed 16-bit multiplying: 3 cycles

• Interrupt (saving PC and PS): 6 cycles, 16 priority levels

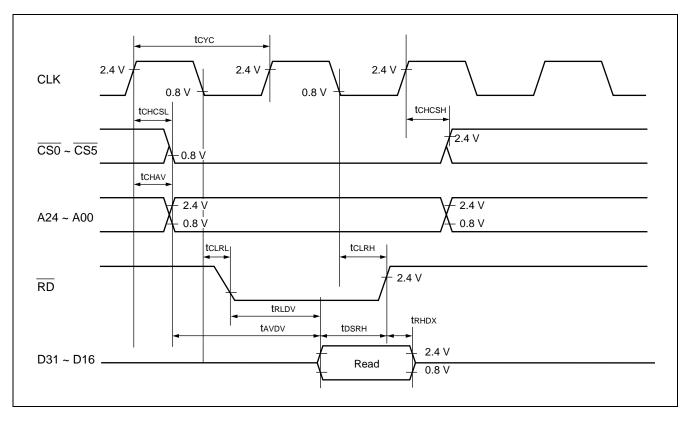

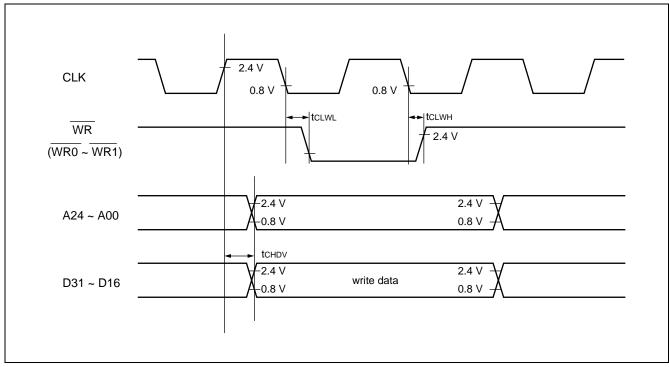

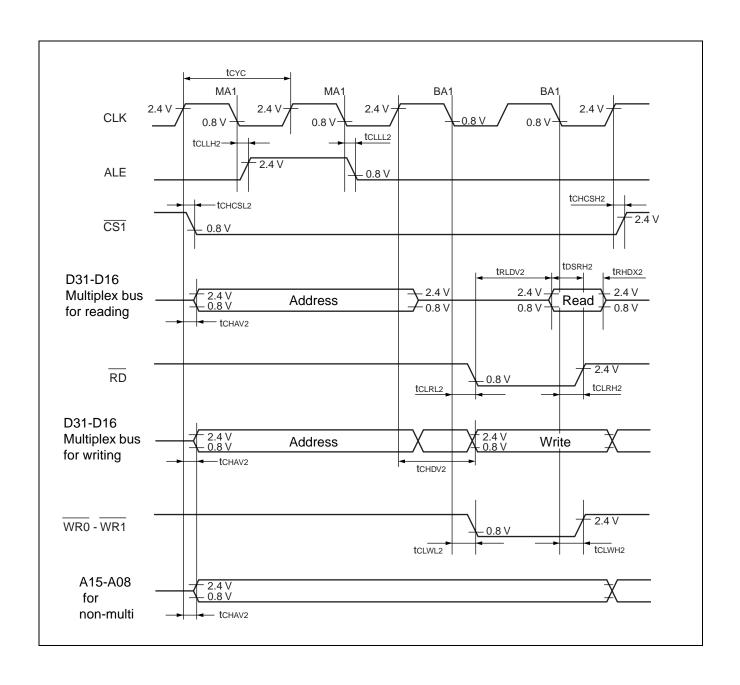

#### **Bus interface**

- Maximum of 25 MHz internal operation rate

- 25-bit address bus (32 MB space)

- 16-bit address output, 8/16-bit data input/output

- Basic bus cycle: 2-clock cycle

- Chip selection outputs specifiable in a minimum of 64 Kbytes steps : 6 outputs

- Automatic wait cycle: Specifiable flexibly from 0 cycle to 7 cycles for each area

- Supporting time-division input/output interface for address/data (for area 1 only)

- · Unassigned data/address terminals are available as input/output ports

- Supporting little endian mode (selecting one area from area 1 to area 5)

#### **DMAC (DMA controller)**

- 8 channels

- Transfer factor : Interrupt request of built-in resources

- Transfer sequence: Step transfer/Block transfer/Burst transfer/Consecutive transfer

- Transfer data length: Selectable among 8 bits, 16 bits, and 32 bits

- Pausing is allowed by interrupt request

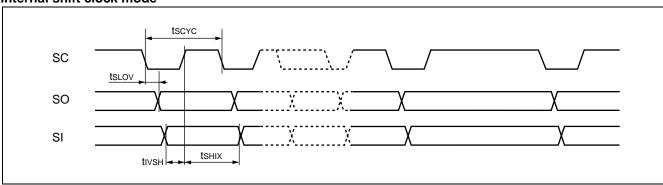

#### **UART**

- 3 channels

- Full-duplex double buffer

- Data length: 7 to 9 bits (no parity), 6 to 8 bits (with parity)

- Asynchronous (start-stop synchronization) or CLK synchronous communication is selectable

- Multi processor mode

- Built-in 16-bit timer (U-Timer) used as a baud-rate generator: Generates an arbitrary baud rate

- External clock is available as a transfer clock

- Error detection : parity, frame, and overrun

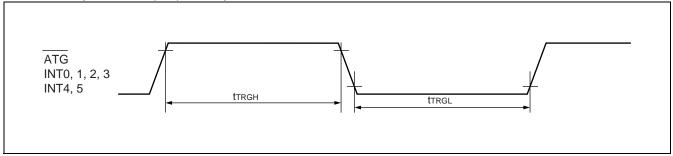

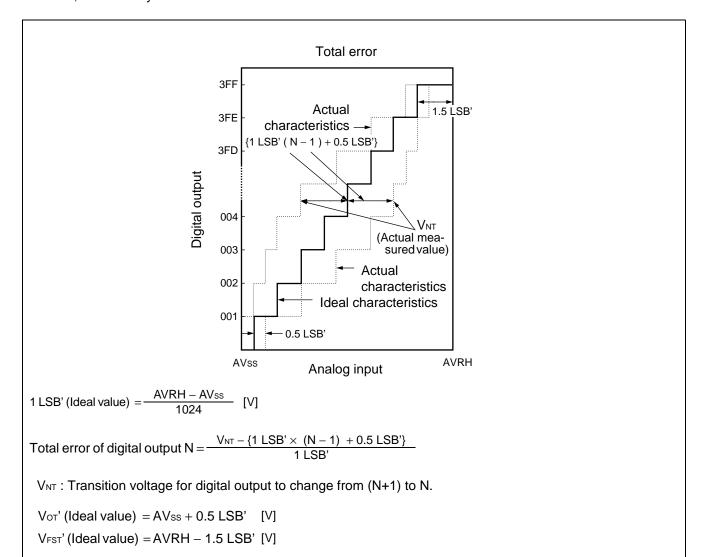

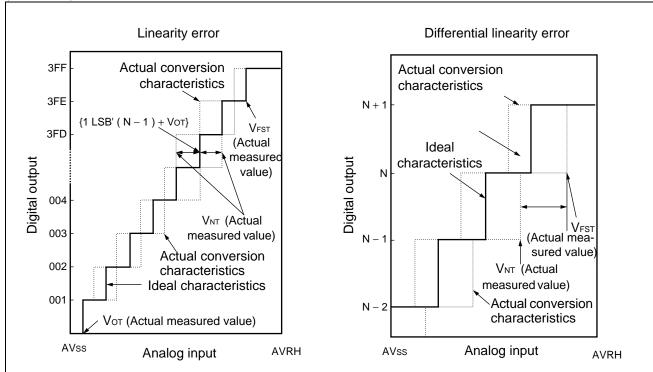

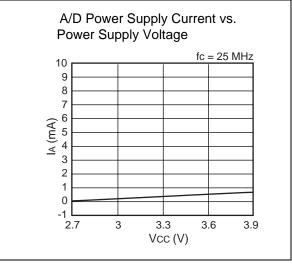

#### A/D converter (sequential transducer)

- 8/10-bit resolution, 8 channels

- Sequential comparison and transducer: At 25 MHz, 5.2 μs

- Built-in sample and hold circuit

- Conversion mode: Selectable among single conversion, scan conversion, and repeat conversion

- Activation: Selectable among software, external trigger, and built-in timer

#### Reload timer

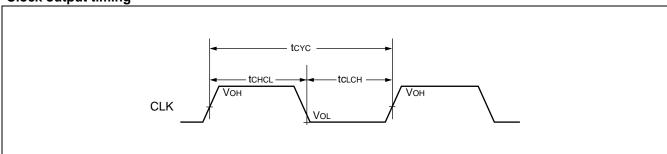

- 16-bit timer: 3 channels

- Internal clock: 2-clock cycle resolution, selectable among 2/8/32 dividing and external clock

#### (Continued)

#### Other interval timers

16-bit timer: 3 channels (U-Timer)

• PPG timer: 4 channels

• 16-bit OCU: 4 channels, ICU: 4 channels, Free-run timer: 1 channel

• Watchdog timer: 1 channel

#### Flash memory 510 KB

• 510 KB FLASH ROM: Read/Write/Erase is allowed with a same power

#### **Built- in RAM 14 KB**

• D-bus RAM 12 KB, C-bus RAM 2 KB

#### Bit search module

• Position of a first bit that changes between "1" and "0" is searched in one cycle, within an MSB of one word.

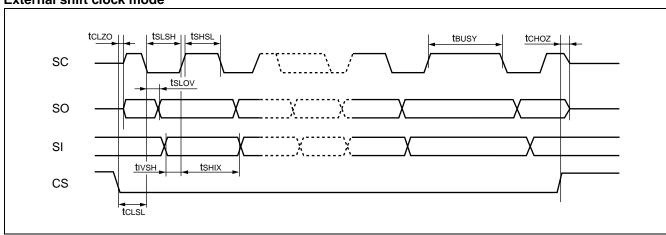

#### Interrupt controller

- External interrupt input: Normal interrupt×6 (INT0 to INT5)

- Internal interrupt factors: UART, DMAC, A/D, Reload timer, UTIMER, delay interrupt, PPG, ICU, and OCU

- Priority levels are programmable (16 levels)

#### **Reset factors**

Power-on reset/watchdog timer/software reset/external reset

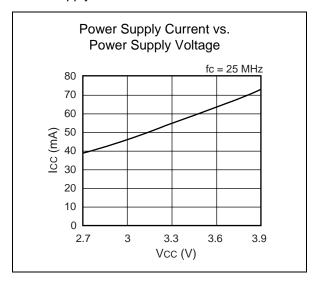

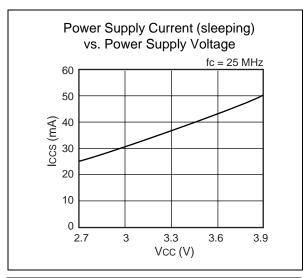

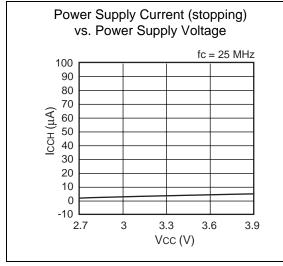

#### Low power consumption mode

• Sleep/stop mode

#### **Clock control**

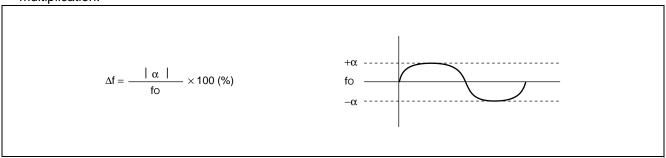

- Built-in PLL circuit, selectable among 1-multiplication, and 2-multiplication

- Gearing function: Operation clock frequencies are freely and independently specifiable for CPU and peripherals.

Gear clocks are selectable among 1/1, 1/2, 1/4, and 1/8 (or among 1/2, 1/4, 1/8, and 1/16). Upper limit of peripheral operations is 25 MHz.

#### **Others**

• Package: LQFP-100

• CMOS technology: 0.35 μm

• Power supply voltage: 3.3 V±0.3 V

#### **■ SERIES CONFIGURATION**

| Model name   | MB91F127            | MB91F128            | MB91FV129          |

|--------------|---------------------|---------------------|--------------------|

| Outline      | Quantity production | Quantity production | Evaluation product |

| FLASH memory | 256 KB              | 510 KB              | 510 KB             |

| D-bus RAM    | 12 KB               | 12 KB               | 16 KB              |

| C-bus RAM    | 2 KB                | 2 KB                | 2 KB               |

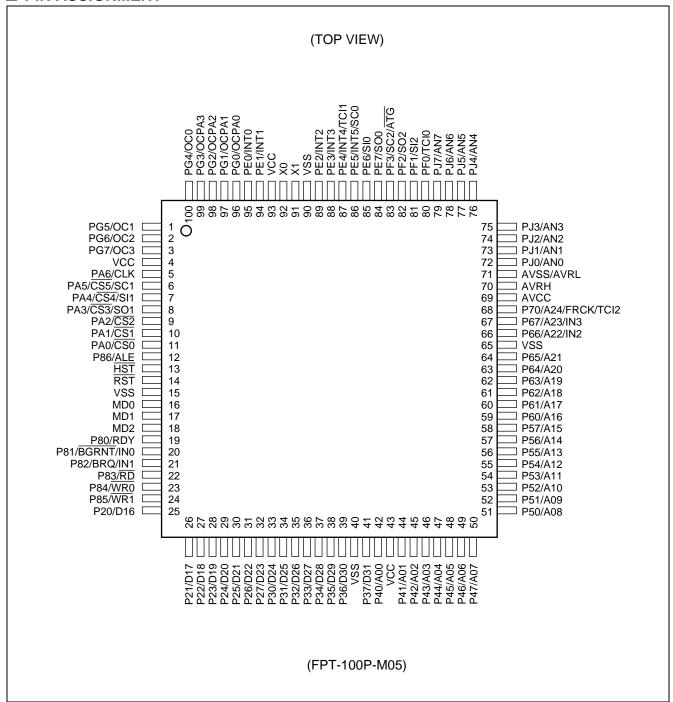

#### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

Note that the numbers in the table are not pin numbers on a package.

| No.                                                                                          | Pin name                                                                                                                                                                     | Input/output circuit type | Description                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                                                         | D16/P20<br>D17/P21<br>D18/P22<br>D19/P23<br>D20/P24<br>D21/P25<br>D22/P26<br>D23/P27                                                                                         | D                         | Bit 16 through bit 23 of external data bus. The terminals are available as general I/O ports (P20 through P27) when external bus width is specified at 8 bits or in single-chip mode.                                                                                      |

| 9<br>10<br>11<br>12<br>13<br>14<br>15                                                        | D24/P30<br>D25/P31<br>D26/P32<br>D27/P33<br>D28/P34<br>D29/P35<br>D30/P36<br>D31/P37                                                                                         | D                         | Bit 24 through bit 31 of external data bus. The terminals are available as general I/O ports (P30 through P37) when the terminals are not used.                                                                                                                            |

| 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32 | A00/P40<br>A01/P41<br>A02/P42<br>A03/P43<br>A04/P44<br>A05/P45<br>A06/P46<br>A07/P47<br>A08/P50<br>A09/P51<br>A10/P52<br>A11/P53<br>A12/P54<br>A13/P55<br>A14/P56<br>A15/P57 | D                         | Bit 00 through bit 15 of external address bus. The terminals are available as general I/O ports (P40 through P47 and P50 through P57) when the terminals are not used as address buses.                                                                                    |

| 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40                                                 | A16/P60<br>A17/P61<br>A18/P62<br>A19/P63<br>A20/P64<br>A21/P65<br>A22/P66/IN2<br>A23/P67/IN3                                                                                 | D                         | Bit 16 through bit 23 of external address bus. The terminals are available as general I/O ports (P60 through P67) when the terminals are not used as address busses. [IN2,IN3]: Input terminals of input capture. This function is active when input capture is operating. |

| No.            | Pin name                      | Input/output circuit type | Description                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|----------------|-------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 41             | A24/P70/FRCK/<br>TCI2         | D                         | Bit 24 of external address bus.  [P70] A24, FRCK and TCI2 are available as general input ports when they are not used.  [FRCK] External clock input of free-run timer. This function is active when external clock input of free-run timer is used.  [TCI2] External clock input of timer 2. This function is active when external clock input of timer 2 is used. |  |  |  |  |

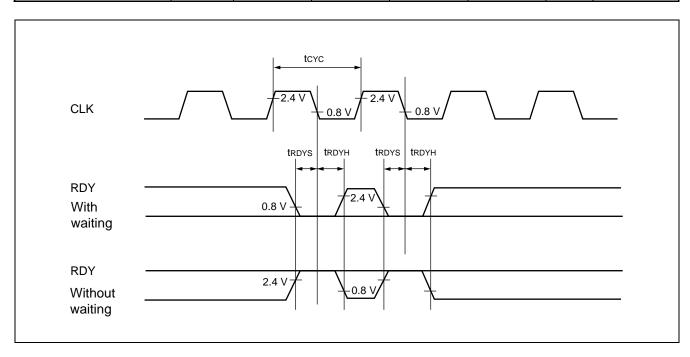

| 42             | RDY/P80                       | D                         | External ready input. Enter "0" when bus cycle under execution does not complete. This terminal is available as general input/output port when it is not used.                                                                                                                                                                                                     |  |  |  |  |

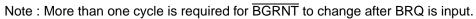

| 43             | BGRNT/P81/IN0                 | D                         | External bus open receive output. This terminal outputs "L" when an external bus is released. This terminal is available as general input/output port when it is not used. [IN0] Input capture input.  This function is active when input capture is under input operation.                                                                                        |  |  |  |  |

| 44             | BRQ/P82/IN1                   | D                         | External bus open request input. Enter "1" when releasing external bus. This terminal is available as general input/output port when it is not used.  [IN1] Input capture input.  This function is active when input capture is under input operation.                                                                                                             |  |  |  |  |

| 45             | RD/P83                        | D                         | External bus read strobe. This terminal is available as general input/output port when it is not used.                                                                                                                                                                                                                                                             |  |  |  |  |

| 46             | WR0/P84                       | D                         | External bus write strobe.Control signals and data bus byte positions are related as the following:                                                                                                                                                                                                                                                                |  |  |  |  |

|                |                               |                           | 16-bit bus width Single chip mode                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                |                               |                           | D31 to D24 WR0 WR0 (port allowed)                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 47             | WR1/P85                       | D                         | D23 to D16 WR1 (port allowed) (port allowed)                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                |                               |                           | Note: WR1 is set to Hi-z during resetting.  For using with 16-bit bus width, use an external pull-up resistor.  [P84 or P85] Available as general input/output ports when WR0 and WR1 are not used.                                                                                                                                                                |  |  |  |  |

| 48<br>49<br>50 | CS0/PA0<br>CS1/PA1<br>CS2/PA2 | D                         | Chip select 0 output (Low active) Chip select 1 output (Low active) Chip select 2 output (Low active) [PA0,1,or 2] Available as general input/output ports when CS0, CS1 and CS2 are not used.                                                                                                                                                                     |  |  |  |  |

| No.                                          | Pin name                                                                                     | Input/output circuit type | Description                                                                                                                                                                                                                                                     |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 51<br>52<br>53                               | CS3/PA3/SO1<br>CS4/PA4/SI1<br>CS5/PA5/SC1                                                    | D                         | Chip select 3, 4, 5 output (Low active). [PA3,4,5] Available as general input/output ports when channel 1 of chip select UART is not used. [SO1,SI1,SC1] Data output, data input, and clock terminals of UART1. Active when UART1 operation is allowed.         |  |

| 54                                           | CLK/PA6                                                                                      | D                         | System clock output. Outputs a same clock as the same frequency of external bus operation. [PA6] Available as general input/output ports it is not used.                                                                                                        |  |

| 55<br>56<br>57<br>58<br>59<br>60<br>61<br>62 | OCPA0/PG0<br>OCPA1/PG1<br>OCPA2/PG2<br>OCPA3/PG3<br>OC0/PG4<br>OC1/PG5<br>OC2/PG6<br>OC3/PG7 | D                         | [OCPA0 to 3] PPG timer outputs. The function is active when PPG timer output is allowed. [OC0 to 3] Output comparison output. The function is active when output comparison output is allowed. [PB0-7] Available as general input/output ports it is not used.  |  |

| 63<br>64<br>65                               | MD0<br>MD1<br>MD2                                                                            | В                         | Mode terminals 0 through 2. The terminals specify basic operation mode of MCU.  Use the terminals by connecting them directly to VCC or VSS.                                                                                                                    |  |

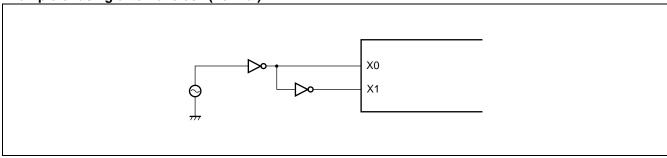

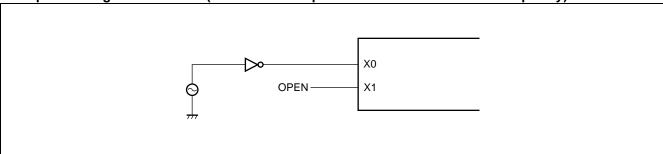

| 66<br>67                                     | X0<br>X1                                                                                     | А                         | Clock (oscillation) input. Clock (oscillation) output.                                                                                                                                                                                                          |  |

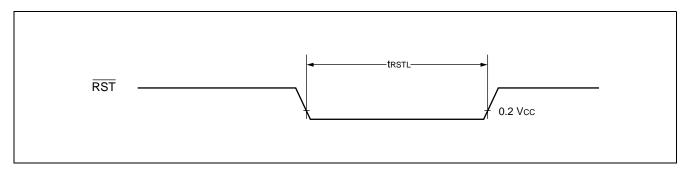

| 68                                           | RST                                                                                          | С                         | External reset input.                                                                                                                                                                                                                                           |  |

| 69                                           | HST                                                                                          | С                         | Hardware standby input.                                                                                                                                                                                                                                         |  |

| 70                                           | P86/ALE                                                                                      | D                         | [ALE] Address latch signal output. The function is active when ALE output of EPCR is allowed.                                                                                                                                                                   |  |

| 71<br>72                                     | INT0/PE0<br>INT1/PE1<br>INT2/PE2                                                             | D                         | [INT0,1,2,3] External interrupt request inputs. The input is used whenever necessary if external interrupt is allowed. Output of other functions must be suspended if not on purpose.                                                                           |  |

|                                              | INT3/PE3                                                                                     |                           | [PE0,1,2,3] General input/output port                                                                                                                                                                                                                           |  |

| 75<br>76                                     | INT4/PE4/TCI1<br>INT5/PE5/SC0                                                                | D                         | [INT4,5] External interrupt request inputs. The input is used whenever necessary if concerned external interrupt is allowed. Output of other functions must be suspended if not on purpose. [TCI1] External clock input of timer 1. [SC0] Clock input of UART0. |  |

|                                              |                                                                                              |                           | [PE4,5] General input/output port                                                                                                                                                                                                                               |  |

| 77                                           | SI0/PE6                                                                                      | D                         | [SI0] Data input of UART0. This function is active when data input of UART0 is allowed.                                                                                                                                                                         |  |

|                                              |                                                                                              |                           | [PE6]General input/output port                                                                                                                                                                                                                                  |  |

| 78                                           | SO0/PE7                                                                                      | D                         | [SO0] Data output of UART0. This function is active when data output of UART0 is allowed.                                                                                                                                                                       |  |

|                                              |                                                                                              |                           | [PE7] General input/output port                                                                                                                                                                                                                                 |  |

#### (Continued)

| No.       | Pin name                                            | Input/output circuit type | Description                                                                                                                                                                                                      |

|-----------|-----------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 79        | PF0/TCI0                                            | D                         | [TCI0] External clock input of timer 0.                                                                                                                                                                          |

| 79        | PPO/TOIO                                            |                           | [PF0] General input/output port                                                                                                                                                                                  |

| 80        | SI2/PF1                                             | D                         | [SI2] Data input of UART2. This function is active when data input of UART2 is allowed.                                                                                                                          |

|           |                                                     |                           | [PF1] General input/output port                                                                                                                                                                                  |

| 81        | SO2/PF2                                             | D                         | [SO2] Data output of UART2. This function is active when data output of UART2 is allowed.                                                                                                                        |

| 01        | 302/FF2                                             |                           | [PF2] General input/output port. This function is active when data output of UART2 is disallowed.                                                                                                                |

| 82        | SC2/PF3/ATG                                         | D                         | [SC2] Clock input of UART2 [ATG]External trigger input of A/D converter The input is used whenever necessary if a function concerned is selected. Output of other functions must be suspended if not on purpose. |

|           |                                                     |                           | [PF3] General input/output port                                                                                                                                                                                  |

|           | AN0/PJ0<br>AN1/PJ1<br>AN2/PJ2                       |                           | [AN0 to AN7] Analog input of A/D converter.<br>This function is active when analog input is specified in AIC register.                                                                                           |

| 83 to 90  | AN3/PJ3<br>AN4/PJ4<br>AN5/PJ5<br>AN6/PJ6<br>AN7/PJ7 | E                         | [PJ0 through PJ7] General input/output ports                                                                                                                                                                     |

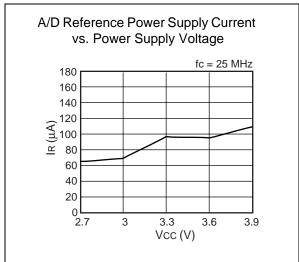

| 91        | AVCC                                                | _                         | VCC power supply for A/D converter                                                                                                                                                                               |

| 92        | AVRH                                                | _                         | Reference voltage of A/D converter (high potential side). Be sure to turn on or off this terminal with a potential higher than AVRH applied to VCC.                                                              |

| 93        | AVSS/AVRL                                           | _                         | A/D converter VSS power source and reference voltage (low potential side).                                                                                                                                       |

| 94 to 96  | VCC                                                 | _                         | Power sources of digital circuits. Be sure to connect power source to all terminals when the device is used.                                                                                                     |

| 97 to 100 | VSS                                                 | _                         | Ground level of digital circuits.                                                                                                                                                                                |

Note: Most of the above terminals multiplex inputs and outputs of I/O ports and resources, as indicated as "XXXX/PXX". If the outputs of ports and resources conflict with each other on the terminals, resources take preferences.

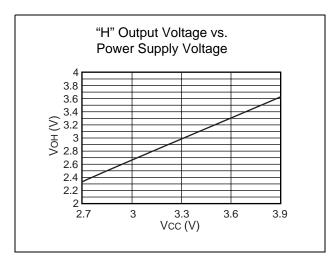

### ■ INPUT/OUTPUT CIRCUIT TYPE

| Туре | Circuit                                                                         | Remarks                                                                                                                                |

|------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| А    | X1 Clock input  X0 STANDBY                                                      | <ul> <li>For 25 MHz system</li> <li>Oscillation feedback register :<br/>Approx. 1MΩ</li> <li>Standby control is available.</li> </ul>  |

| В    | Control signal Mode input Diffused resistor                                     | CMOS level input     High-voltage control is available for FLASH test.                                                                 |

| С    | Diffused resistor  N-channel transistor  Digital input                          | CMOS level hysteresis input     Standby control is not available.                                                                      |

| D    | Diffused resistor Digital output  Digital output  Digital output  Digital input | <ul> <li>CMOS level output</li> <li>CMOS level hysteresis input</li> <li>Standby control is available</li> </ul>                       |

| E    | Diffused resistor  Analog input  STANDBY  Digital output  Digital input         | <ul> <li>Standby control is available</li> <li>CMOS level output</li> <li>CMOS level hysteresis input</li> <li>Analog input</li> </ul> |

#### **■ HANDLING DEVICES**

#### 1. Preventing latch up

On a CMOS IC, latch up may occur when a voltage higher than VCC or a voltage lower than VSS is applied to input terminal or output terminal, or when a voltage exceeding rated level is applied across VCC and VSS. Latch up causes drastic increase of power source current, which may result in destruction of the element by heat. Take extra care not to exceed maximum rating in use. Also, take extra care so that analog terminal does not exceed digital power source.

#### 2. Treatment of unused input terminals

Leaving unused terminals open may cause malfunction. Apply pull-up or pull-down treatment on unused terminals.

#### 3. External reset input

Complete resetting of internal system requires inputting "L" level signal to  $\overline{\mathsf{RST}}$  terminal for a minimum of 5 machine cycles.

#### 4. Notes on using external clock

When using an external clock, supply a clock signal to X0 terminal and supply its antiphase clock to X1 terminal simultaneously. In this case, do not use STOP mode (oscillation stop mode). (Because X1 terminal halts with "H" output under STOP status.)

Under a 12.5 MHz frequency, the device operates with a clock supplied to X0 terminal only.

Figures show examples of using an external clock.

Example of using external clock (normal)

Note: STOP mode (oscillation stop mode) is not available.

Example of using external clock (allowed under operation at 12.5 MHz or lower frequency)

#### 5. Connecting power supply terminals (VCC, VSS)

If two or more VCC, VSS terminals are used, the terminals to be placed under the same potentials are connected with each other internally for preventing malfunctions such as latch up. However, for reducing unwanted radiation, preventing malfunctions of strobe signals and observing total power and current ratings, be sure to connect all of these terminals to power supply and ground externally.

Connecting power supply to VCC - VSS in impedance as low as possible is desirable.

#### 6. Crystal oscillator circuit

Noises around X0 and X1 terminals causes malfunction of the device. Design printed wiring so that X0, X1, and crystal oscillator (or ceramic oscillator), and bypass capacitor to the ground are aligned as close as possible one another. Also the wiring of those elements should not cross with other wiring if possible. Printed wiring with ground wires around X0 and X1 terminals ensures more stable operations. Such designing is strongly recommended.

#### 7. Treating NC terminals

Be sure to leave NC terminals open.

#### 8. Mode terminals (MD0 through MD2)

Do not connect the mode terminals directly to VCC or VSS.

For preventing malfunctions caused by noises, make printed traces between the mode terminals and VCC or VSS as short as possible, and connect the elements in lower impedance.

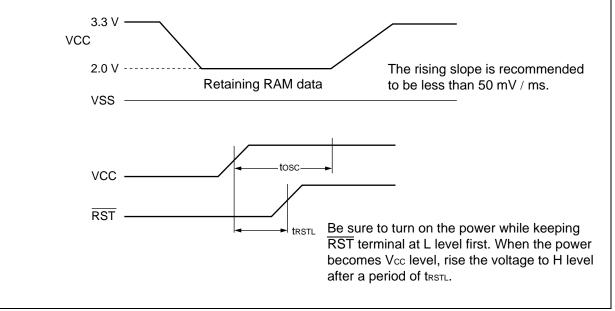

#### 9. Turning power on

Be sure to turn on the power of the device with  $\overline{RST}$  terminal placed under "L" level. Ensure a period at a minimum of 5 cycles of internal operation clock before placing the terminal under "H" level.

#### 10. Terminal status upon turning on power

Status upon turning on the power is indefinite. Upon turning on the power, oscillation starts and the circuit is initialized.

#### 11. Oscillation input upon turning on power

Upon turning on the power, be sure to input a clock signal until oscillation stabilizing wait status is released.

#### 12. Initializing power-on reset

The device includes some built-in registers that are initialized only with power-on reset operation. For initializing the registers, perform power-on reset by turning on the power again.

#### 13. Recovery from Sleep/Stop status

For recovering from Sleep/Stop status initiated by a program in C-Bus RAM, reset the device instead of recovering by an interrupt process.

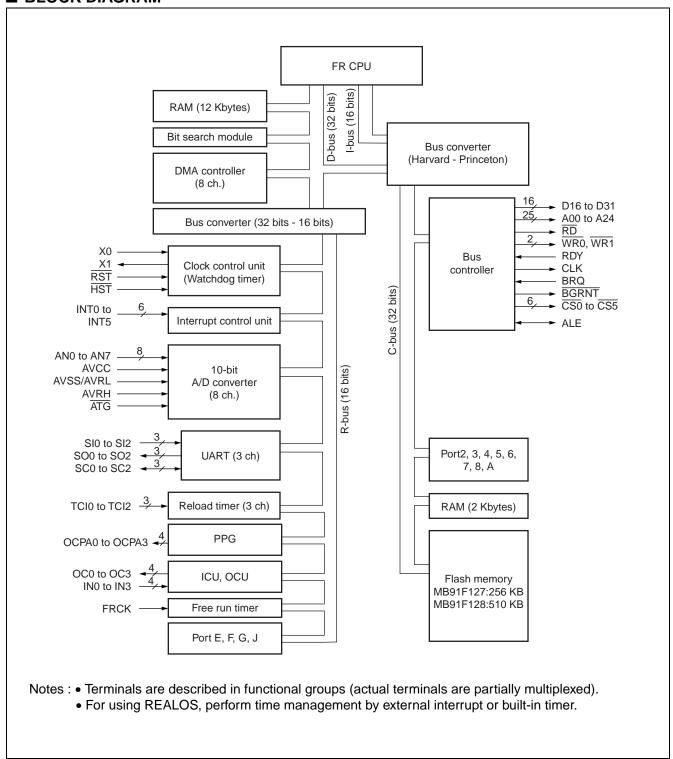

#### **■ BLOCK DIAGRAM**

#### **■ CPU CORE MEMORY SPACE**

#### • MB91F127

|            | External ROM<br>External bus mode | Internal ROM<br>External bus mode | Single-chip mode      |                          |

|------------|-----------------------------------|-----------------------------------|-----------------------|--------------------------|

| 0000 0000н | I/O                               | I/O                               | I/O                   | Direct addressing areas  |

| 0000 0800н | I/O                               | I/O                               | I/O                   | I/O map                  |

| 0000 1000н | Access inhibit                    | Access inhibit                    | Access inhibit        |                          |

|            | Internal RAM<br>12 KB             | Internal RAM<br>12 KB             | Internal RAM<br>12 KB |                          |

| 0000 4000н | Access inhibit                    | Access inhibit                    | Access inhibit        |                          |

| 0001 0000н |                                   | External area                     | Access inhibit        | 0001 0000н               |

|            |                                   | Internal RAM<br>2 KB              | Internal RAM<br>2 KB  | 0008 0800н               |

|            | External area                     | Access inhibit                    | Access inhibit        | 000С 0000н               |

|            |                                   | FLASH ROM<br>256 KB               | FLASH ROM<br>256 KB   |                          |

| FFFF FFFFH |                                   | External area                     | Access inhibit        | 0010 0000н<br>FFFF FFFFн |

Note: External area is not accessible in single-chip mode. When accessing to external areas, select the internal ROM external bus mode in mode register.

#### Direct addressing areas

The areas described below are used for I/O processes. The areas, referred to as "direct addressing areas," allow specifying an operand address directly by an instruction. The direct addressing areas varies as the following, depending on size of the data to be accessed.

Byte-data access: 0 to 0FFH

Half-word data access: 0 to 1FFH

Word-data access: 0 to 3FFH

#### • MB91F128

|            | External ROM<br>External bus mode | Internal ROM<br>External bus mode | Single-chip mode      |                         |

|------------|-----------------------------------|-----------------------------------|-----------------------|-------------------------|

| 0000 0000н | I/O                               | I/O                               | I/O                   | Direct addressing areas |

| 0000 0800н | I/O                               | I/O                               | I/O                   | I/O map                 |

| 0000 1000н | Access inhibit                    | Access inhibit                    | Access inhibit        |                         |

|            | Internal RAM<br>12 KB             | Internal RAM<br>12 KB             | Internal RAM<br>12 KB |                         |

| 0000 4000н |                                   |                                   |                       |                         |

|            | Access inhibit                    | Access inhibit                    | Access inhibit        |                         |

| 0001 0000н |                                   | External area                     | Access inhibit        | 0001 0000н              |

|            |                                   | Internal RAM<br>2 KB              | Internal RAM<br>2 KB  | 0008 0000н              |

|            | External area                     |                                   |                       | 0008 0800н              |

|            |                                   | FLASH ROM<br>510 KB               | FLASH ROM<br>510 KB   |                         |

|            |                                   |                                   |                       | 0010 0000н              |

| FFFF FFFFH |                                   | External area                     | Access inhibit        | FFFF FFFFH              |

Note: External area is not accessible in single-chip mode. When accessing to external areas, select the internal ROM external bus mode in mode register.

#### Direct addressing areas

The areas described below are used for I/O processes. The areas, referred to as "direct addressing areas," allow specifying an operand address directly by an instruction. The direct addressing areas varies as the following, depending on size of the data to be accessed.

Byte-data access: 0 to 0FFH

Half-word data access: 0 to 1FFH

Word-data access: 0 to 3FFH

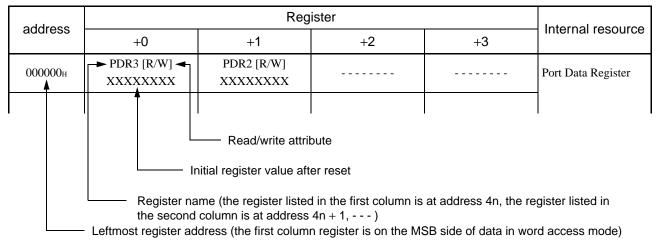

#### ■ LEGEND OF I/O MAP

Note: Register bit values indicate initial values as shown below:

"1" : Initial value"1"

"0" : Initial value"0"

"X" : Initial value "X"

"-" : Register does not exist physically in this position.

### ■ I/O MAP

| Address |                        | Reg                    | ister                        |                        | Internal resource                    |

|---------|------------------------|------------------------|------------------------------|------------------------|--------------------------------------|

| Address | +0                     | +1                     | +2                           | +3                     | Internal resource                    |

| 000000н | PDR3 [R/W]<br>XXXXXXXX | PDR2 [R/W]<br>XXXXXXXX | _                            | _                      |                                      |

| 000004н | PDR7 [R/W]             | PDR6 [R/W]<br>XXXXXXXX | PDR5 [R/W]<br>XXXXXXXX       | PDR4 [R/W]<br>XXXXXXXX |                                      |

| 000008н | _                      | PDRA [R/W]<br>XXXXXXXX | _                            | PDR8[R/W]<br>XXXXXX    | Port data Registe                    |

| 00000Сн |                        | _                      | _                            | 1                      |                                      |

| 000010н | _                      | _                      | PDRE [R/W]<br>XXXXXXXX       | PDRF [R/W]<br>XXXXXXXX |                                      |

| 000014н | PDRG [R/W]<br>XXXXXXXX | _                      | _                            | PDRJ [R/W]<br>XXXXXXXX |                                      |

| 000018н | _                      | _                      | _                            | _                      | Reserved                             |

| 00001Сн | SSR [R/W]<br>00001-00  | SIDR [R/W]<br>XXXXXXXX | SCR [R/W]<br>00000100        | SMR [R/W]<br>00 0 - 00 | UART0                                |

| 000020н | SSR [R/W]<br>00001-00  | SIDR [R/W]<br>XXXXXXXX | SCR [R/W]<br>00000100        | SMR [R/W]<br>00 0 - 00 | UART1                                |

| 000024н | SSR [R/W]<br>00001-00  | SIDR [R/W]<br>XXXXXXXX | SCR [R/W]<br>00000100        | SMR [R/W]<br>00 0 - 00 | UART2                                |

| 000028н | TMRL<br>XXXXXXXX       | R [W]<br>XXXXXXXX      | TMR [W] XXXXXXXX XXXXXXX     |                        | Dalaad Timar O                       |

| 00002Сн | _                      | _                      |                              | R [R/W]<br>00000000    | Reload Timer 0                       |

| 000030н |                        | .R [W]<br>XXXXXXXX     |                              | R [W]<br>XXXXXXXX      | Reload Timer 1                       |

| 000034н | _                      | _                      |                              | R [R/W]<br>00000000    | - Reload Timer I                     |

| 000038н | _                      | _                      | _                            | _                      | Reserved                             |

| 00003Сн |                        | .R [W]<br>XXXXXXXX     |                              | R [W]<br>XXXXXXXX      | Reload Timer 2                       |

| 000040н | _                      | _                      | TMCSR [R/W]                  |                        | - Reload Tilliel 2                   |

| 000044н | IPCF<br>XXXXXXXX       | P1[R]<br>XXXXXXXX      | IPCP0[R] XXXXXXXX XXXXXXX    |                        |                                      |

| 000048н |                        | P3[R]<br>XXXXXXXX      | IPCP2[R]<br>XXXXXXXX XXXXXXX |                        | 16 bit ICU                           |

| 00004Сн | _                      | ICS23[R/W]<br>00000000 | ICS01[R/W] 00000000          |                        |                                      |

| 000050н | ADCI<br>00101-XX       | R [W]<br>XXXXXXXX      | ADCS<br>000000000            | [R/W]<br>00000000      | A/D converter<br>(Serially compared) |

| A -l -l |                                 | Regis                  | ster                     |                            | Internal management |

|---------|---------------------------------|------------------------|--------------------------|----------------------------|---------------------|

| Address | +0                              | +1                     | +2                       | +3                         | Internal resource   |

| 000054н | OCCP1[R/W]<br>XXXXXXXX XXXXXXX  |                        |                          | CP0[R/W]<br>XX XXXXXXXX    | — 16 bit OCU        |

| 000058н | OCCP<br>XXXXXXXX                | 3[R/W]<br>XXXXXXXX     |                          | CCP2[R/W]<br>XX XXXXXXXX   | 10 bit 000          |

| 00005Сн | _                               | _                      |                          |                            | Reserved            |

| 000060н | _                               | _                      |                          |                            | Reserved            |

| 000064н | OCS2,<br>XXX00000               |                        |                          | S0, 1[R/W]<br>000 0000XX00 | 16 bit OCU          |

| 000068н | _                               | _                      |                          |                            | Reserved            |

| 00006Сн | TCDT [R/W]<br>00000000 00000000 |                        | TCCS [R/W]<br>0 00000000 |                            | Free run timer      |

| 000070н | _                               |                        | _                        |                            | Reserved            |

| 000074н | _                               | _                      | _                        |                            | Reserved            |

| 000078н | UTM/UTI<br>00000000             |                        |                          | UTIMC[R/W]<br>0 00001      | U-Timer0            |

| 00007Сн | UTM/UTI<br>00000000             | MR [R/W]<br>00000000   | _                        | UTIMC[R/W]<br>0 00001      | U-Timer1            |

| 000080н | UTM/UTI<br>00000000             |                        | _                        | UTIMC[R/W]<br>0 00001      | U-Timer2            |

| 000084н | -                               | _                      |                          | <del></del>                | Reserved            |

| 000088н | _                               | _                      |                          | <del></del>                | Reserved            |

| 00008Сн | _                               | _                      | _                        |                            | Decembed            |

| 000090н | _                               | _                      | _                        |                            | Reserved            |

| 000094н | EIRR [R/W]<br>00000000          | ENIR [R/W]<br>00000000 | _                        |                            | External interrupt/ |

| 000098н | EHVR [R/W]<br>0000              | ELVR [R/W]<br>00000000 |                          | _                          | NMI                 |

| Address |                                                         | Internal resource   |                         |                               |                         |  |

|---------|---------------------------------------------------------|---------------------|-------------------------|-------------------------------|-------------------------|--|

| Address | +0                                                      | +1                  | +2                      | +3                            | - internal resource     |  |

| 00009Сн |                                                         | -                   | _                       |                               |                         |  |

| 0000А0н |                                                         | _                   |                         |                               |                         |  |

| 0000А4н |                                                         |                     | _                       |                               |                         |  |

| 0000А8н |                                                         |                     | _                       |                               |                         |  |

| 0000АСн |                                                         | -                   | _                       |                               |                         |  |

| 0000В0н |                                                         |                     | _                       |                               |                         |  |

| 0000В4н |                                                         |                     | _                       |                               | Reserved                |  |

| 0000В8н |                                                         | -                   | _                       |                               |                         |  |

| 0000ВСн |                                                         | -                   | _                       |                               |                         |  |

| 0000С0н |                                                         | -                   | _                       |                               |                         |  |

| 0000С4н |                                                         | -                   | _                       |                               |                         |  |

| 0000С8н |                                                         | -                   | _                       |                               |                         |  |

| 0000ССн |                                                         | -                   | _                       |                               |                         |  |

| 0000D0н | _                                                       | _                   | DDRE [W]<br>00000000    | DDRF [W]<br>00000000          | Port direction register |  |

| 0000Д4н |                                                         | AIC3[W]<br>11111111 | _                       | _                             | A/D converter           |  |

| 0000D8н | DDRG [W]<br>00000000                                    |                     | _                       | DDRJ [W]<br>00000000          | Port direction register |  |

| 0000DСн | GCN1<br>00110010                                        |                     |                         | GCN2[R/W]<br>00000000         | PPG ctl                 |  |

| 0000Е0н | PTMF<br>11111111                                        |                     |                         | R0 [W]                        | DDCO                    |  |

| 0000Е4н | PDUT<br>XXXXXXXX                                        |                     | PCNH0[R/W]<br>0000000 - | PCNL0[R/W]<br>00000000        | PPG0                    |  |

| 0000Е8н | PTMR1 [R] PCSR1 [W] 11111111 11111111 XXXXXXXX XXXXXXXX |                     | DDC4                    |                               |                         |  |

| 0000ЕСн | PDUT1 [W]<br>XXXXXXXX XXXXXXX                           |                     | PCNH1[R/W]<br>0000000 - | PCNL1[R/W]<br>00000000        | PPG1                    |  |

| 0000F0н | PTMR2 [R] PCSR2 [W] 11111111 11111111 XXXXXXXX XXXXXXXX |                     | DDC2                    |                               |                         |  |

| 0000F4н | PDUT2 [W]<br>XXXXXXXX XXXXXXX                           |                     | PCNH2[R/W]<br>0000000 - | PCNL2[R/W]<br>00000000        | PPG2                    |  |

| 0000F8н | PTMF<br>11111111                                        |                     |                         | PCSR3 [W]<br>XXXXXXXX XXXXXXX |                         |  |

| 0000FCн |                                                         | 3 [W]               | PCNH3[R/W]<br>0000000 - | PCNL3[R/W]<br>00000000        | - PPG3                  |  |

| A dduccc                 |                                         | Reg                      | ister                    |       | Internal reserves |  |

|--------------------------|-----------------------------------------|--------------------------|--------------------------|-------|-------------------|--|

| Address —                | +0                                      | +1                       | +2                       | +3    | Internal resource |  |

| 000100н<br>to<br>0001FCн |                                         | Reserved                 |                          |       |                   |  |

| 000200н                  |                                         | DPDP                     | [R/W]<br>                | 000   |                   |  |

| 000204н                  | 00                                      | DACSR<br>000000 00000000 | [R/W]<br>00000000 000000 | 000   | DMAC              |  |

| 000208н                  |                                         |                          |                          |       |                   |  |

| 00020Сн                  |                                         |                          |                          |       |                   |  |

| 000210н<br>to<br>0002FCн |                                         | Reserved                 |                          |       |                   |  |

| 000300н<br>to<br>0003ECн |                                         | Reserved                 |                          |       |                   |  |

| 0003F0н                  | BSD0 [W] XXXXXXXX XXXXXXXX XXXXXXXX     |                          |                          |       |                   |  |

| 0003F4 н                 | BSD1 [R/W] XXXXXXXX XXXXXXXX XXXXXXXX   |                          |                          |       |                   |  |

| 0003F8н                  | F8H BSDC [W] XXXXXXXX XXXXXXXX XXXXXXXX |                          |                          |       |                   |  |

| 0003FСн                  | XXXX                                    | BSRR<br>XXXX XXXXXXX     | [R/W]<br>XXXXXXXX XXXX   | (XXXX |                   |  |

| Address                  |                                  | Reg                  | ister               |                      | Internal resource    |  |

|--------------------------|----------------------------------|----------------------|---------------------|----------------------|----------------------|--|

| Address                  | +0                               | +1                   | +2                  | +3                   | - internal resource  |  |

| 000400н                  | ICR00 [R/W]<br>11111             | ICR01[R/W]<br>11111  | ICR02[R/W]<br>11111 | ICR03[R/W]<br>11111  |                      |  |

| 000404н                  | ICR04[R/W]<br>11111              | ICR05[R/W]<br>11111  | ICR06[R/W]<br>11111 | ICR07[R/W]<br>11111  |                      |  |

| 000408н                  | ICR08 [R/W]<br>11111             | ICR09[R/W]<br>11111  | ICR10[R/W]<br>11111 | ICR11[R/W]<br>11111  |                      |  |

| 00040Сн                  | ICR12[R/W]<br>11111              | ICR13[R/W]<br>11111  | ICR14[R/W]<br>11111 | ICR15[R/W]<br>11111  |                      |  |

| 000410н                  | ICR16[R/W]<br>11111              | ICR17[R/W]<br>11111  | ICR18[R/W]<br>11111 | ICR19[R/W]<br>11111  |                      |  |

| 000414н                  | ICR20[R/W]<br>11111              | ICR21[R/W]<br>11111  | ICR22[R/W]<br>11111 | ICR23[R/W]<br>11111  |                      |  |

| 000418н                  | ICR24 [R/W]<br>11111             | ICR25[R/W]<br>11111  | ICR26[R/W]<br>11111 | ICR27[R/W]<br>11111  | Interrupt controller |  |

| 00041Сн                  | ICR28[R/W]<br>11111              | ICR29[R/W]<br>11111  | ICR30[R/W]<br>11111 | ICR31[R/W]<br>11111  |                      |  |

| 000420н                  | ICR32[R/W]<br>11111              | ICR33[R/W]<br>11111  | ICR34[R/W]<br>11111 | ICR35[R/W]<br>11111  |                      |  |

| 000424н                  | ICR36[R/W]<br>11111              | ICR37[R/W]<br>11111  | ICR38[R/W]<br>11111 | ICR39[R/W]<br>11111  |                      |  |

| 000428н                  | ICR40[R/W]<br>11111              | ICR41[R/W]<br>11111  | ICR42[R/W]<br>11111 | ICR43[R/W]<br>11111  |                      |  |

| 00042Сн                  | ICR44[R/W]<br>11111              | ICR45[R/W]<br>11111  | ICR46[R/W]<br>11111 | ICR47[R/W]<br>11111  |                      |  |

| 000430н                  | DICR [R/W]                       | HRCL [R/W]<br>11111  | _                   | _                    | Delay interrupt      |  |

| 000434н<br>to<br>00047Сн |                                  | -                    | _                   |                      | Reserved             |  |

| 000480н                  | RSRR/WTCR<br>[R/W]<br>1XXXX - 00 | STCR [R/W]<br>000111 | PDDR [R/W]<br>0000  | CTBR [W]<br>XXXXXXXX | Clock controller     |  |

| 000484н                  | GCR [R/W]<br>110011 - 1          | WPR [W]<br>XXXXXXXX  | _                   | _                    | - block              |  |

| 000488н                  | PTCR [R/W]<br>00 0               |                      | _                   |                      | PLL controller block |  |

| 00048Сн<br>to<br>0005FСн |                                  | _                    | _                   |                      | Reserved             |  |

(Continued)

| Address                  | Register               |                       |                                                                                    |                       |                                      |  |                             |

|--------------------------|------------------------|-----------------------|------------------------------------------------------------------------------------|-----------------------|--------------------------------------|--|-----------------------------|

| Address                  | +0                     | +1                    | +2                                                                                 | +3                    | Internal resource                    |  |                             |

| 000600н                  | DDR3 [W]<br>00000000   | DDR2 [W]<br>00000000  | _                                                                                  | _                     |                                      |  |                             |

| 000604н                  | DDR7 [W]               | DDR6 [W]<br>00000000  | DDR5 [W]<br>00000000                                                               | DDR4 [W]<br>00000000  | Data direction reg-<br>ister         |  |                             |

| 000608н                  | _                      | DDRA [W]<br>-0000000  | _                                                                                  | DDR8 [W]<br>000000    |                                      |  |                             |

| 00060Сн                  | ASR′<br>00000000       |                       |                                                                                    | 1 [W]<br>00000000     |                                      |  |                             |

| 000610н                  | ASR2<br>00000000       | 2 [W]<br>00000010     |                                                                                    | 2 [W]<br>00000000     |                                      |  |                             |

| 000614н                  | ASR3<br>00000000       |                       | AMR3 [W] 00000000 00000000  AMR4 [W] 00000000 00000000  AMR5 [W] 00000000 00000000 |                       |                                      |  |                             |

| 000618н                  | ASR4<br>00000000       |                       |                                                                                    |                       |                                      |  |                             |

| 00061Сн                  | ASR5<br>00000000       |                       |                                                                                    |                       |                                      |  | External bus inter-<br>face |

| 000620н                  | AMD0 [R/W]<br>XX111    | AMD1 [R/W]<br>0 00000 | AMD32[R/W]<br>00000000                                                             | AMD4 [R/W]<br>0 00000 |                                      |  |                             |

| 000624н                  | AMD5[R/W]<br>0 00000   | DSCR [W]<br>00000000  |                                                                                    | [R/W]<br>00 000       |                                      |  |                             |

| 000628н                  | EPCF<br>1 - 1100       |                       | EPCR1 [W]                                                                          |                       |                                      |  |                             |

| 00062Сн                  | DMCR-<br>00000000      |                       | DMCR:<br>00000000                                                                  | 5 [R/W]<br>0000000-   |                                      |  |                             |

| 000630н<br>to<br>0007BCн |                        | _                     | _                                                                                  |                       | Reserved                             |  |                             |

| 0007С0н                  | FSTR [R/W]<br>000XXXX0 | _                     | _                                                                                  | _                     | Flash memory                         |  |                             |

| 0007С4н<br>to<br>0007F8н |                        | _                     | _                                                                                  |                       | Reserved                             |  |                             |

| 0007FСн                  | _                      | _                     | LER [W]                                                                            | MODR [W]<br>XXXXXXXX  | Little endian register mode register |  |                             |

Note: Do not issue RMW instructions to a register with write-only bit.

RMW instructions (RMW : Read modify write)

AND Rj, @Ri OR Rj, @Ri EOR Rj, @Ri

ANDH Rj, @Ri ORH Rj, @Ri EORH Rj, @Ri

ANDB Rj, @Ri ORB Rj, @Ri EORB Rj, @Ri

BANDL #u4, @Ri BORL #u4, @Ri BEORL #u4, @Ri

BANDH #u4, @Ri BORH #u4, @Ri BEORH #u4, @Ri

Data in "Reserved" or "-" area is indefinite.

### ■ INTERRUPT CAUSES, INTERRUPT VECTORS AND INTERRUPT CONTROL REGISTER ALLOCATIONS

| Intown out access               | Interrup | ot number   | Interru                       | pt level | TBR default           |

|---------------------------------|----------|-------------|-------------------------------|----------|-----------------------|

| Interrupt causes                | Decimal  | Hexadecimal | Register*1                    | Offset   | Address*2             |

| Reset                           | 0        | 00          | _                             | 3FСн     | 000FFFCн              |

| Reserved by system              | 1        | 01          | _                             | 3F8н     | 000FFFF8н             |

| Reserved by system              | 2        | 02          | _                             | 3F4н     | 000FFFF4н             |

| Reserved by system              | 3        | 03          | _                             | 3F0н     | 000FFFF0 <sub>H</sub> |

| Reserved by system              | 4        | 04          | _                             | 3ЕСн     | 000FFFECн             |

| Reserved by system              | 5        | 05          | _                             | 3Е8н     | 000FFFE8н             |

| Reserved by system              | 6        | 06          | _                             | 3Е4н     | 000FFFE4н             |

| Reserved by system              | 7        | 07          |                               | 3Е0н     | 000FFFE0н             |

| Reserved by system              | 8        | 08          | _                             | 3DСн     | 000FFFDCн             |

| Reserved by system              | 9        | 09          | _                             | 3D8н     | 000FFFD8н             |

| Reserved by system              | 10       | 0A          | _                             | 3D4н     | 000FFFD4н             |

| Reserved by system              | 11       | 0B          | _                             | 3D0н     | 000FFFD0н             |

| Reserved by system              | 12       | 0C          | _                             | 3ССн     | 000FFFCCн             |

| Reserved by system              | 13       | 0D          | _                             | 3С8н     | 000FFFC8н             |

| Undefined instruction exception | 14       | 0E          | _                             | 3С4н     | 000FFFC4н             |

| NMI request                     | 15       | 0F          | 15 (F <sub>H</sub> )<br>fixed | 3С0н     | 000FFFC0н             |

| External interrupt 0            | 16       | 10          | ICR00                         | 3ВСн     | 000FFFBCн             |

| External interrupt 1            | 17       | 11          | ICR01                         | 3В8н     | 000FFFB8н             |

| External interrupt 2            | 18       | 12          | ICR02                         | 3В4н     | 000FFFB4н             |

| External interrupt 3            | 19       | 13          | ICR03                         | 3В0н     | 000FFFB0н             |

| UART 0 reception complete       | 20       | 14          | ICR04                         | 3АСн     | 000FFFACн             |

| UART 1 reception complete       | 21       | 15          | ICR05                         | 3А8н     | 000FFFA8н             |

| UART 2 reception complete       | 22       | 16          | ICR06                         | 3А4н     | 000FFFA4н             |

| UART 0 transmission complete    | 23       | 17          | ICR07                         | 3А0н     | 000FFFA0н             |

| UART 1 transmission complete    | 24       | 18          | ICR08                         | 39Сн     | 000FFF9Сн             |

| UART 2 transmission complete    | 25       | 19          | ICR09                         | 398н     | 000FFF98н             |

| Intonuount correct    | Interrup | t number    | Interrup   | ot level | TBR default           |  |

|-----------------------|----------|-------------|------------|----------|-----------------------|--|

| Interrupt causes      | Decimal  | Hexadecimal | Register*1 | Offset   | Address*2             |  |

| DMAC 0 (end, error)   | 26       | 1A          | ICR10      | 394н     | 000FFF94н             |  |

| DMAC 1 (end, erro)    | 27       | 1B          | ICR11      | 390н     | 000FFF90н             |  |

| DMAC 2 (end, erro)    | 28       | 1C          | ICR12      | 38Сн     | 000FFF8Сн             |  |

| DMAC 3 (end, erro)    | 29       | 1D          | ICR13      | 388н     | 000FFF88н             |  |

| DMAC 4 (end, erro)    | 30       | 1E          | ICR14      | 384н     | 000FFF84н             |  |

| DMAC 5 (end, erro)    | 31       | 1F          | ICR15      | 380н     | 000FFF80н             |  |

| DMAC 6 (end, erro)    | 32       | 20          | ICR16      | 37Сн     | 000FFF7Сн             |  |

| DMAC 7 (end, erro)    | 33       | 21          | ICR17      | 378н     | 000FFF78н             |  |

| A/D (sequential type) | 34       | 22          | ICR18      | 374н     | 000FFF74н             |  |

| Reload timer 0        | 35       | 23          | ICR19      | 370н     | 000FFF70н             |  |

| Reload timer 1        | 36       | 24          | ICR20      | 36Сн     | 000FFF6Сн             |  |

| Reload timer 2        | 37       | 25          | ICR21      | 368н     | 000FFF68н             |  |

| External interrupt 4  | 38       | 26          | ICR22      | 364н     | 000FFF64н             |  |

| External interrupt 5  | 39       | 27          | ICR23      | 360н     | 000FFF60н             |  |

| Reserved by system    | 40       | 28          | ICR24      | 35Сн     | 000FFF5Сн             |  |

| Reserved by system    | 41       | 29          | ICR25      | 358н     | 000FFF58н             |  |

| U-TIMER 0             | 42       | 2A          | ICR26      | 354н     | 000FFF54н             |  |

| U-TIMER 1             | 43       | 2B          | ICR27      | 350н     | 000FFF50 <sub>H</sub> |  |

| U-TIMER 2             | 44       | 2C          | ICR28      | 34Сн     | 000FFF4Сн             |  |

| FLASH memory          | 45       | 2D          | ICR29      | 348н     | 000FFF48н             |  |

| Reserved by system    | 46       | 2E          | ICR30      | 344н     | 000FFF44н             |  |

| Reserved by system    | 47       | 2F          | ICR31      | 340н     | 000FFF40н             |  |

| PPG0                  | 48       | 30          | ICR32      | 33Сн     | 000FFF3Сн             |  |

| PPG1                  | 49       | 31          | ICR33      | 338н     | 000FFF38н             |  |

| PPG2                  | 50       | 32          | ICR34      | 334н     | 000FFF34н             |  |

| PPG3                  | 51       | 33          | ICR35      | 330н     | 000FFF30н             |  |

| ICU0 (capture)        | 52       | 34          | ICR36      | 32Сн     | 000FFF2Сн             |  |

| ICU1 (capture)        | 53       | 35          | ICR37      | 328н     | 000FFF28н             |  |

| ICU2 (capture)        | 54       | 36          | ICR38      | 324н     | 000FFF24н             |  |

| ICU3 (capture)        | 55       | 37          | ICR39      | 320н     | 000FFF20н             |  |

#### (Continued)

| Interrupt course                       | Interrup        | t number       | Interru    | ot level           | TBR default                  |

|----------------------------------------|-----------------|----------------|------------|--------------------|------------------------------|

| Interrupt causes                       | Decimal         | Hexadecimal    | Register*1 | Offset             | Address*2                    |

| OCU0 (match)                           | 56              | 38             | ICR40      | 31Сн               | 000FFF1Сн                    |

| OCU1 (match)                           | 57              | 39             | ICR41      | 318н               | 000FFF18н                    |

| OCU2 (match)                           | 58              | 3A             | ICR42      | 314н               | 000FFF14н                    |

| OCU3 (match)                           | 59              | 3B             | ICR43      | 310н               | 000FFF10н                    |

| Reserved by system                     | 60              | 3C             | ICR44      | 30Сн               | 000FFF0Сн                    |

| 16 bit free-run timer                  | 61              | 3D             | ICR45      | 308н               | 000FFF08н                    |

| Reserved by system                     | 62              | 3E             | ICR46      | 304н               | 000FFF04н                    |

| Delay interrupt cause bit              | 63              | 3F             | ICR47      | 300н               | 000FFF00н                    |

| Reserved by system (used by REALOS) *3 | 64              | 40             | _          | 2FСн               | 000FFEFCн                    |

| Reserved by system (used by REALOS) *3 | 65              | 41             | _          | 2F8н               | 000FFEF8⊦                    |

| Used by INT                            | 66<br>to<br>255 | 42<br>to<br>FF | _          | 2F4н<br>to<br>000н | 000FFEF4н<br>to<br>000FFC00н |

<sup>\*1 :</sup> ICR specifies interrupt levels for interrupt requests, using the registers in interrupt controller. ICR is provided for each interrupt request.

Information: An 1 Kbyte area starting with an address indicated by TBR is the vector area for EIT. Size of the area for one vector is 4 byte. Relation between a vector number and a vector address is as follows:

vctadr =

$$TBR + vctofs$$

=  $TBR + (3FCH - 4 \times vct)$

Vctadr Vector address, vctofs: Vector offset, vct: Vector number

<sup>\*2 :</sup> TBR is a register that indicates a head address of the vector table for EIT.

An address that is found by adding offset values defined by TBR and EIT cause, is a vector address.

<sup>\*3 :</sup> If REALOS/FR is used, 0x40 and 0x41 interrupts are used for system code.

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. Absolute Maximum Ratings

(Vss = AVss = 0 V)

| Parameter                                   | Symbol         | Ra          | ating      | Unit  | Remarks |

|---------------------------------------------|----------------|-------------|------------|-------|---------|

| Farameter                                   | Symbol         | Min         | Max        | Ullit | Remarks |

| Power supply voltage                        | Vcc            | Vss - 0.3   | Vss + 4.0  | V     |         |

| Analog supply voltage                       | AVcc           | Vss - 0.3   | Vss + 4.0  | V     | *1      |

| Analog reference voltage                    | AVRH           | Vss - 0.3   | Vss + 4.0  | V     | *1      |

| Input voltage                               | Vı             | Vss - 0.3   | Vcc + 0.3  | V     |         |

| Analog input voltage                        | VIA            | Vss - 0.3   | Avcc + 0.3 | V     |         |

| Output voltage                              | Vo             | Vss - 0.3   | Vcc + 0.3  | V     |         |

| Maximum clamp current                       | ICLAMP         | - 2.0       | + 2.0      | mA    | *5      |

| Total maximum clamp current                 | Σ   ICLAMP     | <del></del> | 20         | mA    | *5      |

| "L" level maximum output current            | loL            |             | 10         | mA    | *2      |

| "L" level average output current            | lolav          | <del></del> | 4          | mA    | *3      |

| "L" level maximum total output current      | ΣΙοι           |             | 100        | mA    |         |

| "L" level average total output cur-<br>rent | $\Sigma$ lolav | _           | 50         | mA    | *4      |

| "H" level maximum output current            | Іон            | _           | -10        | mA    | *2      |

| "H" level average output current            | lohav          | _           | -4         | mA    | *3      |

| "H" level maximum total output current      | ΣІон           | _           | -50        | mA    |         |

| "H" level average total output current      | ΣΙομαν         | _           | -20        | mA    | *4      |

| Power consumption                           | Pd             | _           | 500        | mW    |         |

| Operating temperature                       | TA             | -30         | +70        | °C    |         |

| Storage temperature                         | Tstg           | -55         | +150       | °C    |         |

<sup>\*1 :</sup> Care must be taken that AV $_{CC}$ , AVRH do not exceed V $_{CC}$  + 0.3 V. Also, care must be taken that AVRH do not exceed AV $_{CC}$ .

- Use within recommended operating conditions.

- Use at DC voltage (current) .

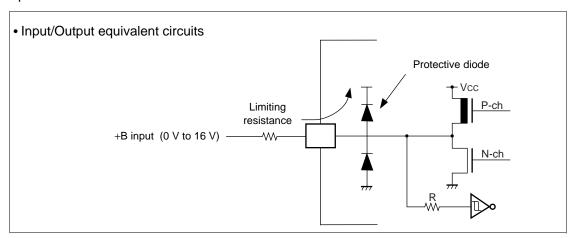

- The +B signal should always be applied with a limiting resistance placed between the +B signal and the microcontroller.

<sup>\*2 :</sup> Maximum output current defines a peak value of a specific terminal.

<sup>\*3 :</sup> Average output current defines a mean value of current flow within a period of 100 ms in a specific terminal.

<sup>\*4 :</sup> Average total output current defines a mean value of current flow within a period of 100 ms in all terminals.

<sup>\*5: •</sup> Aplicable to pins: D16 to D31, A00 to A24, RDY, BGRNT, BRQ, RD, WR0, WR1, CS0 to CS5, CLK, OCPA0 to OCPA3, OC0 to OC3, ALE, INT0 to INT5, SI0, SI2, SO0, SO2, TCI0, SC2

#### (Continued)

- The value of the limiting resistance should be set so that when the signal is applied the input current to the microcontroller pins does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the VCC pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power suplly is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the input pin open.

- Sample recommended circuits

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### 2. Recommended Operating Conditions

(Vss = AVss = 0 V)

| Parameter                | Symbol | Va        | lue       | Unit  | Remarks                                |  |

|--------------------------|--------|-----------|-----------|-------|----------------------------------------|--|

| raiailletei              | Зуппоп | Min       | Max       | Oille | Remarks                                |  |

|                          |        | 3.0       | 3.6       |       | Normal operation                       |  |

| Power supply             | Vcc    | 2.0       | 3.6       | V     | Retain RAM data under "stop" condition |  |

| Analog supply voltage    | Avcc   | Vss - 0.3 | Vss + 3.6 | V     |                                        |  |

| Analog reference voltage | AVRH   | AVss      | AVcc      | V     |                                        |  |

| Operating temperature    | TA     | -30       | +70       | °C    |                                        |  |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

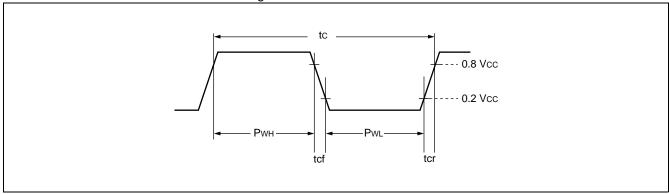

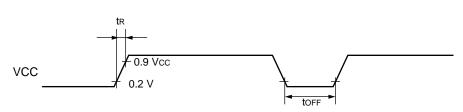

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.