DS07-16314-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

32-Bit Microcontroller

CMOS

FR60 MB91307 Series

MB91306R/MB91307R

DESCRIPTION

The FUJITSU FR family of single-chip microcontrollers using a 32-bit high-performance RISC CPU, with a variety

of built-in I/O resources and bus control mechanisms for built-in control applications requiring high-capability,

high-speed CPU processing. External bus access is assumed in order to support the expanded address space

accessible by the 32-bit CPU, and a 1K bytes cache memory plus large RAM are provided for high-speed execution

of CPU instructions.

This microcontroller is ideal for built-in applications such as DVD players, navigation systems, high-capability FAX

and printer control that demand high-capability CPU processing power.

The MB91307 series is a FR60 family product based on the FR30/40 family CPU with enhanced bus access for

higher speed operation.

FEATURES

FR CPU

· 32-bit RISC, load/store architecture, 5-stage pipeline

· Operating frequency 66MHz [with PLL: base frequency 16.5 MHz]

· 16-bit fixed length instructions (basic instructions), 1 instruction per cycle

· Instructions for built-in applications: memory-to-memory transfer, bit processing, barrel shift etc.

· Instructions adapted for high-level languages: function input/output instructions, register contents multi-load/

store instructions

(Continued)

PACKAGE

120-pin, plastic LQFP

(FPT-120P-M21)

MB91307 Series

2

· Easier assembler notation: register interlock function

· Built-in multiplier/instruction level support

Signed 32-bit multiplication: 5 cycles

Signed 16-bit multiplication: 3 cycles

· Interrupt (PC, PS removal): 6 cycles, 16 priority levels

· Harvard architecture for simultaneous execution of program access and data access

· CPU hold 4-word queue allows advanced instruction fetch function

· 4G bytes expanded memory space enables linear access

· Instruction compatible with FR30/40 family

Bus Interface

· Operating frequency: Max 33 MHz

· 8- or 16-bit data output

· Built-in pre-fetch buffer

· Unused data/address pins can be used as general-0purpose input/output ports

· Fully independent 8-area chip select outputs, can be set in minimum 64K bytes units

· Interface support for many memory types

SRAM, ROM/Flash

Page mode flash ROM, page mode ROM interface

Burst mode flash ROM (select burst length 1, 2, 4, 8)

· Basic bus cycle: 2 cycles

· Programmable by area with automatic wait cycle generation to enable wait insert

· RDY input for external wait cycles

· DMA supports fly-by transfer with independent I/O wait control

Built-in RAM

· 128K bytes (MB91307R), 64K bytes (MB91306R)

· Accepts writing of data and instruction codes, enabling use as instruction RAM

Instruction cache

· 1K bytes capacity

· 2-way set associative

· 4-words (16 bytes) per set

· Lock function enables permanent program storage

· Areas not used for instruction cache can be used for RAM

DMAC (DMA controller)

· 5-channel (3-channel external-to-external)

· 3 transfer sources (external pin, internal peripheral, software)

· Addressing mode with 32-bit full address indication (increment, decrement, fixed)

· Transfer mode (demand transfer / burst transfer / step transfer / block transfer)

· Fly-by transfer support (3 channels between external I/O and external memory)

· Transfer data size selection 8/16/32-bit

Bit search module (using REALOS)

· Searches words from MSB for first bit position of a 1/0 change

Reload timer (includes 1 channel for REALOS)

· 16-bit timer: 3 channels

· Internal clock multiplier choice of x2, x8, x32

(Continued)

MB91307 Series

3

(Continued)

UART

· Full duplex double buffer

· 3-channel

· Parity/no parity selection

· Asynchronous (start-stop synchronized), CLK-synchronized communications selection

· Built-in exclusive baud rate timer

· External clock can be used as transfer clock

· Variety of error detection functions (parity, frame, overrun)

I

2

C* interface

Interrupt controller

· Total of 9 external interrupts: 1 non-maskable interrupt pin (NMI) and 8 normal interrupt pins INT7-INT0

· Interrupt from internal peripheral devices

· Programmable priority settings (16 levels) enabled, except for non-maskable interrupt

· Can be used for wake-up from stop mode

A/D converter

· 10-bit resolution, 4-channel

· Sequential comparator type, conversion time approx. 5.4

µ

s

· Conversion modes: single conversion mode, continuous conversion mode

· Startup source: software / external trigger / timer output signal

Other interval timers

· 16-bit timer with 3 channels (U-timer)

· Watchdog timer

I/O port

· Maximum 69 ports

Other features

· Built-in oscillator circuit for clock source, PLL multiplier selection enabled

· INIT reset pin

· Also included: watchdog timer reset, software reset

· Power-saving modes: stop mode, sleep mode supported

· Gear functions

· Built-in time base timer

· Packages: LQFP-120 (FPT-120P-M21) : MB91306R, MB91307R

: MB91V307R (Evaluation products)

· CMOS technology

: 0.25

µ

m : MB91V307R, 0.18

µ

m : MB91306R, MB91307R

· Supply voltage

: MB91V307R : 3.3 V

±

0.3 V (built-in regulator 3.3 V

2.5 V)

: MB91306R, MB91307R : 3.3 V

±

0.3 V, 1.8V

±

0.15 V dual power supplies

* : Purchase of Fujitsu I

2

C components conveys a license under the Philips I

2

C Patent rights to use, these components

in an I

2

C system provided that the system conforms to the I

2

C Standard Specification as defined by Philips.

· Master/slave sending and receiving

· Arbitration function

· Clock synchronization function

· Slave address/general call address detection function

· Transfer direction detection function

· Start condition repeat generator and detection function

· Bus error detection function

· 10-bit/7-bit slave address

· Operates in standard mode (Max 100 Kbps) or high speed mode (Max 400 Kbps)

MB91307 Series

4

PIN ASSIGNMENT

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

PA3/CS3

PA4/CS4

PA5/CS5

V

CCI

PA6/CS6

PA7/CS7

P80/RDY

P81/BGRNT

P82/BRQ

RD

UUB/WR0

P85/ULB/WR1

NMI

V

CCI

V

SS

INIT

P90/SYSCLK

P91

P92/MCLK

P93

P94/LBA/AS

P95/BAA

P96

P97/WE

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

PI5/SC1

PI4/SO1

PI3/SI1

PI2/SC0

PI1/SO0

PI0/SI0

V

CC

PJ7/INT7/ATG

PJ6/INT6/TIN2

PJ5/INT5/TIN1

PJ4/INT4/TIN0

PJ3/INT3

PJ2/INT2

PJ1/INT1

PJ0/INT0

AN3

AN2

AN1

AN0

AV

SS

/AVRL

AVRH

AV

CC

A24/P70

A23/P67

A22/P66

A21/P65

A20/P64

A19/P63

A18/P62

A17/P61

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

P26/D22

P27/D23

D24

D25

D26

D27

D28

D29

D30

D31

V

SS

A00

A01

A02

A03

A04

A05

A06

A07

V

CC

A08

A09

A10

A11

A12

A13

A14

A15

V

SS

P60/A16

P

A2/CS2

P

A1/CS1

P

A0/CS0

PB7/IORD

PB6/IO

WR

V

CC

X0

X1

V

SS

PB5/DEOP1/DSTP

1

PB4/D

A

CK1

PB3/DREQ1

PB2/DEOP0/DSTP

0

PB1/D

A

CK0

PB0/DREQ0

MD2

MD1

MD0

PG2/DEOP2/DSTP

2

PG1/D

A

CK2

PG0/DREQ2

PH7/SCL

PH6/SD

A

PH5/T

O

T

2

PH4/T

O

T

1

PH3/T

O

T

0

V

SS

PH2/SC2

PH1/SO2

PH0/SI2

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

* : "L" level output after initialization and reset

FPT-120P-M21

MB91307 Series

5

PIN DESCRIPTIONS

(Continued)

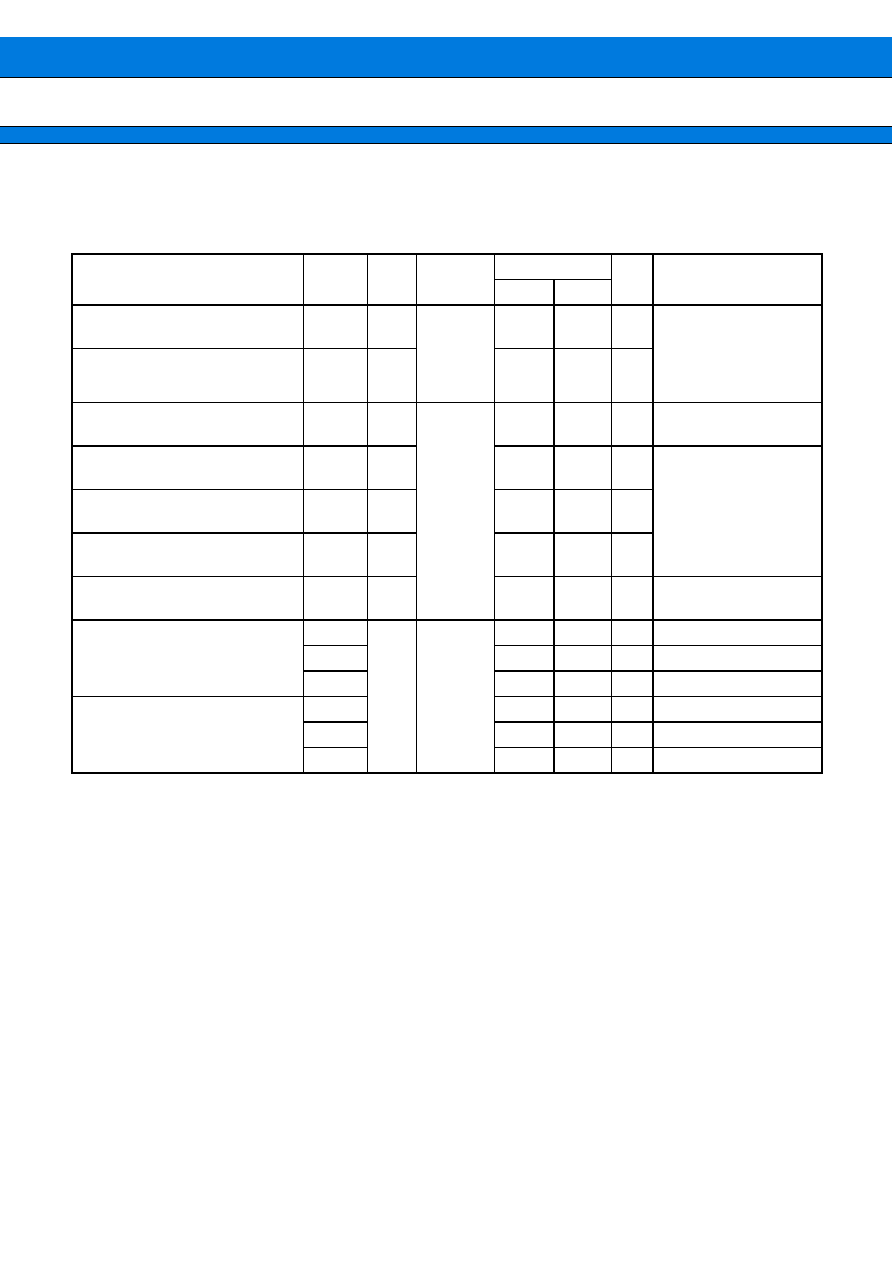

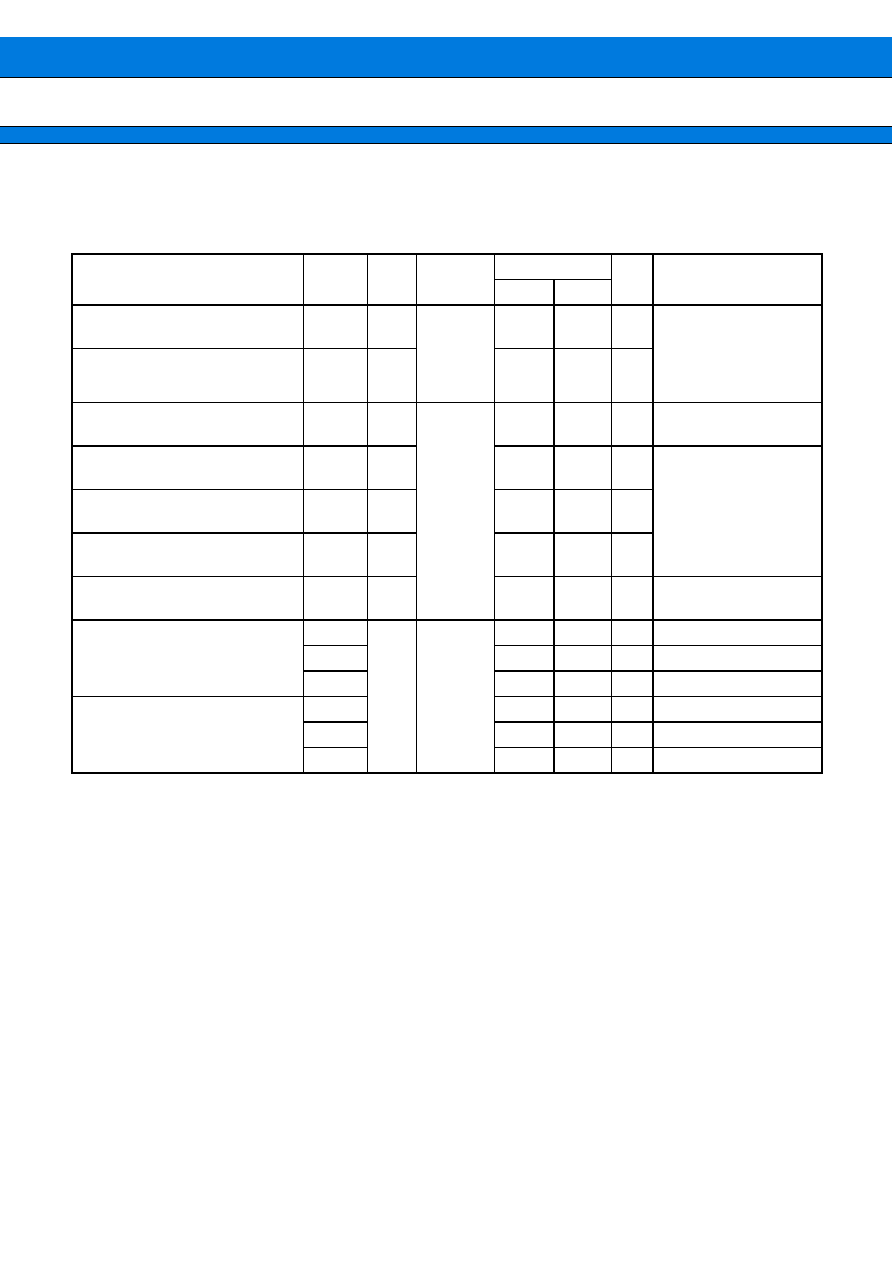

Pin no.

Pin name

I/O

circuit type

Description

85 to 92

D16 to D23

C

External data bus bit 16 to bit 23

Valid only in external bus 16-bit mode.

P20 to P27

These pins can be used as ports in external bus 8-bit mode

93 to 100

D24 to D31

C

External data bus bit 24 to bit 31

102 to 109

A00 to A07

F

External address output bit0 to bit7

111 to 118

A08 to A15

F

External address output bit8 to bit15

120, 1 to 7

A16 to A23

F

External address output bit16 to bit23

P60 to P67

These pins can be used as ports according to setting

8

A24

F

External data bus output bit24

P70

This pin can be used as a port according to setting

9

AV

CC

Power supply pin. Analog power supply for A/D converter

10

AVRH

A/D converter reference voltage supply

11

AV

SS

/AVRL

Power supply pin. Analog power supply for A/D converter

12 to 15

AN0 to AN3

D

A/D converter reference voltage supply. Analog input pin.

16 to 19

INT0 to INT3

I

External interrupt input. When the corresponding external interrupt is en-

abled, this input is in use at all times, so that output from other functions

must be stopped unless used intentionally

PJ0 to PJ3

General purpose input/output port

20 to 22

TIN0 to TIN2

I

Reload timer input. When the corresponding timer input is enabled, this

input is in use at all times, so that output from other functions must be

stopped unless used intentionally.

INT4 to INT6

External interrupt input. When the corresponding external interrupt is en-

abled, this input is in use at all times, so that output from other functions

must be stopped unless used intentionally.

PJ4 to PJ6

General purpose input/output port

23

ATG

I

A/D converter external trigger input. When selected as an A/D start

source, this input is in use at all times, so that output from other functions

must be stopped unless used intentionally.

INT7

External interrupt input. When the corresponding external interrupt is en-

abled, this input is in use at all times, so that output from other functions

must be stopped unless used intentionally.

PJ7

General purpose input/output port

25

SI0

F

UART0 data input. When the UART0 channel is in input operation, this

input is in use at all times, so that output from other functions must be

stopped unless used intentionally.

PI0

General purpose input/output port.

26

SO0

F

UART0 data output. This function is valid when the UART0 data output

function setting is disabled.

PI1

General purpose input/output port. This function is valid when the

UART0 data output function setting is disabled.

MB91307 Series

6

(Continued)

Pin no.

Pin name

I/O

circuit type

Description

27

SC0

F

UART0 clock output. The clock output is valid when the UART0 clock

output function setting is enabled.

PI2

General purpose input/output port. This function is valid when the

UART0 clock output function is disabled.

28

SI1

F

UART1 data input. When UART1 is set for input operation, this input is

in use at all times, so that output from other functions must be stopped

unless used intentionally.

PI3

General purpose input/output port.

29

SO1

F

UART1 data output. This function is enabled when the UART1 data out-

put function setting is enabled.

PI4

General purpose input/output port. This function is valid when the

UART1 data output function setting is disabled.

30

SC1

F

UART1 clock input/output. The clock output is enabled when the UART1

clock output function setting is enabled.

PI5

General purpose input/output port. This function is valid when the

UART1 clock output function setting is disabled.

31

SI2

F

UART2 data input. When UART2 is set for input operation, this input is

in use at all times, so that output from other functions must be stopped

unless used intentionally.

PH0

General purpose input/output port.

32

SO2

F

UART2 data output. This function is enabled when the UART2 data out-

put function setting is enabled.

PH1

General purpose input/output port This function is enabled when the

UART2 data output function setting is disabled.

33

SC2

F

UART2 clock input/output. The clock output is enabled when the UART2

clock output function setting is enabled.

PH2

General purpose input/output port This function is enabled when the

UART2 clock output function is disabled.

35

TOT0

C

Timer output port. This function is valid when the timer output setting is

enabled.

PH3

General purpose input/output port.This pin outputs an "L" level signal at

reset.

36

TOT1

C

Timer output port. This function is valid when the timer output setting is

enabled.

PH4

General purpose input/output port.This pin outputs an "L" level signal at

reset.

37

TOT2

C

Timer output port. This function is valid when the timer output is enabled.

PH5

General purpose input/output port.

MB91307 Series

7

(Continued)

Pin no.

Pin name

I/O

circuit type

Description

38

SDA

Q

I

2

C bus input/output port. This function is valid when I

2

C operation is en-

abled. When the I

2

C bus is in use, the port output must be set to Hi-Z

level. When the I

2

C bus is in use, this is an open drain pin.

PH6

General purpose input/output port.

39

SCL

Q

I

2

C bus input/output port. This function is valid when I

2

C operation is en-

abled. When the I

2

C bus is in use, the port output must be set to Hi-Z

level. When the I

2

C bus is in use, this is an open drain pin.

PH7

General purpose input/output port.

40

DREQ2

F

DMA external transfer request input. When selected as a DMA startup

source, this input is in use at all times, so that output from other functions

must be stopped unless used intentionally.

PG0

General purpose input/output port.

41

DACK2

F

DMA external transfer request acknowledge output. This function is valid

when the DMA transfer request acknowledge output setting is enabled.

PG1

General purpose input/output port. This function is valid when the DMA

transfer request acknowledge output setting is enabled.

42

DEOP2

F

DMA external transfer end output. This function is valid when the DMA

external transfer end output setting is enabled.

DSTP2

DMA external transfer stop input. This function is valid when the DMA ex-

ternal transfer stop input setting is enabled.

PG2

General purpose input/output port. This function is valid when the DMA

external transfer end output selection and the DMA external transfer stop

input selection are disabled.

43 to 45

MD2 to MD0

G

Mode pins 2 to 0. The setting of these two pins determines the basic

operating mode. They should be connected to V

cc

or V

ss

.

46

DREQ0

F

DMA external transfer request input. When selected as a DMA startup

source, this input is in use at all times, so that output from other functions

must be stopped unless used intentionally.

PB0

General purpose input/output port.

47

DACK0

F

DMA external transfer request acknowledge output. This function is valid

when the DMA transfer request acknowledge output setting is enabled.

PB1

General purpose input/output port. This function is enabled when the

DMA transfer request acknowledge output setting is disabled.

48

DEOP0

F

DMA external transfer end output. This function is valid when the DMA

external transfer end output setting is enabled.

DSTP0

DMA external transfer stop input. This function is valid when the DMA ex-

ternal transfer stop input setting is enabled.

PB2

General purpose input/output port. This function is valid when the DMA

external transfer end output selection and the DMA external transfer stop

input selection are disabled.

MB91307 Series

8

(Continued)

Pin no.

Pin name

I/O

circuit type

Description

49

DREQ1

F

DMA external transfer request input. When selected as a DMA startup

source, this input is in use at all times, so that output from other functions

must be stopped unless used intentionally.

PB3

General purpose input/output port.

50

DACK1

F

DMA external transfer request acknowledge output. This function is valid

when the DMA transfer request acknowledge output setting is enabled.

PB4

General purpose input/output port. This function is enabled when the

DNA transfer request acknowledge output setting is disabled.

51

DEOP1

F

DMA external transfer end output. This function is valid when the DMA

external transfer end output setting is enabled.

DSTP1

DMA external transfer stop input. This function is valid when the DMA ex-

ternal transfer stop input setting is enabled.

PB5

General purpose input/output port. This function is valid when the DMA

external transfer end output selection and the DMA external transfer stop

input selection are disabled.

53

X1

A

Clock (oscillator) output

54

X0

Clock (oscillator) input

56

IOWR

F

Write strobe output for DMA fly-by transfer. This function is valid when

the DMA fly-by transfer write strobe output setting is enabled.

PB6

General purpose input/output port. This function is valid when the DMA

fly-by transfer write strobe output setting is disabled.

57

IORD

F

Read strobe output for DMA fly-by transfer. This function is valid when

the DMA fly-by transfer read strobe output setting is enabled.

PB7

General purpose input/output port. This function is valid when the DMA

fly-by transfer read strobe output setting is disabled.

58

CS0

F

Chip select output. This function is valid when the chip select 0 output

setting is enabled.

PA1

General purpose input/output port. This function is valid when the chip

select 0 output setting is disabled.

59

CS1

F

Chip select output. This function is valid when the chip select 1 output

setting is enabled.

PA1

General purpose input/output port. This function is valid when the chip

select 1 output setting is disabled.

60

CS2

F

Chip select output. This function is valid when the chip select 2 output

setting is enabled.

PA2

General purpose input/output port. This function is valid when the chip

select 2 output setting is disabled.

61

CS3

F

Chip select output. This function is valid when the chip select 3 output

setting is enabled.

PA3

General purpose input/output port. This function is valid when the chip

select 3 output setting is disabled.

MB91307 Series

9

(Continued)

Pin no.

Pin name

I/O

circuit type

Description

62

CS4

F

Chip select output. This function is valid when the chip select 4 output set-

ting is enabled.

PA4

General purpose input/output port. This function is valid when the chip se-

lect 4 output setting is disabled.

63

CS5

F

Chip select output. This function is valid when the chip select 5 output set-

ting is enabled.

PA5

General purpose input/output port. This function is valid when the chip se-

lect 5 output setting is disabled.

64

V

CCI

Internal Power supply pin (1.8 V power supply) .

65

CS6

F

Chip select output. This function is valid when the chip select 6 output set-

ting is enabled.

PA6

General purpose input/output port. This function is valid when the chip

select 6 output setting is disabled.

66

CS7

F

Chip select output. This function is valid when the chip select 7 output set-

ting is enabled.

PA7

General purpose input/output port. This function is valid when the chip

select 7 output setting is disabled.

67

RDY

C

External ready signal input. This function is valid when the external ready

input setting is enabled.

P80

General purpose input/output port. This function is valid when the exter-

nal ready input setting is disabled.

68

BGRNT

F

External bus open acknowledge output. This pin outputs an L level signal

when the external bus is open. This function is valid when the output set-

ting is enabled.

P81

General purpose input/output port. This function is valid when the output

setting is disabled.

69

BRQ

P

External bus open request input. The input value is "1" when the external

bus is open. This function is valid when the input setting is enabled.

P82

General purpose input/output port. This function is valid when the input

setting is disabled.

70

RD

M

External bus read strobe output.

71

WR0

UUB

F

External bus write strobe output.

Upper side of the 16-bit SRAM input/output mask enable signal.

It is valid when the external bus is set to SRAM use. (WE/P97 function as

the write strobe.)

72

WR1

ULB

F

External bus write strobe output.

Lower side of the 16-bit SRAM input/output mask enable signal.

It is valid when the external bus is set to SRAM use. (WE/P97 function as

the write strobe.)

P85

General purpose input/output port. This function is valid when the enable

output setting is disabled.

MB91307 Series

10

(Continued)

Pin no.

Pin name

I/O

circuit type

Description

73

NMI

H

NMI

request

input

74

V

CCI

H

Internal Power supply pin(1.8 V power supply)

76

INIT

B

External reset input

77

SYSCLK

F

System clock output. This function is valid when the system clock output

setting is enabled. The clock signal output is at the same frequency as the

external bus operating frequency. Clock output halts in the stop mode or

the hardware standby mode.

P90

General purpose input/output port. This function is enabled when the sys-

tem clock output setting is disabled.

78

P91

F

General purpose input/output port. This function is enabled when the

SDRAM clock enable output setting is disabled.

79

MCLK

F

Memory clock output. Clock output halts in the sleep mode, the stop mode

or the hardware standby mode.

P92

General purpose input/output port. This function is enabled when the

clock output setting is disabled.

80

P93

F

General purpose input/output port. This function is enabled when the

SDRAM clock re-input setting is disabled.

81

AS

F

Address strobe output. This function is valid when the address strobe out-

put setting is disabled.

LBA

Burst flash ROM address load output. This function is valid when the ad-

dress load output setting is enabled.

P94

General purpose input/output port. This function is valid when the address

load output and address strobe output settings are disabled.

82

BAA

Burst flash ROM address advance output. This function is valid when the

address advance output setting is enabled.

P95

General purpose input/output port. This function is valid when the address

advance output and column address strobe output settings are disabled.

83

P96

F

General purpose input/output port. This function is enabled when the col-

umn address strobe output setting is disabled.

84

WE

Write strobe output for 16-bit SRAM. This function is enabled when the

write strobe output setting is enabled.

P97

General purpose input/output port. This function is enabled when the write

strobe output setting is prohibited.

9

AV

CC

A/D converter power supply

10

AVRH

A/D converter power supply

11

AV

SS

/AVRL

A/D converter power supply (GND)

24, 55,

110

V

CC

Power supply pins

34, 52,

75, 101

V

SS

Power supply pins (GND)

MB91307 Series

11

I/O CIRCUIT TYPE

(Continued)

Type

Circuit

Remarks

A

· Oscillator feedback resistance

approx. 1 M

B

· CMOS hysteresis input

with pull-up resistance (25 k

)

C

· CMOS level input/output

with standby control

D

· Analog input with switch

X1

STANDBY

CONTROL

X0

clock input

digital input

STANDBY CONTROL

digital input

digital output

digital output

CONTROL

analog input

MB91307 Series

12

(Continued)

Type

Circuit

Remarks

F

· CMOS level output

· CMOS level hysteresis input

with standby control

G

· CMOS level input

without standby control

H

· CMOS level hysteresis input

without standby control

I

· CMOS level input

· CMOS level hysteresis input

without standby control

M

· CMOS level input

STANDBY CONTROL

digital output

digital input

digital output

digital input

digital input

digital output

digital input

digital output

digital output

digital output

MB91307 Series

13

(Continued)

Type

Circuit

Remarks

P

· CMOS level input/output

with standby control

with pull-down resistance (25 k

)

Q

· Open drain output

CMOS level hysteresis input

with standby control

STANDBY CONTROL

CONTROL

digital output

digital input

digital output

STANDBY CONTROL

digital input

Open drain control

digital output

MB91307 Series

14

HANDLING DEVICES

MB91307 Series

·

Preventing Latchup

When CMOS integrated circuit devices are subjected to applied voltages higher than V

CC

at input and output

pins (other than medium- and high-withstand voltage pins), or to voltages lower than V

SS

, as well as when voltages

in excess of rated levels are applied between V

CC

and V

SS

, a phenomenon known as latchup can occur. When

a latchup condition occurs, supply current can increase dramatically and may destroy semiconductor elements.

In using semiconductor devices, always take sufficient care to avoid exceeding maximum ratings.

·

Treatment of unused pins

Do not leave an unused input pin open, since it may cause a malfunction. Handle by, using a pull-up or

pull-down resistor.

·

About power supply pins

In products with multiple V

CC

or V

SS

pins, the pins of the same potential are internally connected in the device

to avoid abnormal operations including latch-up. However, you must connect the pins to external power supply

and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals

caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with the V

CC

and V

SS

pins of this device at the low impedance.

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1 mF between V

CC

and V

SS

near

this device.

·

Notes on Power-ON/shut-down

Cautions to take when turning on/off V

CCI

(1.8-V internal power supply) and V

SS

(3.3-V external-pin power

supply)

Do not apply V

SS

(external) alone continuously (for over an indication of one minute) with V

CCI

(internal) discon-

nected not to cause a reliability problem with the LSI.

When V

SS

(external) returns from the OFF state to the ON state, the circuit may fail to hold its internal state, for

example, due to power supply noise.

·

Precautions for use of stop mode

The built-in regulator in this device stops operating when the device is in stop mode. In such cases as when

increased leak current (I

CCH

) in stop mode, or abnormal operation or power fluctuation due to noise while in

operating mode cause the regulator to stop, the internal 2.5 V power supply can ball below the voltage at which

operation is assured. Therefore it is necessary when using the internal regulator and stop mode to assure that

the external power supply does not fall below 3.3 V. And even if this should occur, the internal regulator can be

set to restart when a reset is applied. (In this case the oscillator stabilization wait period should also be set to

"L" level.)

When the power is turned on

V

CCI

(internal)

V

SS

(external)

Signal

When the power is turned off

Signal

V

SS

(external)

V

CCI

(internal)

MB91307 Series

15

· Sample use of Stop Mode with 3.3 V power supply

·

About crystal oscillator circuit

Noise near the X0 and X1 pins may cause the device to malfunction. Design the printed circuit board so that

X0, X1, the crystal oscillator (or ceramic oscillator) , and the bypass capacitor to ground are located as close to

the device as possible.

It is strongly recommended to design the PC board artwork with the X0 and X1 pins surrounded by ground plane

because stable operation can be expected with such a layout.

·

Treatment of NC pins

Any pins marked "NC" (not connected) must be left open.

·

About mode pins (MD0 to MD2)

Mode pins (MD0 to MD2) should be connected directly to V

CC

or V

SS

.

To prevent the device erroneously switching to test mode due to noise, design the printed circuit board such that

the distance between the mode pins and V

CC

or V

SS

is as short as possible and the connection impedance is low.

·

Operation at startup

Immediately after a power-on startup, always apply a reset initialization (INIT) at the INIT pin. Also, in order to

assure a wait period for the oscillator circuits to stabilize immediately after startup, be sure that the "L" level input

to the INIT pin continues for the required stabilization wait interval. (The INIT cycle for the INIT pin includes only

the minimum setting for the stabilization wait period.)

·

Base oscillator input at startup

At power-on startup, always input a clock signal until the oscillator stabilization wait period is ended.

·

Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even

when there is no external oscillator or external clock input is stopped. Performance of this operation, however,

cannot be guaranteed.

·

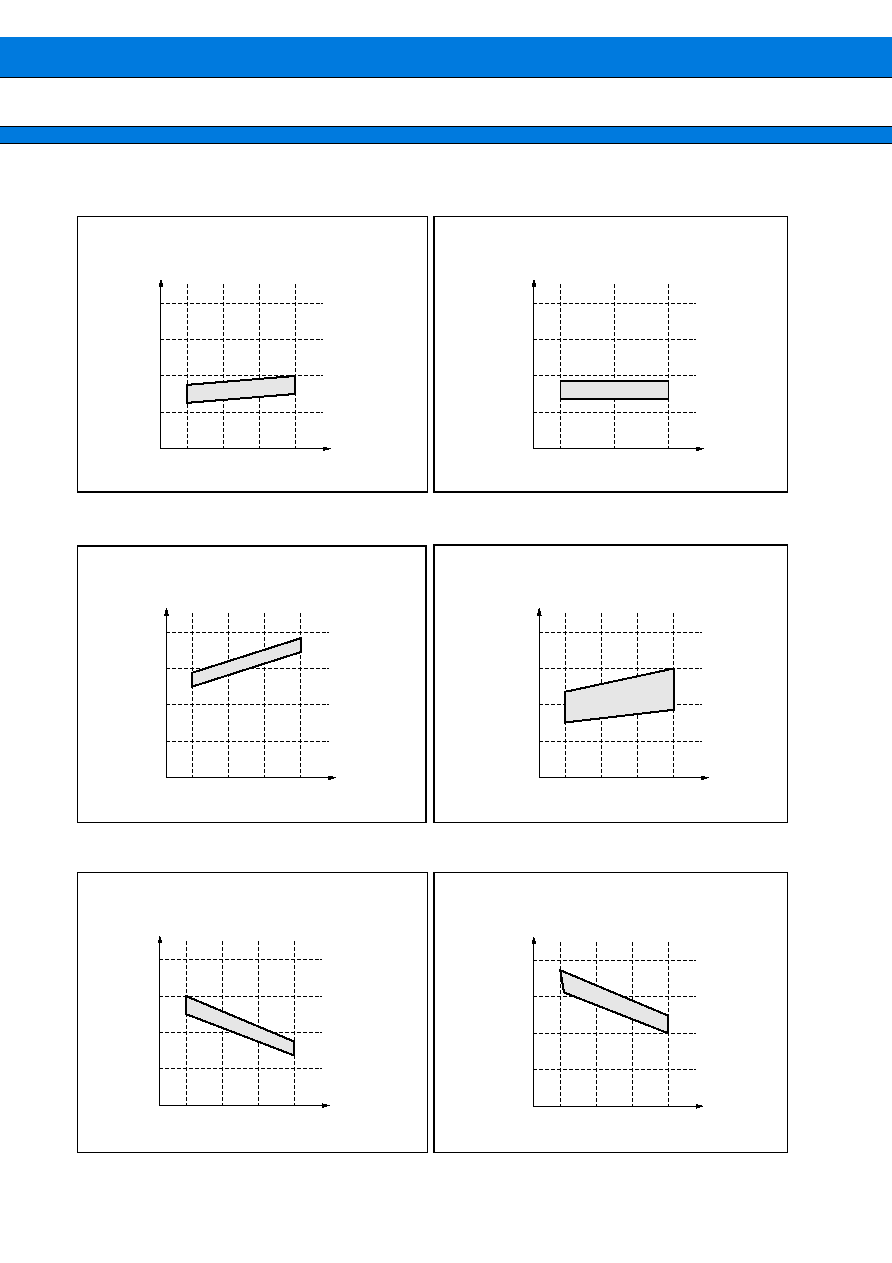

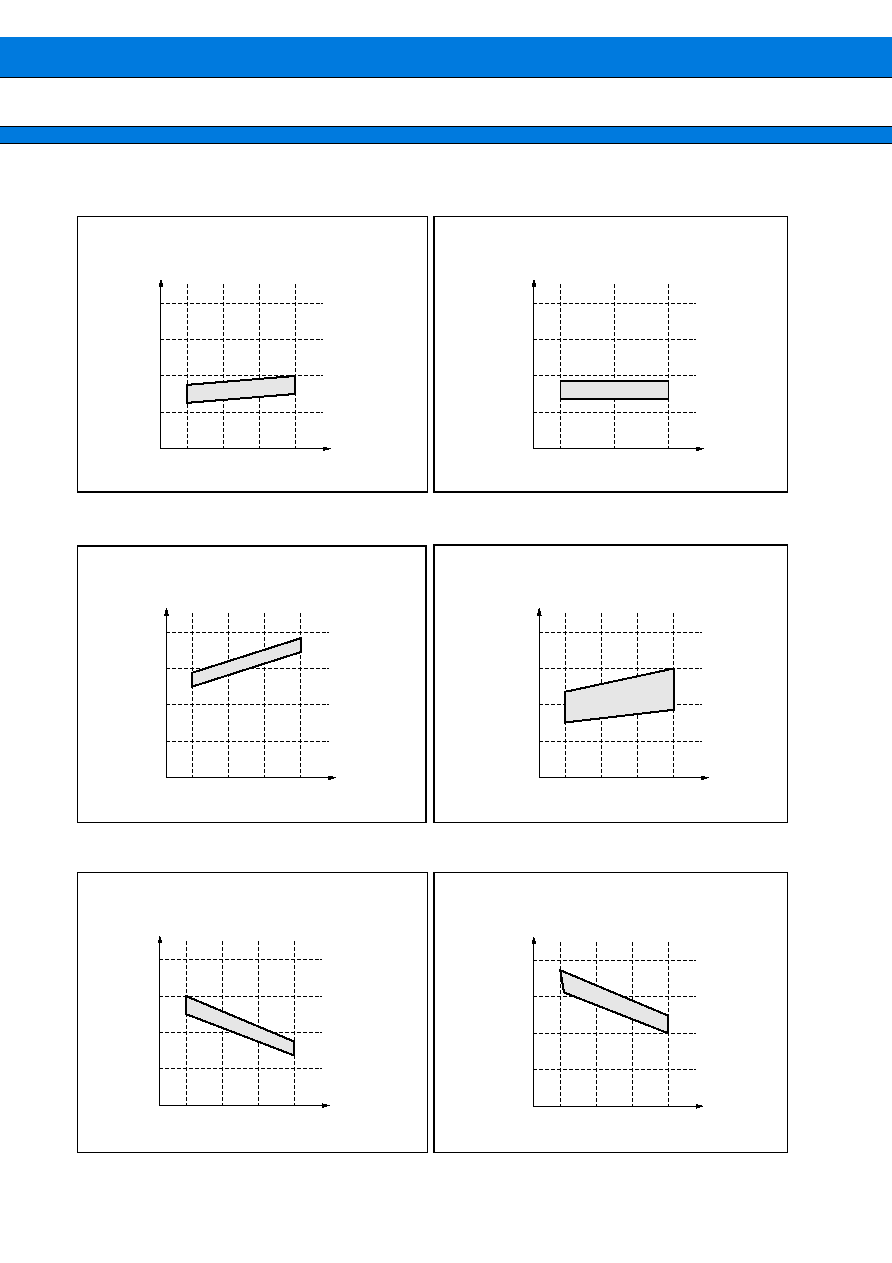

Precaution on using ports 6 and 7

If one of P60/A15 to P70/A24, which are shared for output of external bus interface addresses, is used as a port,

a grid voltage is applied to the port instantaneously when the status of another address output pin is changed.

Therefore, add resistors or capacitors to those ports to prevent application of the grid voltage.

V

CC

C

V

SS

0.1 F

3.3 V

2.4 k

7.6 k

GND

MB91307 Series

16

·

Clock control block

For L-level input to the INIT pin, allow for the regulator settling time or oscillation settling time.

·

Bit search module

The 0-detection, 1-detection, and transition-detection data registers (BSD0, BSD1, and BSDC) are only word-

accessible.

·

Prefetch

When accessing a prefetch-enabled little endian area, use word access only (access in 32 bits).

Byte or halfword access results in wrong data read.

·

Setting of external bus

The MB91307 series is guaranteed at an external bus frequency of 33 MHz. As the external bus is capable of

supporting 66 MHz for future enhancements, the initial value is the same rate as the base clock (determined by

the PLL setting) . The external bus is set to 66 MHz if you set the base clock to 66 MHz with the external-bus

base clock division setting register (DIVR1) containing the initial value. To change the base clock frequency, set

the external bus frequency not exceeding 33 MHz and set the new base clock frequency.

·

MCLK and SYSCLK

MCLK causes a stop in SLEEP/STOP mode while SYSCLK causes a stop only in STOP mode. Use either

depending on each application.

·

I

2

C input/output pin

The SDA and SCL pins of the MB91307 series are pseudo open-drain pins with the P-ch transistor turned off

to prevent the "H" level from being output. As the circuit configuration has a diode added to the V

CC

side, therefore,

the communication voltage must be adjusted to the 3.3-V power supply of this model (pulled up to a voltage of

3.3 V) .

·

Shared port function switching

To switch a pin that also serves as a port, use the port function register (PFR). Note, however, that bus pins are

switched depending on external bus settings.

·

Pull-up control

Connecting a pull-up resistor to the pin serving as an external bus pin cannot a guarantee the AC standard.

Even the port for which a pull-up resistor has been set is invalid in stop mode with HIZ = 1 or in hardware standby

mode.

·

I/O port access

Byte access only for access to port

·

Remarks for the external clock operation

When selecting the external clock, active X0 pin generally. Also simultaneously the opposite phase clock to X0

must be supplied to X1 pin. When using the clock along with STOP (oscillation stopped) mode, the X1 pin stops

when "H" is input in STOP mode. To prevent one output from competing against another, in this case, the stop

mode must not be used.

MB91307 Series

17

·

Low-power consumption modes

·

To enter the standby mode, use the synchronous standby mode (set with the SYNCS bit as bit 8 in the

TBCR, or time-base counter control register) and be sure to use the following sequence:

(LDI

#value_of_standby, R0)

(LDI

#_STCR, R12)

STB

R0, @R12

; Write to standby control register (STCR)

LDUB

@R12, R0

; Read STCR for synchronous standby

LDUB

@R12, R0

; Read STCR again for dummy read

NOP

; NOP x 5 for timing adjustment

NOP

NOP

NOP

NOP

Set the I-flag and the ILM and ICR registers to branch to an interrupt handler when the interrupt handler

triggers the microcontroller to return from the standby mode.

·

If you use the monitor debugger, follow the precautions below:

Do not set a breakpoint within the above array of instructions.

Do not single-step the above array of instructions.

·

Current at power-on (only for MB91V307R)

About 300 mA of power supply current flows when the power is turned on with INIT set to 0.

Set INIT to 1 to stop the overcurrent flowing. After that, the overcurrent will not flow even if INIT is set to 0.

·

Watchdog timer

The watchdog timer function of this model monitors that a program delays a reset within a certain period of time

and resets the CPU if the program fails to delay it, for example, because the program runs out of control. Once

the watchdog timer function is enabled, therefore, the watchdog timer countinues to operate until a reset takes

place.

An exception, for example during stop, sleep and DMA transfer modes, is the automatic delaying of a reset under

a condition in which the CPU stops program execution.

Note, however, that a watchdog reset may not occur in the above state caused when the system runs out of

control. If this is the case, use the external INIT pin to cause a reset (INIT).

MB91307 series

X0

X1

Using external clock (normal)

Note : Stop mode (oscillation stop mode) cannot be used.

MB91307 Series

18

·

Terminal and timing control register (TCR) (0x00000683)

The terminal and timing control register (TCR) is a write-only register. Therefore, do not access TCR with a bit

manipulation instruction.

If you intend to disable sharing of the bus by writing "0" to Bit 7 (BREN bit) of TCR when the bit is "1", be sure

to follow the procedure below. If the procedure is not followed, the device may hang up.

1. Write "0" to Bit 2 (BRQE bit) of the port 8 function register (PFR8).

2. Write "0" to Bit 7 (BREN bit) of TCR.

·

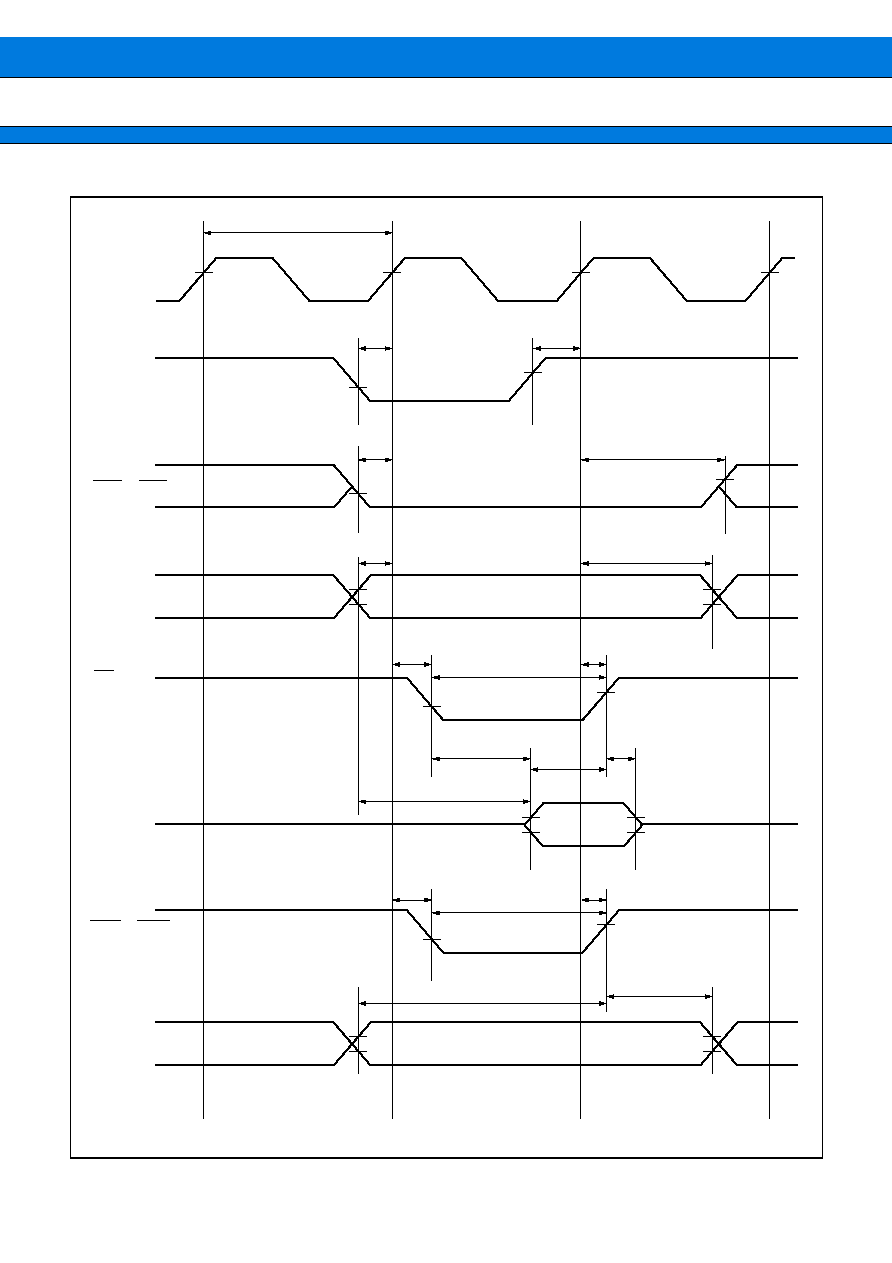

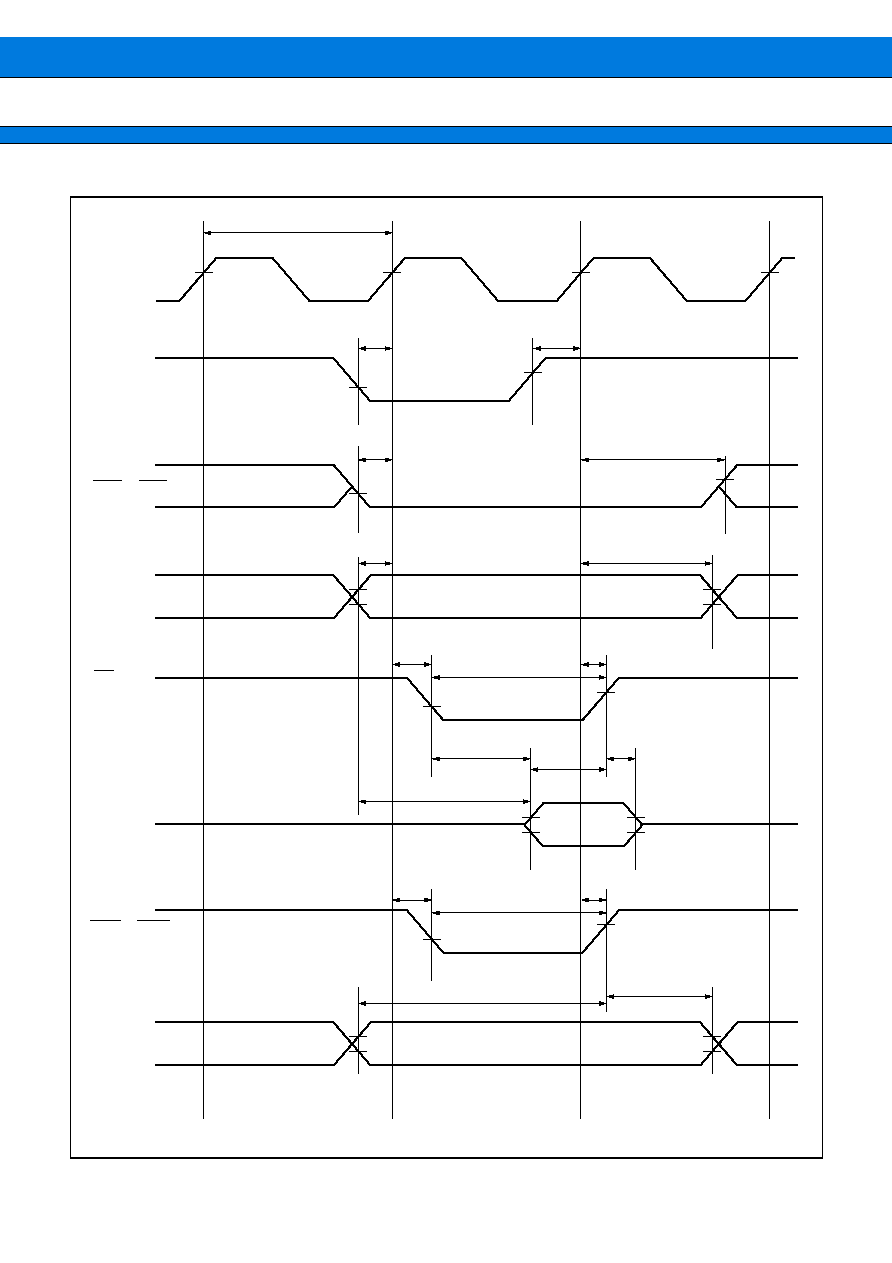

RD/WR

CS hold extension cycle

Assume that use of the RD/WR

CS hold extension cycle is specified (Bit 0 of AWR is 1) for an

area for which the normal memory/IO access type is set (the TYPE3 to TYPE0 bits of ACR are

0xxx). Even in this case, the hold extension cycle might not be inserted when the operation and

settings are specified in a specific combination.

The hold extension cycle will not be inserted when the following conditions are met:

· Use of the RD/WR

CS hold extension cycle is specified.

(Bit 0 [W00 bit] of AWR is 1.)

· A normal memory/IO access type is set for the area.

(Bits 3 to 0 [TYPE3 to TYPE0 bits] of ACR are 0xxx.)

Note: The MB91307 series allows only this type to be set.

· Disuse of the address

CS delay cycle is specified.

(Bit 2 [W02 bit] of AWR is 0.)

· A setting (recovery enabled) other than 0 cycle is made for the write recovery cycle.

(Bits 5 and 4 [W05 and W04 bits] of AWR are other than 00.)

(Example: First word writing to an external bus 16-bit area)

· If an access is made to write data larger than the bus width to the relevant area under the above conditions,

the RD/WR-CS hold extension cycle is not inserted in any cycle other than the last cycle to write divisions of

the data. Therefore, the hold time becomes insufficient.

Note : This problem does not occur in the read cycle.

To use this function, make either of the following settings:

· Specify the use of the address

CS delay cycle.

(Set 1 for Bit 2 [W02 bit] of AWR.)

· Specify 0 cycle for the write recovery cycle.

(Set 00 for Bits 5 and 4 [W05 and W04 bits] of AWR.)

·

Signed DIVIDE statement (DIVOS)

When the instruction immediately before the instruction of DIVOS is an instruction by which the memory access

is done, a correct calculation result might not be obtained.

This is generated under the following conditions.

· When the instruction performs memory accesses just before a DIVOS instruction.

Note : Instructions that performs relevant memory accesses (a total of 58 instructions)

ST Ri, @- R15

ST Rs, @- R15

ST PS, @- R15

STB Ri, @Rj

STB Ri, @ (R13, Rj)

DMOVB R13, @dir8

STB Ri, @ (R14, disp8)

LDUB @Rj, Ri

LD @ (R13, Rj), Ri

LDUH @ (R13, Rj), Ri

LDUB @ (R13, Rj), Ri

DMOV @dir10, R13

DMOVH @dir9, R13

DMOVB @dir8, R13

LD @ (R14, disp10), Ri

MB91307 Series

19

LDUH @ (R14, disp9), Ri

LDUB @ (R14, disp8), Ri

AND Rj, @Ri

ANDH Rj, @Ri

ANDB Rj, @Ri

ORB Rj, @Ri

EORB Rj, @Ri

DMOV @R13+, @dir10

DMOVH @R13+, @dir9

DMOVB @R13+, @dir8

DMOV @dir10, @R13+

DMOVH @dir9, @R13+

DMOVB @dir8, @R13+

DMOV @R15+, @dir10

DMOV @dir10, @- R15

· When full trace mode is specified as trace mode and the DIVOS and DIV1 instructions are not 4-byte aligned.

· Even if the DIVOS and DIV1 instructions are 4-byte aligned, perform a D-bus DMA transfer or specify the full

trace mode as trace mode if a breakpoint is set in the DIV1 instruction.

Avoid this notes as follows:

(1) Do not place an instruction that performs memory access before a DIVOS instruction.

(2) Do not perform a DMA transfer to the D-bus or set full trace mode as trace made when a DIVOS instruction

is specified.

To output the code for avoiding above (1) condition, specify "-@div0s 1" as the compiler option.

SOFTUNE compiler:

· In case of using the SOFTUNE V3: after the SOFTUNE compiler V30L07R07

· In case of using the SOFTUNE V5: after the SOFTUNE compiler V50L04

· In case of using the SOFTUNE V6: after the SOFTUNE compiler V60L01

·

DMA demand transfer

In sleep mode, demand transfer is executed only once and processing does not go further. During normal

operation, the efficiency of demand transfers may seem to be lowered.

This action occurs only in demand transfers (it does not occur in DREQ edge detection mode or the like).

This is occurred in the following cases:

· A demand transfer by DMAC is performed in sleep mode.

- After a demand transfer is performed once, processing does not go further although DREQ is input

successively.

- A subsequent transfer is started if the device is released from sleep mode and an external bus operation

other than a DMA transfer occurs.

· A demand transfer by DMAC is performed during normal operation.

- After a demand transfer is performed once, a subsequent transfer is not performed until an external bus

access other than a DMA transfer occurs.

- A demand transfer does not progress while there is no external bus access because cache hitting is

performed continuously or internal ROM operation continues.

· A subsequent demand transfer is not started even if an external bus access for prefetching occurs.

Avoid this notes as follows:

· Do not perform a demand transfer by DMAC in sleep mode.

· Do not use sleep mode during a demand transfer by DMAC.

MB91307 Series

20

·

RMW instructions using R15

If one of the instructions listed below is executed, the value of SSP or USP* is not used as the value of R15 and,

as a result, an incorrect value is written to memory. Therefore, the compiler does not generate the following

instructions:

AND

R15,@Rj ANDH

R15,@Rj ANDB

R15,@Rj

OR

R15,@Rj ORH

R15,@Rj ORB

R15,@Rj

EOR

R15,@Rj EORH

R15,@Rj EORB

R15,@Rj

XCHB

@Rj,R15

* : R15 is an insubstantial register. If R15 is accessed by a program, SSP or USP is accessed according to the

state of the S flag of the PS register.

Avoid this notes as follows:

· When programming any of the above 10 instructions by an assembler, specify a general-purpose register in

place of R15.

·

Executing instructions on RAM

· If instruction codes are placed in RAM, they should not be placed in the last 8 address bytes 0005 FFF8

H

to

0005 FFFF

H

. (Instruction code prohibited area)

·

Notes on the PS register

Since some instructions manipulate the PS register earlier, the following exceptions may cause the interrupt

handler to break or the PS flag to update its display setting when the debugger is being used. As the microcon-

troller is designed to carry out reprocessing correctly upon returning from such an EIT event, it performs oper-

ations before and after the EIT as specified in either case.

·

The following operations may be performed when the instruction immediately followed by a DIVOU/DIVOS

instruction is (a) halted by a user interrupt or NMI, (b) single-stepped, or (c) breaks in response to a data

event or emulator menu:

(1) D0 and D1 flags are updated earlier.

(2) The EIT handler (user interrupt/NMI or emulator) is executed.

(3) Upon returning from the EIT, the DIVOU/DIVOS instruction is executed and the D0 and D1 flags are

updated to the same values as those in (1) above.

·

The following operations are performed when the ORCCR/STILM/MOV Ri and PS instructions are executed

to enable interruptions when a user interrupt or NMI trigger event has occurred.

(1) The PS register is updated earlier.

(2) The EIT handler (user interrupt/NMI or emulator) is executed.

(3) Upon returning from the EIT, the above instructions are executed and the PS register is updated to the

same value as that in (1) above.

·

Notes on I-bus Memory

Do not access data in the instruction cache control register or the instruction cache RAM immediately before

the RETI instruction.

MB91307 Series

21

Unique to the evaluation chip MB91V307R

·

Simultaneous occurrences of a software break and a user interrupt/NMI

When a software break and a user interrupt /NMI take place at the same time, the emulator debugger can cause

the following phenomena:

·

The debugger stops pointing to a location other than the programmed breakpoints.

·

The halted program is not re-executed correctly.

If these phenomena occur, use a hardware break instead of the software break. If the monitor debugger has

been used, avoid setting any break at the relevant location.

·

Single-stepping the RETI instruction

If an interrupt occurs frequently during single stepping, execute only the relevant processing routine repeatedly

after single-stepping RETI. This will prevent the main routine and low-interrupt-level programs from being

executed. Do not single-step the RETI instruction for avoidance purposes. When the debugging of the relevant

interrupt routine becomes unnecessary, perform debugging with that interrupt disabled.

·

Break function

· If the address of a current system stack pointer or an area that includes a stack pointer is specified as an

object address of a hardware break (including an event break), a break occurs after one instruction is executed.

The break occurs although the relevant user program does not include an actual data access instruction. To

avoid this problem, do not set the (word) access to an area that includes the address of a system stack pointer

as a target of a hardware break (including an event break).

· If an instruction that causes a wait is executed between an instruction to read a branch destination address

from memory and a branch instruction, an instruction alignment error occurs at a point where an instruction

alignment error cannot occur originally. Then, an ICE break (CPU error break) occurs, and execution of

instructions stops. Furthermore, even if an instruction break is set for the branch destination address at the

point where the above error occurs, a break might not occur.

Example: LD

@R1,R0 ; read F-bus RAM

LD

@R2,R3 ; read F-bus RAM

CALL

@R0

; An incorrect alignment error may occur or a break might not occur.

To avoid the incorrect alignment error as described above, turn off the alignment error function in debugger

function setup.

To perform the instruction break correctly, do not specify use of a hardware break, but specify use of a software

break in debugger function setup.

·

Trace mode

If the trace mode for debugging is set to full trace mode, which uses internal FIFO memory as the output buffer,

the current may increase or DMA access to the D-bus may be lost.

This is occurred if:

· A DMA transfer to the D-bus or standby mode occurs in full trace mode.

Use internal trace mode to avoid this notes.

MB91307 Series

22

·

Alignment error (emulator debugger)

Assume that instruction alignment error break is enabled and an instruction that causes a wait is executed

between an instruction to read a branch destination address from memory and a branch instruction. Under these

conditions, an instruction alignment error occurs at a point where an instruction alignment error cannot occur

originally, an ICE break occurs, and execution of instructions stops. Then, a message indicating an unknown

break factor or a CPU error break is output.

Furthermore, even if an instruction break is set for the branch destination address at the point where the above

error occurs, a break might not occur.

This problem occurs if the following three types of instructions are executed successively:

(1) LD or DMOV instructions causing a wait (reading a branch destination address)

LD

@Rj,Ri

LDUH @Rj,RI

LD

@(R13,Rj)Ri

LDUH @(R13,Rj),Ri

LDUB @(R13,Rj),Ri

LD

@(R14,disp10),Ri LDUH @(R14,disp9),Ri LDUB @(R14,disp8),Ri

LD

@R15+,Ri LD

@R15+,Rs

LD

@R15+,PS

DMOV @dir10,R13

DMOVH @dir9,R13

DMOVB @dir8,R13

(2) Instructions causing a wait (reading F-bus RAM or external memory)

(3) Branch instructions such as JMP @Ri, JMP: D @Ri, CALL @Ri, CALL: D @Ri, RET, and RET: D

Example:

LD@R1,R0

;read F-bus RAM

LD@R2,R3

;read F-bus RAM

CALL @R0

Avoid this notes as follows:

Assume that instruction alignment error break is enabled and an instruction that causes a wait is executed

between an instruction to read a branch destination address from memory and a branch instruction. Under these

conditions, an instruction alignment error occurs at a point where an instruction alignment error cannot occur

originally, an ICE break occurs, and execution of instructions stops. Then, a message indicating an unknown

break factor or a CPU error break is output.

Furthermore, even if an instruction break is set for the branch destination address at the point where the above

error occurs, a break might not occur.

Avoid this problem as follows:

· To avoid the incorrect alignment error as described above, turn off the alignment error function in debugger

function setup.

· To perform the instruction break correctly, set the break point in an address other than the branch destination

address.

·

Operand break

A stack pointer placed in an area set for a DSU operand break can cause a malfunction. Do not apply a data

event break to access to the area containing the address of a system stack pointer.

MB91307 Series

23

BLOCK DIAGRAM

CPU Core

32

RAM*

32 16

Adapter

UART

3 channels

U-TIMER

3 channels

A/D

4 channels

I

2

C

1 channel

Bus Converter

Instruction

cache

1K bytes

DMAC

5 channels

32

32

16

Reload

timer

3 channels

Bit search

External

memory

interface

Clock control

Interrupt

controller

External

interrupt

Port

* : Internal RAM 128K bytes for MB91307R

64K bytes for MB91306R

MB91307 Series

24

CPU AND CONTROL BLOCK

Internal Architecture

The FR series CPU is a high-performance core using RISC architecture with a high-capability instruction set

intended for built-in applications.

1.

Features

· Uses of RISC Architecture

Basic instruction set: 1 instruction to 1 cycle.

· 32-bit architecture

General-purpose registers: 32-bits

×

16 registers

· 4G bytes linear memory space

· Built-in multipliers

32-bit

×

32-bit multiplication: 5 cycles

16-bit

×

16-bit multiplication: 3 cycles

· Enhanced interrupt processing

High-speed response (6 cycles)

Multiple interrupt support

Level masking functions (16 levels)

· Enhanced I/O operating instructions

Memory-to-memory transfer instructions

Bit processing instructions

· High code efficiency

Basic instruction length: 16 bits

· Low power consumption

Sleep mode, stop mode

· Gear function

MB91307 Series

25

2.

Internal Architecture

The FR series CPU uses a Harvard architecture with independent instruction bus and data bus. The instruction

bus (I-bus) is connected to an on-chip instruction cache. a 32-bit

16-bit bus converter is connected to the

bus (F-bus) to provide an interface between the CPU and peripheral resources. The Harvard

Princeton bus

converter is connected to the both the I-bus and D-bus as an interface between the CPU and bus controller.

FRex CPU

D-bus

Instruction

cache

I address

I data

D address

32

32

32

32

32

32

16

R-bus

X-bus

D data

F address

F data

RAM

32 bit

16 bit

Bus converter

Princeton

bus

converter

Harvard

Bus controller

Peripherals resource

I-bus

MB91307 Series

26

3.

Programming Model

·

Basic Programming Model

R0

R1

R12

R13

R14

R15

PC

PS

ILM

SCR

CCR

TBR

RP

SSP

USP

MDH

MDL

AC

FP

SP

XXXX XXXX

H

XXXX XXXX

H

0000 0000

H

32 bits

[Default values]

General-purpose register

Program counter

Program status

Table base register

Return pointer

System stack pointer

User stack pointer

Multiplier result registers

MB91307 Series

27

4.

Registers

·

General Purpose Register

Registers R 0 to R 15 are general-purpose registers. These registers can be used as accumulators for compu-

tation operations, or as pointers for memory access.

Of the 16 registers, enhanced commands are provided for the following registers to enable their use for particular

applications.

R13: Virtual accumulator

R14: Frame pointer

R15: Stack pointer

Default values at reset are undefined for R0 to R14. The value for R15 is 00000000

H

(SSP value).

·

PS (Program Status Register)

This register holds the program status, and is divided into three parts, ILM, SCR, and CCR.

All bits not defined in the diagram are reserved bits with read value "0" at all times. Write access to these bits

is not enabled.

·

CCR (Condition Code Register)

S : Stack flag, cleared to "0" at reset.

I : Interrupt flag, cleared to "0" at reset.

N : Negative flag, default value at reset undefined.

Z : Zero flag, default value at reset undefined.

V : Overflow flag, default value at reset undefined.

C : Carry flag, default value at reset undefined.

R0

R1

R12

R13

R14

R15

AC

FP

SP

XXXX XXXX

H

XXXX XXXX

H

0000 0000

H

32 bits

[Default values]

Bit position

PS Register

31

20

16

ILM

SCR

CCR

10

7

8

0

[Default value]

- - 00XXXX

B

CCR Register

7

6

5

4

3

2

1

0

S

I

N

Z

V

C

MB91307 Series

28

·

SCR (System Condition code Register)

Stepwise division flags

These flags store interim data during execution of stepwise division.

Step trace trap flag

Indicates whether the step trace trap is enabled or disabled.

The step trace trap function is used by emulators. When an emulator is in use, it cannot be used in execution

of user programs.

·

ILM(Interrupt Level Mask Register)

This register stores interrupt level mask values, for use in level masking.

The register is initialized to value 15 (01111

B

) at reset.

·

PC (Program Counte Registerr)

The program counter indicates the address of the instruction that is executing.

The default value at reset is undefined.

·

TBR (Table Base Register)

The table base register stores the starting address of the vector table used in EIT processing.

The default value at reset is 000FFC00

H

.

[Default value]

XX0

B

SCR Register

10

9

8

D1

D0

T

[Default value]

01111

B

ILM Register

20

19

18

17

16

ILM4 ILM3 ILM2 ILM1 ILM0

[Default value]

XXXXXXXX

H

PC Register

31

0

PC

[Default value]

000FFC00

H

TBR Register

31

0

TBR

MB91307 Series

29

·

RP (Return Pointer)

The return register stores the address for return from subroutines.

During execution of a CALL instruction, the PC value is transferred to this RP register.

During execution of a RET instruction, the contents of the RP register are transferred to this PC register.

The default value at reset is undefined.

·

SSP (System Stack Pointer)

The SSP register is the system stack pointer.

When the S flag is "0," this register functions as the R15 register.

The SSP register can also be explicitly specified.

This register is also used as a stack pointer to indicate the stack to which the PS and PC are removed when an

EIT occurs.

The default value at reset is 00000000

H

.

·

USP (User Stack Pointer)

The USP register is the user stack pointer.

When the S flag is "1," this register functions as the R15 register.

The USP register can also be explicitly specified.

The default value at reset is undefined.

This register cannot be used with RETI instructions.

·

Multiply & Divide registers

The multiply and divide registers are each 32 bits in length.

The default value at reset is undefined.

[Default value]

XXXXXXXX

H

RP Register

31

0

RP

[Default value]

00000000

H

SSP Register

31

0

SSP

[Default value]

XXXXXXXX

H

USP Register

31

0

USP

Multiply & Divide Registers

31

0

MDH

MDL

MB91307 Series

30

SETTING MODE

In the FR family, the mode pins (MD2, MD1, MD0) and the mode register (MODR) are used to set the operating

mode.

1.

Mode Pins

The three pins MD2, MD1, MD0 are used in mode vector fetch instructions, and also to make settings in test mode.

2.

Mode Register (MODR)

The mode data fetch instruction writes data to the address "0000 07FD

H

" called the mode data.

The area "0000 07FD

H

" is the mode register (MODR). When a setting is made to this register, the device will

operate the mode corresponding to that setting.

The mode register can only be set by a reset source at the INIT level. It is not possible to write to this register

from a user program.

Note : No data exists at the FR family mode register address (0000 07FF

H

).

[bit7 to bit3] Reserved bits

These bits should always be set to "00000." If set to any other value, stable operation is not assured.

[bit2] ROMA (Internal RAM enable bit)

This bit indicates whether internal RAM is enabled.

[bit1, 0] WTH1, WTH0 (Bus width indicator bits)

In external bus mode, these bits determine the bus width setting.

In external bus mode, the value of these bits sets the BW1, 0 bits in the AMD0 register (CS0 area).

Mode pin

Mode name

Reset vector access area

Remarks

MD2

MD1

MD0

0

0

1

External ROM mode vector

Outside

Bus width is set by mode register.

ROMA

Function

Remarks

0

External ROM mode

The built-in RAM area functions as external area.

1

Internal RAM mode

The built-in RAM area is enabled.

The 128K bytes built-in RAM can be used.

WTH1

WTH0

Bus width

0

0

8-bit

0

1

16-bit

1

0

Setting prohibited

1

1

Setting prohibited

<

Detailed register description >

MODR

Default

Address

0000 07FD

H

XXXXXXXX

B

7

6

5

4

3

2

1

0

0

0

0

0

0

ROMA

WTH1

WTH0

Operating mode setting bits

MB91307 Series

31

MEMORY SPACE

1.

Memory Space

The FR family has 4G bytes (2

32

addresses) of logical address space with linear access from the CPU.

·

Direct Addressing Areas

The following areas of address space are used for I/O operations.

These areas are called direct addressing areas, in which the address of an operand can be specified directly

during an instruction.

The direct areas differ according to the size of the data accessed, as follows.

2.

Memory Map

The following diagram illustrates memory space in the FR family.

byte data access

: 000

H

to 0FF

H

half word data access : 000

H

to 1FF

H

word data access

: 000

H

to 3FF

H

0000 0000

H

0000 0400

H

0001 0000

H

0004 0000

H

0006 0000

H

0010 0000

H

FFFF FFFF

H

0000 0000

H

0000 0400

H

0001 0000

H

0004 0000

H

0006 0000

H

0010 0000

H

I/O

I/O

I/O

I/O

I/O

I/O

0005 0000

H

Direct addressing

area

Refer to I/O map

Access

prohibited

Internal RAM

128K bytes

Access

prohibited

External area

Access

prohibited

External area

Access

prohibited

Internal RAM

128K bytes

Access

prohibited

External area

Internal ROM

external bus mode

External bus mode

MB91307R

External area

MB91306R

MB91306R/MB91307R

Internal ROM

external bus mode

MB91307 Series

32

·

Use of Built-in RAM

The MB91307R contains 128K bytes of internal RAM, and MB91306R contains 64K bytes of internal RAM. To

enable use of this RAM, the mode register must be set to internal ROM external bus mode (ROMA=1).

Precautions for use of this model

· The reset vector is fixed at 000F FFFC

H

.

· For the MB91307R, the 128K bytes RAM area is from 0004 0000

H

to 0005 FFFF

H

and for the MB91306R, the

64K bytes RAM area is from 0004 0000

H

to 0004 FFFF

H

. The area from 0006 0000

H

to 000F FFFF

H

is access

prohibited.

· In order to use RAM the mode register must be set to internal ROM external bus mode.

· In internal ROM external bus mode the built-in RAM area can be used, but the vector area 000F FFXX

H

is an

internal area and cannot be accessed externally. Please refer to the following explanation.

· When placing instruction code in RAM, nothing should be placed in the last 8 bytes of the area 0005 FFF8

H

to 0005 FFFF

H

. (This is an instruction code prohibited area.)

0000 0000

H

0000 0400

H

0001 0000

H

0004 0000

H

0006 0000

H

0010 0000

H

FFFF FFFF

H

I/O

I/O

I/O

I/O

I/O

I/O

0005 0000

H

Direct addressing

area

Refer to I/O map

Access

prohibited

External area

Access

prohibited

External area

After reset release

After mode setting

Internal ROM external bus mode

Internal RAM

128K bytes

Access

prohibited

External area

External area

After mode register setting the vector area is an internal area. Therefore before writing to the mode register

it is necessary to rewrite the TBR register so that the vector area is changed to an external area.

External area

Access

prohibited

Access

prohibited

Internal RAM

64K bytes

: The shaded portion is an internal area.

MB91307 Series

33

USER PROGRAM INITIALIZATION

The following sequence describes an example using built-in RAM.

For the MB91306R, only the internal RAM area is different but the setting is same.

1.

Hardware Setting Conditions

2.

Immediately After Reset Release

1) Assume that 1M bytes of external ROM is placed beginning at 0010 0000

H

. Place the program at this location

in the linker. (The following description can apply to other addresses than this one as well.)

2) Connect addresses A19 to A1 (1M bytes) to ROM, other addresses will use CS0.

3) Set the mode pins (MD2, MD1, MD0) to external vectors.

4) Write the reset vector to 001F FFFC

H

. Likewise write the mode vector to 001F FFF8

H

.

1)

After reset release, the CPU will attempt to load a mode vector from 000F FFF8

H

, a reset vector from 000F

FFFC

H

, however because this will be an external vector, the CPU will have to go externally. However the

CS0 default value causes 1M bytes of external ROM to be repeated in external space, so that the mode

vector and the reset vector itself will load the contents written at 001F FFF8

H

and 001F FFFC

H

in external

ROM.

2) The branch destination is set in the linker to an address in the area 001X XXXX

H

, so that subsequent pro-

gram execution will be in this area.

CS0

External

ROM

A19 to A1

MB91307 series

CS0

External

ROM

External

ROM

0000 0000

H

0004 0000

H

FFFF FFFF

H

MB91307 series

1M bytes of ROM can

be viewed again on the

address map.

MB91307 Series

34

3.

User Program Initialization Steps

1) Set the TBR register so that the interrupt table is 001F FFXX

H

, then perform initialization. This process also

includes a chip select setting, and at the same time the CS0 address is set to be valid at 001X XXXX

H

. The

CS0 decoding result is the same before and after the setting, so that the CPU can continue to run programs

on external ROM.

2) If necessary, initialize the contents of RAM.

3) Now initialization is complete, and the application program can be executed.

CS0

External

ROM

External

ROM

0000 0000

H

0004 0000

H

0010 0000

H

001F FFFF

H

FFFF FFFF

H

MB91307 series

1M bytes of ROM space

matches 1M bytes of the

address map.

MB91307 Series

35

I/O MAP

This map shows the correlation between areas of memory space and individual registers in peripheral resources.

[How to read the map]

Note: Default register bit values are indicated as follows:

"1" : Default value "1"

"0" : Default value "0"

"X" : Default value "X"

"-"

: No physical register at this location

Address

Register

Block

+

0

+

1

+

2

+

3

000000

H

PDR0 [R/W]

PDR1 [R/W]

PDR2 [R/W]

PDR3 [R/W]

T-unit

Port Data Register

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

Read/write attributes

Register default value after reset

Register name

(1-column registers at address 4n, 2-column registers at address 4n + 2

...

)

Left most register address

(for word access, the first column of the register contains the MSB end of the data)

MB91307 Series

36

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000000

H

PDR2 [R/W]

T-unit

Port Data Register

XXXXXXXX

000004

H

PDR6 [R/W]

PDR7 [R/W]

XXXXXXXX

-------X

000008

H

PDR8 [R/W]

PDR9 [R/W]

PDRA [R/W]

PDRB [R/W]

--X--XXX

XXXXXXX-

XXXXXXXX

XXXXXXXX

00000C

H

000010

H

PDRG [R/W]

PDRH [R/W]

PDRI [R/W]

PDRJ [R/W]

R-bus

Port Data Register

-----XXX

XXX00XXX

---XXXXX

XXXXXXXX

000018

H

to

00001C

H

000020

H

to

00003C

H

Reserved

000040

H

EIRR [R/W]

ENIR [R/W]

ELVR [R/W]

Ext int

00000000

00000000

00000000

000044

H

DICR [R/W]

HRCL [R/W]

DLYI/I-unit

-------0

0--11111

000048

H

TMRLR [W]

TMR [R]

Reload Timer 0

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

00004C

H

TMCSR [R/W]

----0000 00000000

000050

H

TMRLR [W]

TMR [R]

Reload Timer 1

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000054

H

TMCSR [R/W]

----0000 00000000

000058

H

TMRLR [W]

TMR [R]

Reload Timer 2

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

00005C

H

TMCSR [R/W]

----0000 00000000

000060

H

SSR [R/W]

SIDR [R/W]

SCR [R/W]

SMR [R/W]

UART0

00001-00

XXXXXXXX

00000100

00--0-0-

000064

H

UTIM [R] (UTIMR [W] )

DRCL [W]

UTIMC [R/W]

U-TIMER 0

00000000 00000000

--------

0--00001

000068

H

SSR [R/W]

SIDR [R/W]

SCR [R/W]

SMR [R/W]

UART1

00001-00

XXXXXXXX

00000100

00--0-0-

MB91307 Series

37

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

00006C

H

UTIM [R] (UTIMR [W] )

DRCL [W]

UTIMC [R/W]

U-TIMER 1

00000000 00000000

--------

0--00001

000070

H

SSR [R/W]

SIDR [R/W]

SCR [R/W]

SMR [R/W]

UART2

00001-00

XXXXXXXX

00000100

00--0-0-

000074

H

UTIM [R] (UTIMR [W] )

DRCL [W]

UTIMC [R/W]

U-TIMER 2

00000000 00000000

--------

0--00001

000078

H

ADCR

[R]

ADCS

[R/W]

A/D Converter

sequential comparator

------XX XXXXXXXX

00000000 00000000

00007C

H

Reserved

000080

H

Reserved

000084

H

Reserved

000088

H

Reserved

00008C

H

Reserved

000090

H

Reserved

000094

H

IBCR [R/W]

IBSR [R/W]

ITBA [R/W]

I

2

C interface

00000000

00000000

------00 00000000

000098

H

ITMK [R/W]

ISMK [R/W]

ISBA [R/W]

00----11 11111111

01111111

00000000

00009C

H

IDAR [R/W]

ICCR [R/W]

IDBL [R/W]

00000000

0-011111

-------0

0000A0

H

Reserved

0000A4

H

Reserved

0000A8

H

Reserved

0000AC

H

Reserved

0000B0

H

Reserved

MB91307 Series

38

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000200

H

DMACA0 [R/W]

DMAC

00000000 0000XXXX XXXXXXXX XXXXXXXX

000204

H

DMACB4 [R/W]

00000000 00000000 00000000 00000000

000208

H

DMACA1 [R/W]

00000000 0000XXXX XXXXXXXX XXXXXXXX

00020C

H

DMACB4 [R/W]

00000000 00000000 00000000 00000000

000210

H

DMACA2 [R/W]

00000000 0000XXXX XXXXXXXX XXXXXXXX

000214

H

DMACB4 [R/W]

00000000 00000000 00000000 00000000

000218

H

DMACA3 [R/W]

00000000 0000XXXX XXXXXXXX XXXXXXXX

00021C

H

DMACB4 [R/W]

00000000 00000000 00000000 00000000

000220

H

DMACA4 [R/W]

00000000 0000XXXX XXXXXXXX XXXXXXXX

000224

H

DMACB4 [R/W]

00000000 00000000 00000000 00000000

000228

H

00022C

H

to

00023C

H

Reserved

000240

H

DMACR [R/W]

DMAC

0XX00000 XXXXXXXX XXXXXXXX XXXXXXXX

000244

H

to

000274

H

Reserved

000278

H

Reserved

00027C

H

Reserved

000280

H

to

0002FC

H

Reserved

MB91307 Series

39

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000300

H

Reserved

000304

H

ISIZE [R/W]

Instruction Cache

------00

000308

H

to

0003E0

H

Reserved

0003E4

H

ICHRC [R/W]

Instruction Cache

0 - 000000

0003E8

H

to

0003EC

H

Reserved

0003F0

H

BSD0 [W]

Bit Search Module

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

0003F4

H

BSD1 [R/W]

XXXXXXXX XXXXXXXX XXXXXXXX XXXXXXXX

0003F8

H

BSDC [W]