DS07-16307-3E

FUJITSU SEMICONDUCTOR

DATA SHEET

32-Bit RISC Microcontroller

CMOS

FR Family MB91110 Series

MB91110/MB91V110

s

s

s

s

DESCRIPTION

The MB91110 series is a standard single-chip micro controller featuring various I/O resources and bus control

mechanisms to incorporate the control with required for high performance high-speed CPU processes, having a

32-bit RISC CPU (FR30 series) in its core. Although external bus access is the basis for supporting a large address

space accessible by a 32-bit CPU, a 1-KB instruction cache memory has been built-in to increase the instruction/

execution speed of the CPU.

This unit features the optimal specifications for incorporating applications that require high performance CPU

processing power such as navigation systems, high performance facsimile systems, printer control, etc.

s

s

s

s

FEATURES

FR30CPU

· 32-bit RISC, load / store architecture, 5-level pipeline

· Operating frequency : external 25 MHz, internal 50 MHz

· Multi-purpose register : 32 bits

×

16

· 16-bit fixed length instructions (basic instruction) , 1 instruction per cycle

· Instructions for barrel shift, bit processing and inter memory transfers : Instructions suited to loading purposes

(Continued)

s

s

s

s

PACKAGE

144-pin plastic LQFP

(FPT-144P-M08)

MB91110 Series

2

(Continued)

· Function entry / exit instruction, multi load / store instruction of register details : Instruction capable of handling

High level language instruction.

· Register Interlock function : Simplification of assembler description

· Branch instruction with delay slot : Reduction in overheads in case of branching

· Multiplier is built-in / Supported at instruction level

Signed 32-bit multiplication : 5 cycles

Signed 16-bit multiplication : 3 cycles

· Interruption (saving PC and PS) : 6 cycles, 16 priority levels

Bus Interface

· 24-bit address bus (16 MB space)

· Operating frequency : 25 MHz

· 16- / 8-bit data bus

· Basic external bus cycle : 2 clock cycles

· Chip select output that can be set to a minimum 64-Kbyte units

· Interface support for various memories

DRAM interface (areas 4, 5)

· Automatic waiting cycle : Can be randomly set from 0 to 7 cycles per area

· Unused data and address pins can be used as input/output ports.

· Supports "little endian" mode (One area is selected from areas 1 to 5)

DRAM Interface

· 2-bank individual control (area 4, 5)

· Normal mode / high speed page mode

· Basic bus cycles : normally 5 cycles, 1 cycle access is possible in high-speed page mode.

· Programmable waveform : 1 cycle waiting can be inserted automatically in RAS and CAS.

· DRAM refresh

CBR refresh (Interval is randomly set using the 6-bit timer.)

Self refresh mode

· Supports addresses for 8, 9, 10 and 12 columns

· 2CAS/1WE or 2WE/1CAS can be selected.

Cache Memory

· 1 KB instruction cache

· 2 way set associative

· 32 blocks / way, 4 entries (4 words) / block

· Lock function : Residing in the specified program codes at cache

DMA Controller (DMAC)

· 5 channels

· External

external 2.5 access cycles / transfer (if 2 clock cycles are defined as 1 access cycle)

· Internal

external 1.5 access cycles / transfer (if 2 clock cycles are defined as 1 access cycle)

· Address register (inc, dec, or reload are possible) : 32 bits

×

5 channels

· Transfer count register (reload possible) : 16 bits

×

5 channels

· Transfer factors : external pin / built-in resources interruption request / software

· Transfer sequence

Step transfer / block transfer

Burst / consecutive transfer

· Transfer data length : 8-bit, 16-bit or 32-bit can be selected

· Suspension is possible using NMI / interruption request

MB91110 Series

3

UART

· Fully duplicated double buffer

· Data length : 7 to 9 bits (without parity) , 6 to 8 bits (with parity)

· Asynchronous (start-stop synchronization) or CLK synchronized communication can be selected.

· Multiprocessor mode

· Dedicated baud rate generator is built-in.

· External clock can be used as the transfer clock

· Baud rate clock can be output

· Error detection : parity, frame, overrun

PPG Timer

· 16 bits, 6 channels (frequency setting register / duty setting register)

· PWM function or one-shot function can be selected

· Initiation : Software or external trigger can be selected

A/D Converter (sequential conversion type)

· 10-bit resolution, 8 channels

· Sequential comparison conversion : 5.6

µ

s in the case of 25 MHz

· Sample & hold circuit is built-in.

· Conversion mode : Single, scan or repeat conversion can be selected.

· Initiation : Software, external trigger or built-in timer can be selected.

Reloading Timer

· 16-bit timer : 2 channels

· Internal clock : 2 clock cycle resolutions, 2, 8 or 32 cycles can be selected.

· Pin input : event counter input / gate function

· Rectangular wave output

Other Interval Timer

· Watchdog timer : 1 channel

Bit Search Module

· Searches the first "1" / "0" change bit positions within 1 cycle from MSB in 1 word.

Interruption Controller

· External interruption input : Mask impossible interruption (NMI) , normal interruption

×

8 (INT0 to INT7)

· Internal interruption factors : UART, DMAC, A/D, reloading timer, PPG timer, delay interruption

· Priority levels are programmable except for mask impossible interruption (16 levels)

Reset Factors

· Power-on reset / hardware standby / watchdog timer / software reset / external reset

Low Power Consumption Mode

· Sleep / stop mode

Clock Control

· Gear functions : Operating clock frequencies peripheral to the CPU can be set randomly and independently.

Gear locks can be selected from 1/1, 1/2, 1/4 or 1/8 (or 1/2, 1/4, 1/8, or 1/16) .

Others

· Package : LQFP-144

· CMOS technology : 0.35

µ

m

· Power : 5.0 V

±

10

%

, 3.3 V

±

5

%

MB91110 Series

4

s

s

s

s

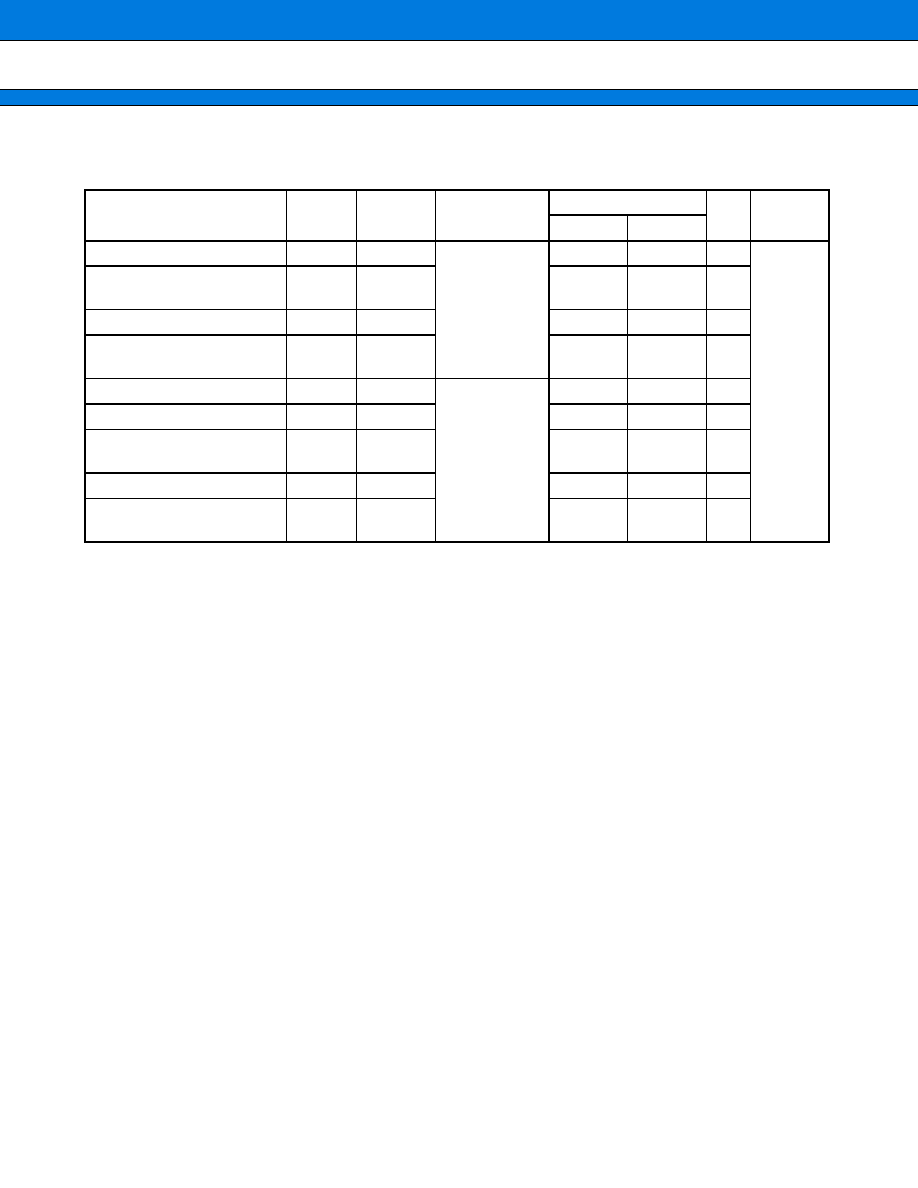

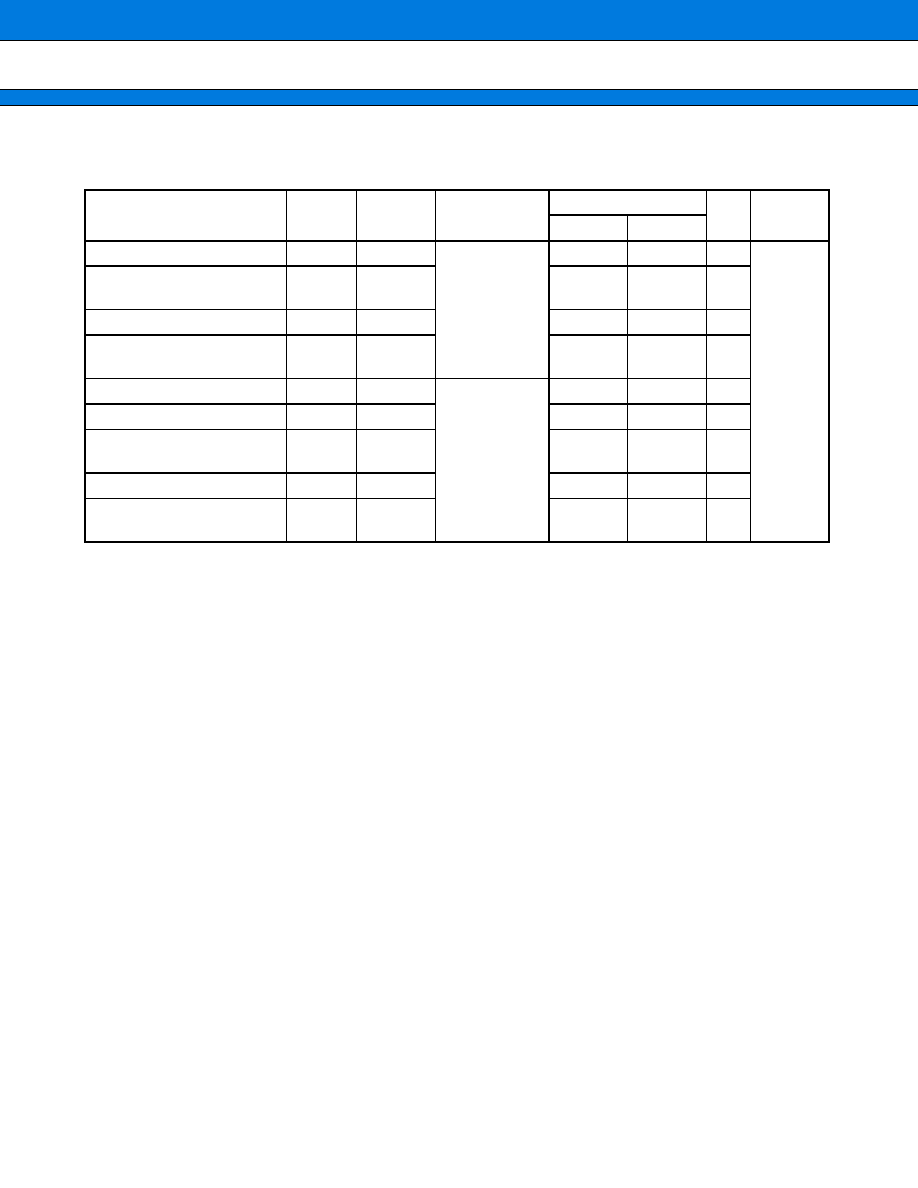

PRODUCT LINEUP

MB91V110

(For evaluation)

MB91110

(I-RAM mounted version)

I-RAM

16 Kbyte

16 Kbyte

RAM

5 Kbyte

5 Kbyte

ROM

I-$

1 Kbyte

1 Kbyte

DSU3

evaluation function

Mounted

MB91110 Series

5

s

s

s

s

PIN ASSIGNMENT

(TOP VIEW)

(FPT-144P-M08)

PE3/TRG2, 5

PF0/INT0

PF1/INT1

PF2/INT2

PF3/INT3

PF4/INT4

PF5/INT5

PF6/INT6

PF7/INT7

V

SS

PG0/DREQ0

PG1/DACK0

PG2/DEOP0

PG3/DREQ1

PG4/DACK1

PG5/DEOP1

V

CC

5

V

CC

3

PH0/DREQ2

PH1/DACK2

PH2/DEOP2

PH3/SI

PH4/SO

PH5/SCK

PH6/TI0

PH7/TO0

V

SS

PI0/TI1

PI1/TO1

PI2/PPG0

PI3/PPG1

PI4/PPG2

PI5/PPG3

PI6/PPG4

PI7/PPG5

V

SS

NMI

DW1/PB7

CS1H/PB6

CS1L/PB5

RAS1/PB4

V

SS

V

CC

5

DW0/PB3

CS0H/PB2

CS0L/PB1

RAS0/PB0

CLK/PA6

CS5/PA5

CS4/PA4

CS3/PA3

CS2/PA2

CS1/PA1

CS0

V

SS

WR1/P85

WR0

RD

BRQ/P82

BGRNT/P81

RDY/P80

V

CC

3

V

CC

5

A23/P67

A22/P66

A21/P65

A20/P64

A19/P63

A18/P62

A17/P61

A16/P60

V

SS

110

115

120

125

130

135

140

TRG1, 4/PE2

TRG0, 3/PE1

ATG/PE0

V

SS

V

CC

5

AN7

AN6

AN5

AN4

AN3

AN2

AN1

AN0

AV

SS

AVRL

AVRH

AV

CC

(OPEN)

(OPEN)

(OPEN)

(OPEN)

(OPEN)

(OPEN)

(OPEN)

(OPEN)

(OPEN)

V

CC

3

HST

RST

V

SS

X1

X0

V

CC

5

MD2

MD1

MD0

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

V

SS

D24

D25

D26

D27

D28

D29

D30

D31

V

CC

5

V

SS

A00

A01

A02

A03

A04

A05

A06

A07

V

SS

A08

A09

A10

A11

A12

A13

A14

A15

1

5

10

15

20

25

30

35

105

100

95

90

85

80

75

70

65

60

55

50

45

40

INDEX

MB91110 Series

6

s

s

s

s

PIN DESCRIPTIONS

(Continued)

Pin no.

Pin name

I/O*

Circuit type

Function

1

2

3

4

5

6

7

8

D16/P20

D17/P21

D18/P22

D19/P23

D20/P24

D21/P25

D22/P26

D23/P27

I/O

C

These pins use bits 16 to 23 of the external data bus.

They can be used as a port (P20 to P27) if the external bus

width is 8 bits.

10

11

12

13

14

15

16

17

D24

D25

D26

D27

D28

D29

D30

D31

I/O

C

These pins use bits 24 to 31 of the external data bus.

20

21

22

23

24

25

26

27

A00

A01

A02

A03

A04

A05

A06

A07

I/O

C

These pins use bits 00 to 07 of the external address bus.

29

30

31

32

33

34

35

36

A08

A09

A10

A11

A12

A13

A14

A15

I/O

C

These pins use bits 08 to 15 of the external address bus.

38

39

40

41

42

43

44

45

A16/P60

A17/P61

A18/P62

A19/P63

A20/P64

A21/P65

A22/P66

A23/P67

I/O

C

These pins use bits 16 to 23 of the external address bus.

48

RDY/P80

I/O

C

This is for external ready input. "0" is input if the bus cycle be-

ing executed is incomplete. It can be used as a port when not

otherwise used.

49

BGRNT/P81

I/O

H

This is the external bus open reception output. "L" is output if

the external bus is opened. It can be used as a port when not

otherwise used.

MB91110 Series

7

(Continued)

Pin no.

Pin name

I/O*

Circuit type

Function

50

BRQ/P82

I/O

C

This is the external bus open request input. "1" is input if the

external bus is to be opened. It can be used as a port when

not otherwise used.

51

RD

O

G

This is the external bus read strobe.

52

WR0

O

G

This is the external bus write strobe.

53

WR1/P85

I/O

H

55

CS0

O

G

Chip select 0 output (Low active)

56

57

58

59

60

CS1/PA1

CS2/PA2

CS3/PA3

CS4/PA4

CS5/PA5

I/O

H

Chip select 1 output (Low active)

Chip select 2 output (Low active)

Chip select 3 output (Low active)

Chip select 4 output (Low active)

Chip select 5 output (Low active)

They can be used as ports when not otherwise used.

61

CLK/PA6

I/O

H

This is the system clock output. The same clock as the stan-

dard clock is output. This can be used as a port when not oth-

erwise used.

62

63

64

65

68

69

70

71

RAS0/PB0

CS0L/PB1

CS0H/PB2

DW0/PB3

RAS1/PB4

CS1L/PB5

CS1H/PB6

DW1/PB7

I/O

H

RAS output with DRAM bank 0.

CASL output with DRAM bank 0.

CASH output with DRAM bank 0.

WE output with DRAM bank 0. (Low active)

RAS output with DRAM bank 1.

CASL output with DRAM bank 1.

CASH output with DRAM bank 1.

WE output with DRAM bank 1. (Low active)

They can be used as ports when not otherwise used.

72

NMI

I

E

Non Maskable Interrupt (NMI) input. (Low active)

73

74

75

MD0

MD1

MD2

I

I

These are mode pins from 0 to 2.

Basic MCU operation modes are set using these pins.

They should be connected directly to V

CC

or V

SS

for use.

77

78

X0

X1

I

O

A

Clock (oscillation) input.

Clock (oscillation) output.

80

RST

I

B

This is the external reset input. (Low active)

81

HST

I

E

This is the hardware standby input. (Low active)

83

(OPEN)

Set this to OPEN.

84

85

86

(OPEN)

(OPEN)

(OPEN)

Set this to OPEN.

16-bit bus width

8-bit bus width

D31-24

WR0

WR0

D23-16

WR1

(Port is possible)

MB91110 Series

8

(Continued)

Pin no.

Pin name

I/O*

Circuit type

Function

87

88

89

90

(OPEN)

(OPEN)

(OPEN)

(OPEN)

Set this to OPEN.

91

(OPEN)

Set this to OPEN.

92

AV

CC

V

CC

power supply for the A/D converter.

93

AVRH

A/D converter reference voltage (high potential side).

Be sure to turn on/off this pin with potential higher than AVRH

applied to V

CC

.

94

AVRL

A/D converter reference voltage (low potential side).

95

AV

SS

V

SS

power supply for the A/D converter.

96

97

98

99

100

101

102

103

AN0

AN1

AN2

AN3

AN4

AN5

AN6

AN7

I

D

[AN0 to 7] A/D converter analog input.

106

ATG/PE0

I/O

H

[ATG] This is the external trigger input for the A/D converter.

This function is always used if selected as the initiation factor

for A/D, so output by other functions should be stopped ex-

cept when it is carried out intentionally.

[PE0] This is a general-purpose input/output port.

107

108

109

TRG0, 3/PE1

TRG1, 4/PE2

TRG2, 5/PE3

I/O

H

[TRG0 to 5] These are external trigger input pins of the PPG.

[PE1 to 3] These are general-purpose input/output ports.

110

111

112

113

114

115

116

117

INT0/PF0

INT1/PF1

INT2/PF2

INT3/PF3

INT4/PF4

INT5/PF5

INT6/PF6

INT7/PF7

I/O

F

[INT0 to 7] These are external interruption request inputs.

This input is always used while the corresponding external

interruption is permitted, so output using other functions

should be stopped except when carried out intentionally.

[PF0 to 7] These are general-purpose input/output ports.

119

DREQ0/PG0

I/O

H

[DREQ0] This is the DMA external transfer request input (ch

0) . This input is always used if selected as the transfer factor

for DMAC, so outputs from other functions should be

stopped except when carried out intentionally.

[PG0] This is a multi-purpose input/output port.

MB91110 Series

9

(Continued)

Pin no.

Pin name

I/O*

Circuit type

Function

120

DACK0/PG1

I/O

C

[DACK0] This is the DMAC external transfer request recep-

tion output (ch 0) . This function is effective if the transfer re-

quest reception output specification of DMAC is permitted.

[PG1] This is a multi-purpose input/output port. This function

is effective if the transfer request reception output specifica-

tion of DMAC is prohibited.

121

DEOP0/PG2

I/O

C

[DEOP0] This is the DMA transfer end signal output (ch 0) .

This function is effective if the transfer end signal output

specification of DMAC is permitted.

[PG2] This is a multi-purpose input/output port. This function

is effective if the transfer end signal output specification of

DMAC is prohibited.

122

DREQ1/PG3

I/O

H

[DREQ1] This is the DMA external transfer request input (ch

1) . This input is always used if selected as the transfer factor

of DMAC, so output using other functions should be stopped

except when carried out intentionally.

[PG3] This is a multi-purpose input/output port.

123

DACK1/PG4

I/O

C

[DACK1] This is the DMAC external transfer request recep-

tion output (ch 1) . This function is effective if the transfer re-

quest reception output specification of DMAC is permitted.

[PG4] This is a multi-purpose input/output port. This function

is effective if the transfer request reception output specifica-

tion of DMAC is prohibited.

124

DEOP1/PG5

I/O

C

[DEOP1] This is the DMA transfer end signal output (ch 1) .

This function is effective if the transfer end signal output

specification of DMAC is permitted.

[PG5] This is a multi-purpose input/output port. This function

is effective if the transfer end signal output specification of

DMAC is prohibited.

127

DREQ2/PH0

I/O

H

[DREQ2] This is the DMA external transfer request input (ch

2) . This input is always used if selected as the transfer factor

of DMAC, so output using other functions should be stopped

except when carried out intentionally.

[PH0] This is a multi-purpose input/output port.

128

DACK2/PH1

I/O

C

[DACK2] This is the DMAC external transfer request recep-

tion output (ch 2) . This function is effective if the transfer re-

quest reception output specification of DMAC is permitted.

[PH1] This is a multi-purpose input/output port. This function

is effective if the transfer request reception output specifica-

tion of DMAC is prohibited.

MB91110 Series

10

(Continued)

Pin no.

Pin name

I/O*

Circuit type

Function

129

DEOP2/PH2

I/O

C

[DEOP2] This is the DMA transfer end signal output (ch 2) .

This function is effective if the transfer end signal output

specification of DMAC is permitted.

[PH2] This is a multi-purpose input/output port. This function

is effective if the transfer end signal output specification of

DMAC is prohibited.

130

SI/PH3

I/O

H

[SI] This is UART data input. This input is always used while

UART inputs, so outputs from other functions should be

stopped except when carried out intentionally.

[PH3] This is a general-purpose input/output port.

131

SO/PH4

I/O

C

[SO] This is UART data output. This function is effective

when UART data output specification is permitted.

[PH4] This is a general-purpose input/output port. This func-

tion is effective when UART data output specification is pro-

hibited.

132

SCK/PH5

I/O

H

[SCK] This is UART clock input/output. Clock output is effec-

tive when UART clock output specification is permitted.

[PH5] This is a general-purpose input/output port. This func-

tion is effective when UART clock output specification is pro-

hibited.

133

TI0/PH6

I/O

H

[TI0] This is reload timer 0 input. It is always used when re-

load timer input is permitted, so outputs from other functions

should be stopped except when carried out intentionally.

[PH6] This is a general-purpose input/output port.

134

TO0/PH7

I/O

C

[TO0] This is reload timer 0 Output. This function is effective

when reload timer specification is permitted.

[PH7] This is a general-purpose input/output port. This func-

tion is effective when reload timer specification is prohibited.

136

TI1/PI0

I/O

H

[TI1] This is reload timer 1 input. It is always used when re-

load timer input is permitted, so outputs from other functions

should be stopped except when carried out intentionally.

[PI0] This is a general-purpose input/output port.

137

TO1/PI1

I/O

C

[T01] This is the reload timer 1 output. This function is effec-

tive if the output specification of the reload timer is permitted.

[PI1] This is a multi-purpose input/output port. This function

is effective if the output specification of the reload timer is

prohibited.

MB91110 Series

11

(Continued)

* : I/O shown above indicates input/output classification.

Note : The I/O port and resource input/outputs for most of the above pins are multiplexed, i.e. Pxx/xxxx. In the event

of both the port and resource outputs were to use the same pins, the resource is given priority.

Pin no.

Pin name

I/O*

Circuit type

Function

138

139

140

141

142

143

PPG0/PI2

PPG1/PI3

PPG2/PI4

PPG3/PI5

PPG4/PI6

PPG5/PI7

I/O

C

[PPG0 to 5] This is the PPG timer 1 output. This function is

effective if the output specification of the PPG timer is permit-

ted.

[PI2 to 7] This is a multi-purpose input/output port. This func-

tion is effective if the output specification of the PPG timer is

prohibited.

18

46

66

76

104

125

V

CC

5

This provides power for the 5 V digital circuit system.

47

82

126

V

CC

3

This provides power for the 3 V digital circuit system.

9

19

28

37

54

67

79

105

118

135

144

V

SS

This is the earth level for digital circuits.

MB91110 Series

12

s

s

s

s

I/O CIRCUIT TYPE

(Continued)

Type

Circuit types

Remarks

A

· Oscillation feedback resistance :

approximately 1 M

· 12.5 MHz oscillation

B

· CMOS level hysteresis input

Without standby control

With pull-up resistance

C

· CMOS level output

CMOS level input

With standby control

D

· A/D converter

Analog input pin

X1

STANDBY

CONTROL

X0

Clock input

V

SS

V

CC

P-channel type Tr

Digital input

STANDBY

CONTROL

Digital output

Digital output

Digital input

Analog input

MB91110 Series

13

(Continued)

Type

Circuit types

Remarks

E

· CMOS level hysteresis input

Without standby control

F

· CMOS level output

· CMOS level hysteresis input

Without standby control

G

· CMOS level output

H

· CMOS level output

· CMOS level hysteresis input

With standby control

I

· CMOS level input

Without standby control

Digital input

Digital output

Digital output

Digital input

Digital output

Digital output

STANDBY

CONTROL

Digital output

Digital output

Digital input

Digital input

MB91110 Series

14

s

s

s

s

HANDLING DEVICES

· Preventing Latch-up

The "Latch-up" phenomenon may be generated if a voltage in excess of V

CC

or lower than V

SS

is applied to the

input/output pins, or if the voltage exceeds the rating between V

CC

and V

SS

. If latch-up is generated, the electrical

current increases significantly and may destroy certain components due to the excessive heat, so great care

must be taken to ensure that the maximum rating is not exceeded during use.

· Handling Unused Input Pins

Input pins that are not used should be pulled up or down as they may cause erroneous operations if they are

left open.

· External Reset Input

"L" level should be input to the RST pin, which is required for at least five machine cycles to ensure the internal

status is reset.

· Using External Clocks

If external clock is used, X0 pin should be provided, and X1 pin should be provided with reverse phase to X0

pin input. If the STOP mode (oscillation stop mode) is used simultaneously, the X1 pin is stopped with the "H"

output. So, when STOP mode is specified, approximately 1 k

of resistance should be added externally. An

example of the external clock usage methods is shown in the following circuit.

Note : Resistance must be added to the X1 pin if the STOP mode (oscillation stop mode) is used.

· Power Supply Pins

In products with multiple Vcc or Vss pins, the pins of the same potential are internally connected in the device

to avoid abnormal operations including latch-up. However you must connect the pins to an external power and

a ground line to lower the electro-magnetic emission level to prevent abnormal operation of strobe signals caused

by the rise in the ground level, and to conform to the total current rating.

Make sure to connect Vcc and Vss pins via the lowest impedance to power lines.

It is recommended to provide a bypass capacitor of around 0.1 F between Vcc and Vss pins near the device.

· Crystal Oscillator Circuits

Noise around the X0 or X1 pins may cause erroneous operation. Make sure to provide bypass capacitors via

shortest distances from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure

that lines of oscillation circuits not cross the lines of other circuit.

A printed circuit board artwork surrounding the X0 and X1 pins with ground area for stabilizing the operation is

highly recommended .

X0

X1

MB91110

Example of External Clock Usage (normal case)

MB91110 Series

15

· N.C. Pins

N.C. pins must be opened for use.

· Mode Pins (MD0 to MD2)

Those pins must be directly connected to V

CC

or V

SS

for use.

Pattern length between V

CC

or V

SS

and each mode pin on the printed-circuit board should be arranged to be as

short as possible to prevent the test mode being erroneously turned on due to noise, they should also be

connected with low impedance.

· In the Event that Power Is Turned on

The RST pin must be started from "L" level when the power is turned on, and when the power is adjusted to the

V

CC

level it should be changed to the "H" level after being left for at least five cycles of the internal operation clock.

· Original Oscillation Input in the Event that Power Is Turned on

The clock must be input until the waiting status for oscillation stability is reset in the event that power is turned on.

· Hardware Standby in the Event that Power Is Turned on

Standby is not set in the event that power is turned on while the HST pin is set at "L" level. The HST pin becomes

effective after being reset, but it must first be returned to "H" level.

· Power on Reset

When power is turned on, "Power on reset" must be executed. If the power voltage falls below the guaranteed

operating voltage, "Power on reset" must be executed by turning on power supply again.

· Restrictions for Standby

Programs to be set for stop and sleep must be placed address area of the external memory. If placed in the

RAM address area on the I-bus, operation can not be guaranteed after returning.

· Execution of Programs in I-RAM Areas

In the event that programs in the I-RAM areas are executed, enter the I-RAM areas in accordance with the JMP

system instruction. Conversely, when changing from programs in the I-RAM area to those in other areas, exit

in accordance with the JMP system instructions.

· Caution on Operation during PLL Clock Mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even

when there is no external oscillator or external clock input is stopped. Performance of this operation, however,

cannot be guaranteed.

MB91110 Series

16

s

s

s

s

BLOCK DIAGRAM

FR30 CPU

D-bus (32 bit)

Harvard

Prinston

Bus Converter

Bit Search Module

DMAC (5 ch)

DREQ0

DACK0

DEOP0

DREQ1

DACK1

DEOP1

DREQ2

DACK2

DEOP2

32 bit 16 bit

Bus Converter

X0 X1

RST

HST

Clock Control Unit

INT0

INT7

NMI

Interrupt Control Unit

AN0

AN7

ATG

AV

CC

AV

SS

AVRH AVRL

TI0 TI1

TO0 TO1

A/D Converter (8 ch)

Reload Timer (2 ch)

Port E

I

R-bus (16 bit)

UART

16 bit PPG Timer

(6 ch)

SI

SO

SCK

PPG0

PPG5

TRG0

TRG5

(32 bit)

C-bus

Port 0

B

DRAM Controller

Bus Controller

RAS0

CS0L

CS0H

DW0

RAS1

CS1L

CS1H

DW1

D31

D16

A23

A00

RD

WR0

WR 1

RDY

CLK

CS0

CS5

BRQ BGRNT

RAM

PLL

50 MHz

5 KB

Instruction RAM

Instruction Cache

1 KB

16 KB

50 MHz

25 MHz

50 MHz

25 MHz

I-bus

(16 bit)

Notes :

·

Pins are described per function. Some of the pins are multiplexed.

·

In the event that REALOS is used, an external interruption or built-in timer should be used to control

the time.

MB91110 Series

17

s

s

s

s

MEMORY SPACE

The FR30 series has 4 Gbytes (2

32

addresses) of logic address space which the CPU accesses linearly.

1.

Memory Map

Note : MB91110 series only supports external ROM external bus mode.

· Direct addressing area

The following areas of the address space are used for I/O. This area is called the "direct addressing area" and

the address of the operand can be specified directly during instruction. The direct area differs depending on

data size to be accessed.

·

Byte data access

: 0-0FF

H

·

Half-word data access

: 0-1FF

H

·

Word data access

: 0-3FF

H

0000 0000

H

0000 0400

H

0000 0800

H

0000 1000

H

0000 2400

H

0001 0000

H

0008 0000

H

000B C000

H

000C 0000

H

0010 0000

H

FFFF FFFF

H

I/O

I/O

I-RAM 16 KB

External ROM external bus modes

Access is prohibited

Built-in RAM 5 KB

Access is prohibited

Access is prohibited

External area

External area

External area

Direct addressing area

(Refer to "I/O MAP")

MB91110 Series

18

2.

Registers

There are two types of multi-purpose registers in the FR family. One is a dedicated purpose register that exists

within the CPU and the other is a multi-purpose register that exists in the memory.

· Dedicated Registers

· Program Status (PS)

PS is the register that holds the program status and is classified into three categories, namely, Condition Code

Register (CCR) , System Condition Code Register (SCR) and Interruption Level Master Register (ILM) .

Program Counter (PC)

: 32-bit length; indicates instruction storage position.

Program Status (PS)

: 32-bit length; stores register pointers and condition codes.

Table Base Register (TBR)

: Holds the starting address of the vector table to be used for Exception, In-

terruption and Trapping (EIT) .

Return Pointer (RP)

: Holds the address to which you will return to from the sub-routine.

System Stuck Pointer (SSP) : Indicates the systems stuck position.

User Stuck Pointer (USP)

: Indicates the user's stuck position.

Multiplication and Division

Results Resister (MDH/MDL)

: 32-bit length; These are the registers for multiplication and division.

PC

PS

TBR

RP

SSP

USP

MDH

MDL

XXXX XXXX

H

(Undecided)

XXXX XXXX

H

(Undecided)

XXXX XXXX

H

(Undecided)

XXXX XXXX

H

(Undecided)

XXXX XXXX

H

(Undecided)

0000 0000

H

000F FC00

H

32 bit

Program Counter

Program Status

Table Base Register

Return Pointer

System Stuck Pointer

User Stuck Pointer

Multiplication and Division

Results Resister

Initial values

PS

ILM4 ILM3 ILM2

ILM

SCR

CCR

ILM1 ILM0

D1

D0

T

S

I

N

Z

V

C

0

1

2

3

4

5

6

7

8

9

10

16

17

18

19

20

31 to 21

15 to 11

MB91110 Series

19

· Condition Code Register (CCR)

· System Condition Code Register (SCR)

· Interruption Level Mask Register (ILM)

S flag

: Specifies the stuck pointer to be used as R15.

I flag

: Controls permission and prohibition of user interruption requests.

N flag

: Indicates codes when the computation results are defined as integers that are expressed in

complements of 2.

Z flag

: Indicates if arithmetic results were "0."

V flag

:

Indicates when operands are used for computation and defined as integers expressed in com-

plements of 2, and indicates whether or not an overflow is generated as a result of the compu-

tation.

C flag

: Indicates whether carrying or borrowing is generated from the highest bit as a result of the com-

putation.

T flag

: Specifies whether or not the step- trace- trap will be valid.

ILM4 to ILM0 : Holds the interruption level mask values, and those values that are held by the ILM are used

for the level mask. Interruption requests can only be accepted when the interruption levels

handled within the interruption requests to be input into the CPU are stronger than the levels

shown by the ILM.

ILM4

ILM3

ILM2

ILM1

ILM0

Interruption level

Strength

0

0

0

0

0

0

Strong

0

1

0

0

0

15

1

1

1

1

1

31

Weak

MB91110 Series

20

s

s

s

s

MULTI-PURPOSE REGISTERS

The multi-purpose registers are CPU registers (R0 to R15) which are used as accumulators for various compu-

tations and memory access pointers (field that indicates the address) .

Special purposes are assumed for the following three registers out of the 16 registers. Thus, some instructions

are emphasized.

R13 : Virtual accumulator (AC)

R14 : Frame Pointer (FP)

R15 : Stack Pointer (SP)

Initial values for R0 to R14 on resetting are unspecified. The initial value of R15 will be 0000 0000

H

(SSP value) .

· Register bank configuration

R0

R1

R12

R13

R14

R15

AC (Accumulator)

FP (Frame Pointer)

SP (Stack Pointer)

XXXX XXXX

H

XXXX XXXX

H

0000 0000

H

32-bit

Initial value

MB91110 Series

21

s

s

s

s

MODE SETTING

1.

Pins

· Mode pins and set mode

* : MB91110 series is not supported single chip mode.

2.

Register

· Mode register (MODR) and set mode

· Bus mode set bit and its functions

Mode pins

Mode name

Reset vector

access areas

External data bus

width

Bus modes

MD2

MD1

MD0

0

0

0

External vector

mode 0

External

8-bit

External ROM external

bus mode

0

0

1

External vector

mode 1

External

16-bit

0

1

0

Setting is prohibited

0

1

1

Internal vector

mode

Internal

(Mode register)

Single chip mode*

1

Usage is prohibited

M1

M0

Functions

Remarks

0

0

Single chip mode

Not supported

0

1

Internal ROM external bus mode

Not supported

1

0

External ROM external bus mode

1

1

Setting is prohibited

Address

Initial value

Access

0000 07FF

H

XXXXXXXX

B

W

M1

M0

*

*

*

*

*

*

Bus mode set bit

W : Write only

X : Undecided

* : "0" should always be written for bits other than M1 and M0.

MB91110 Series

22

s

s

s

s

I/O MAP

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000000

H

PDR2

(R/W)

Port data register

XXXXXXXX

000004

H

PDR6

(R/W)

XXXXXXXX

000008

H

PDRB

(R/W)

PDRA

(R/W)

PDR8

(R/W)

XXXXXXXX

-

XXXXXX

-

-

-

X

-

-

XXX

00000C

H

000010

H

PDRE

(R/W)

PDRF

(R/W)

-

-

-

-

XXXX

XXXXXXXX

000014

H

PDRG

(R/W)

PDRH

(R/W)

PDRI

(R/W)

-

-

XXXXXX

XXXXXXXX

XXXXXXXX

000018

H

Reserved

00001C

H

Reserved

000020

H

SSR

(R/W)

SIDR/SODR (R/W)

SCR

(R/W)

SMR

(R/W)

UART

0

0

0

0

1

-

0

0

XXXXXXXX

0

0

0

0

0

1

0

0

0

0

0

0

0

-

0

0

000024

H

CDCR

(R/W)

0 - - 1 1 1 1 1

000028

H

TMRLR

(W)

TMR

(R)

Reload timer 0

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

00002C

H

TMCSR

(R/W)

-

-

-

-

0

0

0

0 0

0

0

0

0

0

0

0

000030

H

TMRLR

(W)

TMR

(R)

Reload timer 1

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000034

H

TMCSR

(R/W)

-

-

-

-

0

0

0

0 0

0

0

0

0

0

0

0

000038

H

ADCR

(R)

ADCS

(R/W)

A/D converter

(Sequential

comparison type)

-

-

-

- -

- XX XXXXXXXX

0

0

0

0

0

0

0

0 0

0

0

0

0

0

0

0

00003C

H

Reserved

MB91110 Series

23

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000040

H

Reserved

000044

H

Access is prohibited

PCSR

(W)

PPG0

XXXXXXXX XXXXXXXX

000048

H

PDUT

(W)

PCNH

(R/W)

PCNL

(R/W)

XXXXXXXX XXXXXXXX

0

0

0

0

0

0

0

-

0

0

0

0

0

0

0

0

00004C

H

Access is prohibited

PCSR

(W)

PPG1

XXXXXXXX XXXXXXXX

000050

H

PDUT

(W)

PCNH

(R/W)

PCNL

(R/W)

XXXXXXXX XXXXXXXX

0

0

0

0

0

0

0

-

0

0

0

0

0

0

0

0

000054

H

Access is prohibited

PCSR

(W)

PPG2

XXXXXXXX XXXXXXXX

000058

H

PDUT

(W)

PCNH

(R/W)

PCNL

(R/W)

XXXXXXXX XXXXXXXX

0

0

0

0

0

0

0

-

0

0

0

0

0

0

0

0

00005C

H

Access is prohibited

PCSR

(W)

PPG3

XXXXXXXX

XXXXXXXX

000060

H

PDUT

(W)

PCNH

(R/W)

PCNL

(R/W)

XXXXXXXX XXXXXXXX

0

0

0

0

0

0

0

-

0

0

0

0

0

0

0

0

000064

H

Access is prohibited

PCSR

(W)

PPG4

XXXXXXXX XXXXXXXX

000068

H

PDUT

(W)

PCNH

(R/W)

PCNL

(R/W)

XXXXXXXX XXXXXXXX

0

0

0

0

0

0

0

-

0

0

0

0

0

0

0

0

00006C

H

Access is prohibited

PCSR

(W)

PPG5

XXXXXXXX XXXXXXXX

000070

H

PDUT

(W)

PCNH

(R/W)

PCNL

(R/W)

XXXXXXXX XXXXXXXX

0

0

0

0

0

0

0

-

0

0

0

0

0

0

0

0

000074

H

Reserved

000078

H

00007C

H

000080

H

MB91110 Series

24

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000084

H

Reserved

000088

H

00008C

H

000090

H

000094

H

EIRR

(R/W)

ENIR

(R/W)

External interruption/

NMI

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

000098

H

ELVR

(R/W)

0

0

0

0

0

0

0

0 0

0

0

0

0

0

0

0

00009C

H

Reserved

0000A0

H

0000A4

H

0000A8

H

0000AC

H

0000B0

H

0000B4

H

0000B8

H

0000BC

H

0000C0

H

0000C4

H

MB91110 Series

25

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

0000C8

H

Reserved

0000CC

H

0000D0

H

DDRE

(W)

DDRF

(W)

Data direction

register

-

-

-

-

0

0

0

0

0

0

0

0

0

0

0

0

0000D4

H

DDRG

(W)

DDRH

(W)

DDRI

(W)

-

-

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0000D8

H

to

0000FC

H

Reserved

000100

H

to

0001FC

H

Reserved

000200

H

DMACS0

(R/W)

DMA controller

channel 0

0

-

0

0

-

0

0

0

0

0 -

-

0

0

0

0

XX

-

0

0

0

0

0

-

-

-

-

XX

-

X

000204

H

DMACC0

(R/W)

- - - - XXXX

XXXX - XXX

XXXXXXXX

XXXXXXXX

000208

H

DMASA0

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

00020C

H

DMADA0

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

000210

H

DMACS1

(R/W)

DMA controller

channel 1

0

-

0

0

-

0

0

0

0

0 -

-

0

0

0

0

XX

-

0

0

0

0

0

-

-

-

-

XX

-

X

000214

H

DMACC1

(R/W)

-

-

-

-

XXXX

XXXX

-

XXX

XXXXXXXX

XXXXXXXX

000218

H

DMASA1

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

00021C

H

DMADA1

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

MB91110 Series

26

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000220

H

DMACS2

(R/W)

DMA controller

channel 2

0

-

0

0

-

0

0

0

0

0

-

-

0

0

0

0

XX

-

0

0

0

0

0

-

-

-

-

XX

-

X

000224

H

DMACC2

(R/W)

-

-

-

-

XXXX

XXXX

-

XXX

XXXXXXXX

XXXXXXXX

000228

H

DMASA2

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

00022C

H

DMADA2

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

000230

H

DMACS3

(R/W)

DMA controller

channel 3

0

-

0

0

-

0

0

0

0

0 -

-

0

0

0

0

XX

-

0

0

0

0

0

-

-

-

-

XX

-

X

000234

H

DMACC3

(R/W)

-

-

-

-

XXXX

XXXX

-

XXX

XXXXXXXX

XXXXXXXX

000238

H

DMASA3

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

00023C

H

DMADA3

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

000240

H

DMACS4

(R/W)

DMA controller

channel 4

0

-

0

0

-

0

0

0

0

0 -

-

0

0

0

0

XX

-

0

0

0

0

0

-

-

-

-

XX

-

X

000244

H

DMACC4

(R/W)

-

-

-

-

XXXX

XXXX

-

XXX

XXXXXXXX

XXXXXXXX

000248

H

DMASA4

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

00024C

H

DMADA4

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

000250

H

DMACR

(R/W)

Overall DMA

controller

- - - - - - - -

- - - - - - - -

0 0 - - - - - -

- - - - - - - 0

000254

H

Reserved

000258

H

00025C

H

000260

H

MB91110 Series

27

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000264

H

Reserved

000268

H

00026C

H

000270

H

000274

H

000278

H

to

0002FC

H

000300

H

to

0003E0

H

0003E4

H

ICHCR

(R/W)

Instruction cache

-

-

0 0 0 0 0 0

0003E8

H

Reserved

0003EC

H

IRMC

(R/W)

I-RAM control

-

-

-

-

-

-

-

0

0003F0

H

BSD0

(W)

Bit search module

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

0003F4

H

BSD1

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

0003F8

H

BSDC

(W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

0003FC

H

BSRR

(R)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

000400

H

ICR00

(R/W)

ICR01

(R/W)

ICR02

(R/W)

ICR03

(R/W)

Interruption controller

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000404

H

ICR04

(R/W)

ICR05

(R/W)

ICR06

(R/W)

ICR07

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

MB91110 Series

28

(Continued)

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000408

H

ICR08

(R/W)

ICR09

(R/W)

ICR10

(R/W)

ICR11

(R/W)

Interruption controller

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

00040C

H

ICR12

(R/W)

ICR13

(R/W)

ICR14

(R/W)

ICR15

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000410

H

ICR16

(R/W)

ICR17

(R/W)

ICR18

(R/W)

ICR19

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000414

H

ICR20

(R/W)

ICR21

(R/W)

ICR22

(R/W)

ICR23

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000418

H

ICR24

(R/W)

ICR25

(R/W)

ICR26

(R/W)

ICR27

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

00041C

H

ICR28

(R/W)

ICR29

(R/W)

ICR30

(R/W)

ICR31

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000420

H

ICR32

(R/W)

ICR33

(R/W)

ICR34

(R/W)

ICR35

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000424

H

ICR36

(R/W)

ICR37

(R/W)

ICR38

(R/W)

ICR39

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000428

H

ICR40

(R/W)

ICR41

(R/W)

ICR42

(R/W)

ICR43

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

00042C

H

ICR44

(R/W)

ICR45

(R/W)

ICR46

(R/W)

ICR47

(R/W)

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

-

-

-

1

1

1

1

1

000430

H

DICR

(R/W)

HRCL

(R/W)

Delay interruption

-

-

-

-

-

-

-

0

-

-

-

1

1

1

1

1

000434

H

to

00047C

H

Reserved

000480

H

RSRR/WTCR (R/W)

STCR

(R/W)

PDRR

(R/W)

CTBR

(W)

Clock control area

1 XXXX

-

0 0

0 0 0 1 1 1

-

-

-

-

-

-

0 0 0 0

XXXXXXXX

000484

H

GCR

(R/W)

WPR

(W)

1 1 0 0 1 1

-

1

XXXXXXXX

000488

H

PCTR

(R/W)

PLL control register

0 0

-

-

0

-

-

-

00048C

H

to

0005FC

H

Reserved

MB91110 Series

29

(Continued)

Note : Do not execute RMW instructions to registers with write-only bits.

RMW instruction (RMW : Read / Modify / Write)

Data in areas with "

" or reserved ones is undecided.

Address

Register

Internal resource

+

+

+

+

0

+

+

+

+

1

+

+

+

+

2

+

+

+

+

3

000600

H

DDR2

(W)

Data direction

register

0

0

0

0

0

0

0

0

000604

H

DDR6

(W)

0

0

0

0

0

0

0

0

000608

H

DDRB

(W)

DDRA

(W)

DDR8

(W)

0

0

0

0

0

0

0

0

-

0

0

0

0

0

0

-

-

-

0

-

-

0

0

0

00060C

H

ASR1

(W)

AMR1

(W)

External bus

interface

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

000610

H

ASR2

(W)

AMR2

(W)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

000614

H

ASR3

(W)

AMR3

(W)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

000618

H

ASR4

(W)

AMR4

(W)

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

00061C

H

ASR5

(W)

AMR5

(W)

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

000620

H

AMD0

(R/W)

AMD1

(R/W) AMD32

(R/W)

AMD4

(R/W)

-

-

-

0

0

1

1

1

0

-

-

0

0

0

0

0

0

0

0

0

0

0

0

0

0

-

-

0

0

0

0

0

000624

H

AMD5

(R/W)

DSCR

(W)

RFCR

(R/W)

0

-

-

0

0

0

0

0

0

0

0

0

0

0

0

0

-

-

XXXXXX

0

-

-

-

0

0

0

0

000628

H

EPCR0

(W)

EPCR1

(W)

-

-

-

-

1

1

0

0

-

1

1

1

1

1

1

1

- - - - - - - -

1

1

1

1

1

1

1

1

00062C

H

DMCR4

(R/W)

DMCR5

(R/W)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

-

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

-

000630

H

to

0007F8

H

Reserved

0007FC

H

LER

(W)

MODR

(W)

"Little endian" register

Mode register

-

-

-

-

-

0

0

0

XXXXXXXX

AND

Rj, @Ri

OR

Rj, @Ri

EOR

Rj, @Ri

ANDH

Rj, @Ri

ORH

Rj, @Ri

EORH

Rj, @Ri

ANDB

Rj, @Ri

ORB

Rj, @Ri

EORB

Rj, @Ri

BANDL

#u4, @Ri

BORL #u4, @Ri

BEORL

#u4, @Ri

BANDH

#u4, @Ri

BORH #u4, @Ri

BEORH

#u4, @Ri

MB91110 Series

30

s

s

s

s

INTERRUPTION VECTOR

Interruption factor and allocation of interruption vectors / interruption control registers are described in the

interruption vector table.

(Continued)

Interruption source

Interruption number

Interruption

level

*1

Offset

Interruption vector

address to TBR of

default

*2

Decimal

Hexadeci-

mal

Reset

0

00

3FC

H

000FFFFC

H

System reservation

1

01

3F8

H

000FFFF8

H

System reservation

2

02

3F4

H

000FFFF4

H

System reservation

3

03

3F0

H

000FFFF0

H

System reservation

4

04

3EC

H

000FFFEC

H

System reservation

5

05

3E8

H

000FFFE8

H

System reservation

6

06

3E4

H

000FFFE4

H

Coprocessor absence trap

7

07

3E0

H

000FFFE0

H

Coprocessor error trap

8

08

3DC

H

000FFFDC

H

INTE instruction

9

09

4 fixed

3D8

H

000FFFD8

H

System reservation

10

0A

3D4

H

000FFFD4

H

System reservation

11

0B

3D0

H

000FFFD0

H

Step trace trap

12

0C

4 fixed

3CC

H

000FFFCC

H

System reservation

13

0D

3C8

H

000FFFC8

H

Exceptions to undefined instructions

14

0E

3C4

H

000FFFC4

H

NMI request

15

0F

15 (F

H

) fixed

3C0

H

000FFFC0

H

System reservation

16

10

ICR00

3BC

H

000FFFBC

H

System reservation

17

11

ICR01

3B8

H

000FFFB8

H

External interruption 0

18

12

ICR02

3B4

H

000FFFB4

H

External interruption 1

19

13

ICR03

3B0

H

000FFFB0

H

External interruption 2

20

14

ICR04

3AC

H

000FFFAC

H

External interruption 3

21

15

ICR05

3A8

H

000FFFA8

H

External interruption 4

22

16

ICR06

3A4

H

000FFFA4

H

External interruption 5

23

17

ICR07

3A0

H

000FFFA0

H

External interruption 6

24

18

ICR08

39C

H

000FFF9C

H

External interruption 7

25

19

ICR09

398

H

000FFF98

H

System reservation

26

1A

ICR10

394

H

000FFF94

H

UART reception completion

27

1B

ICR11

390

H

000FFF90

H

System reservation

28

1C

ICR12

38C

H

000FFF8C

H

System reservation

29

1D

ICR13

388

H

000FFF88

H

UART transmission completion

30

1E

ICR14

384

H

000FFF84

H

System reservation

31

1F

ICR15

380

H

000FFF80

H

MB91110 Series

31

(Continued)

Interruption source

Interruption number

Interruption

level

*1

Offset

Interruption vector

address to TBR of

default

*2

Decimal

Hexadeci-

mal

System reservation

32

20

ICR16

37C

H

000FFF7C

H

DMAC0 (end, error)

33

21

ICR17

378

H

000FFF78

H

DMAC1 (end, error)

34

22

ICR18

374

H

000FFF74

H

DMAC2 (end, error)

35

23

ICR19

370

H

000FFF70

H

DMAC3 (end, error)

36

24

ICR20

36C

H

000FFF6C

H

DMAC4 (end, error)

37

25

ICR21

368

H

000FFF68

H

System reservation

38

26

ICR22

364

H

000FFF64

H

System reservation

39

27

ICR23

360

H

000FFF60

H

System reservation

40

28

ICR24

35C

H

000FFF5C

H

A/D sequential conversion type

41

29

ICR25

358

H

000FFF58

H

Reload timer 0

42

2A

ICR26

354

H

000FFF54

H

Reload timer 1

43

2B

ICR27

350

H

000FFF50

H

16-bit PPG timer 0

44

2C

ICR28

34C

H

000FFF4C

H

16-bit PPG timer 1

45

2D

ICR29

348

H

000FFF48

H

16-bit PPG timer 2

46

2E

ICR30

344

H

000FFF44

H

16-bit PPG timer 3

47

2F

ICR31

340

H

000FFF40

H

16-bit PPG timer 4

48

30

ICR32

33C

H

000FFF3C

H

16-bit PPG timer 5

49

31

ICR33

338

H

000FFF38

H

System reservation

50

32

ICR34

334

H

000FFF34

H

System reservation

51

33

ICR35

330

H

000FFF30

H

System reservation

52

34

ICR36

32C

H

000FFF2C

H

System reservation

53

35

ICR37

328

H

000FFF28

H

System reservation

54

36

ICR38

324

H

000FFF24

H

System reservation

55

37

ICR39

320

H

000FFF20

H

System reservation

56

38

ICR40

31C

H

000FFF1C

H

System reservation

57

39

ICR41

318

H

000FFF18

H

System reservation

58

3A

ICR42

314

H

000FFF14

System reservation

59

3B

ICR43

310

H

000FFF10

H

System reservation

60

3C

ICR44

30C

H

000FFF0C

H

System reservation

61

3D

ICR45

308

H

000FFF08

H

System reservation

62

3E

ICR46

304

H

000FFF04

H

Delay interruption factor bit

63

3F

ICR47

300

H

000FFF00

H

System reservation

(used under REALOS)

*3

64

40

2FC

H

000FFEFC

H

MB91110 Series

32

(Continued)

*1 : ICR sets the interruption level for each interruption request using the register built into the interruption controller.

ICR is prepared in accordance with each interruption request.

*2 : TBR is the register that indicates the starting address of the vector table for EIT.

Addresses with added offset values that are specified per TBR and EIT factor will be the vector addresses.

*3 : REALOS OS/FR uses 0X40, 0X41 interruptions for system codes.

Reference :

The vector area for EIT is 1 KB in accordance with the address shown by TBR.

The size per vector is 4 bytes, and the relationship between the vector numbers and their addresses is shown

as follows.

Interruption source

Interruption number

Interruption

level

*1

Offset

Interruption vector

address to TBR of

default

*2

Decimal

Hexadeci-

mal

System reservation

(used under REALOS)

*3

65

41

2F8

H

000FFEF8

H

Used under INT instruction

66

to

255

42

to

FF

2F4

H

to

000

H

000FFEF4

H

to

000FFD00

H

vctadr

=

TBR

+

vctofs

=

TBR

+

(3FC

H

-

4

×

vct)

vctadr : vector address

vctofs : vector offset

vct : vector number

MB91110 Series

33

s

s

s

s

PERIPHERAL RESOURCES

1.

I/O Port

MB91110 series can be used as the I/O port when settings for resources that handle each pin do not to use the

pins for input/output.

· Block diagram

· I/O Port Registers

I/O port is composed of the Port Data Register (PDR) and Data Direction Register (DDR) .

·

In cases where the input mode is DDR

=

"0"

For PDR reading : Level of external pins to be handled is read out.

For PDR writing : Set value is written in PDR.

·

In cases where the output mode is DDR

=

"1"

For PDR reading : PDR value is read out.

For PDR writing : Set value is written in PDR and the PDR value is simultaneously output to the

externally handled pin.

PDR

DDR

1

0

1

0

Data Bus

pin

PDR read

PDR

:

Port Data Register

DDR

:

Data Direction Register

Resource input

Resource

output

Resource output

allowed

MB91110 Series

34

2.

Port Data Register (PDR)

Port Data Register (PDR2-I) is the input/output data register for the I/O port.

Input/output control is carried out by the handled data direction register (DDR2-I) .

· Port Data Register (PDR)

PDR2

Initial value

Access

Address : 000001

H

XXXXXXXX

B

R/W

PDR6

Initial value

Access

Address : 000005

H

XXXXXXXX

B

R/W

PDR8

Initial value

Access

Address : 00000B

H

- - X- - XXX

B

R/W

PDRA

Initial value

Access

Address : 000009

H

- XXXXXX-

B

R/W

PDRB

Initial value

Access

Address : 000008

H

XXXXXXXX

B

R/W

PDRE

Initial value

Access

Address : 000012

H

- - - - XXXX

B

R/W

PDRF

Initial value

Access

Address : 000013

H

XXXXXXXX

B

R/W

PDRG

Initial value

Access

Address : 000014

H

- - XXXXXX

B

R/W

PDRH

Initial value

Access

Address : 000015

H

XXXXXXXX

B

R/W

PDRI

Initial value

Access

Address : 000016

H

XXXXXXXX

B

R/W

7

6

5

4

3

2

1

0

P26

P27

P25

P24

P23

P22

P21

P20

7

6

5

4

3

2

1

0

P66

P67

P65

P64

P63

P62

P61

P60

7

6

5

4

3

2

1

0

P85

P82

P81

P80

7

6

5

4

3

2

1

0

PA6

PA5

PA4

PA3

PA2

PA1

7

6

5

4

3

2

1

0

PB6

PB7

PB5

PB4

PB3

PB2

PB1

PB0

7

6

5

4

3

2

1

0

PE3

PE2

PE1

PE0

7

6

5

4

3

2

1

0

PF6

PF7

PF5

PF4

PF3

PF2

PF1

PF0

7

6

5

4

3

2

1

0

PG5

PG4

PG3

PG2

PG1

PG0

7

6

5

4

3

2

1

0

PH6

PH7

PH5

PH4

PH3

PH2

PH1

PH0

7

6

5

4

3

2

1

0

PI6

PI7

PI5

PI4

PI3

PI2

PI1

PI0

MB91110 Series

35

3.

Data Direction Register (DDR)

The Data Direction Register (DDR2-I) controls the input/output direction of the I/O port per bit.

0 is used for input and 1 is used to execute output control.

· Data Direction Register (DDR)

DDR2

Initial value Access

Address : 000601

H

00000000

B

W

DDR6

Initial value Access

Address : 000605

H

00000000

B

W

DDR8

Initial value Access

Address : 00060B

H

- - 0 - - 000

B

W

DDRA

Initial value Access

Address : 000609

H

- 000000 -

B

W

DDRB

Initial value Access

Address : 000608

H

00000000

B

W

DDRE

Initial value Access

Address : 0000D2

H

- - - - 0000

B

W

DDRF

Initial value Access

Address : 0000D3

H

00000000

B

W

DDRG

Initial value Access

Address : 0000D4

H

- - 000000

B

W

DDRH

Initial value Access

Address : 0000D5

H

00000000

B

W

DDRI

Initial value Access

Address : 0000D6

H

00000000

B

W

7

6

5

4

3

2

1

0

P26

P27

P25

P24

P23

P22

P21

P20

7

6

5

4

3

2

1

0

P66

P67

P65

P64

P63

P62

P61

P60

7

6

5

4

3

2

1

0

P85

P82

P81

P80

7

6

5

4

3

2

1

0

PA6

PA5

PA4

PA3

PA2

PA1

7

6

5

4

3

2

1

0

PB6

PB7

PB5

PB4

PB3

PB2

PB1

PB0

7

6

5

4

3

2

1

0

PE3

PE2

PE1

PE0

7

6

5

4

3

2

1

0

PF6

PF7

PF5

PF4

PF3

PF2

PF1

PF0

7

6

5

4

3

2

1

0

PG5

PG4

PG3

PG2

PG1

PG0

7

6

5

4

3

2

1

0

PH6

PH7

PH5

PH4

PH3

PH2

PH1

PH0

7

6

5

4

3

2

1

0

PI6

PI7

PI5

PI4

PI3

PI2

PI1

PI0

MB91110 Series

36

4.

Instruction Cache

The instruction cache is a temporary storage memory. In the event that the instruction codes are accessed from

a low speed external memory, it holds the accessed codes internally, and is used to increase the access speed

for all subsequent accesses.

Direct read or write access can not be done by instruction cache or instruction cache tag using software.

· Cacheable area of the instruction cache

Instruction cache allows all space to become a cacheable area.