DS04-28501-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

ASSP

Single Chip 8-Bit A/D and 9-Bit

D/A Converter

MB40168/MB40178

s

DESCRIPTION

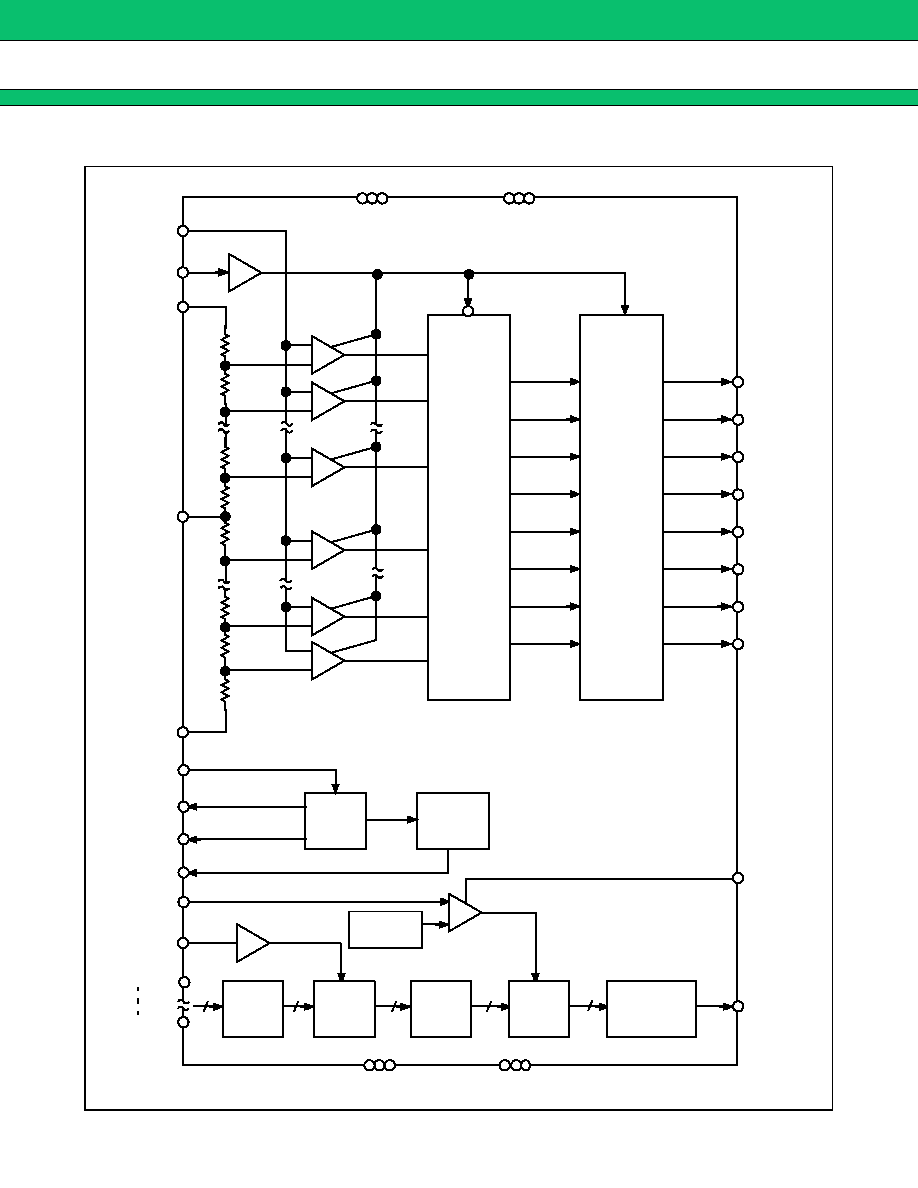

The Fujitsu MB40168 and MB40178 are high speed, low power single chip A/D and D/A converters designed

for video processing applications. The A/D converter has a resolution of 8 bits while the D/A converter has 9-

bit resolution. They are fabricated in Fujitsu's advanced bipolar technology, and housed in a 48-pin plastic shrink

DIP or 44-pin plastic QFP package.

s

FEATURES

· Resolution

A/D: 8 bits

D/A: 9 bits

· Conversion Rate

A/D: Max. 20 MSPS

D/A: Max. 40 MSPS

· Linearity Error

A/D:

Max.

+

0.3%

D/A: Max.

+

0.2%

· On-chip reference voltage generator (resistor divided method) and clamp circuit

· Analog Input Voltage

3 to 5 V without clamp circuit

0 to 3 V in 1.95 V

P-P

clamp circuit

· Analog Output Voltage

3 to 5 V

(Continued)

s

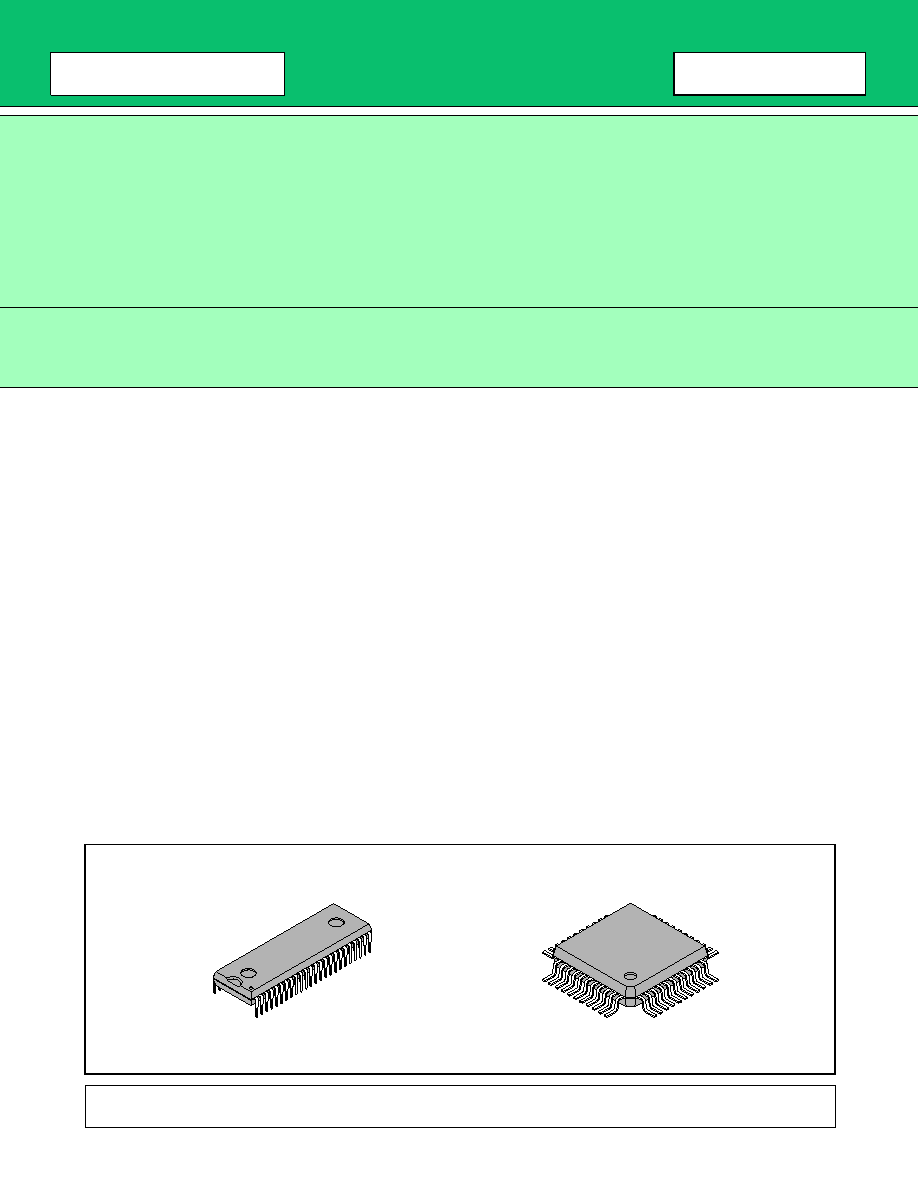

PACKAGES

(DIP-48P-M01)

48 pin, Plastic SH-DIP

(FPT-44P-M11)

44 pin, Plastic QFP

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that

normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

2

MB40168/MB40178

(Continued)

· Digital Input/Output Interface

TTL Levels

· Power Supply Voltage

+ 5.0 V single power supply

· Power Dissipation

Typ. 350 mW

· Package Options

48-pin Plastic Shrink DIP/

44-pin Plastic QFP Package

s

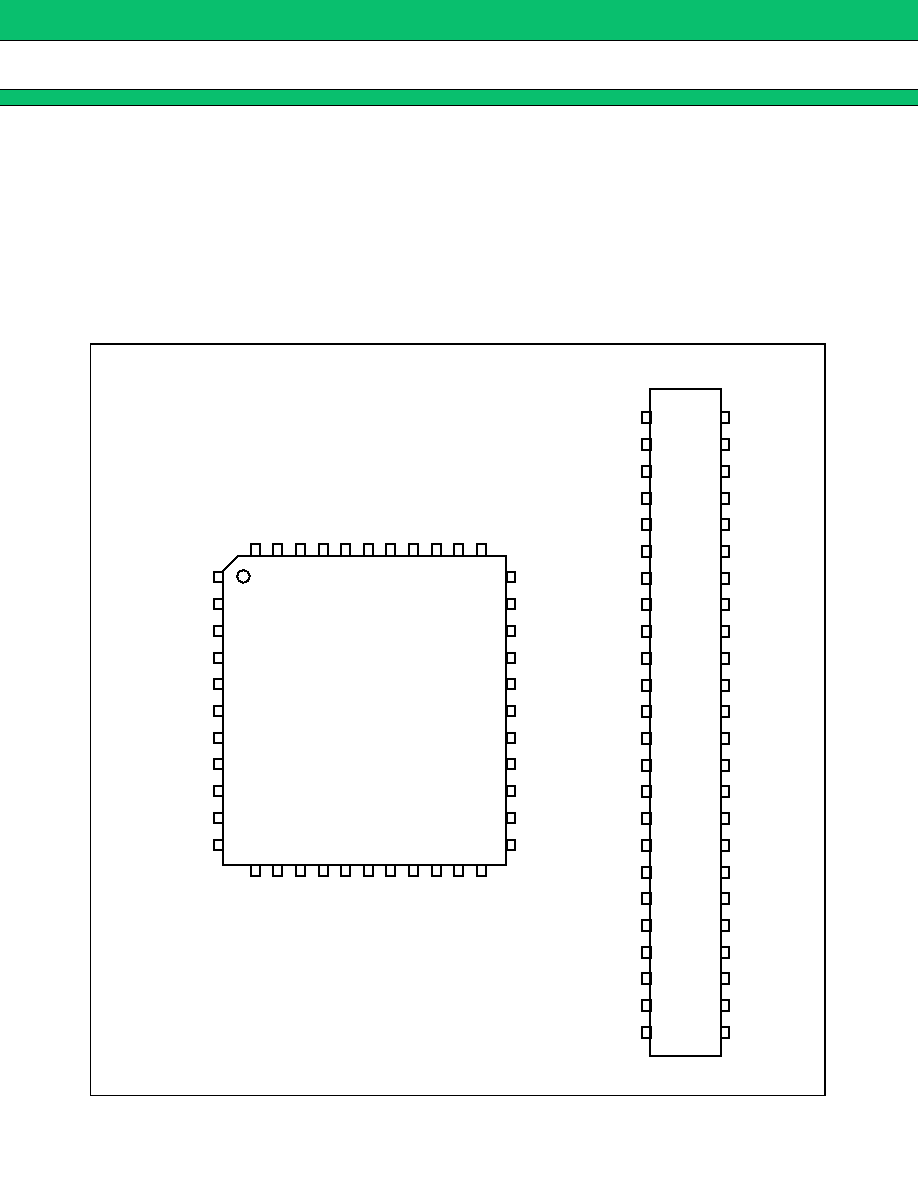

PIN ASSIGNMENTS

1

2

3

4

5

6

7

8

9

10

11

V

RIN

V

REF

V

RB

D.GND

A.GND

V

CCD

V

CCA

V

RM

V

INA

V

CLMP

V

OUTC

33

32

31

30

29

28

27

26

25

24

23

D

D6

D

D5

D

D4

D

D3

D

D2

(MSB) D

D1

(LSB) D

A8

D

A7

D

A6

D

A5

D

A4

12 13 14 15 16 17 18 19 20 21 22

44 43 42 41 40 39 38 37 36 35 34

D

D7

D

D8

D

D9

(LSB)

DACLK

D.GND

D.GND

A.GND

V

CCD

V

CCA

A.OUT

COMP

D

A3

D

A2

(MSB) D

A1

ADCLK

D.GND

A.GND

A.GND

V

CCD

V

CCA

V

RT

V

INC

(TOP VIEW)

(TOP VIEW)

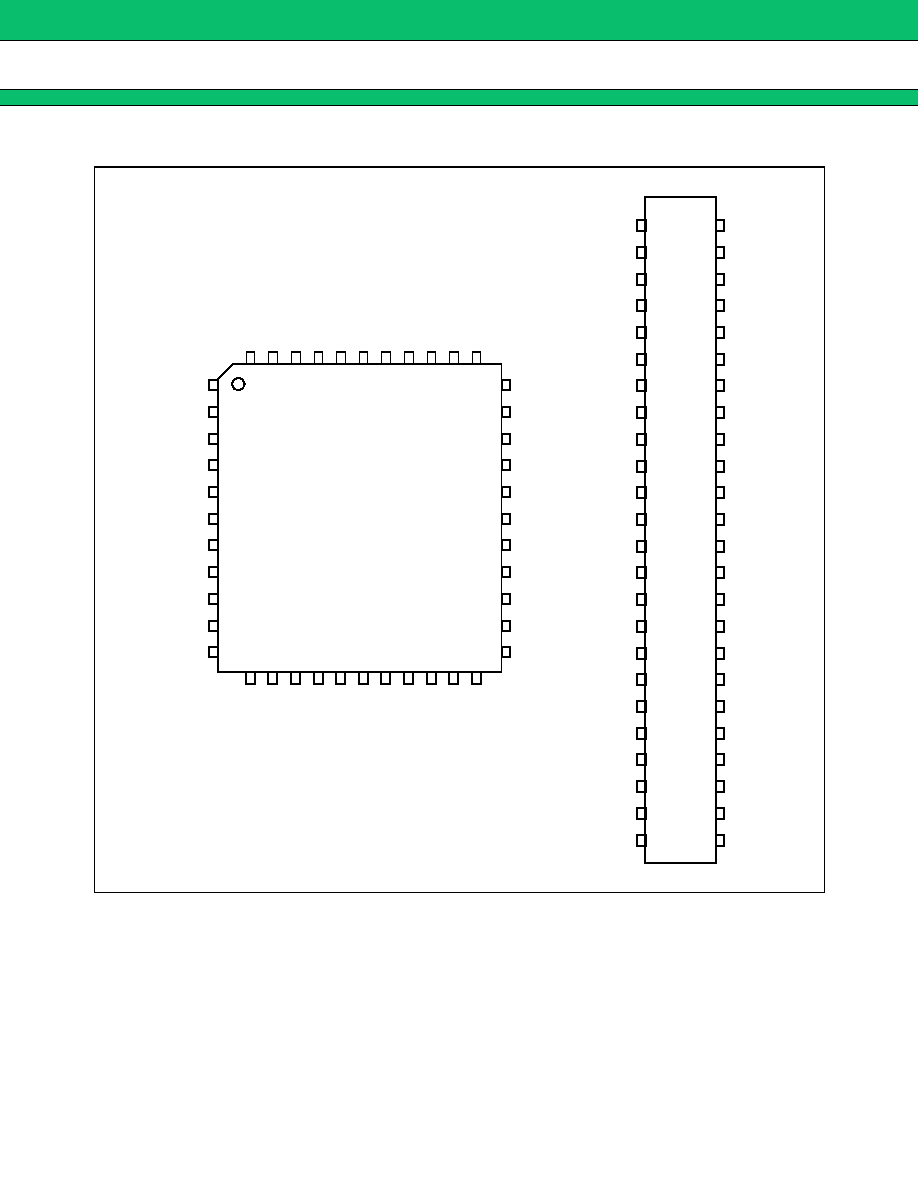

(FPT-44P-M11)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

D.GND

DACLK

(LSB) D

D9

D

D8

D

D7

D

D6

D

D5

D

D4

D

D3

D

D2

(MSB) D

D1

NC

NC

NC

(LSB) D

A8

D

A7

D

A6

D

A5

D

A4

D

A3

D

A2

(MSB) D

A1

ADCLK

D.GND

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

A.GND

V

CCD

V

CCA

A.OUT

COMP

V

RIN

V

REF

V

RB

NC

D.GND

A.GND

V

CCD

V

CCD

V

CCA

V

CCA

V

RM

V

INA

V

CLMP

V

OUTC

V

INC

V

RT

V

CCA

V

CCD

A.GND

(DIP-48P-M01)

· MB40168

4

MB40168/MB40178

s

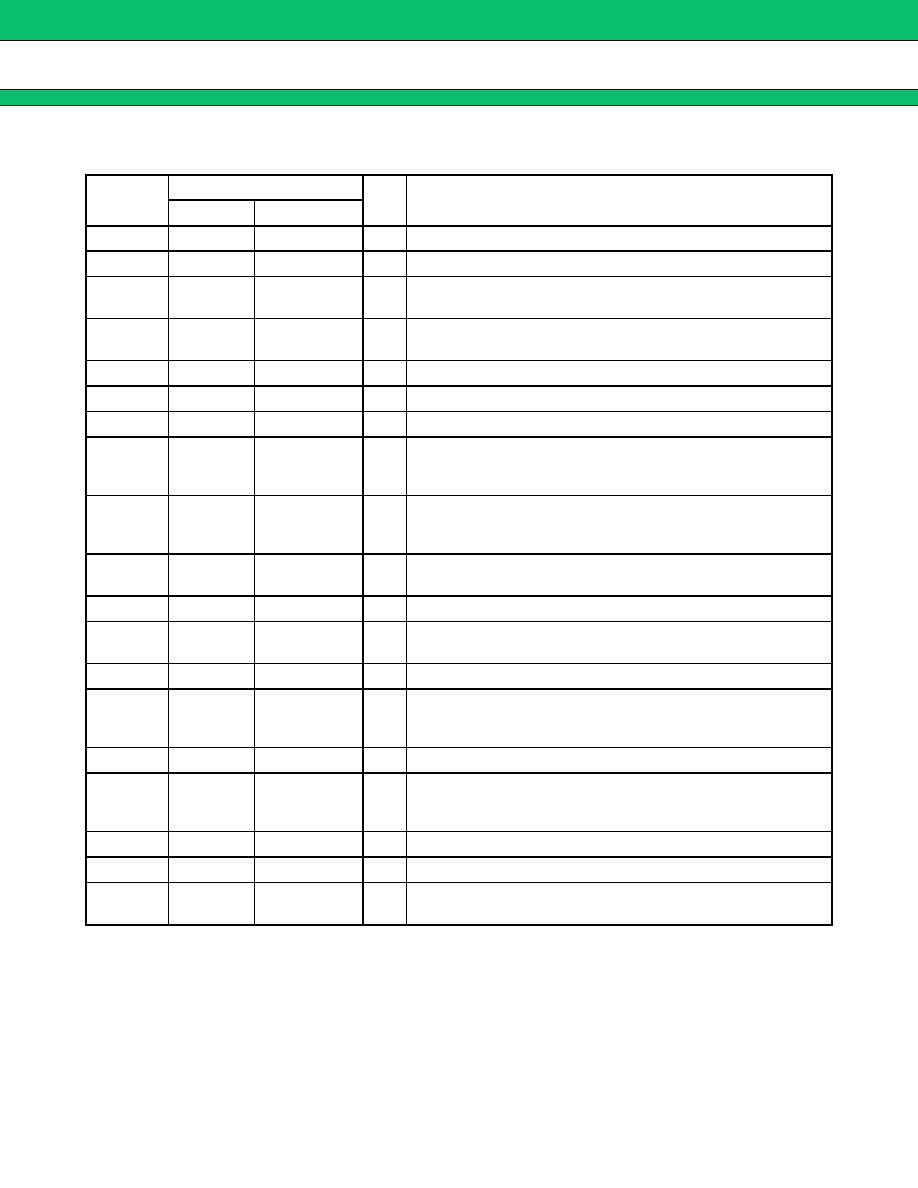

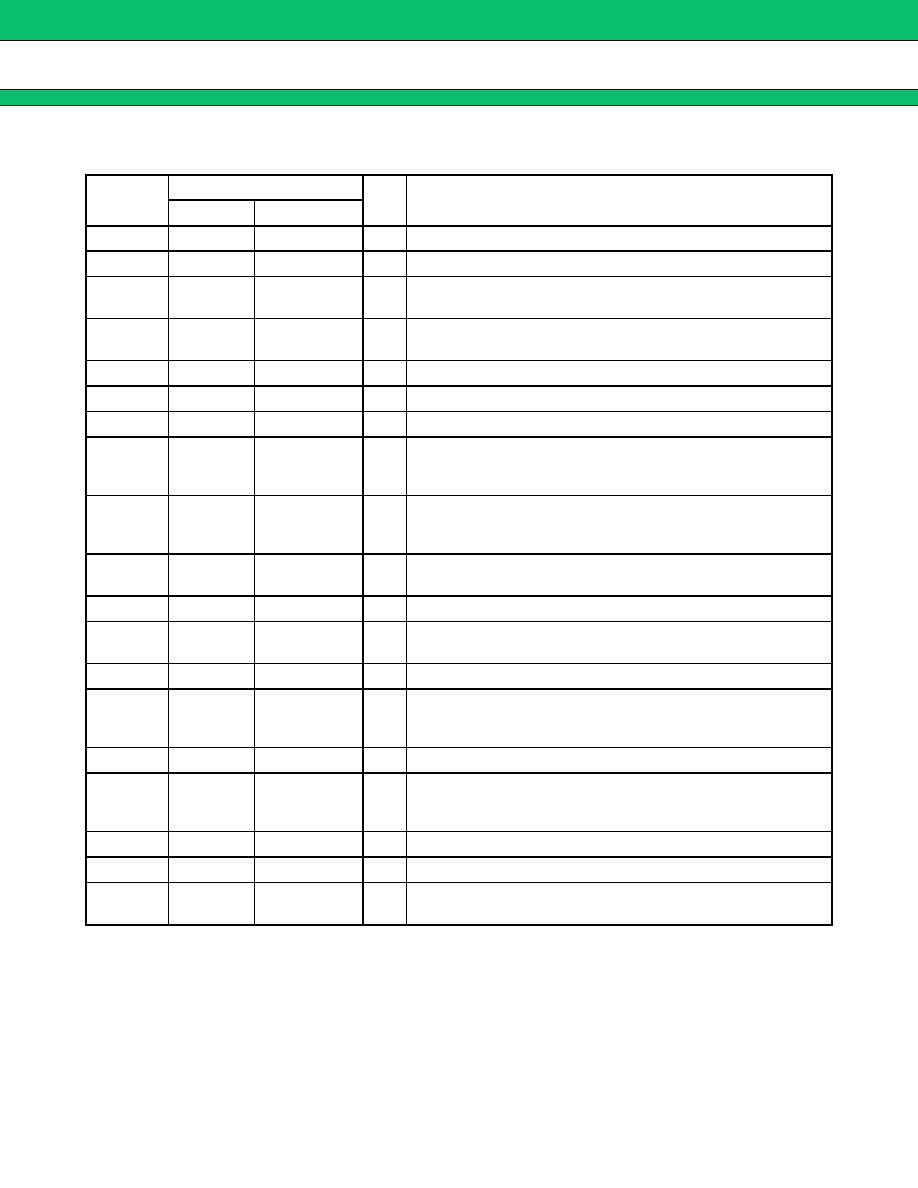

PIN DESCRIPTION

*1: MB40168 (MSB: 6 pin, LSB: 42 pin), MB40178 (MSB: 42 pin, LSB: 6 pin)

*2: MB40168 (MSB: 11 pin, LSB: 3 pin), MB40178 (MSB: 3 pin, LSB: 11 pin)

Symbol

Pin No.

I/O

Name & Function

QFP-44

SH-DIP-48

V

CCD

19, 28, 37

26, 36, 37, 47

--

Digital Power Supply pins (+ 5 V).

V

CCA

20, 27, 36

27, 34, 35, 46

--

Analog Power Supply pins (+ 5 V).

DGND

16, 30,

39, 40

1, 24, 39

--

Digital Ground (0 V). These pins should be connected to the

analog ground on the application system.

AGND

17, 18,

29, 38

25, 38, 48

--

Analog Ground (0 V). These pins should be connected to the

analog ground on the application system.

D

A8

- D

A1

7 - 14

15 - 22

O

ADC Digital Output pins. TTL level.

ADCLK

15

23

I

ADC Clock Input pin. TTL level.

V

RT

21

28

I

ADC Reference Voltage Input pin. (5 V Input)

V

INC

22

29

I

Sync Tip Clamp Circuit Analog Input pin. (0 - 3 V, 1.95 V

P-P

).

When a clamp circuit is not used, this pin is connected to

ground.

V

OUTC

23

30

O

Clamp Circuit Analog Output pin. It is used by adding a

capacitor (1

µ

F or more) between V

CLMP

and V

OVTC

pins.

When a clamp circuit is not used, this pin is left open.

V

CLMP

24

31

O

Clamp Voltage Output pin (3.05V Output). When a clamp

circuit is not used, this pin is left open.

V

INA

25

32

I

ADC Analog Signal Input pin. (3 - 5 V)

V

RM

26

33

--

ADC Middle Reference Voltage Monitor pin. (Mid of V

RT -

V

RB

is set to this pin). Normally this pin is left open.

V

RB

31

41

I

ADC Reference Voltage Input pin. (3 V)

V

REF

32

42

O

Reference Voltage Output pin. (Resistor Divider, 3 V)

By connecting this pin to V

RB

pin, 3V Voltages are generated.

When a reference voltage is not used, this pin is left open.

V

RIN

33

43

I

DAC Reference Voltage Input pin (3 V)

COMP

34

44

--

Phase Compensation Capacitor pin. (Capacitor greater than

0.1

µ

F should be connected between this pin and Analog

Ground.)

A

OUT

35

45

O

Analog Signal Output pin

DACLK

41

2

I

DAC Clock Input pin. TTL level.

D

D9

- D

D1

1 - 6 *

1

42 - 44

3 - 11*

2

I

DAC Digital Data Input pins. TTL level.