# Intel<sup>®</sup> 31244 PCI-X to Serial ATA Controller

**Developer's Manual**

April 2004

Order Number: 273603-006

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTELR PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 31244 PCI-X to Serial ATA Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantlP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetWerge, Intel NetWerge, Intel NetStructure, Intel Play, Intel Play Iogo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel Xeon, Perlinum, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2004, Intel Corporation

# int<sub>el®</sub> Contents

| 1 | About       | This Do        | cument                                                                                                                                                 | .15                             |

|---|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   | 1.1<br>1.2  |                | nce Documents<br>ology and Conventions<br>Representing Numbers<br>Fields<br>Specifying Bit and Signal Values<br>Signal Name Conventions<br>Terminology | .16<br>.16<br>.16<br>.17<br>.17 |

| 2 | Overv       |                |                                                                                                                                                        |                                 |

|   | 2.1         |                | 9S                                                                                                                                                     |                                 |

|   | 2.1         |                | nterface                                                                                                                                               |                                 |

|   | 2.2         |                | mmands Supported in M/S (PCI IDE) Mode                                                                                                                 |                                 |

|   | 2.0         | 2.3.1          | PCI Commands Supported in DPA Mode                                                                                                                     |                                 |

|   | 2.4         | Serial A       | ATA Interface                                                                                                                                          |                                 |

|   | 2.5         | Modes          | of Operation                                                                                                                                           | .27                             |

|   |             | 2.5.1          | Master/Slave Mode (or PCI IDE Mode)                                                                                                                    | .27                             |

|   |             | 2.5.2          | Direct Port Access Mode                                                                                                                                |                                 |

|   |             | 2.5.3          | Selecting DPA or M/S Mode                                                                                                                              |                                 |

|   |             | 2.5.4          | DPA Mode Port Initialization                                                                                                                           |                                 |

|   | 2.6         |                | EPROM Interface                                                                                                                                        |                                 |

|   | 2.7         |                | ed Voltage Mode                                                                                                                                        |                                 |

|   | 2.8         |                | TY LEDS                                                                                                                                                |                                 |

|   | 2.9         | 2.8.1          | Reference Clock Generation                                                                                                                             |                                 |

|   | 2.9<br>2.10 |                | nd Storage Features<br>nterface                                                                                                                        |                                 |

| 0 |             |                |                                                                                                                                                        |                                 |

| 3 |             |                | Μ                                                                                                                                                      |                                 |

|   | 3.1         |                | tatus Register (WRSR) Command                                                                                                                          |                                 |

|   |             | 3.1.1          | PROGRAM Command                                                                                                                                        |                                 |

|   |             | 3.1.2          | READ Command                                                                                                                                           |                                 |

|   |             | 3.1.3          | Write Disable (WRDI) Command                                                                                                                           |                                 |

|   |             | 3.1.4<br>3.1.5 | Read Status Register (RDSR) Command                                                                                                                    |                                 |

|   |             | 3.1.5          | Write Enable (WREN) Command<br>Sector Erase (SECT_ERASE) Command                                                                                       |                                 |

|   |             | 3.1.7          | CHIP ERASE Command                                                                                                                                     |                                 |

|   |             | 3.1.8          | Read ID Register (RDID) Command                                                                                                                        |                                 |

|   |             | 3.1.9          | Serial EEPROM SPI Interface – Address 90h                                                                                                              |                                 |

|   |             | 01110          | 3.1.9.1 Programming Details                                                                                                                            |                                 |

|   |             |                | 3.1.9.2 SPI Command / Control / Status Register - Address 90h                                                                                          |                                 |

|   |             |                | 3.1.9.2.1 SPI Command                                                                                                                                  | .45                             |

|   |             |                | 3.1.9.2.2 SPI Control                                                                                                                                  |                                 |

|   |             |                | 3.1.9.2.3 SPI Status                                                                                                                                   |                                 |

|   |             | 2 1 10         | 3.1.9.3 SPI Data Register - Address 94h                                                                                                                |                                 |

|   |             | 3.1.10         | Detection of the EEPROM at Power-Up                                                                                                                    | .40                             |

| 4 | Funct | ional Blo | cks                                                                                                          | 48 |

|---|-------|-----------|--------------------------------------------------------------------------------------------------------------|----|

|   | 4.1   | Serial A  | TA                                                                                                           | 48 |

|   |       | 4.1.1     | Out-of-Band Signaling                                                                                        |    |

|   | 4.2   | Operat    | onal Blocks                                                                                                  |    |

|   |       | 4.2.1     | Serial Engine                                                                                                |    |

|   |       | 4.2.2     | Register Interface                                                                                           |    |

|   |       | 4.2.3     | DMA Controller                                                                                               |    |

|   |       |           | 4.2.3.1 DMA Operation                                                                                        |    |

|   |       |           | 4.2.3.2 Data Synchronization                                                                                 |    |

|   |       |           | 4.2.3.3 DMA Error Conditions                                                                                 |    |

|   |       |           | 4.2.3.4 DMA Throughput                                                                                       |    |

|   |       | 4.2.4     | Programmed I/O (PIO)                                                                                         | 62 |

|   |       | 4.2.5     | Serial ATA II Native Command Queuing                                                                         | 63 |

|   |       |           | 4.2.5.1 Race-free Status Return Mechanism                                                                    |    |

|   |       |           | 4.2.5.2 Interrupt Aggregation                                                                                |    |

|   |       |           | 4.2.5.3 First Party DMA (FPDMA)                                                                              | 65 |

| 5 | Progr | ammina    | nterface                                                                                                     | 66 |

| 0 | -     | -         |                                                                                                              |    |

|   | 5.1   |           | Mode                                                                                                         |    |

|   |       | 5.1.1     | Native-PCI Mode                                                                                              |    |

|   | 5.2   |           | ort Access Mode                                                                                              |    |

|   |       | 5.2.1     | Common Serial ATA Port Registers                                                                             |    |

|   |       | 5.2.2     | Command Block Registers                                                                                      |    |

|   |       | 5.2.3     | Control Block Registers                                                                                      |    |

|   |       | 5.2.4     | DMA Controller Registers                                                                                     |    |

|   |       | 5.2.5     | SATA Superset Registers                                                                                      |    |

|   | 5.3   |           | mmand Processing                                                                                             |    |

|   |       | 5.3.1     | LBA Addressing in PCI IDE Mode                                                                               |    |

|   |       | 5.3.2     | LBA Addressing in DPA Mode                                                                                   |    |

|   | 5.4   |           | nitialization                                                                                                |    |

|   | 5.5   |           | TA BIST                                                                                                      |    |

|   |       | 5.5.1     | Loopback Mode Testing                                                                                        |    |

|   |       | 5.5.2     | Transmit-Only Mode Testing                                                                                   |    |

|   | 5.6   |           | Error Conditions                                                                                             |    |

|   |       | 5.6.1     | Address and Attribute Parity Errors on the PCI Interface                                                     |    |

|   |       | 5.6.2     | Data Parity Errors on the PCI Interface                                                                      |    |

|   |       |           | 5.6.2.1 Outbound Read Request Data Parity Errors                                                             |    |

|   |       |           | 5.6.2.1.1 Immediate Data Transfer                                                                            |    |

|   |       |           | 5.6.2.1.2 Split Response Termination                                                                         |    |

|   |       |           | 5.6.2.2 Outbound Write Request Data Parity Errors                                                            |    |

|   |       |           | 5.6.2.2.1 Outbound Writes that are Not MSI (Message Signaled Interrupts). 8<br>5.6.2.2.2 MSI Outbound Writes |    |

|   |       |           | 5.6.2.3 Inbound Read Request Data Parity Errors                                                              |    |

|   |       |           | 5.6.2.3.1 Immediate Data Transfer                                                                            | 87 |

|   |       |           | 5.6.2.4 Inbound Write Request Data Parity Errors                                                             |    |

|   |       |           | 5.6.2.5 Outbound Read Completion Data Parity Errors                                                          |    |

|   |       |           | 5.6.2.6 Split Completion Messages                                                                            |    |

|   |       | 5.6.3     | Master Aborts on the PCI Interface                                                                           |    |

|   |       |           | 5.6.3.1 Master-Aborts Signaled by Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller                    |    |

|   |       |           | as an Initiator                                                                                              | 89 |

|   |       |           | 5.6.3.1.1 Master Aborts for Outbound Read or Write Request                                                   | 89 |

|      |                  | 5.6.3.2            | Master-Aborts Signaled by Intel <sup>®</sup> 31244 PCI-X to Serial ATA Con<br>as a Target   |          |

|------|------------------|--------------------|---------------------------------------------------------------------------------------------|----------|

|      |                  | 563                | 3.2.1 Unsupported PCI Commands                                                              | 90<br>90 |

|      |                  |                    | 3.2.2 PCI IDE Control Block Registers                                                       |          |

|      | 5.6.4            |                    | Aborts on the PCI Interface                                                                 |          |

|      |                  | 5.6.4.1            | Target Aborts for Outbound Read Request or Outbound                                         |          |

|      |                  |                    | Write Request                                                                               | 91       |

|      |                  | 5.6.4.2            | Target-Aborts Signaled by Intel <sup>®</sup> 31244 PCI-X to Serial ATA Cor                  | ntroller |

|      |                  |                    | as a Target                                                                                 | 92       |

|      |                  | 5.6.4              | 4.2.1 Configuration Read and Write                                                          |          |

|      |                  |                    | 4.2.2 I/O Read and Write                                                                    |          |

|      |                  |                    | 4.2.3 Memory Read                                                                           |          |

|      | 5.6.5            | -                  | ed or Unexpected Split Completions                                                          |          |

|      |                  | 5.6.5.1<br>5.6.5.2 | Completer Address                                                                           |          |

|      | FCC              |                    | Completer Attributes                                                                        |          |

|      | 5.6.6            |                    | Assertion and Detection                                                                     |          |

|      | 5.6.7            |                    | or Summary                                                                                  |          |

| 5.7  |                  |                    | and Device Error Conditions<br>TA Device Error Conditions                                   |          |

|      | 5.7.1            |                    | TA Bus and Protocol Error Conditions                                                        |          |

| - 0  | 5.7.2            |                    |                                                                                             |          |

| 5.8  |                  |                    | rupt Generation                                                                             |          |

| 5.9  | -                |                    | ed Interrupts<br>riggered Versus Edge-Triggered Interrupts                                  |          |

| E 10 | 5.9.1<br>Degiate |                    |                                                                                             |          |

| 5.10 |                  |                    | ons<br>Mode Registers                                                                       |          |

|      |                  |                    |                                                                                             |          |

|      | 5.10.Z           |                    | nfiguration Registers<br>SU Vendor ID Register - SUVID                                      |          |

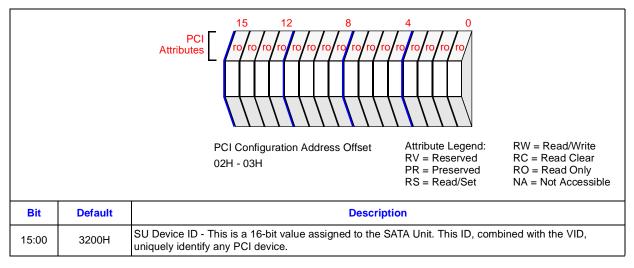

|      |                  | 5.10.2.1           | SU Device ID Register - SUDID                                                               | 109      |

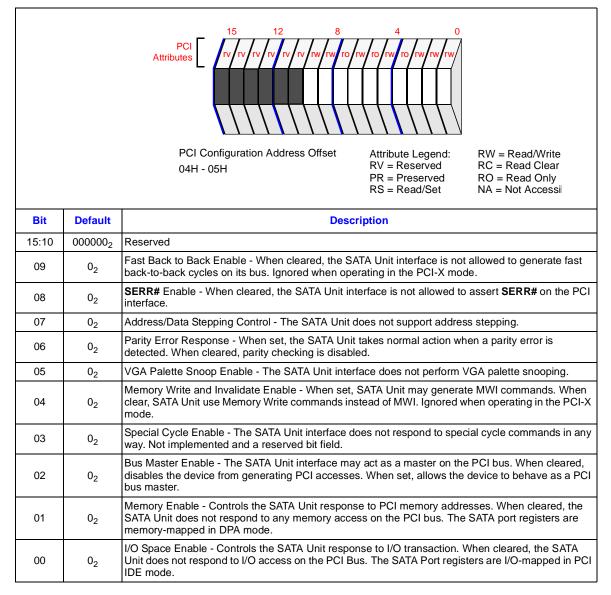

|      |                  |                    | SU Command Register - SUCMD                                                                 |          |

|      |                  | 5 10 2 4           | SU Status Register - SUSR                                                                   | 112      |

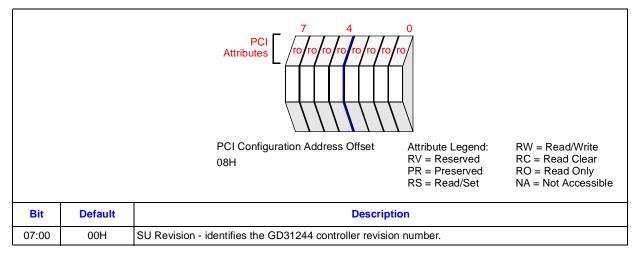

|      |                  | 5.10.2.5           | SU Revision ID Register - SURID                                                             |          |

|      |                  | 5.10.2.6           | SU Class Code Register - SUCCR                                                              |          |

|      |                  | 5.10.2.7           | SU Cacheline Size Register - SUCLSR                                                         | 115      |

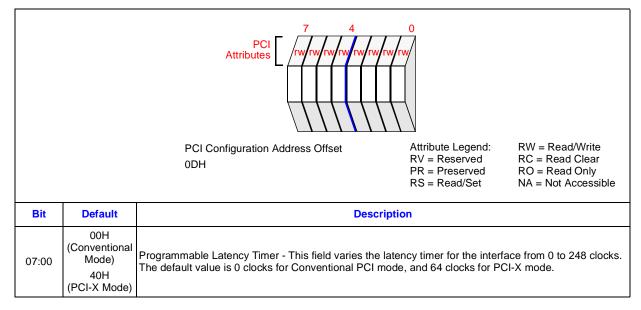

|      |                  | 5.10.2.8           | SU Latency Timer Register - SULT                                                            | 116      |

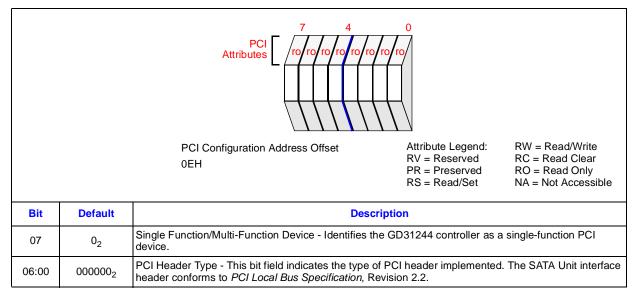

|      |                  | 5.10.2.9           | SU Header Type Register - SUHTR                                                             | 117      |

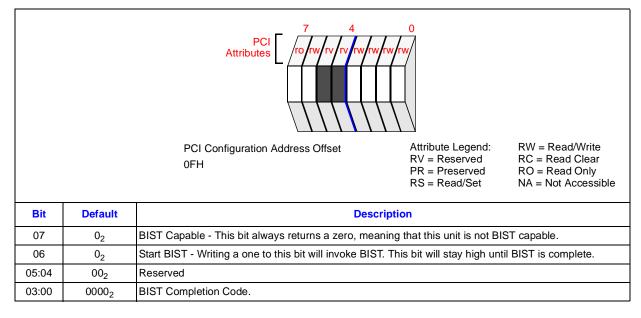

|      |                  | 5.10.2.1           | 0 SU BIST Register - SUBISTR                                                                |          |

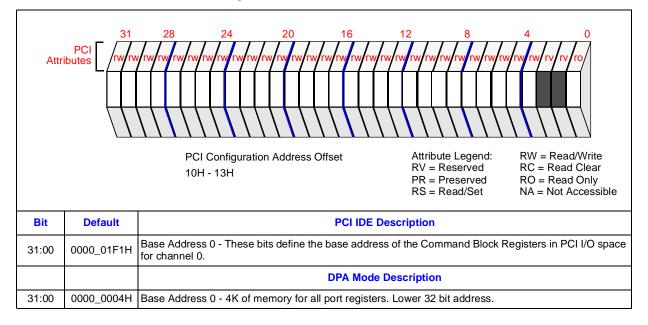

|      |                  |                    | 1 SU Base Address Register 0 - SUBAR0                                                       |          |

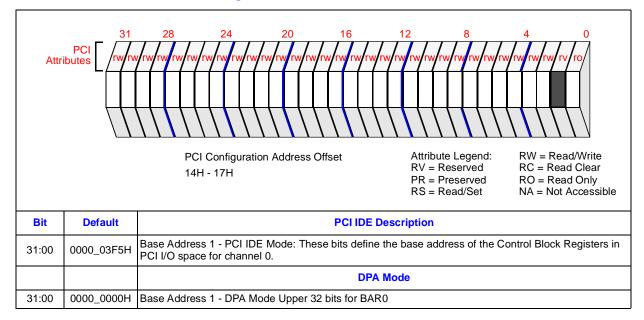

|      |                  |                    | 2 SU Base Address Register 1 - SUBAR1<br>3 SU Base Address Register 2 - SUBAR2              |          |

|      |                  |                    | 4 SU Base Address Register 3 - SUBAR2                                                       |          |

|      |                  |                    | 5 SU Base Address Register 4 - SUBAR4                                                       |          |

|      |                  |                    | 6 SU Base Address Register 5 - SUBAR5                                                       |          |

|      |                  |                    | 7 SU Subsystem Vendor ID Register - SUSVIR                                                  |          |

|      |                  |                    |                                                                                             |          |

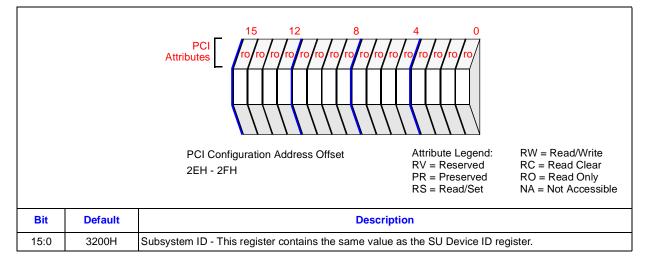

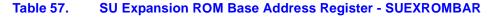

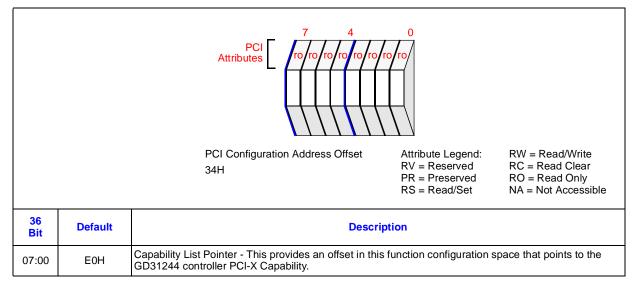

|      |                  | 5.10.2.1           | 8 SU Subsystem ID Register - SUSIR<br>9 SU Expansion ROM Base Address Register - SUEXROMBAR | 127      |

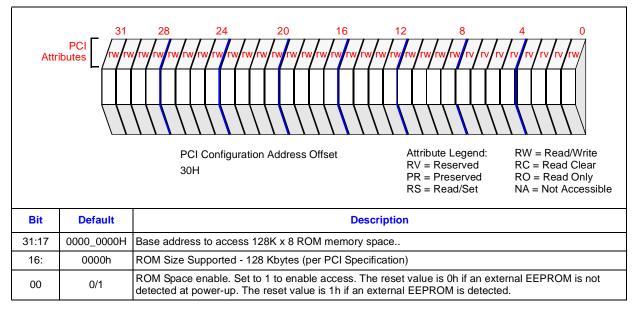

|      |                  | 5.10.2.2           | 20 SU Capabilities Pointer Register - SU_Cap_Ptr                                            |          |

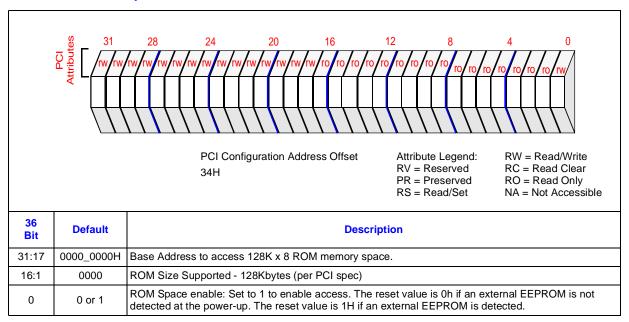

|      |                  | 5.10.2.2           | 1 SU Expansion ROM Base Address - SUEXROM                                                   |          |

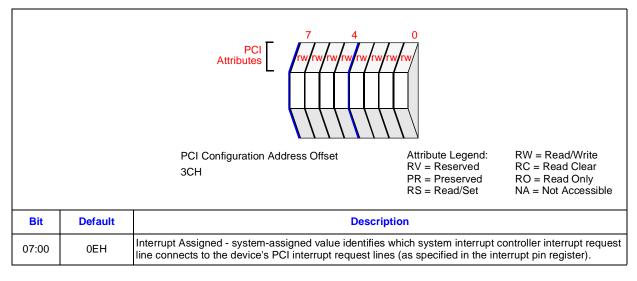

|      |                  | 5.10.2.2           | 2 SU Interrupt Line Register - SUILR                                                        | 130      |

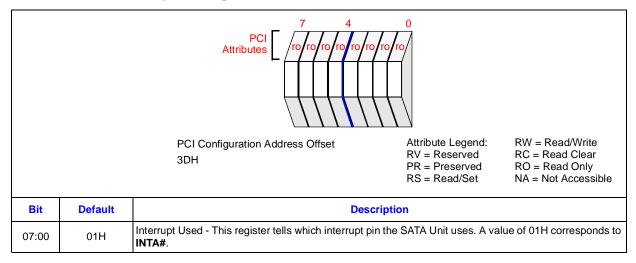

|      |                  | 5.10.2.2           | 3 SU Interrupt Pin Register - SUIPR                                                         |          |

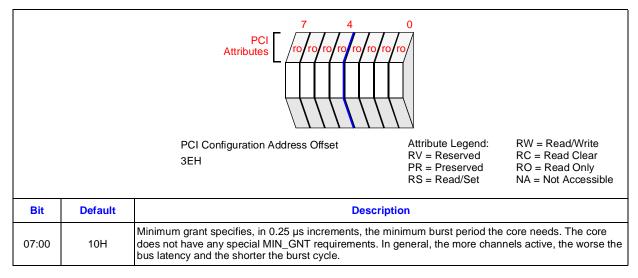

|      |                  |                    | 4 SU Minimum Grant Register - SUMGNT                                                        |          |

|      |                  |                    | 25 SU Maximum Latency Register - SUMLAT                                                     |          |

|      |                  |                    | 6 SPI Command Register - SPICMDR<br>7 SPI Control Register - SPICNTR                        |          |

|      |                  | J. 10.Z.Z          |                                                                                             |          |

|                                                               | 5.10.2.28 | SPI Status Register - SPISTATR                                                     | 136   |

|---------------------------------------------------------------|-----------|------------------------------------------------------------------------------------|-------|

|                                                               | 5.10.2.29 | SPI Data Register - SPIDATR<br>SU Extended Control and Status Register 0 - SUECSR0 | 137   |

|                                                               | 5.10.2.30 | ) SU Extended Control and Status Register 0 - SUECSR0                              | 138   |

|                                                               | 5.10.2.31 | SU DMA Control Status Register- SUDCSCR                                            | 139   |

|                                                               | 5.10.2.32 | 2 SU Dummy Register SUDR                                                           | 140   |

|                                                               |           | SU Interrupt Status Register SUISR                                                 |       |

|                                                               |           | SU Interrupt Mask Register SUIMR                                                   |       |

|                                                               |           | SU Transaction Control SUTCR                                                       |       |

|                                                               |           | SU Target Split Completion Message Enable Register SUTSCMER                        |       |

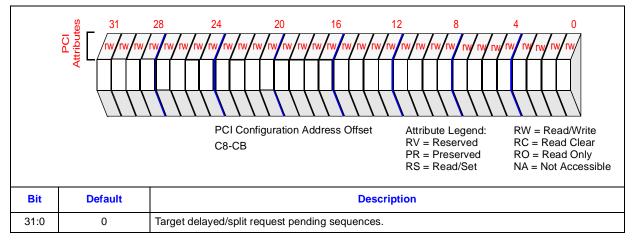

|                                                               | 5.10.2.37 | 7 SU Target Delayed/Split Request Pending Register SUDRPR                          | 145   |

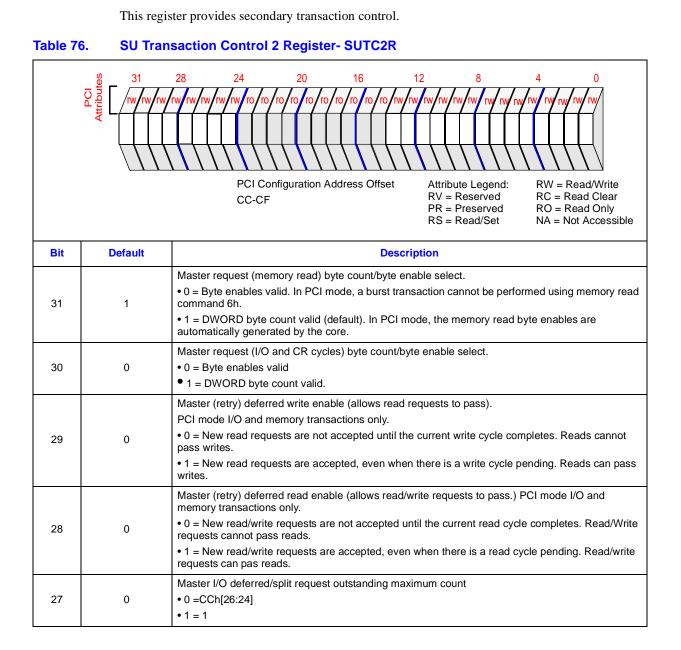

|                                                               |           | SU Transaction Control 2 Register SUTC2R                                           |       |

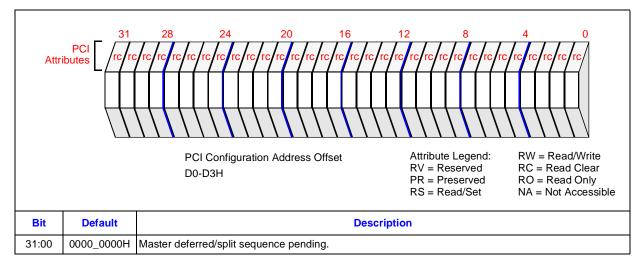

|                                                               |           | SU Master Deferred/Split Sequence Pending Register - SUMDSPR                       | 148   |

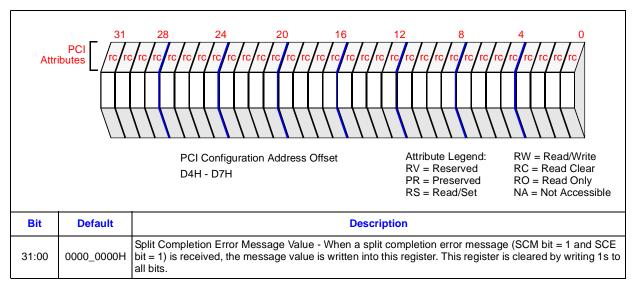

|                                                               | 5.10.2.40 | ) SU Master Split Completion Message Received                                      | 1 1 0 |

|                                                               | E 10 0 11 | with Error Message Register - SUMSCMREMR                                           | 149   |

|                                                               |           | 2 SU PCI-X Capability Identifier Register - SUPCI-X_Cap_ID                         |       |

|                                                               |           | SU PCI-X Capability Identifier Register - SUPCI-X_Cap_ID                           |       |

|                                                               |           | SUPCI-X Next hell Follier Register - SUPCI-X_Next_hell_Fit                         |       |

|                                                               |           | 5 SU PCI-X Status Register - SUPCIXSR                                              |       |

|                                                               | 5 10 2 40 | SUPM Capability Identifier Register - SUPM_Cap_ID                                  | 156   |

|                                                               |           | SUPM Next Item Pointer Register - SUPM_Next_Item_Ptr                               |       |

|                                                               |           | SU Power Management Capabilities Register - SUPMCR                                 |       |

|                                                               | 5 10 2 49 | SU Power Management Control/Status Register - SUPMCSR                              | 159   |

|                                                               |           | ) SU MSI Capability Identifier Register - SUMSI_Cap_ID                             |       |

|                                                               |           | SU MSI Next Item Pointer Register - SUMSI_Next_Ptr                                 |       |

|                                                               |           | 2 SU MSI Message Control Register - SUMSI_Message_Control                          |       |

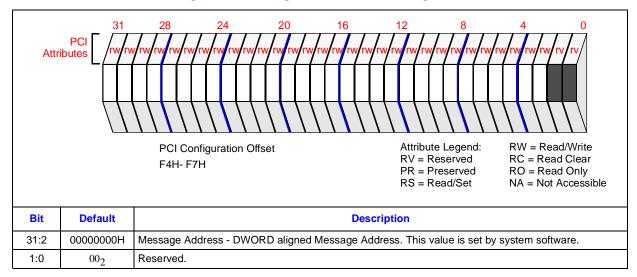

| 5.10.2.53 SU MSI Message Address Register - SUMSI_Message_Add |           |                                                                                    |       |

|                                                               |           | I SU MSI Massaga Upper Address Pagister -                                          |       |

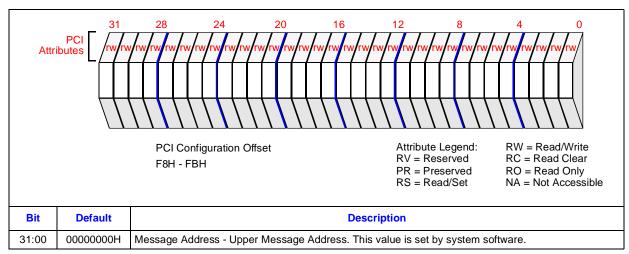

|                                                               |           | SUMSI Message Upper_Address Register -                                             | 164   |

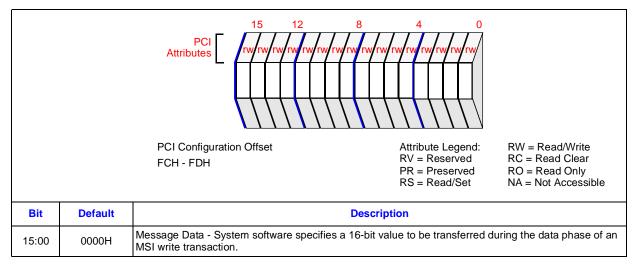

|                                                               | 5.10.2.55 | 5 SU MSI Message Data Register- SUMSI_Message_Data                                 | 165   |

| 5.10.3                                                        |           | DE Mode Command Block Registers                                                    |       |

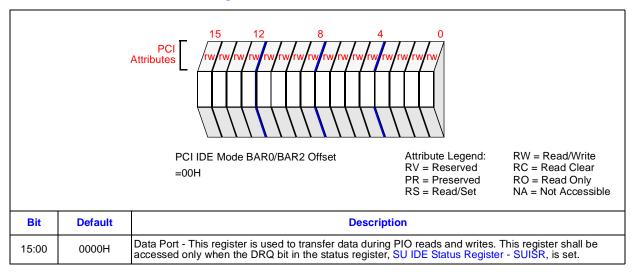

|                                                               |           | SU IDE Data Port Register - SUIDR                                                  |       |

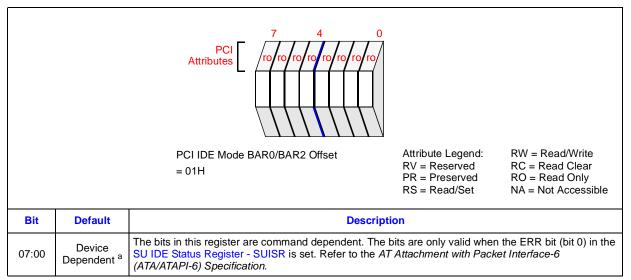

|                                                               |           | SU IDE Error Register - SUIER                                                      |       |

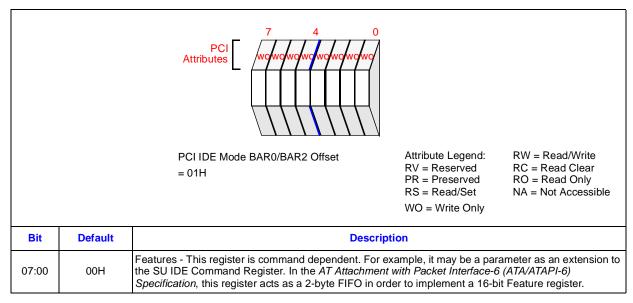

|                                                               | 5.10.3.3  | SU IDE Features Register - SUIFR                                                   | 168   |

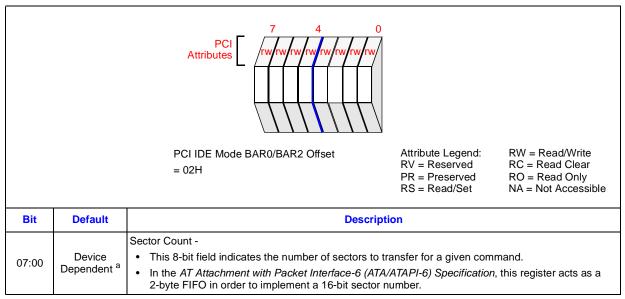

|                                                               | 5.10.3.4  | SU IDE Features Register - SUIFR<br>SU IDE Sector Count Register - SUISCR          | 169   |

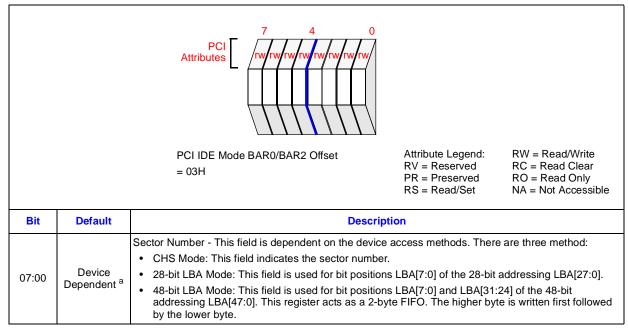

|                                                               | 5.10.3.5  | SU IDE Sector Number Register - SUISNR                                             | 170   |

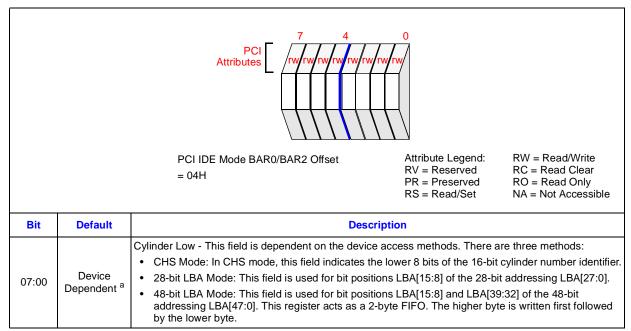

|                                                               | 5.10.3.6  | SU IDE Cylinder Low Register - SUICLR                                              | 171   |

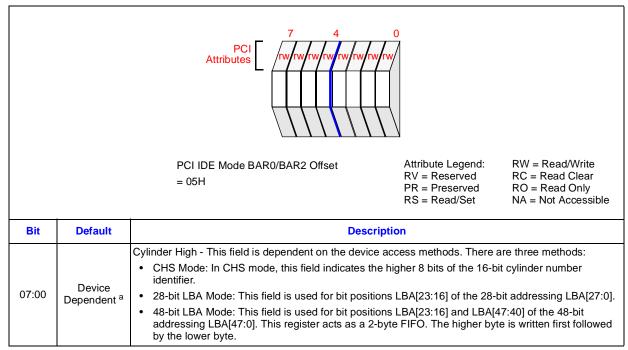

|                                                               | 5.10.3.7  | SU IDE Cylinder High Register - SUICHR                                             | 172   |

|                                                               |           | SU IDE Device/Head Register - SUIDR                                                |       |

|                                                               |           | SU IDE Status Register - SUISR                                                     |       |

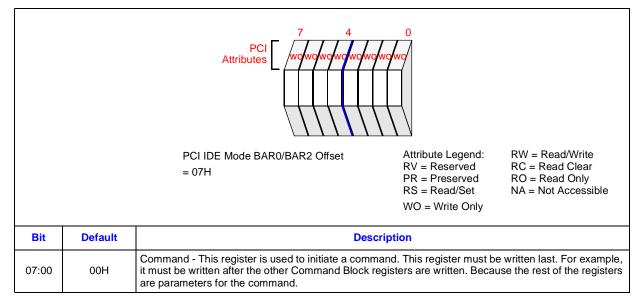

|                                                               | 5.10.3.10 | ) SU IDE Command Register - SUICR                                                  | 175   |

| 5.10.4                                                        |           | DE Mode Control Block Registers                                                    |       |

|                                                               | 5.10.4.1  | SU IDE Device Control Register - SUIDCR                                            | 176   |

|                                                               | 5.10.4.2  | SU IDE Alternate Status Register - SUIASR                                          | 177   |

| 5.10.5                                                        | SU PCI I  | DE Mode DMA Registers                                                              | 178   |

|                                                               | 5.10.5.1  | SU IDE Channel 0 DMA Command Register - SUICDCR0                                   | 178   |

|                                                               |           | SU IDE Channel 0 DMA Status Register - SUICDSR0                                    |       |

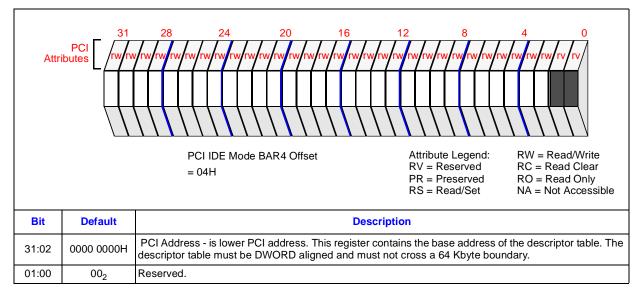

|                                                               | 5.10.5.3  | SU IDE Channel 0 DMA Descriptor Table                                              |       |

|                                                               |           | Pointer Register - SUICDDTPR0                                                      |       |

|                                                               |           | SU IDE Channel 1 DMA Command Register - SUICDCR1                                   |       |

|                                                               |           | SU IDE Channel 1 DMA Status Register - SUICDSR1                                    | 182   |

|                                                               | 5.10.5.6  | SU IDE Channel 1 DMA Descriptor Table                                              |       |

|                                                               |           | Pointer Register - SUICDDTPR1                                                      |       |

| 5.10.6                                                        | SU PCI [  | DPA Mode Registers                                                                 | 184   |

| 5.10.7  | SU PCI DPA Mode Base Address Registers                                           | .192 |

|---------|----------------------------------------------------------------------------------|------|

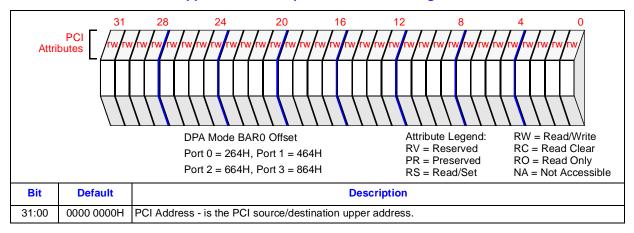

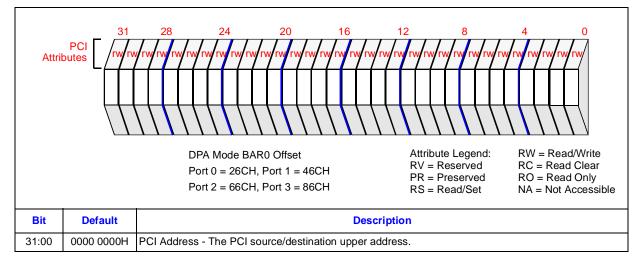

|         | 5.10.7.1 SU PCI DPA Base Address Register 0 - SUPDBAR0                           | 192  |

|         | 5.10.7.2 SU PCI DPA Upper Base Address Register 0 - SUPDUBAR0                    | .193 |

| 5.10.8  | SU PCI DPA Mode Common SATA Port Registers                                       | .194 |

|         | 5.10.8.1 SU PCI DPA Interrupt Pending Register - SUPDIPR                         | 194  |

|         | 5.10.8.2 SU PCI DPA Interrupt Mask Register - SUPDIMR                            | 200  |

| 5.10.9  | SU PCI DPA Mode Command Block Registers                                          | 203  |

|         | 5.10.9.1 SU PCI DPA Data Port Register - SUPDDR                                  | 203  |

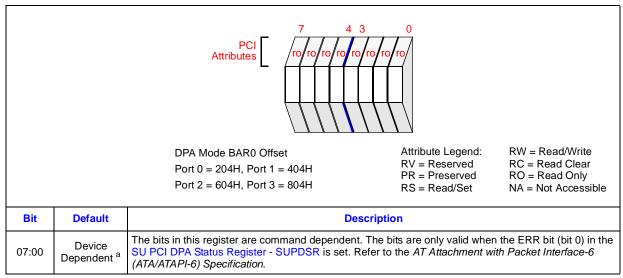

|         | 5.10.9.2 SU PCI DPA Error Register - SUPDER                                      | .204 |

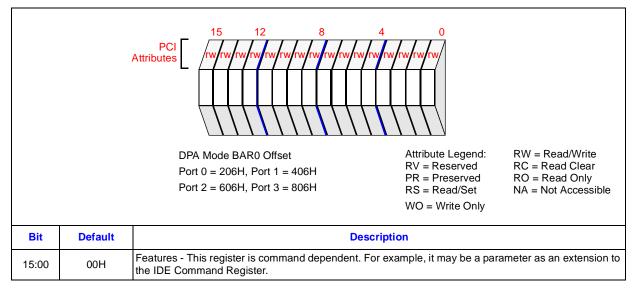

|         | 5.10.9.3 SU PCI DPA Features Register - SUPDFR                                   |      |

|         | 5.10.9.4 SU PCI DPA Sector Count Register - SUPDSCR                              | .206 |

|         | 5.10.9.5 SU PCI DPA Sector Number Register - SUPDSNR                             |      |

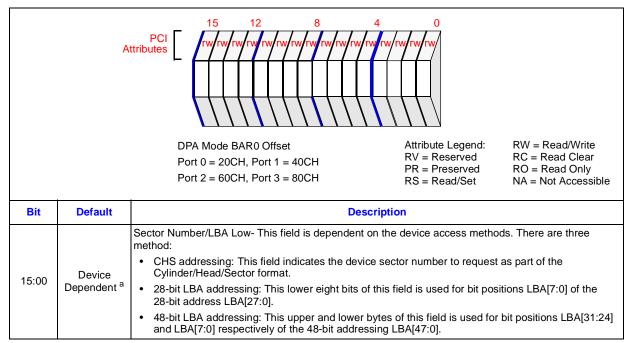

|         | 5.10.9.6 SU PCI DPA Cylinder Low Register - SUPDCLR                              | .208 |

|         | 5.10.9.7 SU PCI DPA Cylinder High Register - SUPDCHR                             |      |

|         | 5.10.9.8 SU PCI DPA Device/Head Register - SUPDDR                                |      |

|         | 5.10.9.9 SU PCI DPA Status Register - SUPDSR                                     |      |

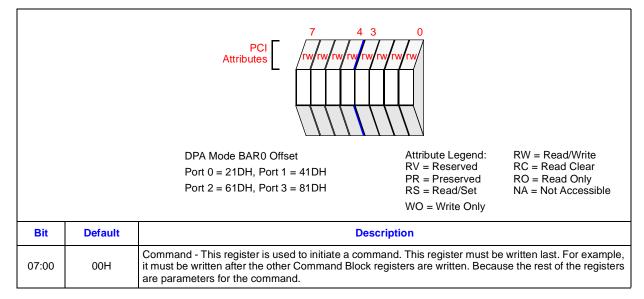

| E 40 4  | 5.10.9.10 SU PCI DPA Command Register - SUPDCR                                   |      |

| 5.10.10 | 0 SU PCI DPA Mode Control Block Registers                                        | .213 |

|         | 5.10.10.1 SU PCI DPA Alternate Status Register - SUPDASR                         | 213  |

| E 40 4  | 5.10.10.2 SU PCI DPA Device Control Register - SUPDDCTLR                         | .214 |

| 5.10.1  | 1 SU PCI DPA Mode DMA Registers                                                  |      |

|         | 5.10.11.1 SU PCI DPA Upper DMA Descriptor Table<br>Pointer Register - SUPDUDDTPR | 045  |

|         | 5.10.11.2 SU PCI DPA Upper DMA Data Pointer Register - SUPDUDDBPR                | 215  |

|         | 5.10.11.2 SU PCI DPA DMA Command Register - SUPDDCMDR                            |      |

|         | 5.10.11.4 SU PCI DPA DMA Status Register - SUPDDSR                               | 218  |

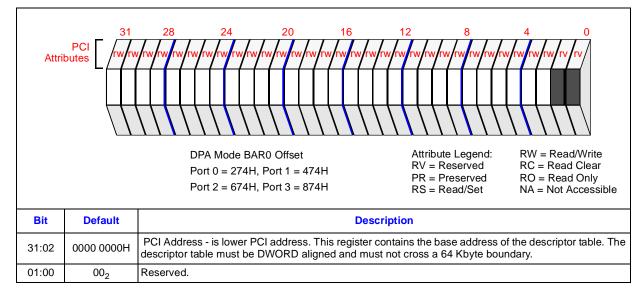

|         | 5.10.11.5 SU PCI DPA DMA Descriptor Table Pointer Register - SUPDDDTPR           | 210  |

| 5 10 1  | 2 SU PCI DPA Mode Superset Registers                                             |      |

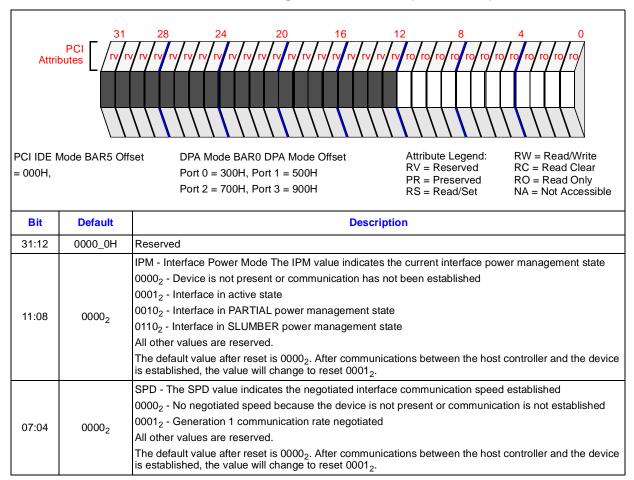

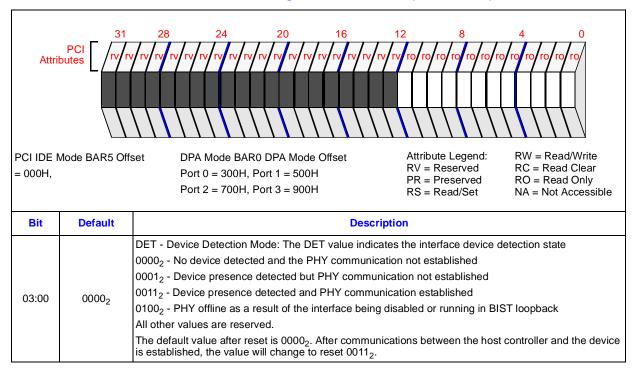

| 0.10.17 | 5.10.12.1 SU PCI DPA SATA SStatus Register - SUPDSSSR                            | 220  |

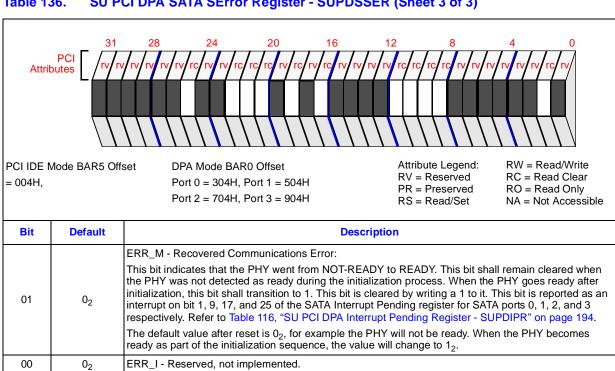

|         | 5.10.12.2 SU PCI DPA SATA SError Register - SUPDSSER                             | 220  |

|         | 5.10.12.3 SU PCI DPA SATA SControl Register - SUPDSSCR                           | 225  |

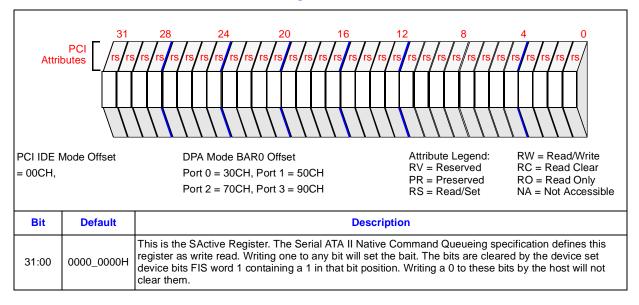

|         | 5.10.12.4 SU PCI DPA Set Device Bits Register - SUPDSDBR                         |      |

|         | 5.10.12.5 SU PCI DPA PHY Feature Register - SUPDPFR                              |      |

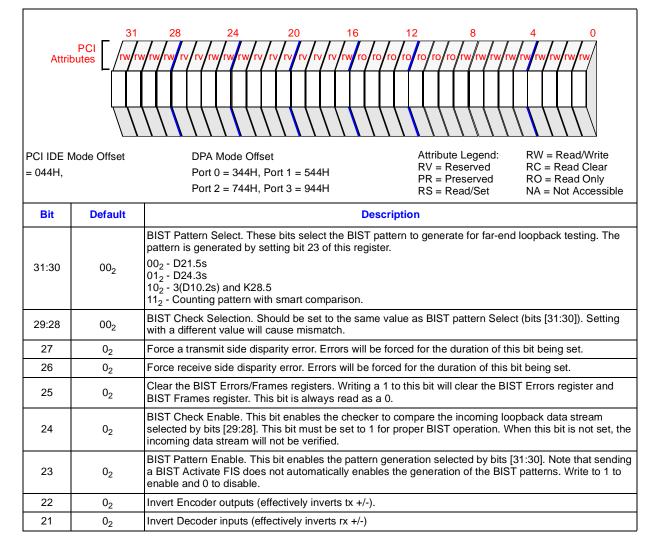

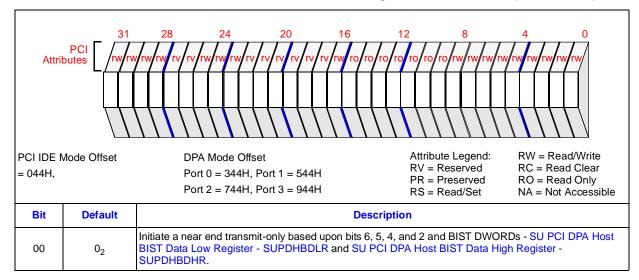

|         | 5.10.12.6 SU PCI DPA BIST FIS Control and Status Register - SUPDBFCSR            | 228  |

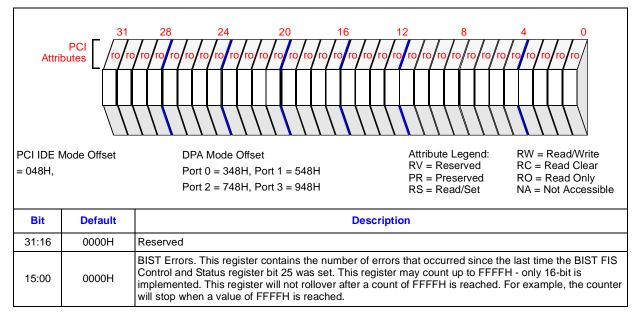

|         | 5.10.12.7 SU PCI DPA BIST Errors Register - SUPDBER                              | .231 |

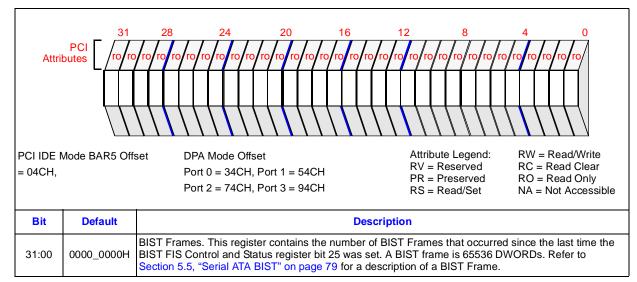

|         | 5.10.12.8 SU PCI DPA BIST Frames Register - SUPDBFR                              | 232  |

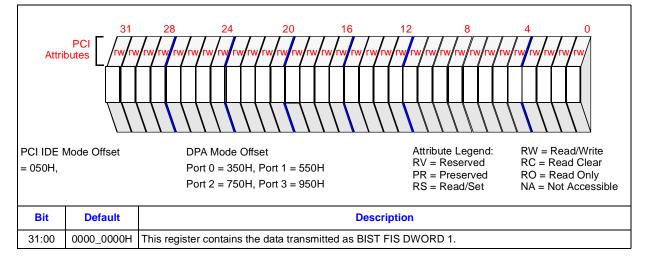

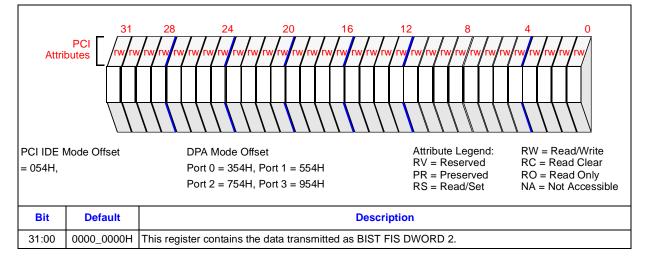

|         | 5.10.12.9 SU PCI DPA Host BIST Data Low Register - SUPDHBDLR                     | 233  |

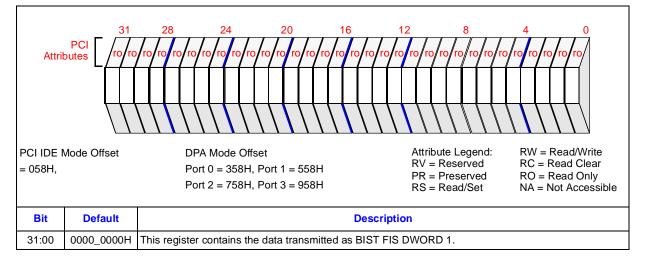

|         | 5.10.12.10SU PCI DPA Host BIST Data High Register - SUPDHBDHR                    |      |

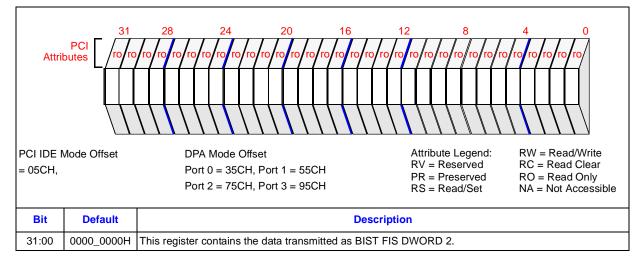

|         | 5.10.12.11SU PCI DPA Device BIST Data Low Register - SUPDDBDLR                   |      |

|         | 5.10.12.12SU PCI DPA Device BIST Data High Register - SUPDDBDHR                  | .236 |

|         | 5.10.12.13SU PCI DPA Queuing Table Base Address Register                         | 007  |

|         | Low - SUPDQTBARL                                                                 | .237 |

|         | 5.10.12.14SU PCI DPA Queuing Table Base Address Register<br>High - SUPDQTBARH    | 220  |

|         | 5.10.12.15SU PCI DPA DMA Setup FIS Control and                                   | 230  |

|         | Status Register - SUPDDSFCSR                                                     | 239  |

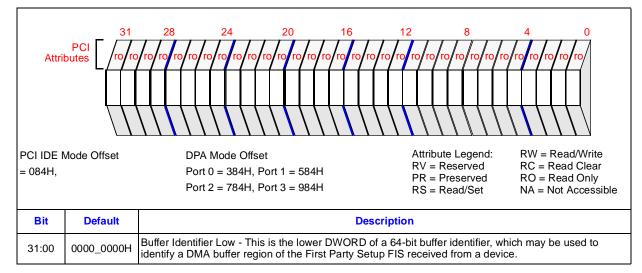

|         | 5.10.12.16SU PCI DPA Host DMA Buffer Identifier                                  | 200  |

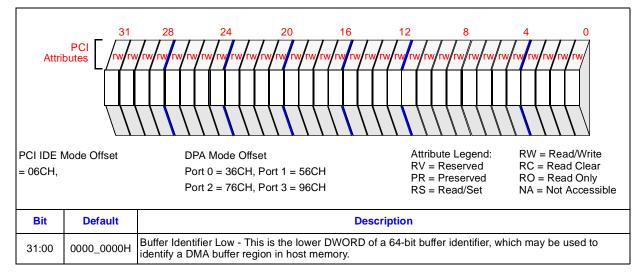

|         | Low Register - SUPDHDBILR                                                        | 240  |

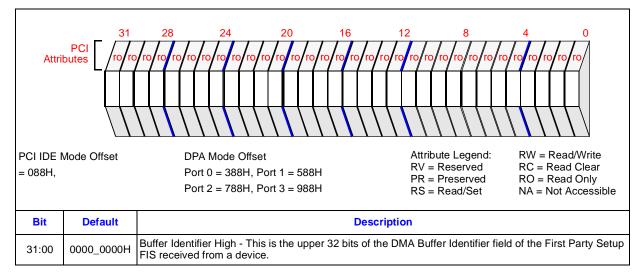

|         | 5.10.12.17SU PCI DPA Host DMA Buffer Identifier                                  |      |

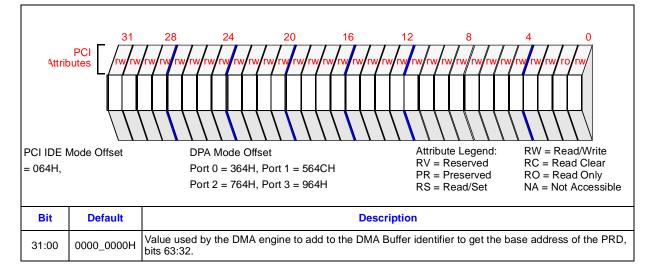

|         | High Register - SUPDHDBIHR                                                       |      |

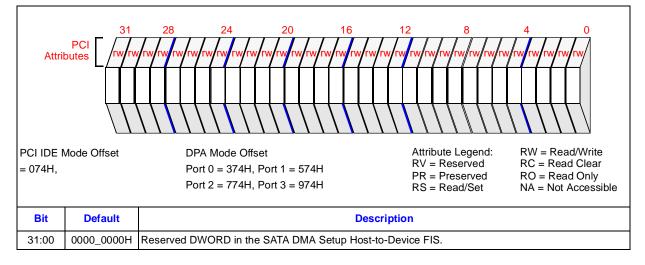

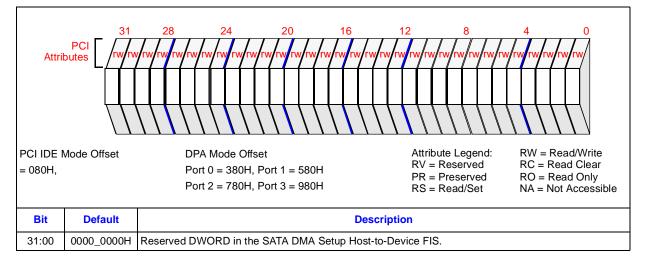

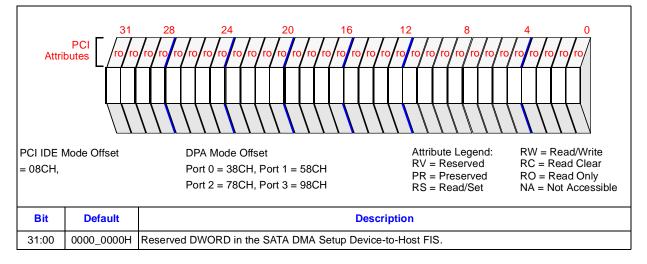

|         | 5.10.12.18SU PCI DPA Host Reserved DWORD Register 0 - SUPDHRDR0                  | .242 |

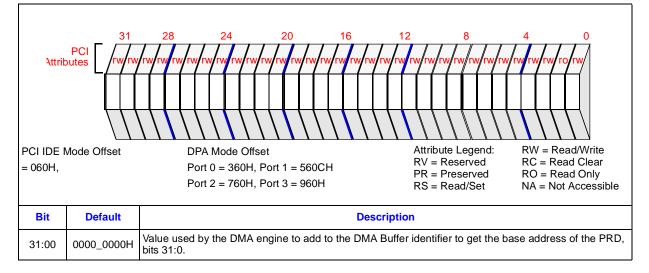

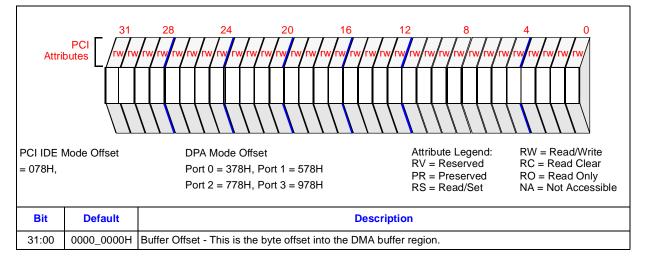

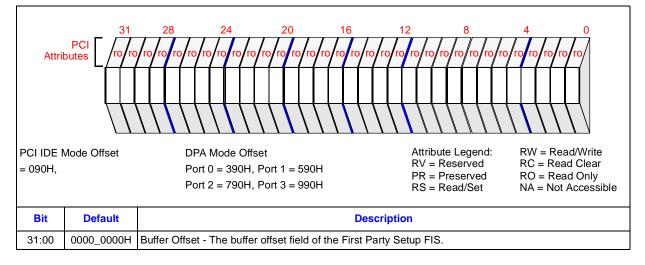

|         | 5.10.12.19SU PCI DPA Host DMA Buffer Offset Register - SUPDHDBOR                 |      |

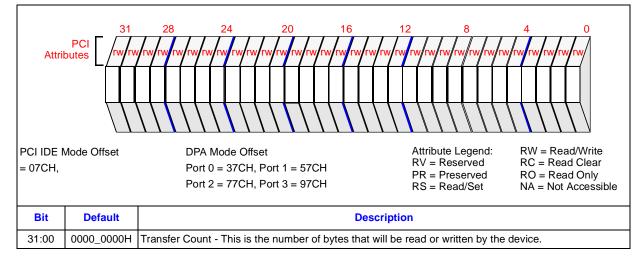

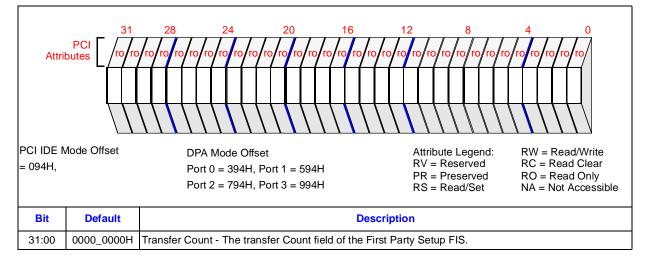

|         | 5.10.12.20SU PCI DPA Host DMA Transfer Count Register - SUPDHDTCR                |      |

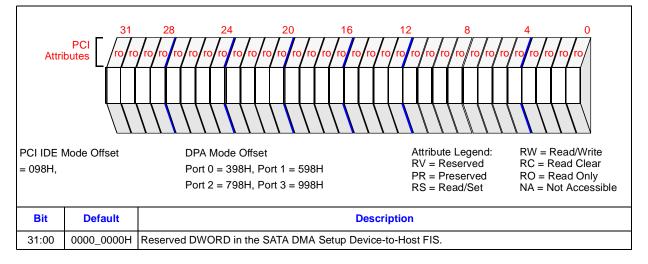

|         | 5.10.12.21SU PCI DPA Host Reserved DWORD Register 1- SUPDHRDR1                   | .245 |

| 5.10.12.22SU PCI DPA Device DMA Buffer Identifier                    |     |

|----------------------------------------------------------------------|-----|

| Low Register - SUPDDDBILR                                            | 246 |

| 5.10.12.23SU PCI DPA Device DMA Buffer Identifier                    |     |

| High Register - SUPDDDBIHR                                           | 247 |

| 5.10.12.24SU PCI DPA Host Reserved DWORD Register 0 - SUPDHRDR0      | 248 |

| 5.10.12.25SU PCI DPA Device DMA Buffer Offset Register - SUPDDDBOR   | 249 |

| 5.10.12.26SU PCI DPA Device DMA Transfer Count Register - SUPDDDTCR. | 250 |

| 5.10.12.27SU PCI DPA Device Reserved DWORD Register 1 - SUPDDRDR1.   | 251 |

|                                                                      |     |

# Figures

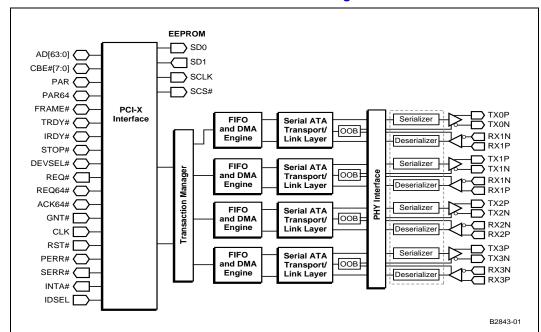

| 1  | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Block Diagram              | .21  |

|----|------------------------------------------------------------------------------------|------|

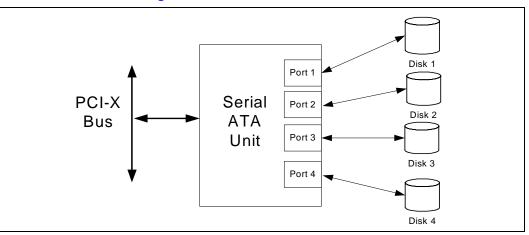

| 2  | Serial ATA Unit Block Diagram                                                      |      |

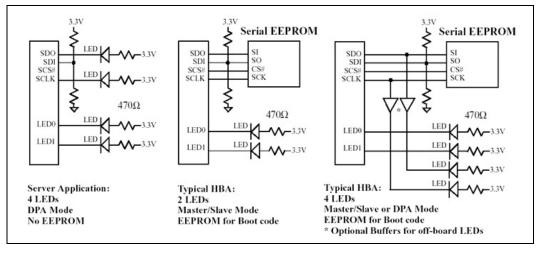

| 3  | Common LED and Serial EEPROM Options                                               | .30  |

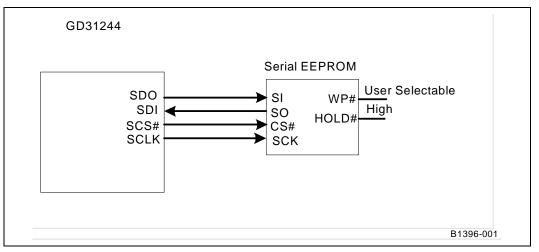

| 4  | Serial EEPROM Interface                                                            |      |

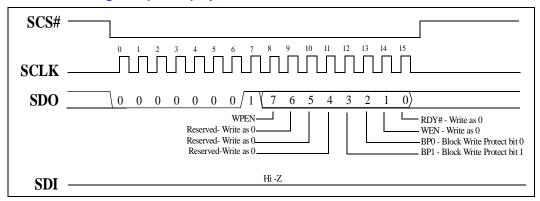

| 5  | Write Status Register (WRSR) Operation                                             | .34  |

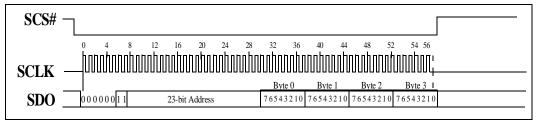

| 6  | Write Memory (PROGRAM) Operation, 4 Byte                                           | . 35 |

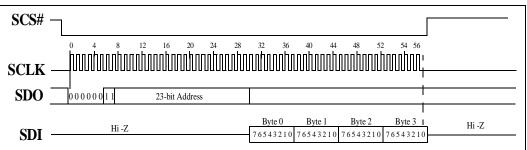

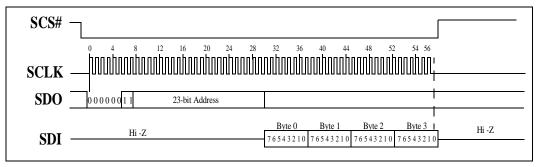

| 7  | Read Memory (READ) Operation, 4 Byte                                               | .36  |

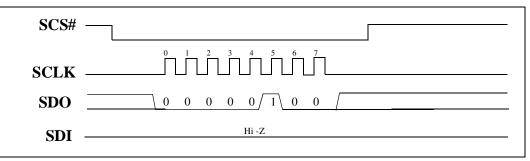

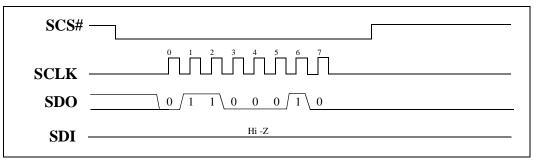

| 8  | Write Disable (WRDI) Operation                                                     | .37  |

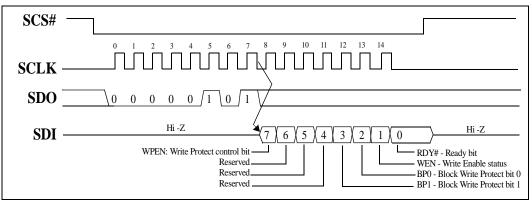

| 9  | Read Status Register (RDSR) Operation                                              | . 38 |

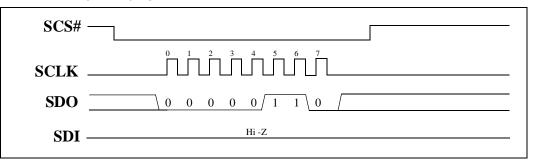

| 10 | Write Enable (WREN) Operation                                                      |      |

| 11 | Sector Erase (SECT_ERASE) Operation                                                | .40  |

| 12 | Chip Erase (CHIP_ERASE) Operation                                                  |      |

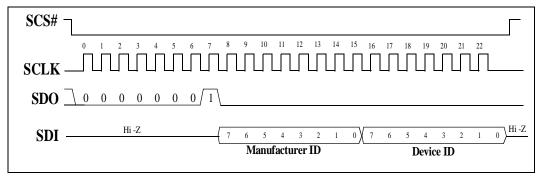

| 13 | Read ID Register (RDID) Operation                                                  | . 42 |

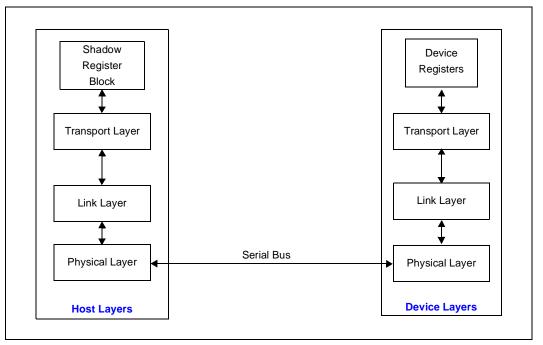

| 14 | SATA Protocol Layers                                                               |      |

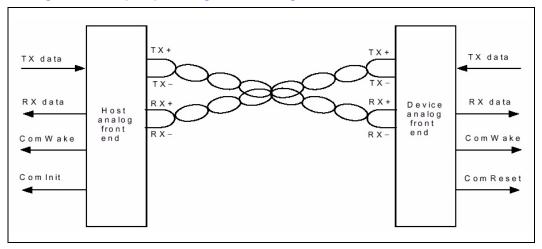

| 15 | Analog Front End (AFE) Cabling and OOB Signals                                     | . 50 |

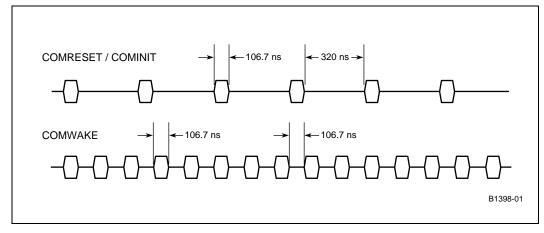

| 16 | OOB Signals Timings                                                                | . 50 |

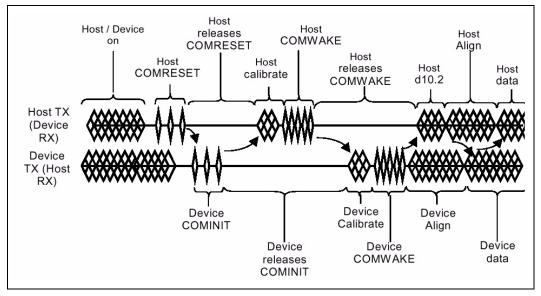

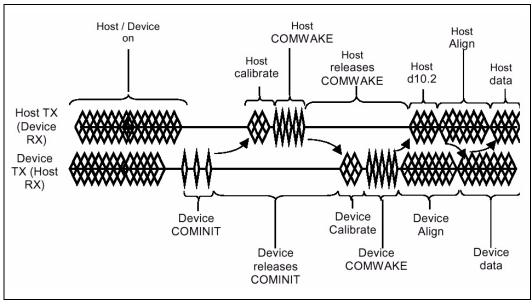

| 17 | COMRESET Sequence                                                                  | .51  |

| 18 | COMINIT Sequence                                                                   |      |

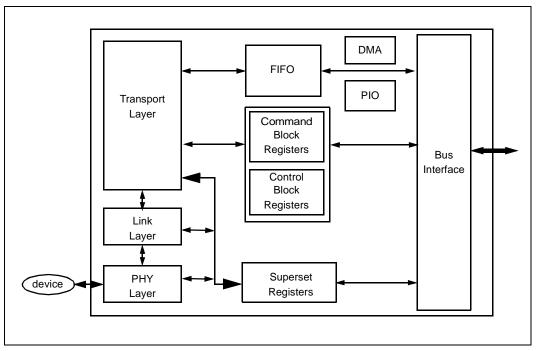

| 19 | SATA Port Block Diagram                                                            |      |

| 20 | DMA Descriptor Table                                                               | .56  |

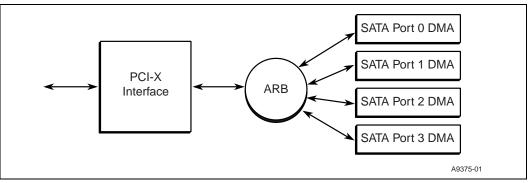

| 21 | DMA Arbitration                                                                    |      |

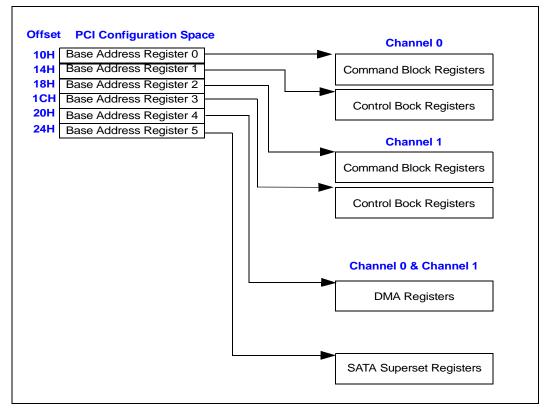

| 22 | SATA Unit Register Mapping in Native-PCI Mode                                      |      |

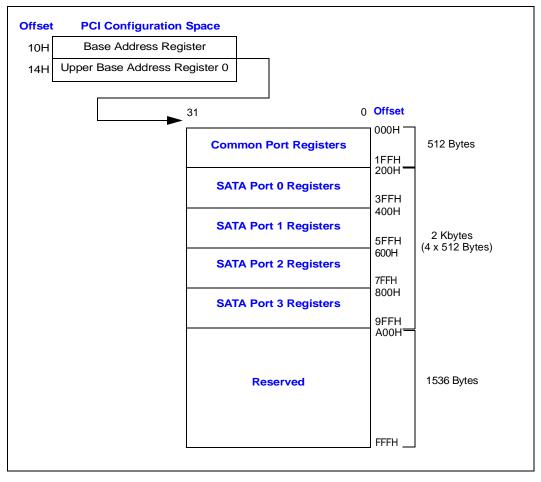

| 23 | SATA Unit Register Mapping in Direct Port Access Mode                              |      |

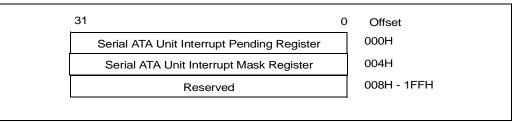

| 24 | Common Serial ATA Port Registers                                                   |      |

| 25 | Command Block Registers for SATA Port 0                                            |      |

| 26 | Control Block Registers for SATA Port 0                                            |      |

| 27 | DMA Controller Registers for SATA Port 0                                           |      |

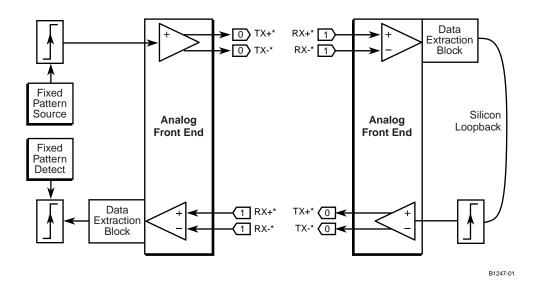

| 28 | Far-End Retimed Loopback Setup                                                     | .79  |

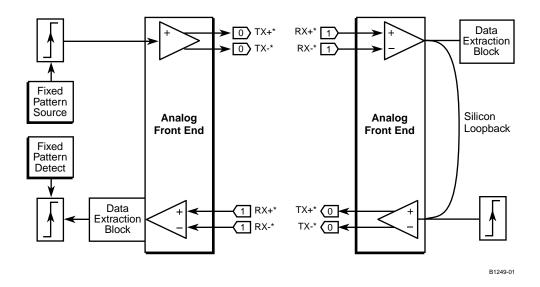

| 29 | Far-End Analog Loopback Setup                                                      | .80  |

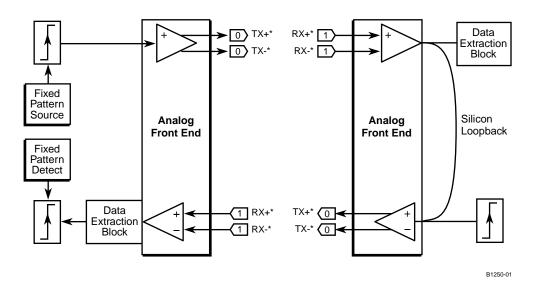

| 30 | Near-End Analog Loopback Setup                                                     | . 80 |

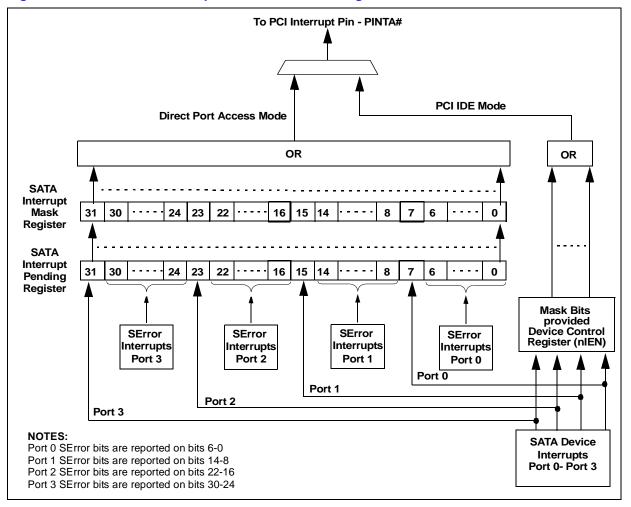

| 31 | SATA Unit Interrupt Generation Block Diagram                                       |      |

| 32 | SU in PCI IDE Mode Interface Configuration Header Format                           |      |

| 33 | SATA Unit Interface Extended Configuration Header Format (PCI-X Capability)        | 104  |

| 34 | SU in PCI IDE Mode Interface Extended Configuration Header                         |      |

|    | Format (Power Management)                                                          |      |

| 35 | SU in PCI IDE Mode Interface Extended Configuration Header Format (MSI Capability) | 105  |

# **Tables**

| 1  | Reference Documents                                           |     |

|----|---------------------------------------------------------------|-----|

| 2  | Terms and Definitions                                         |     |

| 3  | PCI Commands Supported in PCI IDE Mode                        | 23  |

| 4  | PCI Commands Supported in DPA Mode                            | 24  |

| 5  | DPA Mode Interface Features                                   | 27  |

| 6  | BAR Register usage in M/S and DPA Modes                       | 28  |

| 7  | Normal Voltage Mode                                           | 29  |

| 8  | Extended Voltage Mode                                         | 29  |

| 9  | Serial EEPROM Interface Pins                                  | 33  |

| 10 | SCLK Frequency                                                | 33  |

| 11 | Serial EEPROM Commands                                        | 33  |

| 12 | Block Write Protect Bits                                      | 34  |

| 13 | Byte Enables on ROM Memory Reads                              | 36  |

| 14 | Status Register Format (Refer to Atmel* AT25F1024 Datasheet)  | 38  |

| 15 | Write and Read Command Types                                  | 44  |

| 16 | PCI Byte Enables on Read and Write Operations                 | 44  |

| 17 | SPI Command                                                   | 45  |

| 18 | SPI Control                                                   | 45  |

| 19 | SPI Status                                                    | 45  |

| 20 | SPI Data Register - Address 94h                               | 46  |

| 21 | Interrupt /Activity Status Combinations                       | 58  |

| 22 | PCI-X Bus Efficiency for Reads                                | 60  |

| 23 | PCI-X Bus Efficiency for Writes                               |     |

| 24 | Read Transfer Rate on PCI-X Bus                               |     |

| 25 | Write Transfer Rate on PCI-X Bus                              |     |

| 26 | SATA Port Register Mapping in Native PCI IDE Mode             |     |

| 27 | SATA Superset Registers for SATA Port 0 in DPA Mode           |     |

| 28 | 28-Bit LBA Address Bit Layout in PCI IDE Mode                 |     |

| 29 | 48-Bit LBA Address Bit Layout                                 |     |

| 30 | 48-Bit Address Loading Sequence                               |     |

| 31 | 28-Bit LBA Address Bit Layout in DPA Mode                     |     |

| 32 | 48-Bit LBA Address Bit Layout in DPA Mode                     |     |

| 33 | 31244 Controller Error Reporting Summary - PCI Interface      |     |

| 34 | 31244 Controller Serial ATA Protocol and Bus Error Conditions |     |

| 35 | SATA Unit PCI Configuration Space Registers                   |     |

| 38 | SATA DMA Registers in PCI IDE Mode                            |     |

| 36 | SATA Command Block Registers in PCI IDE Mode                  |     |

| 37 | SATA Control Block Registers in PCI IDE Mode                  |     |

| 39 | SU Vendor ID Register - SUVID                                 |     |

| 40 | SU Device ID Register - SUDID                                 |     |

| 41 | SU Command Register - SUCMD                                   |     |

| 42 | SU Status Register - SUSR                                     | 112 |

| 43 | SU Revision ID Register - SURID                               |     |

| 44 | SU Class Code Register - SUCCR                                |     |

| 45 | SU Cacheline Size Register - SUCLSR                           |     |

| 46 | SU Latency Timer Register - SULT                              |     |

| 47 | SU Header Type Register - SUHTR                               |     |

| 48 | SU BIST Register - SUBISTR                                    | 118 |

| 49 | SU Base Address Register 0 - SUBAR0                           | 119 |

| 50 | SU Base Address Register 1 - SUBAR1                                       | 120  |  |

|----|---------------------------------------------------------------------------|------|--|

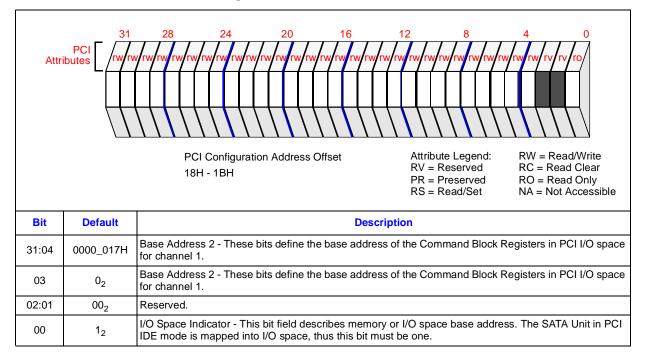

| 51 | SU Base Address Register 2 - SUBAR2                                       |      |  |

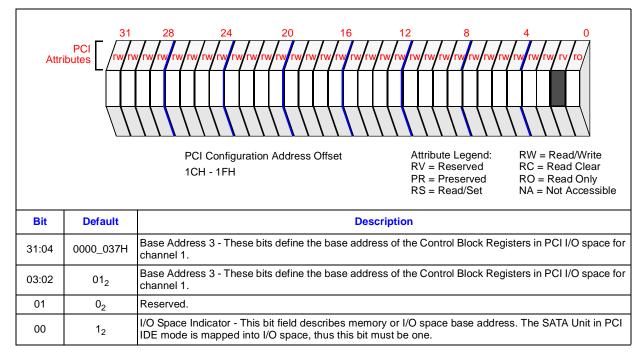

| 52 | SU Base Address Register 3 - SUBAR3                                       | .122 |  |

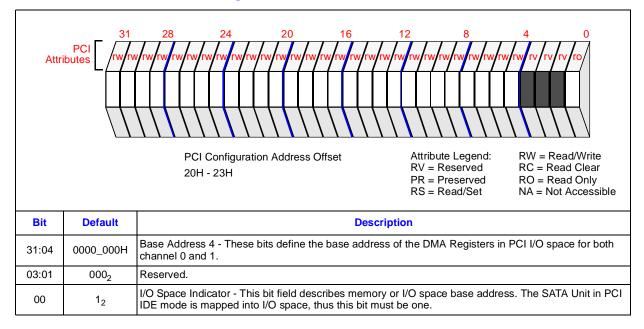

| 53 | SU Base Address Register 4 - SUBAR4                                       | .123 |  |

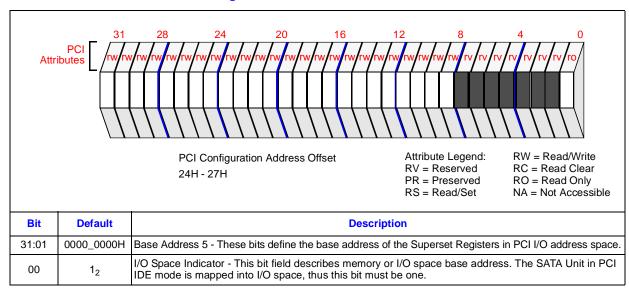

| 54 | SU Base Address Register 5 - SUBAR512                                     |      |  |

| 55 | SU Subsystem Vendor ID Register - SUSVIR                                  |      |  |

| 56 | SU Subsystem ID Register - SUSIR                                          |      |  |

| 57 | SU Expansion ROM Base Address Register - SUEXROMBAR                       |      |  |

| 58 | SU Capabilities Pointer Register - SU_Cap_Ptr                             |      |  |

| 59 | SU Expansion ROM Base Address - SUEXROM                                   |      |  |

| 60 | SU Interrupt Line Register - SUILR                                        |      |  |

| 61 | SU Interrupt Pin Register - SUIPR                                         |      |  |

| 62 | SU Minimum Grant Register - SUMGNT                                        |      |  |

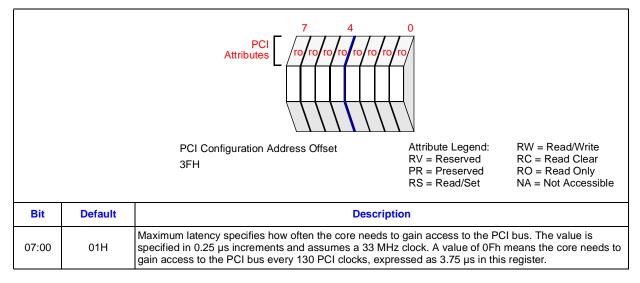

| 63 | SU Maximum Latency Register - SUMLAT                                      |      |  |

| 64 | SPI Command Register - SPICMDR                                            |      |  |

| 65 | SPI Control Register - SPICNTR                                            |      |  |

| 66 | SPI Status Register - SPISTATR                                            | 136  |  |

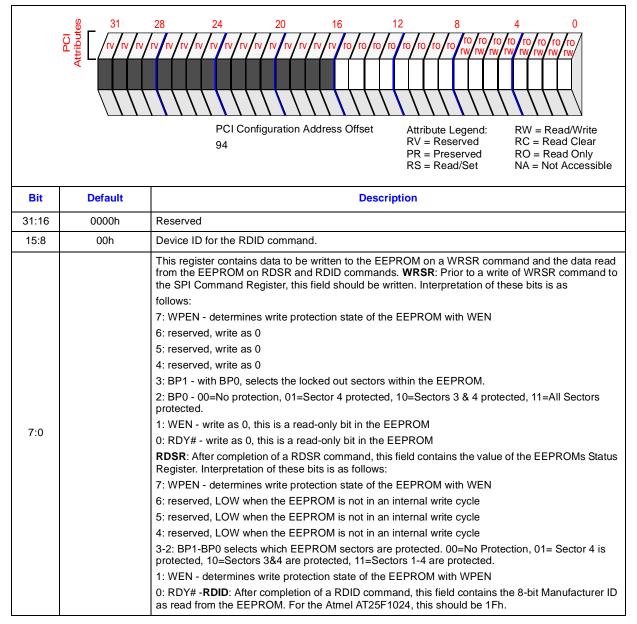

| 67 | SPI Data Register - SPIDATR                                               |      |  |

| 68 | SU Extended Control and Status Register 0 - SUECSR 0                      | 138  |  |

| 69 | SU DMA Control Status Register - SUDCSCR 0                                |      |  |

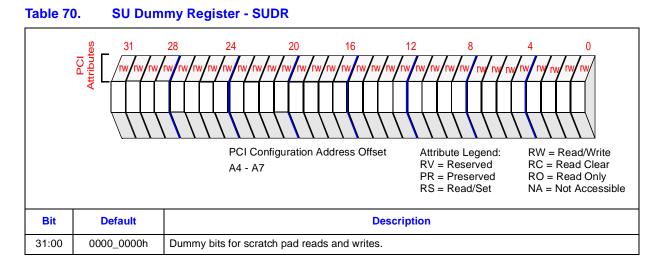

| 70 | SU Dummy Register - SUDR                                                  |      |  |

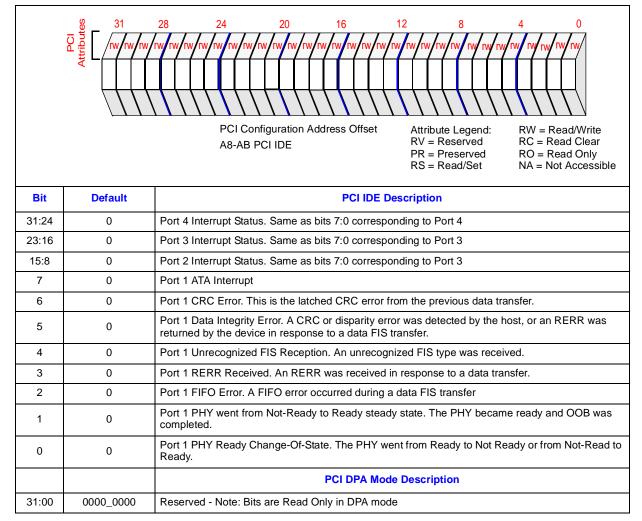

| 71 | SU Interrupt Status Register - SUISR                                      |      |  |

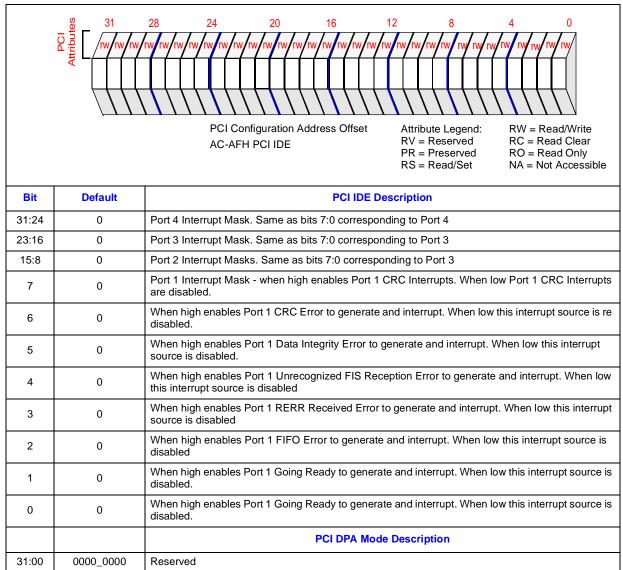

| 72 | SU Interrupt Mask Register - SUIMR                                        |      |  |

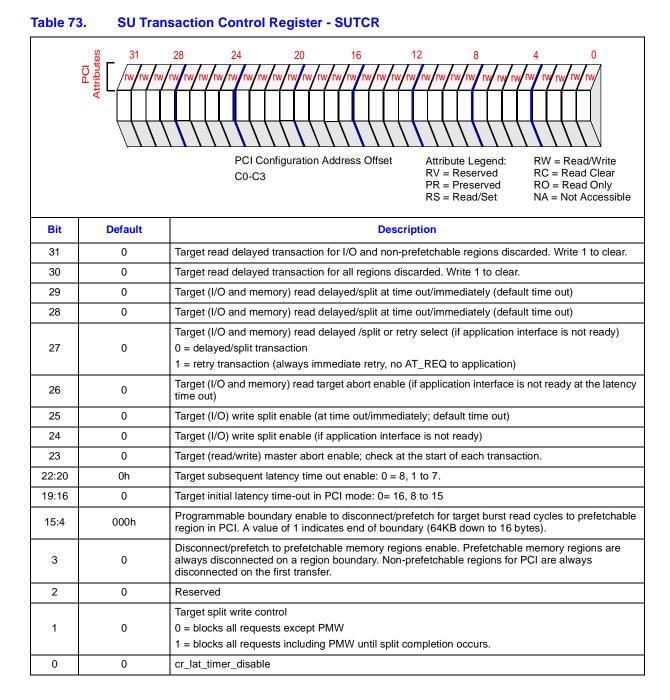

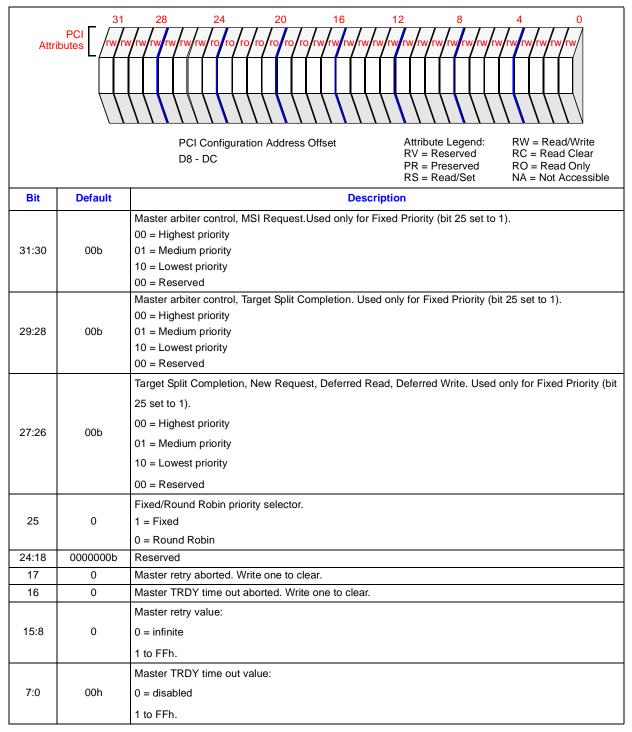

| 73 | SU Transaction Control Register - SUTCR                                   | 143  |  |

| 74 | SU Target Split Completion Message Enable Register- SUTSCMER              | .144 |  |

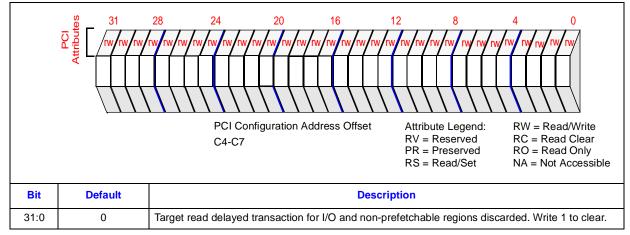

| 75 | SU Target Split Completion Message Enable Register- SUTSCMER              | .145 |  |

| 76 | SU Transaction Control 2 Register- SUTC2R                                 |      |  |

| 77 | SU Master Split Completion Message Received with Error Message Register - |      |  |

|    | SUMSCMREMR                                                                | .148 |  |

| 78 | SU Master Split Completion Message Received with Error Message Register - |      |  |

|    | SUMSCMREMR                                                                |      |  |

| 79 | SU Arbiter Control Register SUACR                                         |      |  |

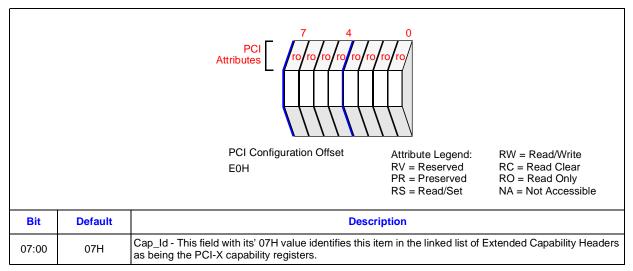

| 80 | SU PCI-X_Capability Identifier Register - SUPCI-X_Cap_ID                  | 151  |  |

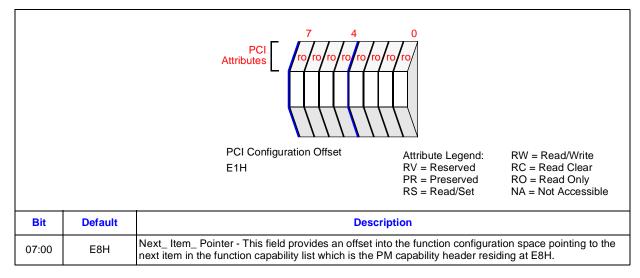

| 81 | SU PCI-X Next Item Pointer Register - SUPCI-X_Next_Item_Ptr               | 152  |  |

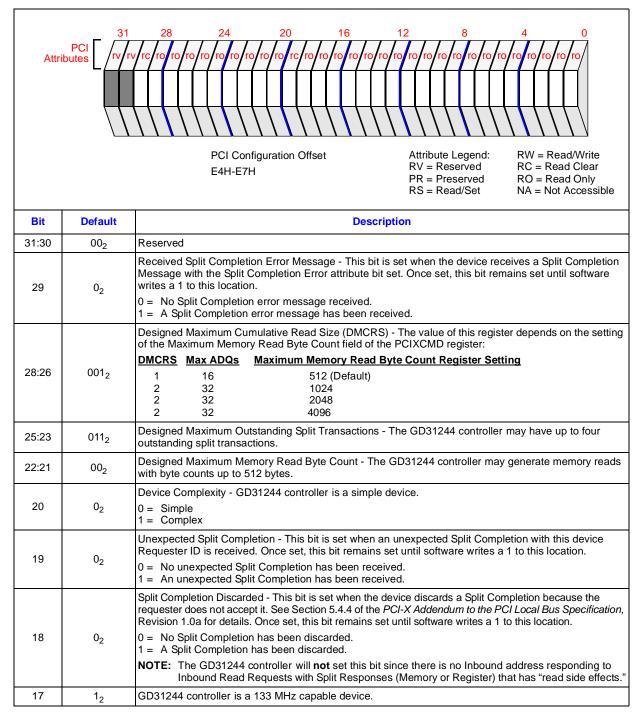

| 82 | SU PCI-X Command Register - SUPCIXCMD                                     |      |  |

| 83 | SU PCI-X Status Register - SUPCIXSR                                       |      |  |

| 84 | SU PM_Capability Identifier Register - SUPM_Cap_ID                        |      |  |

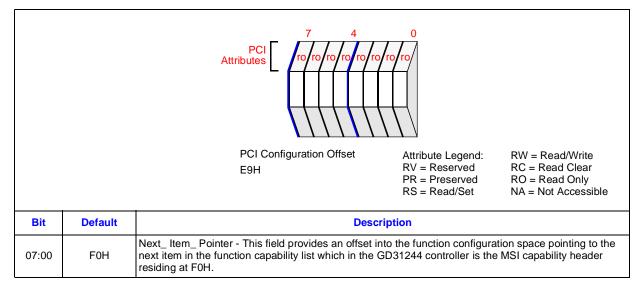

| 85 | SU PM Next Item Pointer Register - SUPM_Next_Item_Ptr                     |      |  |

| 86 | SU Power Management Capabilities Register - SUPMCR                        |      |  |

| 87 | SU Power Management Control/Status Register - SUPMCSR                     |      |  |

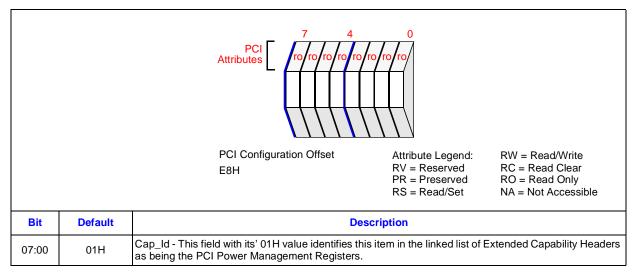

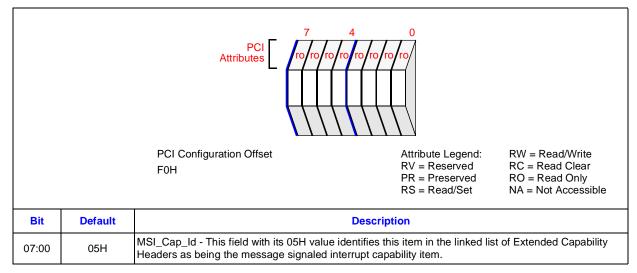

| 88 | SU MSI Capability Identifier Register - SUMSI_Cap_ID                      |      |  |

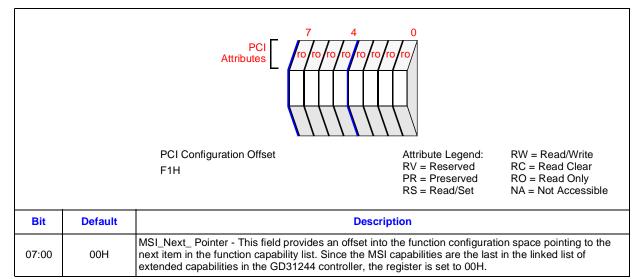

| 89 | SU MSI Next Item Pointer Register - SUMSI_Next_Ptr                        |      |  |

| 90 | SU MSI Message Control Register - SUMSI_Message_Control                   |      |  |

| 91 | SU MSI Message Address Register - SUMSI_Message_Address                   |      |  |

| 92 | SU MSI Message Upper Address Register - SUMSI_Message_Upper_Address       |      |  |

| 93 | SU MSI Message Data Register - SUMSI_Message_Data                         |      |  |

| 94 | SU IDE Data Port Register - SUIDR                                         | .166 |  |

| 95 | SU IDE Error Register - SUIER                                             | .167 |  |

| 96 | SU IDE Features Register - SUIFR                                          | .168 |  |

| 97 | SU IDE Sector Count Register - SUISCR                                     | .169 |  |

|                                                                           | 470 |

|---------------------------------------------------------------------------|-----|

| 98 SU IDE Sector Number Register - SUISNR                                 |     |

| 99 SU IDE Cylinder Low Register - SUICLR                                  |     |

| 100 SU IDE Cylinder High Register - SUICHR                                |     |

| 101 SU IDE Device/Head Register - SUIDHR                                  |     |

| 102 SU IDE Status Register - SUISR<br>103 SU IDE Command Register - SUICR |     |

| 104 SU IDE Device Control Register - SUIDCR                               |     |

| 105 SU IDE Alternate Status Register - SUIASR                             |     |

| 106 SU IDE Channel 0 DMA Command Register - SUICDCR0                      |     |

| 107 SU IDE Channel 0 DMA Status Register - SUICDCR0                       |     |

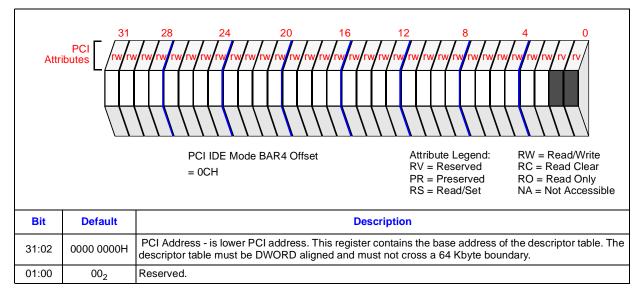

| 108 SU IDE Channel 0 DMA Descriptor Table Pointer Register - SUICDDTPR0   | 100 |

| 109 SU IDE Channel 1 DMA Command Register - SUICDCR1                      |     |

| 110 SU IDE Channel 1 DMA Status Register - SUICDSR1                       |     |

| 111 SU IDE Channel 1 DMA Descriptor Table Pointer Register - SUICDDTPR1   | 183 |

| 112 Configuration Space Comparison                                        |     |

| 113 SATA Port Registers Mapping in PCI DPA Mode                           |     |

| 114 SU PCI DPA Base Address Register 0 - SUDBAR0                          |     |

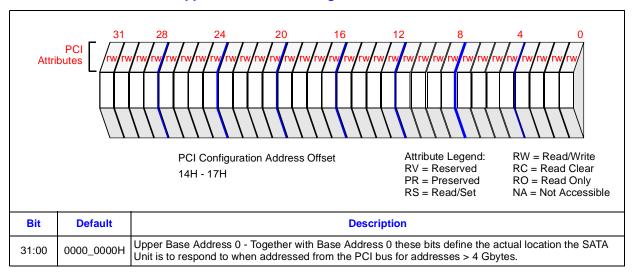

| 115 SU PCI DPA Upper Base Address Register 0 - SUPDUBAR0                  |     |

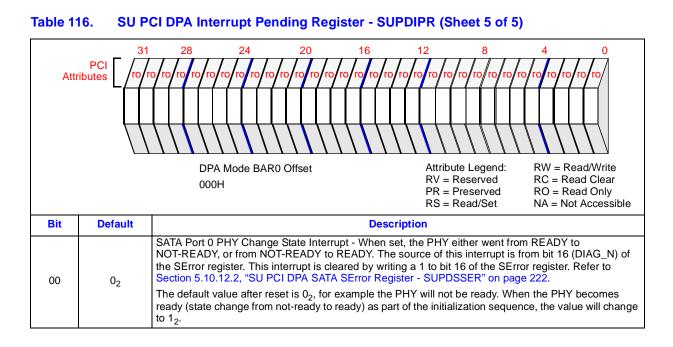

| 116 SU PCI DPA Interrupt Pending Register - SUPDIPR                       |     |

| 117 SU PCI DPA Interrupt Mask Register - SUPDIMR                          |     |

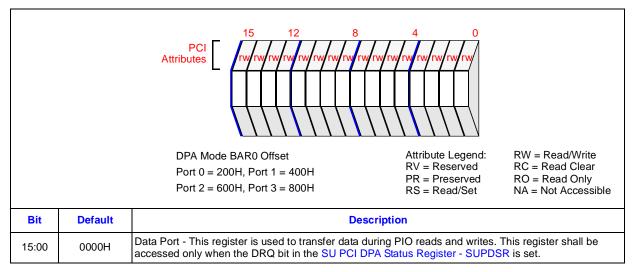

| 118 SU PCI DPA Data Port Register - SUPDDR                                |     |

| 119 SU PCI DPA Error Register - SUPDER.                                   |     |

| 120 SU PCI DPA Features Register - SUPDFR                                 |     |

| 121 SU PCI DPA Sector Count Register - SUPDSCR                            |     |

| 122 SU PCI DPA Sector Number Register - SUPDSNR                           |     |

| 123 SU PCI DPA Cylinder Low Register - SUPDCLR                            |     |

| 124 SU PCI DPA Cylinder High Register - SUPDCHR                           |     |

| 125 SU PCI DPA Device/Head Register - SUPDDHR                             |     |

| 126 SU PCI DPA Status Register - SUPDSR                                   | 211 |

| 127 SU PCI DPA Command Register - SUPDCR                                  |     |

| 128 SU PCI DPA Alternate Status Register - SUPDASR                        | 213 |

| 129 SU PCI DPA Device Control Register - SUPDDCTLR                        | 214 |

| 130 SU PCI DPA Upper DMA Descriptor Table Pointer Register - SUPDUDDTPR   |     |

| 131 SU PCI DPA Upper DMA Data Buffer Pointer Register - SUPDUDDPR         |     |

| 132 SU PCI DPA DMA Command Register - SUPDDCMDR                           | 217 |

| 133 SU PCI DPA DMA Status Register - SUPDDSR                              | 218 |

| 134 SU PCI DPA DMA Descriptor Table Pointer Register - SUPDDDTPR          |     |

| 135 SU PCI DPA SATA SStatus Register - SUPDSSSR                           |     |

| 136 SU PCI DPA SATA SError Register - SUPDSSER                            |     |

| 137 SU PCI DPA SATA SControl Register - SUPDSSCR                          |     |

| 138 SU PCI DPA Set Device Bits Register - SUPDSDBR                        |     |

| 139 SU PCI DPA PHY Feature Register - SUPDPFR                             |     |

| 140 SU PCI DPA BIST FIS Control and Status Register - SUPDBFCSR           |     |

| 141 SU PCI DPA BIST Errors Register - SUPDBER                             |     |

| 142 SU PCI DPA BIST Frames Register - SUPDBFR                             |     |

| 143 SU PCI DPA Host BIST Data Low Register - SUPDHBDLR                    |     |

| 144 SU PCI DPA Host BIST Data High Register - SUPDHBDHR                   |     |

| 145 SU PCI DPA Device BIST Data Low Register - SUPDDBDLR                  |     |

| 146 SU PCI DPA Device BIST Data High Register - SUPDDBDHR                 |     |

| 147 SU PCI DPA Device BIST Data High Register - SUPDDBDHR                 | 231 |

|                                                                           |     |

| 148 SU PCI DPA Device BIST Data High Register - SUPDDBDHR              | 238 |

|------------------------------------------------------------------------|-----|

| 149 SU PCI DPA DMA Setup FIS Control and Status Register - SUPDDSFCSR  | 239 |

| 150 SU PCI DPA Host DMA Buffer Identifier Low Register - SUPDHDBILR    | 240 |

| 151 SU PCI DPA Host DMA Buffer Identifier High Register - SUPDHDBIHR   | 241 |

| 152 SU PCI DPA Host Reserved DWORD Register 0 - SUPDHRDR 0             | 242 |

| 153 SU PCI DPA Host DMA Buffer Offset Register - SUPDHDBOR             | 243 |

| 154 SU PCI DPA Host DMA Transfer Count Register - SUPDHDTCR            | 244 |

| 155 SU PCI DPA Host Reserved DWORD Register 1- SUPDHRDR 1              | 245 |

| 156 SU PCI DPA Device DMA Buffer Identifier Low Register - SUPDDDBILR  | 246 |

| 157 SU PCI DPA Device DMA Buffer Identifier High Register - SUPDDDBIHR | 247 |

| 158 SU PCI DPA Device Reserved DWORD Register 0 - SUPDDRDR0            | 248 |

| 159 SU PCI DPA Device DMA Buffer Offset Register - SUPDDDBOR           | 249 |

| 160 SU PCI DPA Device DMA Transfer Count Register - SUPDDTCR           | 250 |

| 161 SU PCI DPA Device Reserved DWORD Register 1 - SUPDDRDR1            | 251 |

# **Revision History**

| Date          | Revision | Description                                                                                                                                                                                                                             |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | -006     | Removed Section 2.9, "Spread Spectrum Clocking" (page 31).<br>Removed definitions of "SSC" and "SSCEN" from Table 2,<br>"Terms and Definitions" on page 18.                                                                             |

| April 2004    |          | Removed references to "SSC" and "SSCEN" in<br>Section 5.10.12.5, "SU PCI DPA PHY Feature Register -<br>SUPDPFR" on page 227 and Table 139, "SU PCI DPA PHY<br>Feature Register - SUPDPFR" on page 227.                                  |

| February 2004 | -005     | Minor corrections.                                                                                                                                                                                                                      |

| January 2004  | -004     | Updated several register definitions.                                                                                                                                                                                                   |

| March 2003    | -003     | Corrected Figure 2.<br>Modified Section 3.8.6 and Section 3.12.2.36.<br>Updated Table 74.<br>Recreated Figures 14, 15, 16, 17, 27, 28 and 29.                                                                                           |

| December 2002 | -002     | In Section 2, added "Serial EEPROM Interface" sub-section.<br>Updated Section 1.1, "Reference Documents."<br>Updated Table 30, "SATA Unit PCI Configuration Space<br>Registers", to include SPICMDR, SPICNTR, SPISTATR, and<br>SPIDATR. |

| October 2002  | -001     | Initial release of this document.                                                                                                                                                                                                       |

# **About This Document**

# 1

# 1.1 Reference Documents

### Table 1. Reference Documents

| Documentation                                                                               | Document Number/Source                                         |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Intel® 31244 PCI-X to Serial ATA Controller Datasheet                                       | 273595                                                         |

| Intel® 31244 PCI-X to Serial ATA Controller Design Guide                                    | 273651                                                         |

| Intel® 31244 PCI-X to Serial ATA Controller Red Canyon CRB Manual                           | 273801                                                         |

| Atmel* Serial Memory Specification AT25F512/AT25F1024                                       | http://www.atmel.fi/atmel/acrobat/<br>doc1440.pdf              |

| AT Attachment with Packet Interface-6 (ATA/ATAPI-6) Specification,<br>ANSI/INCITS #361-2002 | http://www.techstreet.com/cgi-bin<br>/detail?product_id=932242 |

| Serial ATA Specification                                                                    | http://www.serialata.org                                       |

| Serial ATA II: Extensions to Serial ATA 1.0 Specification                                   | http://www.serialata.org/collateral<br>/index.shtml            |

| PCI Local Bus Specification, Revision 2.2                                                   | http://www.pcisig.com                                          |

| PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0a                            | http://www.pcisig.com                                          |

| PCI Bus Power Management Interface Specification, Revision 1.1                              | http://www.pcisig.com                                          |

| PCI IDE Specification, Revision 1.0                                                         | http://www.bswd.com/pciide.pdf                                 |

| STMicroelectronics* M25P10 Serial Flash Memory                                              | http://us.st.com/stonline/books/pd<br>f/docs/7022.pdf          |

### **1.2 Terminology and Conventions**

### 1.2.1 Representing Numbers

All numbers in this document may be assumed to be Base10, unless designated otherwise. In text, numbers in Base16 are represented as 'nnnH', where the 'H' signifies hexadecimal. In pseudo code descriptions, hexadecimal numbers are represented in the form 0x1234 ABCD. Binary numbers are not explicitly identified, but are assumed when bit operations or bit ranges are used.

### 1.2.2 Fields

| Reserved:           | Is a field that may be used by an implementation. When the initial value<br>of a reserved field is supplied by software, this value must be zero.<br>Software should not modify reserved fields or depend on any values in<br>reserved fields.                                                                                                                                                                |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read/Write:         | May be written to a new value following initialization. This field may<br>always be read to return the current value.                                                                                                                                                                                                                                                                                         |

| Read Only:          | May be read to return the current value. Writes to <i>read only</i> fields are treated as no-op operations and will not change the current value, nor result in an error condition.                                                                                                                                                                                                                           |

| Read/Clear:         | May also be read to return the current value. A write to a <i>read/clear</i> field with the data value of 0 will cause no change to the field. A write to a <i>read/clear</i> field with a data value of 1 will cause the field to be cleared (reset to the value of 0). For example, when a <i>read/clear</i> field has a value of F0H, and a data value of 55H is written, the resultant field will be A0H. |

| Read/Set:           | May also be read to return the current value. A write to a <i>read/set</i> field with the data value of 0 will cause no change to the field. A write to a <i>read/set</i> field with a data value of 1 will cause the field to be set (set to the value of 1). For example, when a <i>read/set</i> field has a value of F0H, and a data value of 55H is written, the resultant field will be F5H.             |

| Writeonce/Readonly: | May be written to a new value <b>once</b> following initialization. After the this write has occurred, the <i>writeonce/readonly</i> field will treat all subsequent writes as no-op operations and will not change the current value or result in an error condition. The field may always be read to return the current value.                                                                              |

### **1.2.3 Specifying Bit and Signal Values**

The terms *set* and *clear* in this specification refer to bit values in register and data structures. When a bit is set, its value is 1; when the bit is clear, its value is 0. Likewise, *setting* a bit means giving it a value of 1 and *clearing* a bit means giving it a value of 0.

The terms *assert* and *deassert* refer to the logically active or inactive value of a signal or bit, respectively.

### 1.2.4 Signal Name Conventions

All signal names use the PCI signal name convention of using the '#' symbol at the end of a signal name to indicate that the signal active state occurs when it is at a low voltage. The absence of the '#' symbol indicates that the signal active state occurs when it is at a high voltage.

### 1.2.5 Terminology

To aid the discussion of the GD31244 controller architecture, the following terminology is used:

#### Table 2.Terms and Definitions (Sheet 1 of 2)

| Term                   | Definition                                                                                                                                                                                             |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAR                    | Base Address Register                                                                                                                                                                                  |

| BIST                   | Built-In Self Test                                                                                                                                                                                     |

| CFG                    | Configure                                                                                                                                                                                              |

| CRB                    | Customer Reference Board                                                                                                                                                                               |

|                        | signal is comprised of a positive conductor and a negative conductor. The                                                                                                                              |

| Differential Signal    | differential signal is the voltage on the positive conductor minus the voltage on the negative conductor (i.e., TX+ – TX-).                                                                            |

| DMA                    | Direct Memory Access                                                                                                                                                                                   |

| Downstream             | At or toward a PCI bus with a higher number (after configuration).                                                                                                                                     |

| DPA Direct Port Access | Refers to a mode that allows more efficient access to the GD31244 registers. See also PCI IDE.                                                                                                         |

| DWORD                  | 32-bit data word.                                                                                                                                                                                      |

| HBA                    | Host Bus Adapter                                                                                                                                                                                       |

| Host processor:        | Processor located upstream from the GD31244 controller.                                                                                                                                                |

| Inbound Transactions   | Transactions that are aimed at the GD31244 controller by an external bus master device.                                                                                                                |

| ISI                    | Inter-symbol interference. Data-dependent deterministic jitter caused by the time propagated at different rates by the transmission media. This translates into high-frequency,data-dependent, jitter. |

| JEDEC                  | Provides standards for the semiconductor industry.                                                                                                                                                     |

| Jitter                 | Jitter is a high-frequency, semi-random displacement of a signal from its ideal location.                                                                                                              |

| M/S                    | Master/Slave. Refers to a legacy ATA mode that uses the traditional methods for accessing the ATA and the DMA registers (see also DPA).                                                                |

| BAR                    | Base Address Register                                                                                                                                                                                  |

| MR                     | Memory Read                                                                                                                                                                                            |

| MRL                    | Memory Read Line                                                                                                                                                                                       |

| MRM                    | Memory Read Multiple                                                                                                                                                                                   |

| MSI                    | Message Signalled Interrupts                                                                                                                                                                           |

| MW                     | Memory Write                                                                                                                                                                                           |

| MWI                    | Memory Write and Invalidate                                                                                                                                                                            |

| Network                | The trace of a PCB that completes an electrical connection between two or more components.                                                                                                             |

| Outbound Transactions  | Transactions that are initiated by the controller to another target device.                                                                                                                            |

| PATA                   | Parallel ATA                                                                                                                                                                                           |

| PBGA                   | Plastic Ball Grid Array                                                                                                                                                                                |

| PERR#                  | Parity error                                                                                                                                                                                           |

| PIO                    | Programmed I/O                                                                                                                                                                                         |

### Table 2.Terms and Definitions (Sheet 2 of 2)

| Term                    | Definition                                                                                                                                                                                                                                                                                               |