# ARTES N<sup>®</sup>

# **SXA10 SERIES**

Application Note 102 Rev. 05 - March 2000

- Surface mount isolated DC/DC converter

- · High reliability, rugged design

- · Low weight, open frame package

- 3:1 input voltage range 25-75V

- Adjustable Undervoltage Lockout (UVLO)

- Full operation over the temperature range of -40°C to +85°C ambient with natural convection, up to 100°C with forced air

- Capable of delivering 10% extra power from -10°C to 70°C

- Low power dissipation for any overload condition

|    | Introduction                                                                                                                                                                                                                                      |                            |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2. | Models                                                                                                                                                                                                                                            |                            |

|    | General Description<br>Electrical description<br>Physical construction                                                                                                                                                                            |                            |

|    | Features and Functions<br>Undervoltage lockout set-point adjustment<br>Remote ON/OFF operation<br>Output voltage trim<br>Output voltage adjust by voltage source                                                                                  | 2<br>3<br>3                |

| 5. | Safety<br>Input fusing<br>Insulation                                                                                                                                                                                                              | 4                          |

| 6. | EMC<br>Conducted emissions                                                                                                                                                                                                                        | 4<br>5<br>5<br>5           |

| 7. | Use in a Manufacturing Environment<br>Recommended reflow profile<br>Handling<br>ESD control<br>Pick and place<br>Resistance to soldering heat<br>Solder re-flow<br>Water washing<br>Functional test                                               | 5<br>5<br>6<br>6<br>6<br>6 |

| 8. | Applications<br>Large capacitive loads<br>Operation in overload<br>Thermals<br>Overtemperature protection<br>Output overvoltage protection<br>Series and parallel operation<br>Second source compatibility<br>Output noise and ripple measurement | 6<br>6<br>7<br>7<br>7<br>8 |

| 9. | Appendices<br>48S2V5 curves<br>48S3V3 curves<br>48S05 curves<br>48S12 curves                                                                                                                                                                      | 9<br>11<br>13              |

# 1. Introduction

The SXA10 series is a new generation of surface mountable isolated DC/DC converters which were designed in response to the growing need for rugged, high reliability DC/DC converters, optimized for highly automated customer processes.

Automated manufacturing methods, conservative component deratings combined with an extensive qualification program, make this product series ideal for Telecoms, Data Networking, Mobile Infrastructure, Industrial and DPA applications.

# 2. Models

| Model        | Input Voltage | Output Voltage |

|--------------|---------------|----------------|

| SXA10-48S2V5 | 25-75VDC      | 2.5V           |

| SXA10-48S3V3 | 25-75VDC      | 3.3V           |

| SXA10-48S05  | 25-75VDC      | 5.0V           |

| SXA10-48S12  | 27-75VDC      | 12V            |

### Table 1 - SXA10, 10 Watt models

# 3. General Description

### **Electrical Description**

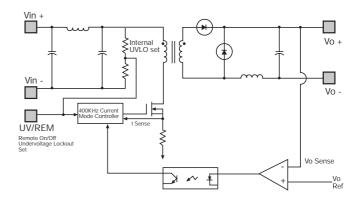

The SXA10 is a resonant reset forward converter. A simplified schematic is shown in Figure 1.

Figure 1 - SXA10 simplified schematic

The DC input is filtered by a damped pi filter. A current mode PWM controller, running at 400KHz is used. The transformer is a robust design, featuring 'heavy gauge' enamelled magnet wires and utilises a UL approved class F (155°C) insulation system. Class B (130'C) is the more usual standard for DC/DC converters.

The optocoupler emitter/ detector currents and power dissipations are derated to circa 2% to ensure very long life. The optocoupler plastics have high Tg to allow extended temperature operation.

The converter features an internal common mode bypass capacitor, value 1.5nF, between input and output to ensure negligible common mode EMI in the application circuitry. The output is sensed and compared with a secondary side reference and an error signal is fed back via an optocoupler to the PWM controller.

The remote On/Off allows the user to disable the switching of the converter, hence forcing the converter into a low power consumption mode. There is also the ability to set the input voltage at which the converter turns on. This is the adjustable undervoltage lockout feature.

#### **Physical Construction**

The SXA10 is an inverted open frame design, constructed using a single 1mm ceramic substrate with edge clip pins for leadout. The entire assembly process is highly automated. The ceramic, which has 2 layers of copper tracking, ensures that the product will retain excellent coplanarity through SMT reflow profiles. A custom automated process has been designed for edge clip attach, reflow and trim/form. The leads are made of phosphor bronze, a material which has high fatigue resistance and are 60/40 tin/lead plated for excellent solderability. Trim and form is to gullwing style for joint inspectability.

All converter components and edge clips are soldered with 221°C eutectic solder as opposed to the standard 180°C solder to proof/guard against complete reflow in the customer SMT process. All appropriate component bodies are also glued to ensure components cannot fall off under extreme reflow temperatures.

The open frame design allows for substantially reduced converter weight which will minimise customer FR4 board warpage during reflow. The inverted form gives a large flat top, which, when combined with the low weight, renders the component particularly compatible with SMT Pick and Place machine requirements.

The open frame design has several advantages over encapsulated closed devices. Among these advantages are:

- **Reliability**: There are no moulding TCE (Thermal Coefficient of Expansion) mismatch stresses on magnetics or other component bodies.

- Cost: No potting compound, casing or moulding process costs involved.

- Thermals: The heat is removed from the heat generating components directly to the ambient.

- Environmental: Encapsulants, in general, are not kind to the environment and create problems in incinerators. In addition open frame converters are more easily re-cycled.

A separate paper discussing the benefits of "open frame low to medium power DC/DC converter modules" Design Note 102 is available from Artesyn Technologies.

### 4. Features and Functions

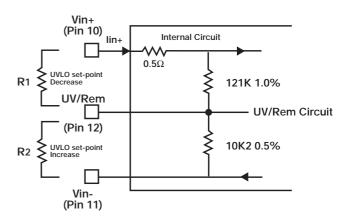

#### Undervoltage lockout set-point adjustment

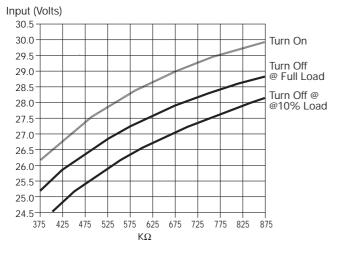

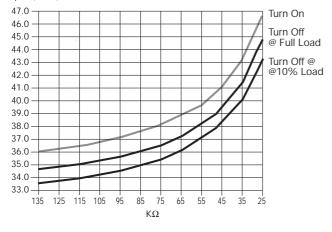

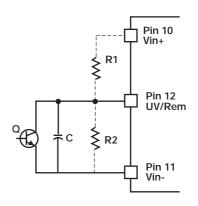

Undervoltage lockout default setting for 48 volt models is 33.86V nominally. This is set by the internal resistor divider network, as shown in figure 2. Adding a resistor between UV/REM (pin 12) and Vin+ (pin 10) will reduce the UVLO in the range 25 to 33 Volts. Adding a resistor between UV/REM (pin 12) and Vin- (pin 11) will increase the UVLO setting. The value for the UVLO set-point resistor may be read from figure 3 or 4. The UVLO turn on value (increasing) is independent of load. The turn-off point is dependent on load, and may be found by interpolation between the turn-off curves for 100% and 10% loadings.

Figures 3 and 4 shown the <u>nominal</u> turn on values and the <u>nominal</u> turn-off values for 10% and 100% load.

The UVLO set-point should be such that the UVLO setting thresholds at the UV/REM pin are as in the table.

|                                | Min   | Nom   | Max    |  |

|--------------------------------|-------|-------|--------|--|

| UVLO On Threshold @ UV/REM pin | 2.54V | 2.62V | 2.675V |  |

| UVLO Hysteresis @ UV/REM pin   | 170mV | 185mV | 200mV  |  |

The remote on/off and the UVLO on/off thresholds may vary slightly from those specified.

The converter must never be allowed operate with less than 23.5V DC input This implies that the minimum UVLO <u>turn on</u> setpoint should be selected to be greater than 26VDC (to allow for turn off hysteresis). <u>A 375KΩ</u>, (1% tolerance) is therefore the minimum allowed value for R1. If the output voltage is being trimmed up; the the minimum UVLO turn on set-point should be selected to be greater than 28VDC. There are no effective restrictions on the choice of value for R2.

Figure 2 - Undervoltage lockout set-point

Figure 3 - UVLO set-point decrease resistor (R1)

Input (Volts)

Figure 4 - UVLO set-point increase resistor (R2)

#### Remote On/Off operation

The UV/REM pin programs both the UVLO set-point and the remote shutdown, refer to Figure 5 for connection details. The converter has an active high remote On/Off function, i.e. is on and operational when the input voltage is above UVLO setpoint. The converter is disabled by pulling the UV/REM pin below the UVLO threshold. When the UV/REM pin is pulled below the lower, remote On/Off threshold, the unit is in a sleep mode and total power consumption is 150mW maximum. A capacitor, C (100pF) as shown in Figure 5 is recommended if the ripple and noise between UV/REM and Vin- is greater than 125mV pk-pk, or operation is required at input voltages less than 36VDC.

It is recommended that this pin is operated with open collector logic. If 'active high' circuitry (i.e. sources current when high or off) is used to drive this pin; a reverse blocking diode will be needed to preserve the UVLO setpoint and protect the converter from operation at low DC input voltages.

Note adding the optional 100pF capacitor between the UV/REM pin and Vin- will also give cleaner power up/down waveforms for Vo.

R1 is optional to decrease UVLO set.R2 is optional to increase UVLO set.C (100pF) is necessary for noisy environments or operation at low input voltages.Q when switched on will turn converter off.

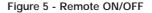

#### Output voltage trim

When trimming up; adjust the nominal output current rating according to converter power capability. The equations to calculate the trim up or down resistor are given below. 'Vout' is the desired new output voltage. The connection details are shown in Figure 6.

Figure 6 - Trim Up/Down connections

Equations for resistor values are given below in table 2.

| MODEL | $R_dn_K\Omega$                     | R_up_KΩ                             |

|-------|------------------------------------|-------------------------------------|

| 2.5V  | Vout .4420 - 9781.12<br>2.5 - Vo.  | 9781.12 - 3400. Vout<br>Vout - 2.5. |

| 3.3V  | 17.52 Vout - 49.74<br>6.6 - 2 Vout | 49.73 - 13.6 Vout<br>2 Vout - 6.6   |

| 5V    | 4 Vout - 15<br>10 - 2 Vout         | 15 - 2 Vout<br>2 Vout - 10          |

| 12V   | 4860 Vout - 32176<br>12 - Vout     | No Trim-up option<br>on 12V Unit    |

Table 2 - Trim equations

#### Output voltage adjust by voltage source

As an alternative to resistive trim up or trim down of the output, the output voltage may be adjusted by applying a programming voltage to the trim pin equivalent to the voltage present when the appropriate trim resistor is used. Voltage margining by this method is only recommended for test purposes because the dynamics of the converter's internal control loop are affected by applying this external source.

# 5. Safety

#### Input Fusing

In order to comply with safety requirements, the user must provide a fuse in the unearthed input line if an earthed input is used. The reason for putting the fuse in the unearthed line is to avoid earth being disconnected in the event of a failure. If an earthed input is not being used then the fuse may be in either input line. A 850mA HRC (High Rupture Capacity) fuse should be used for all 48V nominal input models.

#### Insulation

The SXA10 series has been designed in accordance with EN60950 and CSA C22.2 No. 950/UL1950 March 1998 'Safety of Information Technology Equipment'.

The SXA10 DC/DC converter is intended for inclusion in other equipment and the installer must ensure that it is in compliance with all the requirements of the end application.

Table 3 below contains information extracted from CSA C22.2 No. 950/UL 1950 March 1998 standard and shows that having BASIC isolation may obviate the need for system level fault testing which can often extend the system design cycle time by exposing problems late in the design cycle. For many applications however, models with operational insulation will be sufficient. These cost less and will have an efficiency 1-2% higher than the equivalent model with BASIC.

| Input        | Output          | Insulation<br>Category<br>Required | Add. Requirement<br>CSA C22.2 No. 950/<br>UL1950 March '98.<br>Paragraph quoted |

|--------------|-----------------|------------------------------------|---------------------------------------------------------------------------------|

| SELV         | SELV            | OPERATIONAL                        |                                                                                 |

| TNV1         | SELV            | OPERATIONAL                        | 6.4.1                                                                           |

| TNV2         | SELV            | BASIC                              |                                                                                 |

| TNV3         | SELV            | BASIC                              | 6.4.1                                                                           |

| TNV1, 2 or 3 | Earthed<br>SELV | OPERATIONAL                        | 6.2.1.2, 6.3.3., 6.4.1.,<br>creepages per table 6                               |

#### Table 3

*6.2.1.2.* Separation of TNV from other circuits and from accessible parts. In the event of a single insulation fault; SELV, TNV1 and accessible conductive parts will not exceed TNV-2 and TNV-3 normal operating limits.

*6.3.3. Separation of the telecommunication network from earth.* There shall be insulation between parts connected to the telecom network and parts or circuitry that will be earthed. The insulation is subject to the electric strength test of 6.4.2.2. There are also leakage current requirements. *6.4.1.Separation requirement between TNV-1 or TNV-3 and certain parts of the equipment.* There is a choice of an Impulse Test, 6.4.2.1., or an Electric Strength Test, 6.4.2.2. The SXA10 converter's rated isolation voltage of 1500VDC for 60 seconds, which is production tested on every unit for 1 second, satisfies 6.4.2.2.

#### 6. EMC

#### **Conducted Emissions**

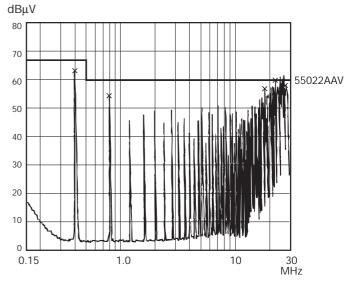

The SXA10 has a substantial pi (damped CLC) filter internally. Without any external filtering components, the unit will typically meet the Class A average limit line for EN55022 or FCC part 15. Figure 7 shows the typical conducted noise spectrum into the 50 $\mu$ H LISN.

Conducted emissions will increase with input voltage and for operation at an input voltage above 60 Volts, the external capacitor which is recommended for level B may be required.

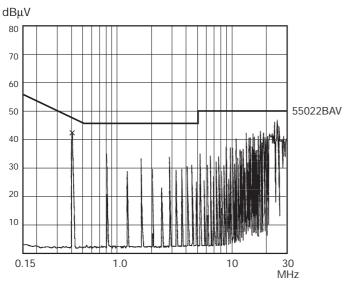

For EMI level B, a SMT gullwing leaded film capacitor such as ITW Paktron 405K100CS4 is recommended for C1. The typical spectrum is given in Figure 8. System level EMC design should verify that this capacitor gives sufficient margin. For high DC input voltages (i.e. >60VDC) and depending on application board layout, a second capacitor may be required.

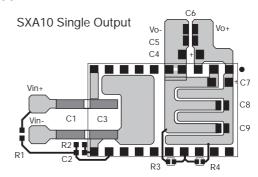

An alternative is to use a low profile surface mount film capacitor. This capacitor, C3, could mount under the converter as shown, see section 8 Applications. There is no difficulty placing passive filtering components under the converter, as shown for C3, C7, C8 and C9, so long as 2mm clearances (for thermals and safety reasons) are maintained to any of the converter components.

Electrolytic type capacitors are not recommended for use at the input stage because of their high ESR (equivalent series resistance) and their low lifetime at high operating temperatures.

Figure 7 - Typical conducted noise spectrum with unit mounted on recommend single sided on layout. No external capacitors are used. Unit is @ 48VDC input and 2.2A load. Unit meets Level A.

Figure 8 - Typical conducted noise spectrum with unit mounted on recommended single sided layout.

A single capacitor, C1, (4μF, 100V, film ITW Paktron

405K100CS4) is fitted. Unit is @ 48VDC input and 2.2A load. Unit meets level B.

#### **Radiated Emissions**

The SXA10 converter is a forward topology and uses a non-gapped magnetic. In contrast to flyback converter types, the SXA10 series will have very low magnetic near field radiation. The applicable standard is EN55022 (FCC Part 15). Testing DC/DC converters as a stand-alone component to the exact requirements of EN55022 (FCC Part 15) is very difficult to do as the standard calls for 1m leads to be attached to the input and output ports and aligned such as to maximize the disturbance. In such a set-up it is possible to form a perfect dipole antenna that very few switchmode DC/DC converters could pass.

However the standard also states that 'An attempt should be made to maximize the disturbance consistent with the typical application by varying the configuration of the test sample'. In addition ETS 300 386-1 states that the testing should be carried out on the enclosure.

Radiated emissions tests were made with the unit mounted on an open test board and with full resistive load on 10cm leads. The unit comfortably met level A, even though no enclosure was used.

#### Common mode noise

This is generated in switching converters and can contribute to both radiated emissions and input conducted emissions. The SXA10 series of converters bypasses common mode noise internally by using a 1.5nF capacitor between input ground and output ground. The SXA10 series will therefore greatly minimise common mode noise currents flowing in the application circuitry.

#### Reflected input current ripple

Assuming that there is no external bypass capacitor across the input, the input current ripple can be estimated from the first harmonic on the input conducted noise plot. This gives the input noise voltage in dBµV across  $50\Omega$  at the switching frequency. The input reflected ripple current at switching frequency may be estimated from:

Iin (AC rms) =  $(1/_{50})$  x Log  $^{-1}$  (dBµV peak from EMI plot / 20)

Note that application generated common mode noise currents could increase the apparent converter input current ripple.

The typical reflected input current ripple at full load and nominal line for all SXA10-48Sxx models is less than  $40\mu$ A.

#### EN61000-4-5 surge immunity test

The unit has been tested with the Combination Wave Generator (1.2/50µSec open circuit voltage ramp, 8/20 short circuit current) surge to Level 1, 500 Volts. There are 5 consecutive surges of positive and negative polarity. Performance is to category 'b' i.e. there will be temporary degradation in performance but the unit will self recover.

The unit is intended for a Class 1, 'Partly Protected Environment' which will have 'Secondary Surge Protection'. For this environment the surge generator source impedance is  $42\Omega$ .

#### 7. Use in a Manufacturing Environment

#### Recommended reflow profile

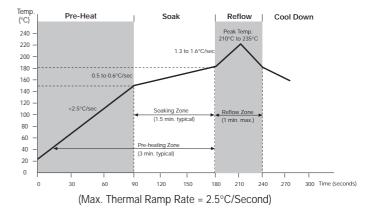

It is critical that the peak reflow temperature of 235°C and the maximum allowable ramp rate of 2.5°C/sec ratings are observed. The recommended reflow profile as shown fits with industry standard SMT processes.

Figure 9 - Recommended reflow profile CECC 00 802

#### Handling

Great care has been taken in ensuring that the customer receives the SXA10 product exactly as it leaves the Artesyn assembly line. To avoid damaging the product, certain precautions must be taken in the customer's process. The converter should never be handled by the leads. However, if it is necessary to handle the product then it should be held at the circuit board level to avoid bending the pins. The product is designed for use in high volume automated SMT assembly equipment and the requirement to manually handle the product must be avoided. The static dissipating waffle trays are designed to be stacked multiple-up and protect the product. The maximum recommended number of stacked trays for shelf storage is twenty-five.

#### ESD Control

The SXA10's are manufactured in an ESD controlled environment and supplied in conductive packaging to prevent ESD damage occurring either before or during shipping. It is essential that the product is unpacked and handled in an ESD controlled environment. Failure to do so could affect the lifetime of the converter.

#### **Pick and Place**

When placing the converter, using odd-form P&P equipment, it is recommended that vision component recognition and alignment be used as opposed to manual chuck (tweezers type) alignment. This will ensure optimum alignment placement accuracy and eliminate the possibility of mechanical deformation of lead position and coplanarity. On the P&P machine, the converter should be programmed as a gull-wing IC type component using standard recognition algorithms. The vacuum nozzle for picking and placing the converter can be the same as used for large area IC's or BGA's and typically a 12mm diameter rubber tipped nozzle should be used - if in doubt contact the equipment manufacturer. If placing these components by hand, then place the tweezers on the central body area where there are no pins.

Applying tweezers on the pins can cause bending and co-planarity may be impacted.

#### Resistance to soldering heat

It is intended that the SXA10 series is only used in an automated SMD assembly process. The unit should not be hand-soldered but nevertheless the MIL-STD-202 method 210D, test has been conducted to determine how well it can resist the temperatures associated with the hand soldering of a PTH (plated through hole) component. For the soldering iron test, condition A, the UUT was placed on a PCB with the recommended PCB layout pattern shown in the applications section. A soldering iron set to 350°C ±10% was applied to each terminal for 5 seconds. The UUT was then removed from the test PCB and was examined under a microscope for any reflow of the pin solder or physical change to the terminations. No reflow or changes occurred.

#### Solder Re-flow

The recommended solder paste thickness is 0.15mm minimum. Figure 9 references the recommended re-flow profile the converter should experience in the user's SMT assembly process. This profile is typical of the profile recommended by solder paste manufacturers when using Sn63/Pb37 or Sn62/Pb36/Ag2 solder alloys. The product is suitable for processing in convection and infra-red as well as combination type re-flow systems. The leads are plated with a Sn60/Pb40 solder finish. This is a standard lead finish and is compatible with industry standard solder alloys.

#### Water Washing

Where possible a no-clean solder paste system should be used for solder attaching the SXA10 product onto application boards. The SXA10 is suitable for water washing applications, as it does not have entrapment areas where water and residues may become trapped long term. However, the user must ensure that the drying process is sufficient to remove all water from the converter after washing - never power the converter unless it is fully dried. The user's process must clean the soldered assembly in accordance with ANSI/J-STD-001.

#### **Functional Test**

All product is 100% functionally tested prior to shipping. If however, it is necessary to functionally test product, a special fixture is required to make electrical spring contacts to the leads at the substrate attach points, and which will preserve the coplanarity and alignment of the leads. Please consult the factory for details on this fixture.

It is always essential to power down the supply before disconnecting the unit. This will prevent inductive transients from damaging the UVLO/Remote circuitry.

#### 8. Applications

Figure 10 - Example single sided layout for good EMI performance

It is recommended that two 'ground planes' under the converter as shown in Figure 10 be used. One should be under the 'input half' and connect to either of the supply lines. The other under the 'output half' should connect to either of the output power pins. These will then locally return any radiated energy.

- 1 For EMI Level B (See Application Note section 6). ITW Paktron 405K100CS4 is recommended for C1 to meet level B.

- 2 All other capacitor locations shown are optional if system design requires lower noise.

- 3 C3, C7, C8, C9 show how passive filtering components may be placed under unit.

#### Large capacative loads

A small overshoot may occur in the output voltage at power up into an extremely large capacitive load (> $2000\mu$ F/Amp). This occurs because of the intrinsic loss of high frequency gain associated with the addition of the large value capacitance. It does not indicate any loss of phase margin or stability.

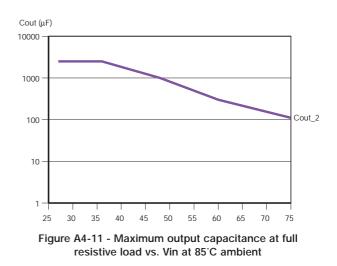

The converter is designed to have high stability margins even with the addition of capacitors with extremely low ESR. Output voltage recovery from a sustained overload or start up at a high temperature may be impacted by the addition of an extremely large capacitive load. Table 4 below shows the maximum limits for total application load capacitance.

| Output Voltage | Vin in the Range<br>25 to 60VDC      | Vin in the Range<br>60 to 75VDC |

|----------------|--------------------------------------|---------------------------------|

| 2V5            | 20,000µF                             | 6,800µF                         |

| 3V3            | 20,000µF                             | 6,800µF                         |

| 5V             | 20,000µF                             | 4,400µF                         |

| 12V            | See 12V data in Appendices for Graph |                                 |

Table 4

#### Operation in overload

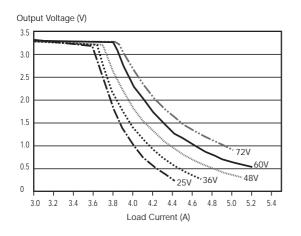

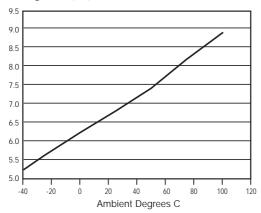

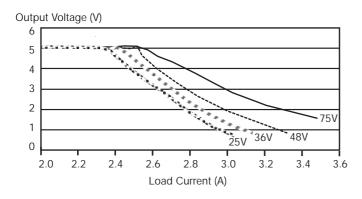

There is a two stage overload protection. For any overload or short circuit, the converter internal component dissipations are fully derated for continuous reliable operation. At approximately 125% load the converter hits the 'first current limit' point and the converter effectively enters a constant power mode. For more output current the output voltage must fall. The variation of the 'first current limit' with temperature is depicted in the V-I curve knee vs temperature characteristic curve in the Appendices. Variation of this point with input voltage is shown in the Vout vs load characteristic curves, also given in the Appendices.

Deeper in overload, at a low output voltage, the converter will enter a 'hiccup mode' of shutdown and restart. The point of entry into 'hiccup mode' is temperature dependent. At higher temperatures the converter enters 'hiccup mode' for lower loads. This sets an effective maximum temperature which each internal component can ever reach.

#### Thermals

The unit has excellent thermal performance. The open frame construction is very good from a thermal perspective because it has a high effective surface area. In a typical application, more than half of the heat generated by the converter will pass directly from the internal components directly to the ambient air as opposed to being conducted through the pins to the application board. All components were selected to have high operating temperature capability. The main transformer for instance uses a Class F (155°C) system of components per UL1950 and the output inductor is a 175°C component. The converter will operate very reliably and with high lifetime even in an enclosed space @  $85^{\circ}$ C with no airflow, where there will still be Artesyn standard design deratings on all components.

#### For safe design in:

1 Pin 3 is the most effective heat-sinking pin for the converter. It is tied directly to the tab of the main output rectifier diode. The layout should centre this pin on at least 2cm<sup>2</sup> of copper plane. Ideally many vias will thermally couple the pin to a full output voltage distribution plane.

Pins 1, 2, 4 and 5 are also very effective at heatsinking the converter and should be tied to as much copper as possible. Pins 4 and 5 may be tied together and will form a good EMI 'star point' for an EMI ground plane under the converter. This plane will act as both a heatsink and EMI shield.

2 The unit is rated for still air ambient at 85°C provided that it is mounted with its substrate in the vertical plane. This will give 15°C of margin over a horizontal plane mounting arrangement where natural convection is impeded. For forced air applications there is no difference between mounting orientations.

For extreme environments the tab of the main output rectifier (see Figure 11 below) should be thermocoupled to check that its normal full load temperature stabilises to <110°C.

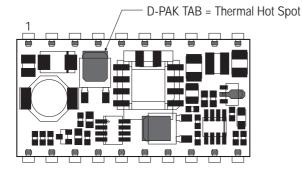

Figure 11 - Thermal hot spot

#### Overtemperature protection

The converter is designed so that no component will ever exceed its design ratings provided that the ambient temperature remains less than 85°C and the application board layout guidelines are adhered to. This is true even for natural convection only and for a continuous overload or short circuit.

In the event that the ambient or the application board is raised to a very high temperature the converter will go into thermal shutdown. This typically occurs when the ceramic substrate is raised above 140°C. There is typically 25°C hysteresis in the thermal protection circuitry so that converter will restart when the ceramic cools to 115°C. During such elevated temperatures some of the 'absolute maximum ratings' may be exceeded. This feature is therefore intended as a 'last line of defence' protection mechanism for the case of a gross fault.

#### Output overvoltage protection

There is no internal output overvoltage fault protection circuitry fitted to the SXA10.

#### Series and parallel operation

A key feature of Artesyn's SXA10 series of converters is their high input to output galvanic isolation. This allows full configuration flexibility to generate different voltages and polarities, through series or parallel connection. The units have undervoltage lockout circuitry and require a low start up current, nevertheless care should be taken to ensure that the source (supply) impedance for each converter is sufficiently low to cater for the individual start up surge currents. We recommend that the maximum Vout (or Vfloat) of a combination does not exceed 250V.

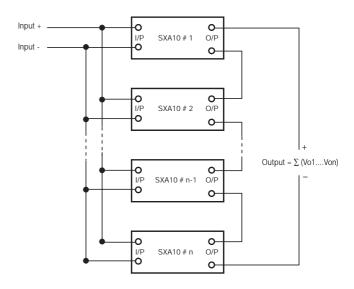

#### (a) Series Operation

Any combination or number of SXA10 units can be connected together in series in order to give a higher voltage or a selection of voltage 'rails' as required for the application. The overall current will however be limited by the lowest current (often the highest voltage) converter in the chain. The key parameters such as output voltage, load, line and noise performance will typically be the summation of the individual unit performances, but they can also be affected by board layout and additional filtering may be necessary to achieve the desired output performance.

Fig (a) Connecting SXA10's in series

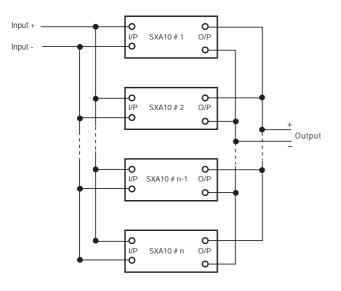

#### (b) Parallel Operation

If more power (or current) is required than that supplied by a single converter, then two or more converters can be directly paralleled in order to achieve the necessary power (or current) output.

Because the SXA10's are designed for full reliability for all operating regions, including overload conditions, the parallel set up can be used even if application impedances are such as to result in one of the converters being in continuous current limit.

Parallel performance can be enhanced with the use of external components i.e.

- Series output diodes on each output to 'decouple' individual outputs (for redundancy)

- Series output filters to improve ripple and noise or to decrease dynamic output impedance etc.

The key unit parameters such as output voltage, load, line and noise performance will depend on the layout and unit Vout matching but the total error band will remain within the quoted overall accuracy for an individual unit.

Fig. (b) Connecting SXA10's in parallel

#### Second source compatibility

Consult factory for electrical compatibility design-in details with other manufacturers' surface mountable converters.

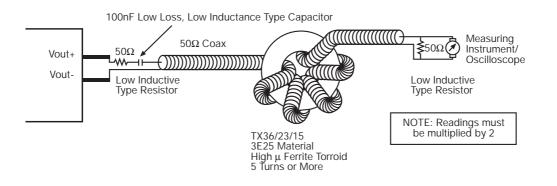

#### Output noise and ripple measurement

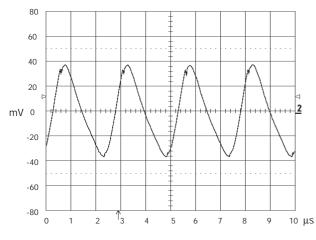

The above circuit has been used for noise measurement on SXA series converters. The large toroid will act as a common mode filter to noise which would otherwise flow through the measuring instrument or oscilloscope to disturb the measurement of the differential mode noise.

A 50 $\Omega$  coax lead should be used with source and termination impedances of 50 $\Omega$ . This will prevent impedance mismatch reflections which would otherwise disturb the noise reading at higher frequencies.

The  $50\Omega$  resistor which is added in series with the output of the power supply will form a voltage divider with the termination  $50\Omega$  and so ripple and noise measurement readings should be multiplied by 2.

# 9. Appendix 1

# Typical characteristic curves for 48S2V5 model

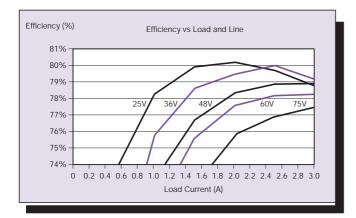

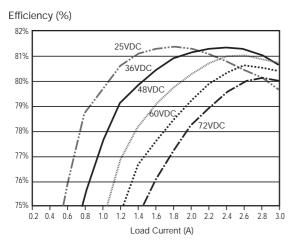

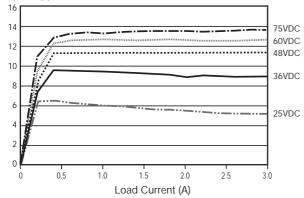

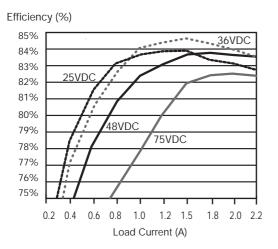

Figure A1-1 - Efficiency vs load and line

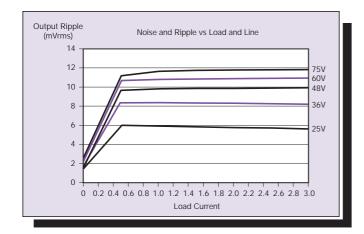

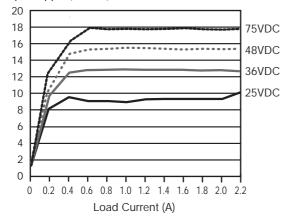

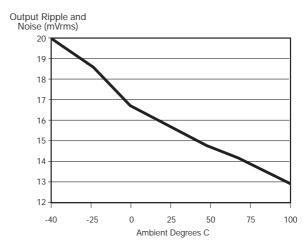

Figure A1-3 - Noise and ripple vs load and line

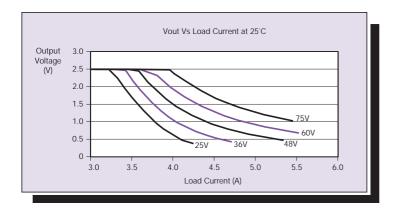

Figure A1-5 - Vout vs. load @ 25°C

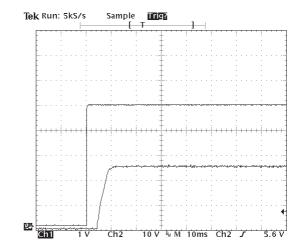

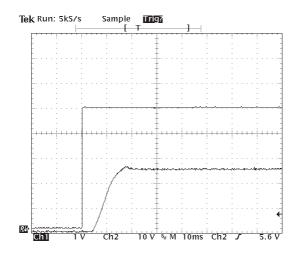

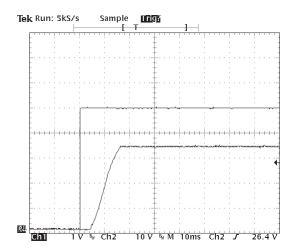

Figure A1-2 - 2V5 Start-up from 48Vin into 3A resistive load

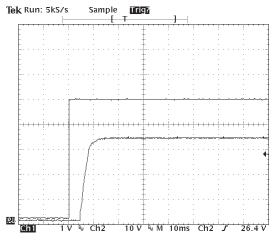

Figure A1-4 - 2V5 Start-up from 48Vin into 3A resistive and 6800µF capacitive load

# Typical characteristic curves for 48S2V5 model continued

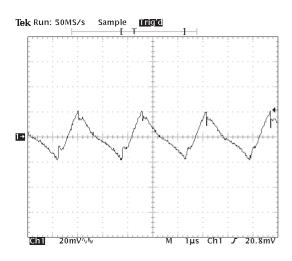

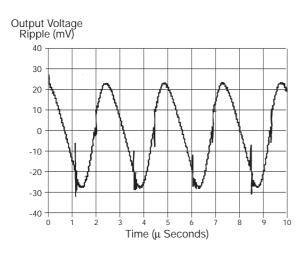

Figure A1-6 - Vo ripple and noise, 20MHz BW

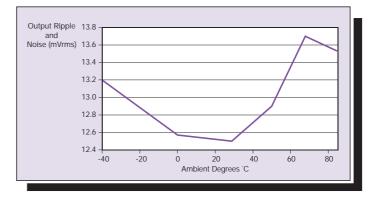

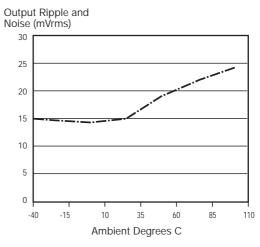

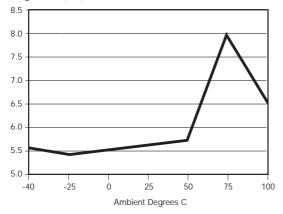

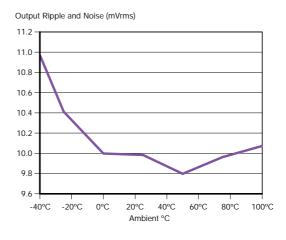

Figure A1-7 - Ripple and noise vs. temperature

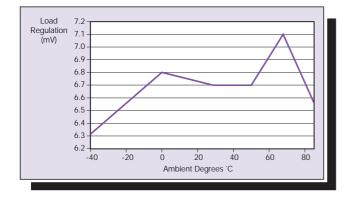

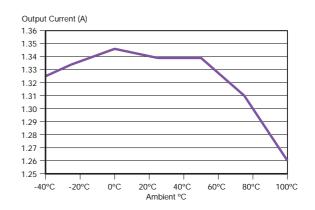

Figure A1-8 - Load regulation: 0% to 100% vs. temperature

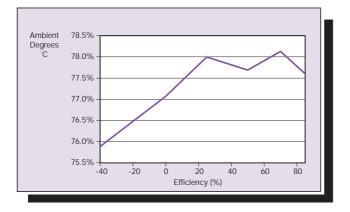

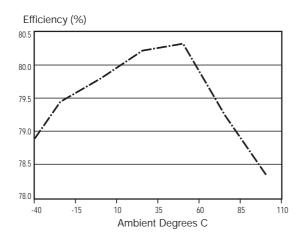

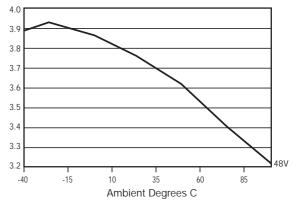

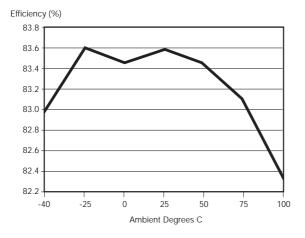

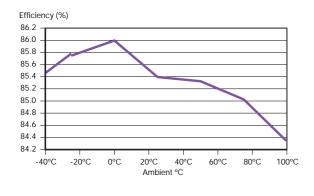

Figure A1-10 - Efficiency vs. temperature

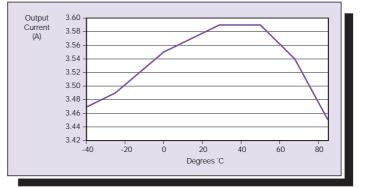

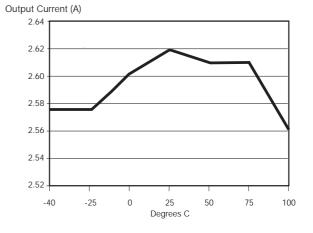

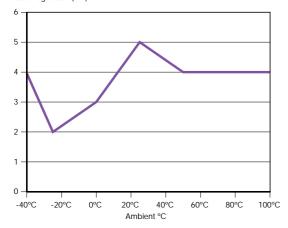

Figure A1-9 - V-I curve knee vs. temperature

# 10. Appendix 2 Typical characteristic curves for 48S3V3 model

Output Ripple (mVrms)

Figure A2-3 - Noise and ripple vs load and line

Figure A2-5 - Vout vs. load @ 25°C

Figure A2-2 - Start-up from 48Vin into 3A resistive load

Figure A2-4 - Start-up from 48Vin into 3A resistive and 6800µF capacitive load

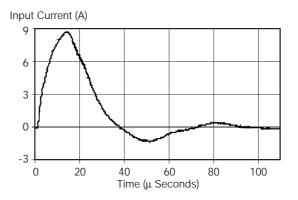

Figure A2-6 - Inrush current per ETSI 300 132-2 (Supply Z =  $3.5\Omega$  + 10µH)

# Typical characteristic curves for 48S3V3 model continued

Figure A2-7 - Vo ripple and noise, 20MHz BW

Load Regulation (mV)

Figure A2-9 - Load regulation: 0% to 100% vs. temperature

Figure A2-11 - Efficiency vs. temperature

Figure A2-8 - Ripple and noise vs. temperature

Figure A2-10 - V-I curve knee vs. temperature

# 9. Appendix 3 Typical characteristic curves for 48S05 model

Figure A3-1 - Efficiency vs load and line

Output Ripple (mVrms)

Figure A3-3 - Noise and ripple vs load and line

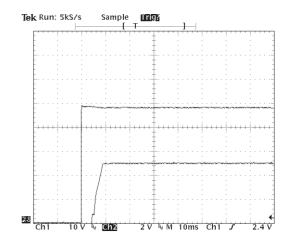

Figure A3-2 - 5V Start-up from 48Vin into 2A resistive load

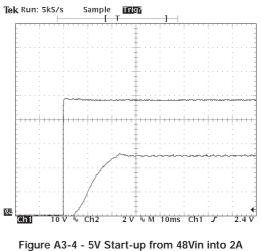

resistive and 4400µF capacitive load

Figure A3-5 - Vout vs. load @ 25°C

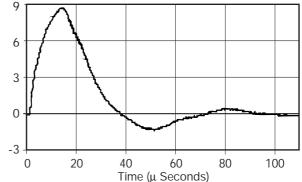

Figure A3-6 - Inrush current per ETSI 300 132-2 (supply Z =  $3.5\Omega + 10\mu$ H)

# Typical characteristic curves for 48S05 model continued

Figure A3-7 - Vo ripple and noise, 20MHz BW

Load Regulation (mV)

Figure A3-9 - Load regulation: 0% to 100% vs. temperature

Figure A3-11 - Efficiency vs. temperature

Figure A3-8 - Ripple and noise vs. temperature

Figure A3-10 - V-I curve knee vs. temperature

# 10. Appendix 4

Typical characteristic curves for 48S12 model

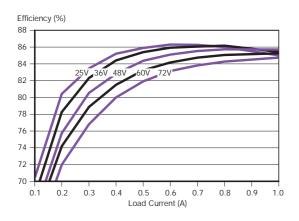

Figure A4-1 - Efficiency vs load and line

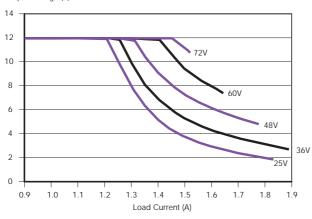

Figure A4-5 - Vout vs. load @ 25°C

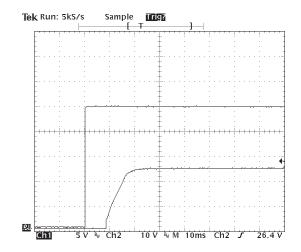

Figure A4-2 - Start-up from 48Vin into 0.93A resistive load

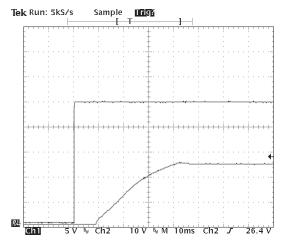

Figure A4-4 - Start-up from 48Vin into 0.93A resistive and 2200µF capacitive load

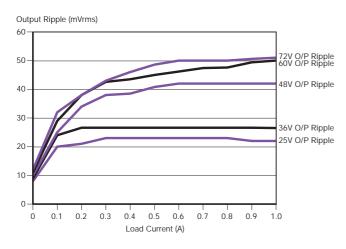

### Typical characteristic curves for 48S12 model continued

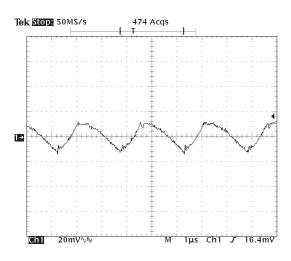

Figure A4-6 - Vo ripple and noise, 20MHz BW

Load Regulation (mV)

Figure A4-8 - Load regulation: 0% to 100% vs. temperature

Figure A4-10 - Efficiency vs. temperature

Figure A4-7 - Ripple and noise vs. temperature

Figure A4-9 - V-I curve knee vs. temperature

Please consult our website for the following items: 🗸 Application Note 🖌 Full Data Sheet 🖌 Simscope™ 🖌 Evaluation Kit http://www.artesyn.com

Data Sheet © Artesyn Technologies® 2000 The information and specifications contained in this data sheet are believed to be correct at time of publication. However, Artesyn Technologies accepts no responsibility for consequences arising from printing errors or inaccuracies. Specifications are subject to change without notice. No rights under any patent accompany the sale of any such product(s) or information contained herein.