## Z86233/243

## CMOS Z8® 8K ROM CONSUMER CONTROLLER PROCESSOR

## **FEATURES**

| Part             | ROM<br>Kbytes | RAM<br>bytes | I/O      | Package<br>Information                                           |

|------------------|---------------|--------------|----------|------------------------------------------------------------------|

| Z86233<br>Z86243 | _             | 237<br>236   | 24<br>32 | 28-pinDIP,SOIC,PLCC<br>40-pin DIP,<br>44-pin PLCC,<br>44-pin QFP |

- 3.0-to 5.5-Volt Operating Range

- Low-Power Consumption: 40 mW (Typical @5.0V)

- 0°C to +70°C Temperature Range

(-40°C to +105°C Temperature Range Available)

- Three Expanded Register File Control Registers

- Z86C33/C43 Pin and Package Compatible Version (With Addition of 4K ROM)

- 32 Input/Output Lines (Three with Comparator Inputs) (Z86243 Only)

- Vectored, Prioritized Interrupts with Programmable Polarity

- Two Comparators

- Two Programmable 8-Bit Counter/Timers, Each with a 6-Bit Programmable Prescaler

- Watch-Dog Timer (WDT)/Power-On Reset (POR)

- On-Chip Oscillator that Accepts a Crystal, Ceramic Resonator, LC, RC, or External Clock Drive

- RAM and ROM Protect

- Clock Free Watch-Dog Timer (WDT) Reset

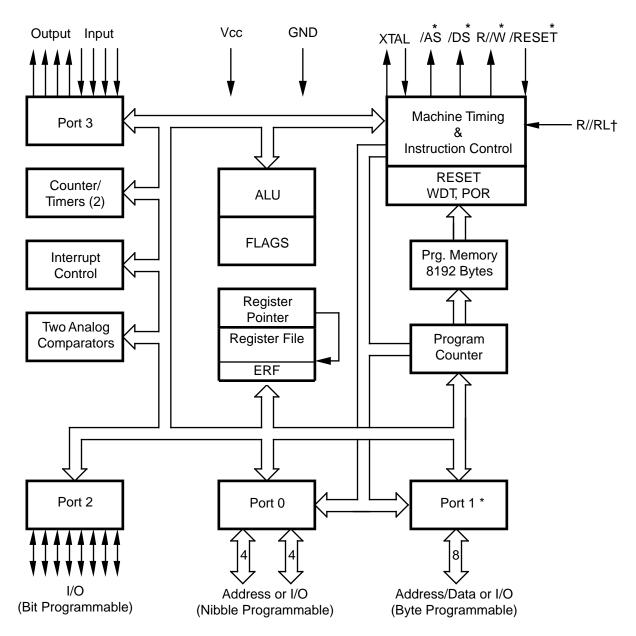

### GENERAL DESCRIPTION

The Z86233/243 Consumer Controller Processor is a member of Zilog's Z8® single-chip microcontroller family featuring enhanced wake-up circuitry, programmable Watch-Dog timers and low-EMI options. The parts provide flexible and efficient growth paths for designers currently using the 4K ROM versions of the consumer controller devices (Z86C30/C40/C33/C43).

Four address spaces, the Program Memory, Register File, Data Memory and Expanded Register File (ERF), support a wide range of memory configurations. Through the ERF, the designer has access to two additional control registers which provide extra peripheral devices, I/O ports, and register addresses.

For applications demanding powerful I/O capabilities, the Z86243 provides 32 pins dedicated to input and output. The Z86233 provides 24 pins dedicated to input and output. These lines are grouped into four ports with eight lines each, and are configurable under software control to provide timing, status signals, or parallel I/O.

With ROM/ROMless selectivity, the Z86243 provides both external memory and pre-programmed ROM, which enables this Z8 microcontroller to be used in high-volume applications, or where code flexibility is required.

**Note:** All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection      | Circuit                | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>Ground | V <sub>cc</sub><br>GND | $egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}$ |

## **GENERAL DESCRIPTION** (Continued)

\* Not available on Z86233. † Available on Z86243 44-Pin QFP and PLCC versions only.

**Functional Block Diagram**

## PIN DESCRIPTION

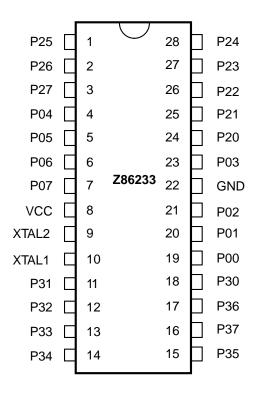

28-Pin DIP/SOIC/PLCC Pin Identification

| Pin # | Symbol   | Function               | Direction    |

|-------|----------|------------------------|--------------|

| 1-3   | P25-P27  | Port 2, Pins 5,6,7     | In/Output    |

| 4-7   | P07-P04  | Port 0, Pins 4,5,6,7   | In/Output    |

| 8     | $V_{CC}$ | Power Supply           |              |

| 9     | XTAL2    | Crystal Oscillator     | Output       |

| 10    | XTAL1    | Crystal Oscillator     | Input        |

| 11-13 | P33-P31  | Port 3, Pins 1,2,3     | Fixed Input  |

| 14-15 | P35-P34  | Port 3, Pins 4,5       | Fixed Output |

| 16    | P37      | Port 3, Pin 7          | Fixed Output |

| 17    | P36      | Port 3, Pin 6          | Fixed Output |

| 18    | P30      | Port 3, Pin 0          | Fixed Input  |

| 19-21 | P02-P00  | Port 0, Pins 0,1,2     | In/Output    |

| 22    | GND      | Ground                 | •            |

| 23    | P03      | Port 0, Pins 3         | In/Output    |

| 24-28 | P24-P20  | Port 2, Pins 0,1,2,3,4 | •            |

|       |          |                        |              |

28-Pin DIP Pin Configuration

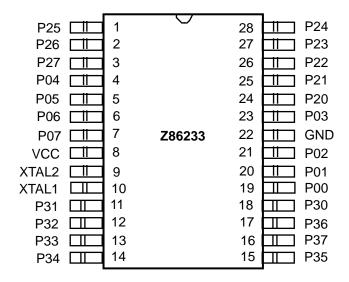

28-Pin SOIC Pin Configuration

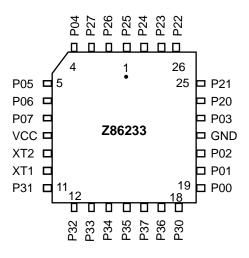

28-Pin PLCC Pin Configuration

## PIN DESCRIPTION (Continued)

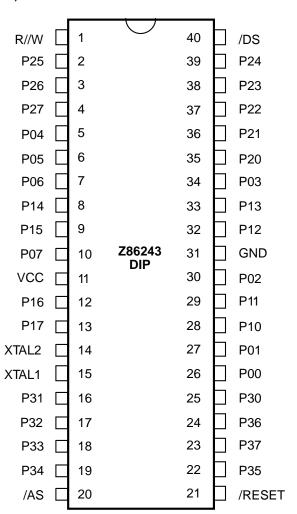

## **40-Pin DIP Pin Configuration**

## 40-Pin DIP Pin Configuaration

| Pin#            | Symbol                            | Function                                           | Direction              |

|-----------------|-----------------------------------|----------------------------------------------------|------------------------|

| 1               | R//W                              | Read/Write                                         | Output                 |

| 2-4             | P25-P27                           | Port 2, Pins 5, 6, 7                               | In/Output              |

| 5-7             | P04-P06                           | Port 0, Pins 4, 5, 6                               | In/Output              |

| 8-9<br>10<br>11 | P14-P15<br>P07<br>V <sub>cc</sub> | Port 1, Pins 4, 5<br>Port 0, Pin 7<br>Power Supply | In/Output<br>In/Output |

| 12-13           | P16-P17                           | Port 1, Pins 6, 7                                  | In/Output              |

| 14              | XTAL2                             | Crystal Oscillator                                 | Output                 |

| 15              | XTAL1                             | Crystal Oscillator                                 | Input                  |

| 16-18           | P31-P33                           | Port 3, Pins 1, 2, 3                               | Input                  |

| 19              | P34                               | Port 3, Pin 4                                      | Output                 |

| 20              | /AS                               | Address Strobe                                     | Output                 |

| 21              | /RESET                            | Reset                                              | Input                  |

| Pin#  | Symbol  | Function               | Direction           |

|-------|---------|------------------------|---------------------|

| 22    | P35     | Port 3, Pin 5          | Output              |

| 23    | P37     | Port 3, Pin 7          | Output              |

| 24    | P36     | Port 3, Pin 6          | Output              |

| 25    | P30     | Port 3, Pin 0          | Input               |

| 26-27 | P00-P01 | Port 0, Pins 0,1       | In/Output           |

| 28-29 | P10-P11 | Port 1, Pins 0,1       | In/Output           |

| 30    | P02     | Port 0, Pin 2          | In/Output In/Output |

| 31    | GND     | Ground                 |                     |

| 32-33 | P12-P13 | Port 1, Pins 2, 3      |                     |

| 34    | P03     | Port 0, Pin 3          | In/Output           |

| 35-39 | P20-P24 | Port 2, Pins 0,1,2,3,4 | In/Output           |

| 40    | /DS     | Data Strobe            | Output              |

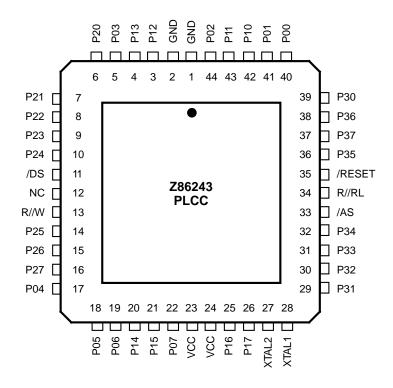

## 44-Pin PLCC Pin Configuration

#### 44-Pin PLCC Pin Identification

| Pin # | Symbol          | Function               | Direction |

|-------|-----------------|------------------------|-----------|

| 1     | GND             | Ground                 |           |

| 2     | GND             | Ground                 |           |

| 3-4   | P12-P13         | Port 1, Pins 2,3       | In/Output |

| 5     | P03             | Port 0, Pin 3          | In/Output |

| 6-10  | P20-P24         | Port 2, Pins 0,1,2,3,4 | In/Output |

| 11    | /DS             | Data Strobe            | Output    |

| 12    | N/C             | Not Connected          |           |

| 13    | R//W            | Read/Write             | Output    |

| 14-16 | P25-P27         | Port 2, Pins 5,6,7     | In/Output |

| 17-19 | P04-P06         | Port 0, Pins 4,5,6     | In/Output |

| 20-21 | P14-P15         | Port 1, Pins 4,5       | In/Output |

| 22    | P07             | Port 0, Pin 7          | In/Output |

| 23    | $V_{CC}$        | Power Supply           |           |

| 24    | V <sub>CC</sub> | Power Supply           |           |

| 25-26 | PĬĞ-P17         | Port 1, Pins 6,7       | In/Output |

| Pin#  | Symbol  | Function           | Direction |

|-------|---------|--------------------|-----------|

| 27    | XTAL2   | Crystal Oscillator | Output    |

| 28    | XTAL1   | Crystal Oscillator | Input     |

| 29-31 | P31-P33 | Port 3, Pins 1,2,3 | Input     |

| 32    | P34     | Port 3, Pin 4      | Output    |

| 33    | /AS     | Address Strobe     | Output    |

| 34    | R//RL   | ROM/ROMless select | Input     |

| 35    | /RESET  | Reset              | Input     |

| 36    | P35     | Port 3, Pin 5      | Output    |

| 37    | P37     | Port 3, Pin 7      | Output    |

| 38    | P36     | Port 3, Pin 6      | Output    |

| 39    | P30     | Port 3, Pin 0      | Input     |

| 40-41 | P00-P01 | Port 0, Pins 0,1   | In/Output |

| 42-43 | P10-P11 | Port 1, Pins 0,1   | In/Output |

| 44    | P02     | Port 0, Pin 2      | In/Output |

## PIN DESCRIPTION (Continued)

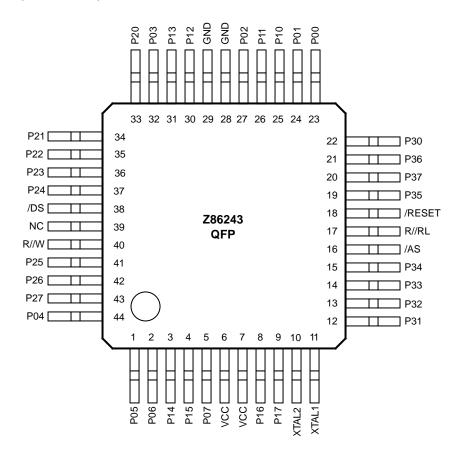

44-Pin QFP Pin Configuration

## 44-Pin QFP Pin Identification

| Pin # | Symbol   | Function           | Direction |

|-------|----------|--------------------|-----------|

| 1-2   | P05-P06  | Port 0, Pins 5,6   | In/Output |

| 3-4   | P14-P05  | Port 1, Pins 4,5   | In/Output |

| 5     | P07      | Port 0, Pin 7      | In/Output |

| 6-7   | $V_{CC}$ | Power Supply       | ·         |

| 8-9   | PĬĞ-P17  | Port 1, Pins 6,7   | In/Output |

| 10    | XTAL2    | Crystal Oscillator | Output    |

| 11    | XTAL1    | Crystal Oscillator | Input     |

| 12-14 | P31-P33  | Port 3, Pins 1,2,3 | Input     |

| 15    | P34      | Port 3, Pin 4      | Output    |

| 16    | /AS      | Address Strobe     | Output    |

| 17    | R//RL    | ROM/ROMless select | Input     |

| 18    | /RESET   | Reset              | Input     |

| 19    | P35      | Port 3, Pin 5      | Output    |

| 20    | P37      | Port 3, Pin 7      | Output    |

| Pin # | Symbol  | Function               | Direction |

|-------|---------|------------------------|-----------|

| 21    | P36     | Port 3, Pin 6          | Output    |

| 22    | P30     | Port 3, Pin 0          | Input     |

| 23-24 | P00-P01 | Port 0, Pin 0,1        | In/Output |

| 25-26 | P10-P11 | Port 1, Pins 0,1       | In/Output |

| 27    | P02     | Port 0, Pin 2          | In/Output |

| 28    | GND     | Ground                 | -         |

| 29    | GND     | Ground                 |           |

| 30-31 | P12-P13 | Port 1, Pins 2,3       | In/Output |

| 32    | P03     | Port 0, Pin 3          | In/Output |

| 33-37 | P20-24  | Port 2, Pins 0,1,2,3,4 | In/Output |

| 38    | /DS     | Data Strobe            | Output    |

| 39    | N/C     | Not Connected          | •         |

| 40    | R//W    | Read/Write             | Output    |

| 41-43 | P25-P27 | Port 2, Pins 5,6,7     | In/Output |

| 44    | P04     | Port 0, Pin 4          | In/Output |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                                 | Min  | Max          | Units |

|---------------------------------------------------------------------------|------|--------------|-------|

| Ambient Temperature under Bias                                            | -40  | +105         | С     |

| Storage Temperature                                                       | -65  | +150         | С     |

| Voltage on any Pin with Respect to V <sub>ss</sub> [Note 1]               | -0.6 | +7           | V     |

| Voltage on V <sub>DD</sub> Pin with Respect to V <sub>SS</sub>            | -0.3 | +7           | V     |

| Voltage on XTAL1 and /RESET Pins with Respect to V <sub>ss</sub> [Note 2] | -0.6 | $V_{DD} + 1$ | V     |

| Total Power Dissipation                                                   |      | 1.21         | W     |

| Maximum Allowable Current out of V <sub>ss</sub>                          |      | 220          | mA    |

| Maximum Allowable Current into V <sub>DD</sub>                            |      | 180          | mA    |

| Maximum Allowable Current into an Input Pin [Note 3]                      | -600 | +600         | μΑ    |

| Maximum Allowable Current into an Open-Drain Pin [Note 4]                 | -600 | +600         | μA    |

| Maximum Allowable Output Current Sinked by Any I/O Pin                    |      | 25           | mΑ    |

| Maximum Allowable Output Current Sourced by Any I/O Pin                   |      | 25           | mA    |

#### Notes:

- [1] This applies to all pins except XTAL pins and where otherwise noted.

- [2] There is no input protection diode from pin to  $V_{nn}$ .

- [3] This excludes XTAL pins.

- [4] Device pin is not at an output Low state.

#### Notice:

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

Total power dissipation should not exceed 1.21 W for the package. Power dissipation is calculated as follows:

$$\begin{aligned} \text{Total Power Dissipation} &= V_{_{DD}} \text{ x } \left[ \text{ I}_{_{DD}} - \left( \text{sum of I}_{_{OH}} \right) \text{ } \right] \\ &+ \text{ sum of } \left[ \text{ } \left( V_{_{DD}} - V_{_{OH}} \right) \text{ x I}_{_{OH}} \right] \\ &+ \text{ sum of } \left( V_{_{0L}} \text{ x I}_{_{0L}} \right) \end{aligned}$$

## STANDARD TEST CONDITIONS

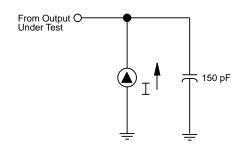

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Test Load).

**Test Load Diagram**

#### CAPACITANCE

$T_A = 25$ °C,  $V_{CC} = GND = 0V$ , f = 1.0 MHz; unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

## DC ELECTRICAL CHARACTERISTICS

|                                |                          | $V_{cc}$     | $T_A = to + 7$                                          |                                                             | $T_A = -t$                                              |                                                             | Typical [  | 11       |                                                          |              |

|--------------------------------|--------------------------|--------------|---------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|------------|----------|----------------------------------------------------------|--------------|

| Sym                            | Parameter                | Note [3]     | Min                                                     | Max                                                         | Min                                                     | Max                                                         | @ 25°C     |          | Conditions                                               | Notes        |

| $V_{\text{CH}}$                | Clock Input High Voltage |              | 0.7 V <sub>cc</sub>                                     | V <sub>cc</sub> +0.3                                        | 0.7 V <sub>cc</sub>                                     | V <sub>cc</sub> +0.3                                        | 1.8        | V        | Driven by External Clock Generator                       |              |

|                                |                          | 5.5V         | $0.7  V_{\rm cc}$                                       | V <sub>CC</sub> +0.3                                        | $0.7 V_{cc}$                                            | V <sub>CC</sub> +0.3                                        | 2.6        | V        | Driven by External Clock Generator                       |              |

| $\overline{V_{\text{CL}}}$     | Clock Input Low Voltage  | 3.0V         | GND-0.3                                                 | 0.2 V <sub>CC</sub>                                         | GND-0.3                                                 | 0.2 V <sub>cc</sub>                                         | 1.2        | V        | Driven by External Clock Generator                       |              |

| W                              | Innut I ligh Voltage     | 5.5V         | GND-0.3                                                 | 0.2 V <sub>cc</sub>                                         | GND-0.3                                                 |                                                             | 2.1        | V        | Driven by External Clock Generator                       |              |

| $V_{IH}$                       | Input High Voltage       | 3.0V<br>5.5V | $0.7 \text{ V}_{\text{cc}}$ $0.7 \text{ V}_{\text{cc}}$ | $V_{cc} + 0.3$<br>$V_{cc} + 0.3$                            | $0.7 \text{ V}_{\text{cc}}$ $0.7 \text{ V}_{\text{cc}}$ | $V_{cc} + 0.3$<br>$V_{cc} + 0.3$                            | 1.8<br>2.6 | V<br>V   |                                                          |              |

| V <sub>IL</sub>                | Input Low Voltage        | 3.0V         | GND-0.3                                                 |                                                             | GND-0.3                                                 | 0.2 V <sub>CC</sub>                                         | 1.1        | V        |                                                          |              |

|                                | 0                        | 5.5V         | GND-0.3                                                 | $0.2\mathrm{V_{CC}^{cc}}$                                   | GND-0.3                                                 | $0.2~\mathrm{V}_{\mathrm{cc}}$                              | 1.6        | V        |                                                          | [0]          |

| $V_{OH1}$                      | Output High Voltage      | 3.0V         | $V_{\rm CC}$ -0.4                                       |                                                             | V <sub>CC</sub> -0.4                                    |                                                             | 3.1        | V        | $I_{OH} = -2.0 \text{ mA}$                               | [8]          |

|                                |                          | 5.5V         | V <sub>cc</sub> -0.4                                    |                                                             | V <sub>cc</sub> -0.4                                    |                                                             | 4.8        | V        | $I_{OH}^{ST} = -2.0 \text{ mA}$                          | [8]          |

| $V_{OL1}$                      | Output Low Voltage       | 3.0V         |                                                         | 0.6                                                         |                                                         | 0.6                                                         | 0.2        | V        | $I_{OL} = +4.0 \text{ mA}$                               | [8]          |

| .,                             | 0 1 11 1/1               | 5.5V         |                                                         | 0.4                                                         |                                                         | 0.4                                                         | 0.1        | V        | $I_{OL}^{OL} = +4.0 \text{ mA}$                          | [8]          |

| $V_{OL2}$                      | Output Low Voltage       | 3.0V<br>5.5V |                                                         | 1.2<br>1.2                                                  |                                                         | 1.2<br>1.2                                                  | 0.3<br>0.4 | V<br>V   | $I_{OL}^{OL} = +6 \text{ mA}$                            | [8]<br>[8]   |

|                                |                          | 3.3V         |                                                         |                                                             |                                                         |                                                             |            |          | I <sub>OL</sub> = +12 mA                                 |              |

| $V_{RH}$                       | Reset Input High Voltage | 3.0V         | .8 V <sub>cc</sub>                                      | V <sub>cc</sub>                                             | .8 V <sub>CC</sub>                                      | V <sub>CC</sub>                                             | 1.8        | V        |                                                          | [13]         |

| M                              | Doost Innut Low Voltage  | 5.5V         | .8 V <sub>CC</sub>                                      | V <sub>CC</sub>                                             | .8 V <sub>cc</sub>                                      | V <sub>CC</sub>                                             | 2.6        | V        |                                                          | [13]         |

| $V_{RI}$                       | Reset Input Low Voltage  | 3.0V<br>5.5V | GND-0.3<br>GND-0.3                                      | $0.2\mathrm{V}_{\mathrm{cc}}$ $0.2\mathrm{V}_{\mathrm{cc}}$ | GND-0.3<br>GND-0.3                                      | $0.2\mathrm{V}_{\mathrm{cc}}$ $0.2\mathrm{V}_{\mathrm{cc}}$ | 1.1<br>1.6 | V<br>V   |                                                          | [13]<br>[13] |

| $V_{\scriptscriptstyle OLR}$   | Reset Output Low Voltage |              | GIVD-0.5                                                | 0.2 v <sub>cc</sub>                                         | GIVD-0.5                                                | 0.2 <b>v</b> <sub>cc</sub>                                  | 0.3        | V        | $I_{OL} = +1.0 \text{ mA}$                               | [13]         |

| OLR                            |                          | 5.5V         |                                                         | 0.6                                                         |                                                         | 0.6                                                         | 0.2        | V        | $I_{0L}^{0L} = +1.0 \text{ mA}$                          | [13]         |

| $\overline{V}_{\text{OFFSET}}$ | Comparator Input Offset  | 3.0V         |                                                         | 25                                                          |                                                         | 25                                                          | 10         | mV       |                                                          | [10]         |

|                                | Voltage                  | 5.5V         |                                                         | 25                                                          |                                                         | 25                                                          | 10         | mV       |                                                          | [10]         |

| I                              | Input Leakage            | 3.0V         | -1<br>1                                                 | 1                                                           | -1                                                      | 2                                                           | 0.004      | μA       | $V_{IN} = OV, V_{CC}$                                    |              |

|                                |                          | 5.5V         | -1                                                      | 1                                                           | -1                                                      | 2                                                           | 0.004      | μA       | $V_{IN} = OV, V_{CC}$                                    |              |

| $I_{OL}$                       | Output Leakage           | 3.0V         | -1                                                      | 1                                                           | -1                                                      | 2                                                           | 0.004      | μA       | $V_{IN} = OV, V_{CC}$                                    |              |

|                                | Dood Innut Current       | 5.5V         | -1<br>20                                                | 1                                                           | -1<br>10                                                | 2                                                           | 0.004      | μA       | $V_{IN} = OV, V_{CC}$                                    |              |

| I <sub>IR</sub>                | Reset Input Current      | 3.0V<br>5.5V | -20<br>-20                                              | -130<br>-180                                                | -18<br>-18                                              | -130<br>-180                                                | -60<br>-85 | μA<br>μA |                                                          |              |

|                                |                          |              | -20                                                     |                                                             | -10                                                     |                                                             |            |          |                                                          |              |

| I <sub>CC</sub>                | Supply Current           | 3.0V         |                                                         | 20                                                          |                                                         | 20                                                          | 7          | mΑ       | @ 16 MHz                                                 | [4]          |

|                                |                          | 5.5V         |                                                         | 25<br>15                                                    |                                                         | 25<br>15                                                    | 20<br>5    | mA<br>mA | @ 16 MHz<br>@ 12 MHz                                     | [4]          |

|                                |                          | 3.0V<br>5.5V |                                                         | 20                                                          |                                                         | 20                                                          | 5<br>15    | mA       | @ 12 MHz                                                 | [4]<br>[4]   |

| I <sub>CC1</sub>               | Standby Current          | 3.0V         |                                                         | 4.5                                                         |                                                         | 4.5                                                         | 2.0        | mA       | V <sub>IN</sub> = OV, V <sub>CC</sub> @ 16 MHz           | [4]          |

| CCT                            | (Halt Mode)              | 5.5V         |                                                         | 8                                                           |                                                         | 8                                                           | 3.7        | mA       | $V_{IN} = OV, V_{CC} @ 16 MHz$                           | [4]          |

|                                |                          | 3.0V         |                                                         | 3.4                                                         |                                                         | 3.4                                                         | 1.5        | mA       | Clock Divide-by-16 @ 16 MHz                              | [4]          |

|                                |                          | 5.5V         |                                                         | 7.0                                                         |                                                         | 7.0                                                         | 2.9        | mA       | Clock Divide-by-16 @ 16 MHz                              | [4]          |

| I <sub>CC2</sub>               | Standby Current          | 3.0V         |                                                         | 8                                                           |                                                         | 8                                                           | 2          | μA       | V <sub>IN</sub> = OV, V <sub>CC</sub> WDT is not Running | [6,11]       |

| 002                            | (Stop Mode)              | 5.5V         |                                                         | 10                                                          |                                                         | 10                                                          | 4          | μΑ       | $V_{IN} = OV$ , $V_{CC}$ WDT is not Running              | [6,11]       |

|                                |                          | 3.0V         |                                                         | 500                                                         |                                                         | 600                                                         | 310        | μA       |                                                          | 6,11,14]     |

|                                |                          | 5.5V         |                                                         | 800                                                         |                                                         | 1000                                                        | 600        | μA       | $V_{IN} = OV, V_{CC} WDT$ is Running [                   | 6,11,14]     |

9

## DC ELECTRICAL CHARACTERISTICS (Continued)

|                        |                                                   | V <sub>cc</sub> | $T_A = 0^{\circ} C$<br>to +70°C              |                                                | $T_A = -40$ °C to +105°C                     |                                                | Typical [1] |          |                                                                                |                  |

|------------------------|---------------------------------------------------|-----------------|----------------------------------------------|------------------------------------------------|----------------------------------------------|------------------------------------------------|-------------|----------|--------------------------------------------------------------------------------|------------------|

| Sym                    | Parameter                                         | Note [3]        | Min                                          | Max                                            | Min                                          | Max                                            | @ 25°C      | Units    | Conditions                                                                     | Notes            |

| VICR                   | Input Common Mode<br>Voltage Range                | 3.0<br>5.5      |                                              | V <sub>cc</sub> -1.0V<br>V <sub>cc</sub> -1.0V |                                              | V <sub>cc</sub> -1.5V<br>V <sub>cc</sub> -1.5V |             | V<br>V   |                                                                                | [10]<br>[10]     |

| I <sub>ALL</sub>       | Auto Latch Low Current                            | 3.0V<br>5.5V    |                                              | 8<br>15                                        |                                              | 10<br>20                                       | 3<br>5      | μA<br>μA | $OV < V_{IN} < V_{CC}$<br>$OV < V_{IN} < V_{CC}$                               | [9]<br>[9]       |

| l <sub>ALH</sub>       | Auto Latch High Current                           |                 |                                              | -5<br>-8                                       |                                              | -7<br>-10                                      | -3<br>-6    | μΑ<br>μΑ | $ \begin{array}{ll} OV < V_{IN} < V_{CC} \\ OV < V_{IN} < V_{CC} \end{array} $ | [9]<br>[9]       |

| $\overline{V_{_{LV}}}$ | V <sub>cc</sub> Low Voltage<br>Protection Voltage |                 | 2.4                                          | 3.1                                            | 2.1                                          | 3.3                                            | 2.8<br>2.8  | V        | 4 MHz max Int. CLK Freq.<br>6 MHz max Int. CLK Freq.                           | [7,15]<br>[7,14] |

| $\overline{V}_{OH}$    | Output High Voltage<br>(Low EMI Mode)             | 3.3V<br>5.0V    | V <sub>CC</sub> -0.4<br>V <sub>CC</sub> -0.4 |                                                | V <sub>CC</sub> -0.4<br>V <sub>CC</sub> -0.4 |                                                | 3.1<br>4.8  | V<br>V   | I <sub>OH</sub> = -0.5 mA<br>I <sub>OH</sub> = -0.5 mA                         |                  |

| $\overline{V}_{OL}$    | Output Low Voltage<br>(Low EMI Mode)              | 3.3V<br>5.0V    |                                              | 0.6<br>0.4                                     |                                              | 0.6<br>0.4                                     | 0.2<br>0.1  | V<br>V   | $I_{OL} = 1.0 \text{ mA}$<br>$I_{OL} = 1.0 \text{ mA}$                         |                  |

#### Notes:

- [1] Typicals are at  $V_{CC} = 5.0V$  and 3.3V.

- $\mathsf{GND} = \mathsf{OV}.$

- The  $V_{\text{DD}}$  voltage specification of 3.0V guarantees 3.3V  $\pm 0.3$ V, and the  $V_{DD}$  voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V. [4] All outputs unloaded, I/O pins floating, inputs at rail.

- [5] CL1 = CL2 = 100 pF.

- [6] Same as note [4] except inputs at V<sub>cc</sub>.

- [7] The  $V_{1V}$  increases as the temperature decreases.

- [8] Standard Mode (not Low EMI).

- [9] Auto Latch (Mask Option) selected.

- [10] For analog comparator, inputs when analog comparators are enabled.

- [11] Clock must be forced Low, when XTAL 1 is clock-driven and XTAL2 is floating.

- [12] Excludes clock pins.

- [13] Z86243 Only.

- [14] 0°C to 70°C (standard temperature).

- [14] -40°C to 105°C (extended temperature).

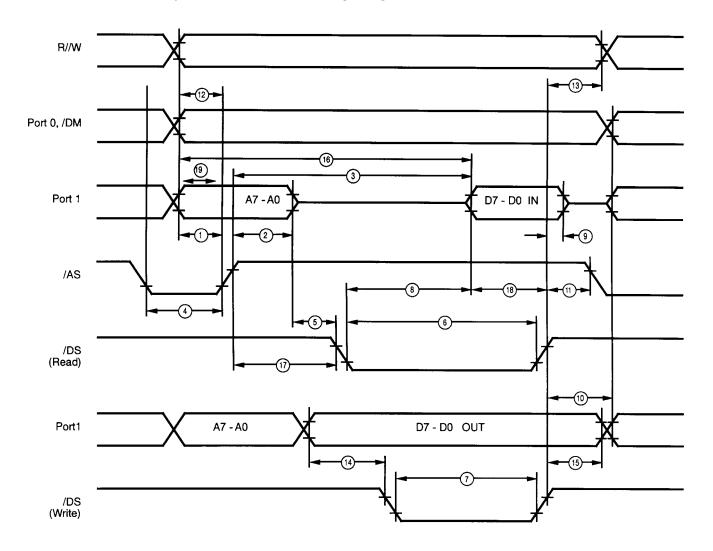

**AC CHARACTERISTICS**External I/O or Memory Read and Write Timing Diagram

External I/O or Memory Read/Write Timing

## **AC CHARACTERISTICS**

External I/O or Memory Read and Write Timing Table (SCLK/TCLK = XTAL/2)

|    |           |                                            | $T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$<br>Note [3] 12 MHz 16 MHz |                 |            |                |            | T <sub>A</sub> = 12 N | –40°С<br>лн <sub>т</sub> | to +10         |            |                |       |

|----|-----------|--------------------------------------------|-----------------------------------------------------------------------------|-----------------|------------|----------------|------------|-----------------------|--------------------------|----------------|------------|----------------|-------|

| No | Symbol    | Parameter                                  | V <sub>CC</sub>                                                             | Min             | Max        | Min            | Max        | Min                   | Max                      | Min            | Max        | Units          | Notes |

| 1  | TdA(AS)   | Address Valid to /AS Rise Delay            | 3.0<br>5.5                                                                  | 35<br>35        |            | 25<br>25       |            | 35<br>35              |                          | 25<br>25       |            | ns             | [2]   |

| 2  | TdAS(A)   | /AS Rise to Address Float Delay            | 3.0<br>5.5                                                                  | 45<br>45        |            | 35<br>35       |            | 45<br>45              |                          | 35<br>35       |            | ns<br>ns       | [2]   |

| 3  | TdAS(DR)  | /AS Rise to Read Data Req'd Valid          | 3.0                                                                         |                 | 250        |                | 180        |                       | 250                      |                | 180        | ns             | [1,2] |

| 4  | TwAS      | /AS Low Width                              | 5.5<br>3.0<br>5.5                                                           | 55<br>55        | 250        | 40<br>40       | 180        | 55<br>55              | 250                      | 40<br>40       | 180        | ns<br>ns<br>ns | [2]   |

| 5  | Td        | Address Float to /DS Fall                  | 3.0<br>5.5                                                                  | 0               |            | 0              |            | 0                     |                          | 0              |            | ns<br>ns       |       |

| 6  | TwDSR     | /DS (Read) Low Width                       | 3.0<br>5.5                                                                  | 200<br>200      |            | 135<br>135     |            | 200<br>200            |                          | 135<br>135     |            | ns<br>ns       | [1,2] |

| 7  | TwDSW     | /DS (Write) Low Width                      | 3.0<br>5.5                                                                  | 110<br>110      |            | 80<br>80       |            | 110<br>110            |                          | 80<br>80       |            | ns<br>ns       | [1,2] |

| 8  | TdDSR(DR) | /DS Fall to Read Data Req'd Valid          | 3.0<br>5.5                                                                  |                 | 150<br>150 |                | 75<br>75   |                       | 150<br>150               |                | 75<br>75   | ns<br>ns       | [1,2] |

| 9  | ThDR(DS)  | Read Data to /DS Rise Hold Time            | 3.0<br>5.5                                                                  | 0               |            | 0              |            | 0                     |                          | 0              |            | ns<br>ns       | [2]   |

| 10 | TdDS(A)   | /DS Rise to Address Active Delay           | 3.0<br>5.5                                                                  | 45<br>55        |            | 50<br>50       |            | 45<br>55              |                          | 50<br>50       |            | ns<br>ns       | [2]   |

| 11 | TdDS(AS)  | /DS Rise to /AS Fall Delay                 | 3.0<br>5.5                                                                  | 30<br>45        |            | 35<br>35       |            | 30<br>45              |                          | 35<br>55       |            | ns             | [2]   |

| 12 | TdR/W(AS) | R//W Valid to /AS Rise Delay               | 3.0<br>5.5                                                                  | 45<br>45<br>45  |            | 25<br>25       |            | 45<br>45<br>45        |                          | 25<br>25       |            | ns<br>ns<br>ns | [2]   |

| 13 | TdDS(R/W) | /DS Rise to R//W Not Valid                 | 3.0<br>5.5                                                                  | 45<br>45        |            | 35<br>35       |            | 45<br>45              |                          | 35<br>35       |            | ns<br>ns       | [2]   |

| 14 | TdDW(DSW) | Write Data Valid to /DS Fall (Write) Delay |                                                                             | 55<br>55        |            | 25<br>25       |            | 55<br>55              |                          | 25<br>25       |            | ns<br>ns       | [2]   |

| 15 | TdDS(DW)  | /DS Rise to Write Data Not Valid Delay     | 3.0<br>5.5                                                                  | 45<br>55        |            | 35<br>35       |            | 45<br>55              |                          | 35<br>35       |            | ns<br>ns       | [2]   |

| 16 | TdA(DR)   | Address Valid to Read Data Req'd Valid     | 3.0<br>5.5                                                                  | 00              | 310<br>310 | 00             | 230<br>230 | 00                    | 310<br>310               | 00             | 230<br>230 | ns<br>ns       | [1,2] |

| 17 | TdAS(DS)  | /AS Rise to /DS Fall Delay                 | 3.0                                                                         | 65              |            | 45<br>45       |            | 65<br>45              |                          | 45<br>45       |            | ns             | [2]   |

| 18 | TdDI(DS)  | Data Input Setup to /DS Rise               | 5.5<br>3.0<br>5.5                                                           | 65<br>115<br>75 |            | 45<br>60<br>60 |            | 65<br>115<br>75       |                          | 45<br>60<br>60 |            | ns<br>ns<br>ns | [1,2] |

| 19 | TdDM(AS)  | /DM Valid to /AS Rise Delay                | 3.0                                                                         | 35              |            | 30             |            | 35                    |                          | 30             |            | ns             | [2]   |

|    |           |                                            | 5.5                                                                         | 35              |            | 30             |            | 35                    |                          | 30             |            | ns             |       |

Notes:

[1] When using extended memory timing add 2 TpC.

[2] Timing numbers given are for minimum TpC.

[3] The  $V_{DD}$  voltage specification of 3.0V guarantees 3.3V  $\pm 0.3$ V, and the  $V_{DD}$  voltage specification of 5.5V guarantees 5.0V  $\pm 0.5$ V.

### **Standard Test Load**

All timing references use 0.7  $\rm V_{\rm cc}$  for a logic 1 and 0.2  $\rm V_{\rm cc}$  for a logic 0.

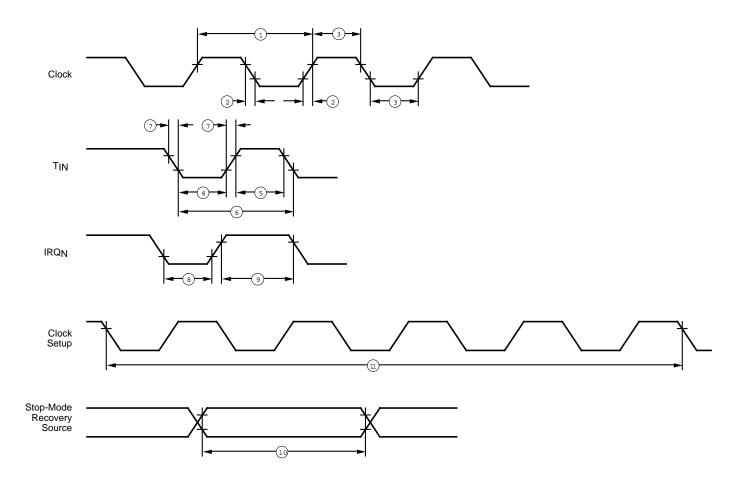

# **AC ELECTRICAL CHARACTERISTICS** Additional Timing Diagram

**Additional Timing**

AC ELECTRICAL CHARACTERISTICS

Additional Timing Table (SCLK/TCLK = XTAL/2)

|    |           | V <sub>cc</sub>               | $T_A = 0$ °C to +70°C<br>12 MHz 16 MHz |      |          |      | T <sub>A</sub> = | = –40°C<br>MHz |          | to +105°C<br>16 MHz |          |       |           |           |

|----|-----------|-------------------------------|----------------------------------------|------|----------|------|------------------|----------------|----------|---------------------|----------|-------|-----------|-----------|

| No | Symbol    | Parameter                     | Note[6]                                | Min  | Max      | Min  | Max              | Min            | Max      | Min                 |          | Units | No        | tes       |

| 1  | ТрС       | Input Clock Period            | 3.0V                                   | 83   | DC       | 62.5 | DC               | 83             | DC       | 62.5                | DC       | ns    | [1]       |           |

| •  | T 0 T(0   | 01 11 18 05 117               | 5.5V                                   | 83   | DC       | 62.5 | DC               | 83             | DC       | 62.5                | DC       | ns    | [1]       |           |

| 2  | TrC,TfC   | Clock Input Rise & Fall Times | 3.0V<br>5.5V                           |      | 15<br>15 |      | 15<br>15         |                | 15<br>15 |                     | 15<br>15 | ns    | [1]       |           |

|    |           |                               |                                        |      | 10       |      | 10               |                | 10       |                     | 10       | ns    | [1]       |           |

| 3  | TwC       | Input Clock Width             | 3.0V                                   | 41   |          | 31   |                  | 41             |          | 31                  |          | ns    | [1]       |           |

|    |           |                               | 5.5V                                   | 41   |          | 31   |                  | 41             |          | 31                  |          | ns    | [1]       |           |

| 4  | TwTinL    | Timer Input Low Width         | 3.0V                                   | 100  |          | 100  |                  | 100            |          | 100                 |          | ns    | [1]       |           |

|    |           |                               | 5.5V                                   | 70   |          | 70   |                  | 70             |          | 70                  |          | ns    | [1]       |           |

| 5  | TwTinH    | Timer Input High Width        | 3.0V                                   | 5TpC |          | 5TpC |                  | 5TpC           |          | 5TpC                |          |       | [1]       |           |

|    |           |                               | 5.5V                                   | 5TpC |          | 5TpC |                  | 5TpC           |          | 5TpC                |          |       | [1]       |           |

| 6  | TpTin     | Timer Input Period            | 3.0V                                   | 8TpC |          | 8TpC |                  | 8TpC           |          | 8TpC                |          |       | [1]       |           |

|    |           |                               | 5.5V                                   | 8TpC |          | 8TpC |                  | 8TpC           |          | 8TpC                |          |       | [1]       |           |

| 7  | TrTin,    | Timer Input Rise & Fall Timer | 3.0V                                   |      | 100      |      | 100              |                | 100      |                     | 100      | ns    | [1]       |           |

|    | TfTin     | •                             | 5.5V                                   |      | 100      |      | 100              |                | 100      |                     | 100      | ns    | [1]       |           |

| 88 | TwIL      | Int. Request Low Time         | 3.0V                                   | 100  |          | 100  |                  | 100            |          | 100                 |          | ns    | [1,2      | 2]        |

|    |           |                               | 5.5 <b>V</b>                           | 70   |          | 70   |                  | 70             |          | 70                  |          | ns    | [1,2      | 2]        |

| 8B | TwlL      | Int. Request Low Time         | 3.0V                                   | 5TpC |          | 5TpC |                  | 5TpC           |          | 5TpC                |          |       | [1,3      | 3]        |

|    |           |                               | 5.5V                                   | 5TpC |          | 5TpC |                  | 5TpC           |          | 5TpC                |          |       | [1,3      | 3]        |

| 9  | TwIH      | Int. Request Input High Time  | 3.0V                                   | 5TpC |          | 5TpC |                  | 5TpC           |          | 5TpC                |          |       | [1,2      |           |

|    |           |                               | 5.5V                                   | 5TpC |          | 5TpC |                  | 5TpC           |          | 5TpC                |          |       | [1,2      | 2]        |

| 10 | Twsm      | STOP-Mode Recovery Width Spec | 3.0V                                   | 12   |          | 12   |                  | 12             |          | 12                  |          | ns    |           |           |

|    |           |                               | 5.5V                                   | 12   |          | 12   |                  | 12             |          | 12                  |          | ns    |           |           |

| 11 | Tost      | Oscillator Startup Time       | 3.0V                                   |      | 5TpC     |      | 5TpC             |                | 5TpC     |                     | 5TpC     |       | [4]       |           |

|    |           |                               | 5.5V                                   |      | 5TpC     |      | 5TpC             |                | 5TpC     |                     | 5TpC     |       | [4]       |           |

| 12 | Twdt      | Watch-Dog Timer Delay Time    |                                        |      |          |      |                  |                |          |                     |          |       | <u>D1</u> | <u>D0</u> |

|    |           | Before Time-Out               | 3.0V                                   | 10   |          | 10   |                  | 10             |          | 10                  |          | ms    | 0         | 0 [5]     |

|    |           |                               | 5.5 <b>V</b>                           | 5    |          | 5    |                  | 5              |          | 5                   |          | ms    | 0         | 0 [5]     |

|    |           |                               | 3.0V                                   | 20   |          | 20   |                  | 20             |          | 20                  |          | ms    | 0         | 1 [5]     |

|    |           |                               | 5.5V                                   | 10   |          | 10   |                  | 10             |          | 10                  |          | ms    |           | 1 [5]     |

|    |           |                               | 3.0V                                   | 40   |          | 40   |                  | 40             |          | 40                  |          | ms    |           | 0 [5]     |

|    |           |                               | 5.5V                                   | 20   |          | 20   |                  | 20             |          | 20                  |          | ms    |           | 0 [5]     |

|    |           |                               | 3.0V                                   | 160  |          | 160  |                  | 160            |          | 160                 |          | ms    |           | 1 [5]     |

|    |           |                               | 5.5V                                   | 80   |          | 80   |                  | 80             |          | 80                  |          | ms    | ı         | 1 [5]     |

| 13 | $T_{POR}$ | Power On Reset Delay          | 3.0V                                   | 7    | 24       | 7    | 24               | 7              | 25       | 7                   | 25       | ms    |           |           |

|    |           |                               | 5.5 <b>V</b>                           | 3    | 13       | 3    | 13               | 3              | 14       | 3                   | 14       | ms    |           |           |

#### Notes:

Timing Reference uses 0.7 V<sub>cc</sub> for a logic 1 and 0.2 V<sub>cc</sub> for a logic 0.

Interrupt request via Port 3 (P31-P33).

Interrupt request via Port 3 (P30).

<sup>[4]</sup> SMR-D5 = 0.

<sup>[5]</sup> Reg. WDTMR, internal RC used.

<sup>[6]</sup> The  $V_{DD}$  voltage specification of 3.0V guarantees 3.3V  $\pm$ 0.3V, and the  $V_{DD}$  voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V.

## **AC ELECTRICAL CHARACTERISTICS**

Additional Timing Table (Divide-By-One Mode, SCLK/TCLK = XTAL)

| No | Constant | Darameter                     | V <sub>cc</sub><br>Note [6] | 4 M  | to +70°C<br>Hz<br>Max | T <sub>A</sub> = -40°C<br>4 M<br>Min | to +105°<br>Hz<br>Max | C<br>Units | Notos     |

|----|----------|-------------------------------|-----------------------------|------|-----------------------|--------------------------------------|-----------------------|------------|-----------|

| No | Symbol   | Parameter                     |                             | Min  | IVIAX                 | IVIIII                               | IVIAX                 | UIIIIS     | Notes     |

| 1  | TpC      | Input Clock Period            | 3.0V                        | 250  | DC                    | 250                                  | DC                    | ns         | [1,7,8]   |

|    |          |                               | 5.5V                        | 250  | DC                    | 250                                  | DC                    | ns         | [1,7,8]   |

| 2  | TrC,TfC  | Clock Input Rise & Fall Times | 3.0V                        |      | 25                    |                                      | 25                    | ns         | [1,7,8]   |

|    |          |                               | 5.5 <b>V</b>                |      | 25                    |                                      | 25                    | ns         | [1,7,8]   |

| 3  | TwC      | Input Clock Width             | 3.0V                        | 125  |                       | 125                                  |                       | ns         | [1,7,8]   |

|    |          |                               | 5.5V                        | 125  |                       | 125                                  |                       | ns         | [1,7,8]   |

| 4  | TwTinL   | Timer Input Low Width         | 3.0V                        | 100  |                       | 100                                  |                       | ns         | [1,7,8]   |

|    |          |                               | 5.5 <b>V</b>                | 70   |                       | 70                                   |                       | ns         | [1,7,8]   |

| 5  | TwTinH   | Timer Input High Width        | 3.0V                        | ЗТрС |                       | ЗТрС                                 |                       |            | [1,7,8]   |

|    |          |                               | 5.5V                        | 3TpC |                       | 3TpC                                 |                       |            | [1,7,8]   |

| 6  | TpTin    | Timer Input Period            | 3.0V                        | 4TpC |                       | 4TpC                                 |                       |            | [1,7,8]   |

|    |          |                               | 5.5V                        | 4TpC |                       | 4TpC                                 |                       |            | [1,7,8]   |

| 7  | TrTin,   | Timer Input Rise & Fall Timer | 3.0V                        |      | 100                   |                                      | 100                   | ns         | [1,7,8]   |

|    | TfTin    |                               | 5.5V                        |      | 100                   |                                      | 100                   | ns         | [1,7,8]   |

| A8 | TwlL     | Int. Request Low Time         | 3.0V                        | 100  |                       | 100                                  |                       | ns         | [1,2,7,8] |

|    |          |                               | 5.5 <b>V</b>                | 70   |                       | 70                                   |                       | ns         | [1,2,7,8] |

| 8B | TwlL     | Int. Request Low Time         | 3.0V                        | ЗТрС |                       | ЗТрС                                 |                       |            | [1,3,7,8] |

|    |          |                               | 5.5V                        | 3TpC |                       | 3TpC                                 |                       |            | [1,3,7,8] |

| 9  | TwlH     | Int. Request Input High Time  | 3.0V                        | 3TpC |                       | 3TpC                                 |                       |            | [1,2,7,8] |

|    |          |                               | 5.5 <b>V</b>                | 3TpC |                       | 2TpC                                 |                       |            | [1,2,7,8] |

| 10 | Twsm     | STOP-Mode Recovery Width Spec | 3.0V                        | 12   |                       | 12                                   |                       | ns         | [4,8]     |

|    |          | -                             | 5.5V                        | 12   |                       | 12                                   |                       | ns         | [4,8]     |

| 11 | Tost     | Oscillator Startup Time       | 3.0V                        |      | 5TpC                  |                                      | 5TpC                  |            | [4,8,9]   |

|    |          | ·                             | 5.5V                        |      | 5TpC                  |                                      | 5TpC                  |            | [4,8,9]   |

### Notes:

<sup>[1]</sup> Timing Reference uses 0.7  $\rm V_{\rm cc}$  for a logic 1 and 0.2  $\rm V_{\rm cc}$  for a logic 0.

<sup>[2]</sup> Interrupt request via Port 3 (P33-P31).

<sup>[3]</sup> Interrupt request via Port 3 (P30).

<sup>[4]</sup> SMR-D5 = 1, POR STOP mode delay is on.

<sup>[5]</sup> Reg. WDTMR.

<sup>[6]</sup> The  $V_{DD}$  voltage specification of 3.0V guarantees 3.3V  $\pm$ 0.3V, and the  $V_{DD}$  voltage specification of 5.5V guarantees 5.5V  $\pm$ 0.5V.

<sup>[7]</sup> SMR D1 = 0.

<sup>[8]</sup> Maximum frequency for internal system clock is 4 MHz when using XTAL divide-by-one mode.

<sup>[9]</sup> For RC and LC oscillator, and for oscillator driven by clock driver.

## **AC ELECTRICAL CHARACTERISTICS**

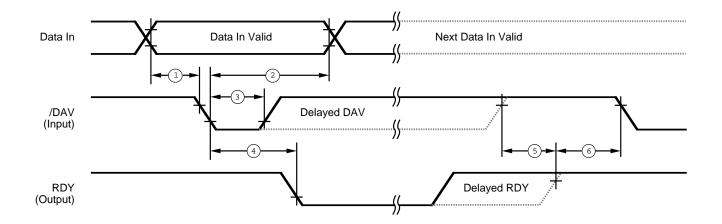

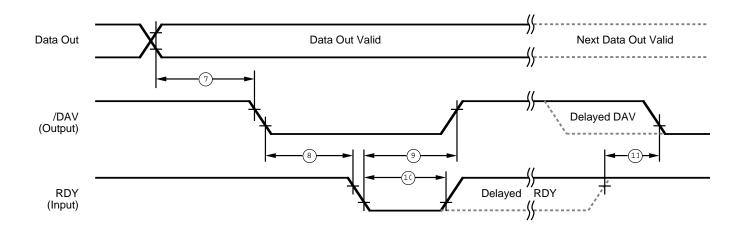

Handshake Timing Diagrams

**Input Handshake Timing**

**Output Handshake Timing**

# **AC ELECTRICAL CHARACTERISTICS** Handshake Timing Table

|    |              |                            |                 | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ |     |     |     | T <sub>A</sub> = |     |      |     |           |

|----|--------------|----------------------------|-----------------|---------------------------------------------|-----|-----|-----|------------------|-----|------|-----|-----------|

|    |              |                            | V <sub>cc</sub> |                                             | ЙHz |     | ИHz |                  | ИHz | 16 N |     | Data      |

| No | Symbol       | Parameter                  | Note[1,2]       | Min                                         | Max | Min | Max | Min              | Max | Min  | Max | Direction |

| 1  | TsDI(DAV)    | Data In Setup Time         | 3.0V            | 0                                           |     | 0   |     | 0                |     | 0    |     | IN        |

|    |              |                            | 5.5V            | 0                                           |     | 0   |     | 0                |     | 0    |     | IN        |

| 2  | ThDI(DAV)    | Data In Hold Time          | 3.0V            | 160                                         |     | 160 |     | 160              |     | 160  |     | IN        |

|    |              |                            | 5.5 <b>V</b>    | 115                                         |     | 115 |     | 115              |     | 115  |     | IN        |

| 3  | TwDAV        | Data Available Width       | 3.0V            | 155                                         |     | 155 |     | 155              |     | 155  |     | IN        |

|    |              |                            | 5.5 <b>V</b>    | 110                                         |     | 110 |     | 110              |     | 110  |     | IN        |

| 4  | TdDAVI(RDY)  | DAV Fall to RDY Fall Delay | 3.0V            |                                             | 160 |     | 160 |                  | 160 |      | 160 | IN        |

|    |              | •                          | 5.5V            |                                             | 115 |     | 115 |                  | 115 |      | 115 | IN        |

| 5  | TdDAVId(RDY) | DAV Rise to RDY Rise Delay | 3.0V            |                                             | 120 |     | 120 |                  | 120 |      | 120 | IN        |

|    |              | •                          | 5.5 <b>V</b>    |                                             | 80  |     | 80  |                  | 80  |      | 80  | IN        |

| 6  | TdRDY0(DAV)  | RDY Rise to DAV Fall Delay | 3.0V            | 0                                           |     | 0   |     | 0                |     | 0    |     | IN        |

|    |              |                            | 5.5 <b>V</b>    | 0                                           |     | 0   |     | 0                |     | 0    |     | IN        |

| 7  | TdD0(DAV)    | Data Out to DAV Fall Delay | 3.0V            | 42                                          |     | 31  |     | 42               |     | 31   |     | OUT       |

|    |              |                            | 5.5 <b>V</b>    | 42                                          |     | 31  |     | 42               |     | 31   |     | OUT       |

| 8  | TdDAV0(RDY)  | DAV Fall to RDY Fall Delay | 3.0V            | 0                                           |     | 0   |     | 0                |     | 0    |     | OUT       |

|    |              |                            | 5.5 <b>V</b>    | 0                                           |     | 0   |     | 0                |     | 0    |     | OUT       |

| 9  | TdRDY0(DAV)  | RDY Fall to DAV Rise Delay | 3.0V            |                                             | 160 |     | 160 |                  | 160 |      | 160 | OUT       |

|    |              | _                          | 5.5 <b>V</b>    |                                             | 115 |     | 115 |                  | 115 |      | 115 | OUT       |

| 10 | TwRDY        | RDY Width                  | 3.0V            | 110                                         |     | 110 |     | 110              |     | 110  |     | OUT       |

|    |              |                            | 5.5V            | 80                                          |     | 80  |     | 80               |     | 80   |     | OUT       |

| 11 | TdRDY0d(DAV) | RDY Rise to DAV Fall Delay | 3.0V            |                                             | 110 |     | 110 |                  | 110 |      | 110 | OUT       |

|    | ,            | ,                          | 5.5V            |                                             | 80  |     | 80  |                  | 80  |      | 80  | OUT       |

## Notes:

<sup>[1]</sup> Timing Reference uses 0.7 V<sub>CC</sub> for a logic 1 and 0.2 V<sub>CC</sub> for a logic 0.

[2] The V<sub>DD</sub> voltage specification of 3.0V guarantees 3.3V±0.3V and the V<sub>DD</sub> voltage specification of 5.5V guarantees 5.0V±0.5V.

## **PRECAUTIONS**

- When in ROM Protect Mode, and executing out of *External Program Memory*, instructions LDC, LDCI, LDE, and LDEI cannot read Internal Program Memory.

- When in ROM Protect Mode, and executing out of *Internal Program Memory*, instructions LDC, LDCI, LDE, and LDEI *can* read Internal Program Memory.

- (2) The device has an oscillator-free reset for the device pins. When the device is reset from a WDT timeout, POR, or V<sub>BO</sub>, the reset will force the device pins to their reset default state even if the oscillator is not running.

- (3) The Port 3 outputs are reset to High State after Reset, except after Stop-Mode Recovery, at which the outputs remain in the last state.

- (4) Extended timing is operable.

- (5) P0/P1/P2/P3 is Low-EMI software programmable.

- (6) P0/P1/P2 is software programmable for open-drain.

- (7) Expanded register PCON is Write Only.

- (8) WDTMR is writeable only within the first 60 internal system clocks after Reset. Afterward, the WDTMR is write protected.

- (9) Device functions down to the  $V_{LV}$  threshold. At temperatures less than 25°C, the  $V_{LV}$  threshold will rise to a maximum  $V_{DD}$  of 3.6V.

- (10) Low EMI is 25 percent of standard pull-down output driver and 25 percent of standard pull-up output driver.

- (11) There is no clock filter on Reset pin.

- (12) Registers FE Hex (SPH) and FF Hex (SPL) are set to 00Hex after any reset.

- (13) When Low EMI OSC is selscted (PCONReg Bit D7=0), the output drive of /DS, /AS, and R//W will also be in low emi mode.

- (14) P01M Reg Bit D4,D3 must be set to 00Hex for Z86233.

© 1996 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 FAX 408 370-8056 Internet: http://www.zilog.com