## **DDR BUFFER FOR SIS CHIPSET**

## W83176R-716

# **Data Sheet Revision History**

|    | Pages | Dates  | Version | Version | Main Contents                                         |

|----|-------|--------|---------|---------|-------------------------------------------------------|

|    |       |        |         | On Web  |                                                       |

| 1  | n.a.  |        |         | n.a.    | All of the versions before 0.50 are for internal use. |

| 2  | n.a.  | 02/Apr | 1.0     | 1.0     | Change version and version on web site to 1.0         |

| 3  |       |        |         |         |                                                       |

| 4  |       |        |         |         |                                                       |

| 5  |       |        |         |         |                                                       |

| 6  |       |        |         |         |                                                       |

| 7  |       |        |         |         |                                                       |

| 8  |       |        |         |         |                                                       |

| 9  |       |        |         |         |                                                       |

| 10 |       |        |         |         |                                                       |

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this data sheet belong to their respective owners.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

### 1.0 GENERAL DESCRIPTION

The W83176R-716 is a 2.5V D.D.R. Clock buffer designed for SiS chipset. W83176R-716 can support 2 D.D.R. DRAM DIMMs. W83176R-716 can be incorporated with W83194BR-640/740 which is the step-less clock with free programmable CPU/AGP/PCI freq. outputs.

The W83176R-716 provides I<sup>2</sup>C serial bus interface to program the registers to enable or disable each clock outputs. The W83176R-716 accepts a pair reference clock as its input and runs on 2.5V supply.

### 2.0 PRODUCT FEATURES

- Zero-delay clock outputs

- Feedback pins for synchronous

- Supports 2 D.D.R. DIMMs

- One pairs of additional outputs for feedback

- Low Skew outputs (< 100ps)</li>

- Supports 266MHz D.D.R. SDRAM

- I<sup>2</sup>C 2-Wire serial interface and I<sup>2</sup>C read back

- 28-pin SSOP package

# 3.0 PIN CONFIGURATION

| CLKC0      | 1 ● 28 | GND          |

|------------|--------|--------------|

| CLKT0      |        | CLKC5        |

| VDD        | 3 26   | CLKT5        |

| CLKT1      | 4 25   | CLKC4        |

| CLKC1      | 5 24   | CLKT4        |

| GND        | 6 23   | VDD          |

| SDCLK      | 7 22   | SDATA        |

| Buffer_INT | 8 21   | NC           |

| NC         | 9 20   | FB_INT       |

| VDDA       | 10 19  | FB_OUTT      |

| GND        | 11 18  |              |

| VDD        | 12 17  | CLKT3        |

| CLKT2      | 13 16  | CLKC3        |

| CLKC2      | 14 15  | GND          |

|            |        | <del>_</del> |

|            |        |              |

|            |        |              |

|            |        |              |

|            |        |              |

# 4.0 PIN DESCRIPTION

IN - Input

OUT - Output

I/O - Bi-directional Pin

- Internal  $120k\Omega$  pull-up

# **4.1 Clock Outputs**

| SYMBOL     | PIN                 | I/O | FUNCTION                                                                                                                                  |  |

|------------|---------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLKC[5:0]  | 1,5,14,16,25,<br>27 | OUT | Complementory Clocks of differential pair outputs                                                                                         |  |

| CLKT[5:0]  | 2,4,13,17,24,<br>26 | OUT | True Clocks of differential pair outputs                                                                                                  |  |

| SDATA      | 22                  | I/O | Serial data of I <sup>2</sup> C 2-wire control interface                                                                                  |  |

| SDCLK      | 7                   | IN  | Serial clock of I <sup>2</sup> C 2-wire control interface                                                                                 |  |

| Buffer_INT | 8                   | IN  | True reference clock input                                                                                                                |  |

| NC         | 9, 18, 20           | IN  | Not connected                                                                                                                             |  |

| FB_OUTT    | 19                  | OUT | True Feedback output, dedicated for external feedback. It switches at the same frequency as the CLK. This output must be wired to FB_INT. |  |

| FB_INC     | 21                  | IN  | Complementory Feedback input, provides feedback signal to the internal PLL for synchronization with CLK_INC to eliminate phase error.     |  |

## **4.2 Power Pins**

| SYMBOL | PIN        | FUNCTION                  |

|--------|------------|---------------------------|

| GND    | 6,11,15,28 | Ground                    |

| VDD    | 3,12,23    | Power Supply 2.5V         |

| AVDD   | 10         | Analog power supply, 2.5V |

# 5.1 Register 0 : Control Register (1 = active, 0 = inactive)

| Bit | @PowerUp | Pin   | Description                    |

|-----|----------|-------|--------------------------------|

| 7   | 1        | 1,2   | CLKC0,CLKT0(Active / Inactive) |

| 6   | 1        | 4,5   | CLKC1,CLKT1(Active / Inactive) |

| 5   | 1        | 13,14 | CLKC2,CLKT2(Active / Inactive) |

| 4   | 1        | 16,17 | CLKC3,CLKT3(Active / Inactive) |

| 3   | 1        | 24,25 | CLKC4,CLKT4(Active / Inactive) |

| 2   | 1        | 26,27 | CLKC5,CLKT5(Active / Inactive) |

| 1   | 1        | -     | Reserved                       |

| 0   | 1        | -     | Reserved                       |

# 5.2 Register 1: Reserved Register (default = 1)

| Bit | @PowerUp | Pin | Description                |

|-----|----------|-----|----------------------------|

| 7   | 1        | -   | Reserved (Skew Control ??) |

| 6   | 1        | -   | Reserved                   |

| 5   | 1        | -   | Reserved                   |

| 4   | 1        | -   | Reserved                   |

| 3   | 1        | -   | Reserved                   |

| 2   | 1        | -   | Reserved                   |

| 1   | 1        | -   | Reserved                   |

| 0   | 1        | -   | Reserved                   |

# 5.3 Register 2: Reserved Register (default = 1)

| Bit | @PowerUp | Pin | Description |

|-----|----------|-----|-------------|

| 7   | 1        | -   | Reserved    |

| 6   | 1        | -   | Reserved    |

| 5   | 1        | -   | Reserved    |

| 4   | 1        | -   | Reserved    |

| 3   | 1        | -   | Reserved    |

| 2   | 1        | -   | Reserved    |

| 1   | 1        | -   | Reserved    |

| 0   | 1        | -   | Reserved    |

Publication Release Date: April. 2001 Revision 1.0

## 5.4 Register 3: Reserved Register (default = 1)

| Bit | @PowerUp | Pin | Description |

|-----|----------|-----|-------------|

| 7   | 1        | -   | Reserved    |

| 6   | 1        | -   | Reserved    |

| 5   | 1        | -   | Reserved    |

| 4   | 1        | -   | Reserved    |

| 3   | 1        | -   | Reserved    |

| 2   | 1        | -   | Reserved    |

| 1   | 1        | -   | Reserved    |

| 0   | 1        | -   | Reserved    |

## 6.0 ORDERING INFORMATION

| Part Number | Package Type | Production Flow          |

|-------------|--------------|--------------------------|

| W83176R-716 | 28 PIN SSOP  | Commercial, 0°C to +70°C |

### 7.0 HOW TO READ THE TOP MARKING

1st line: Winbond logo and the type number: W83176R-716

2nd line: Tracking code 2 8051234

2: wafers manufactured in Winbond FAB 2

8051234: wafer production series lot number

3rd line: Tracking code 814 G B B

814: packages made in '98, week 14

**G**: assembly house ID; O means OSE, G means GR

A: Internal use code

**B**: IC revision

All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

Publication Release Date: April. 2001 Revision 1.0

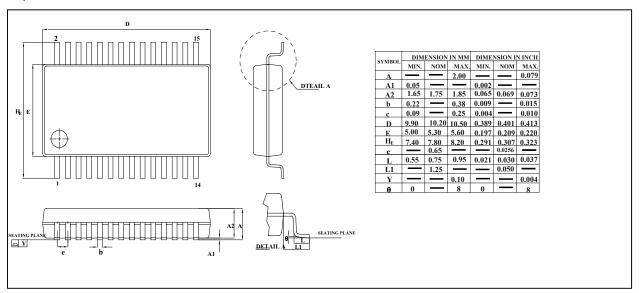

## 8.0 PACKAGE DRAWING AND DIMENSIONS

28pin 209mil

### **Headquarters**

No. 4, Creation Rd. III Science-Based Industrial Park Hsinchu, Taiwan TEL: 886-35-770066 FAX: 886-35-789467 www: http://www.winbond.com.tw/

### Taipei Office

9F, No. 480, Rueiguang Road, Neihu District, Taipei, 114, Taiwan TEL: 886-2-81777168 FAX: 886-2-87153579

#### Winbond Electronics (H.K.) Ltd.

Rm. 803, World Trade Square, Tower II 123 Hoi Bun Rd., Kwun Tong Kowloon, Hong Kong TEL: 852-27516023-7 FAX: 852-27552064

### Winbond Electronics

(North America) Corp.

2727 North First Street San Jose, California 95134 TEL: 1-408-9436666 FAX: 1-408-9436668

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sale.

Publication Release Date: April. 2001 Revision 1.0