# TMC428 – DATASHEET

Intelligent Triple Stepper Motor Controller with **Serial Peripheral Interfaces**

TRINAMIC<sup>®</sup> Microchips GmbH Deelboegenkamp 4c D - 22297 Hamburg GERMANY

P +49 - (0) 40 - 51 48 06 - 0 F +49 - (0) 40 - 51 48 06 - 60 www.trinamic.com info@trinamic.com

#### 1 **Features**

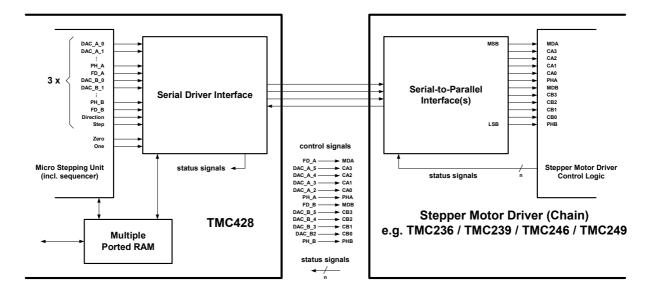

The TMC428 is a miniaturized high performance stepper motor controller. It controls up to three 2phase stepper motors. All motors can operate independently. The TMC428 allows up to 6 bit microstep resolution- corresponding to 64 microsteps per full step -individually selectable for each motor. Once initialized, it performs all real time critical tasks autonomously based on target positions and velocities, which may be altered on-the-fly. So, an inexpensive microcontroller together with the TMC428 forms a complete motion control system. The microcontroller is free to do application specific interfacing and high level control functions. Both, the communication with the microcontroller and with one to three daisy chained stepper motor drivers take place via two separate 4 wire serial peripheral interfaces. The TMC428 directly connects to SPI<sup>TM\*</sup> smart power stepper motor drivers.

- Controls up to three 2-phase stepper motors •

- Serial 4-wire interface for  $\mu C$  with easy-to-use protocol

- .

- Configurable interface for SPI<sup>TM</sup> motor drivers Different types of SPI<sup>TM</sup> stepper motor driver chips may be mixed within a single daisy chain •

- Communication on demand minimizes traffic to the SPI<sup>TM</sup> stepper motor driver chain Programmable SPI<sup>TM</sup> data rates up to 1 Mbit/s •

- Wide range for clock frequency can use CPU clock up to 16 MHz

- Internal 24 bit wide position counters

- Full step frequencies up to 20 kHz

- Read-out facility for actual motion parameters (position, velocity, acceleration) and driver status

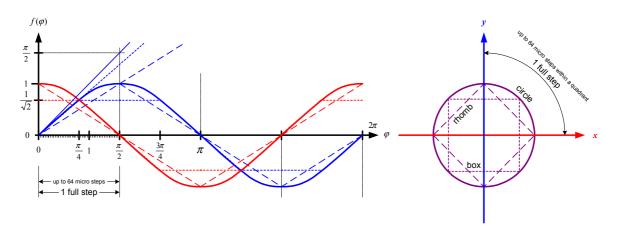

- Individual microstep resolution of {64, 32, 16, 8, 4, 2, 1} microsteps via built-in sequencer

- Programmable 6 bit microstep table with up to 64 entries for a quarter sine-wave period

- Built-in ramp generators for autonomous positioning and speed control

- On-the-fly change of target motion parameters (like position, velocity, acceleration)

- Automatic acceleration dependent current control (power boost)

- Low power operation: Only 1.25 mA @ 4 MHz (typ.)

- Power down mode with transparent wake-up for normal operation

- 3.3V or 5V operation with CMOS / TTL compatible IOs (all inputs Schmitt-Trigger)

- Available in ultra small 16 pin SSOP package, 24 pin SOP package, and 20 pin DIL package

SPI is Trademark of Motorola. Inc.

#### Life support policy

TRINAMIC Microchips GmbH does not authorize or warrant any of its products for use in life support systems, without the specific written consent of TRINAMIC Microchips GmbH.

Life support systems are equipment intended to support or sustain life, and whose failure to perform, when properly used in accordance with instructions provided, can be reasonably expected to result in personal injury or death.

#### © 2000–2003, TRINAMIC Microchips GmbH

Information given in this data sheet is believed to be accurate and reliable. However no responsibility is assumed for the consequences of its use nor for any infringement of patents or other rights of third parties which may result form its use.

Specifications subject to change without notice.

### 2 General Description

The TMC428 is a miniaturized high performance stepper motor controller with a unique price / performance ratio for both, high volume automotive and for demanding industrial motion control applications. Once initialized, the TMC428 controls up to three 2-phase stepper motors. Its low price makes it attractive also for applications, where only one or two stepper motors have to be controlled simultaneously.

The TMC428 performs all real time critical tasks autonomously. Thus a low cost microcontroller is sufficient to perform the tasks of initialization, application specific interfacing, and to specify target positions and velocities. The TMC428 allows on-the-fly change of all motion target parameters also during motion. Any other parameter may be changed at any time– also during motion –which does not make sense in any case, but this uniform access to any TMC428 register simplifies application programming. Read-back option for all internal registers simplifies programming. With its internal position counters , the TMC428 can perform up to 2<sup>23</sup> steps respectively microsteps fully independent from the microcontroller. The step resolution– individually programmable for each stepper motor – ranges from full step (1 "microstep" is one fullstep), half step (2 "microsteps" per fullstep), up to 6 bit microstepping (64 microsteps per full step) for precise positioning and noiseless stepper motor rotation (Table 8-8, page 25). Optionally, the microstep table– common for all motors –can be adapted to motor characteristics to further reduce torque ripple.

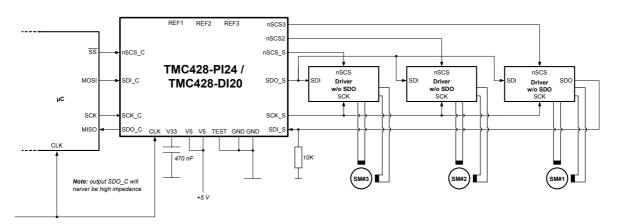

The TMC428 has got serial interfaces for communication with the microcontroller and for the stepper motor drivers. The serial interface for the microcontroller uses a fixed length of 32 bits with a simple protocol, directly connecting to SPI<sup>TM</sup> interfaces. The serial interface to the stepper motor drivers is flexibly configurable for different types– even from different vendors –with up to 64 bit length for the SPI daisy chain. TRINAMIC Microchips smart power stepper motor drivers TMC236, TMC239 and TMC246, TMC249 perfectly fit to the TMC428. Without additional hardware, drivers with same serial interface polarities of chip select and clock signals may be mixed in a single chain. To mix drivers with different serial interface polarities, additional inverters (e.g. 74HC04, 74HC14) are required. For those driver chips without serial data output, two additional variants of the TMC428 with two additional chip select outputs are available. The TMC428 sends data to the driver chain on demand only, which minimizes the interface traffic and reduces the power consumption.

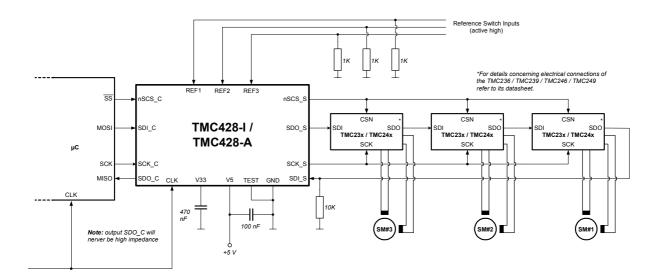

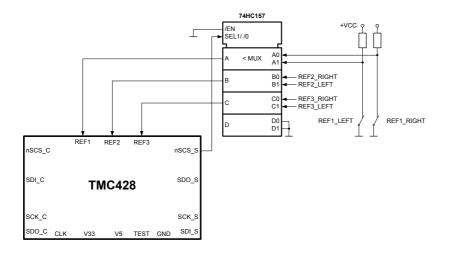

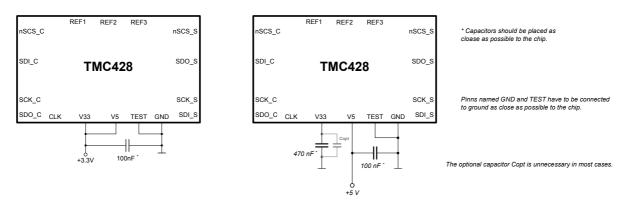

Figure 2-1: TMC428 application environment with TMC428 in SSOP16 package

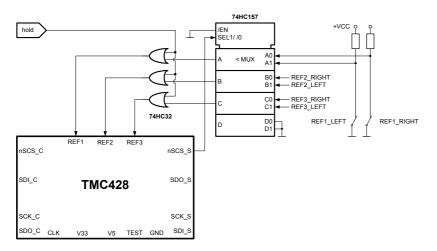

Figure 2-2: Usage of drivers without serial data output (SDO) with TMC428 in larger packages

## 2.1 Step Frequencies

The maximum SPI<sup>TM</sup> data rate is the clock frequency divided by 16. The maximum step frequency depends on the total length of the datagrams sent to the SPI<sup>TM</sup> stepper motor driver chain. At a clock frequency of 16 MHz, with a daisy chain of three SPI<sup>TM</sup> stepper motor drivers of 16 bit datagram length each, the maximum *full step* frequency is 16 MHz / 16 / (3 \* 16). This is approximately 20 kHz and that is much higher than needed for typical stepper motors. But, the microstep rate may be higher, even if the stepper motor driver does not see all microsteps due to SPI<sup>TM</sup> data rate limit, as long as the number of skipped microsteps is less than a full step. In this respect, one should remember, that at high step rates– respectively pulse rates –the differences between microstepping and full step excitation vanishes.

#### 2.2 Modes of Motion

The TMC428 has four different modes of motion, programmable individually for each stepper motor, named RAMPMODE, SOFTMODE, VELOCITYMODE, and HOLDMODE. For positioning applications the RAMPMODE is most suitable, whereas for constant velocity applications the VELOCITYMODE is. In RAMPMODE, the user just sets the position and the TMC428 calculates a trapezoidal velocity profile and drives autonomously to the target position. During motion, the position may be altered arbitrarily. The SOFTMODE is similar to the RAMPMODE, but the decrease of the velocity during deceleration is done with a soft, exponentially shaped velocity profile. In VELOCITYMODE, a target velocity is set by the user and the TMC428 takes into account user defined limits of velocity and acceleration. In HOLDMODE, the user sets target velocities, but the TMC428 ignores any limits of velocity and acceleration, to realize arbitrary velocity profiles, controlled completely by the user. The TMC428 has capabilities to generate interrupts depending on different stepper motor conditions chosen by an interrupt mask. However, status bits sent back automatically to the microcontroller each time it sends data to the TMC428 are sufficient for polling techniques.

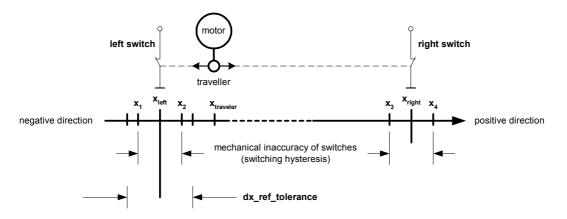

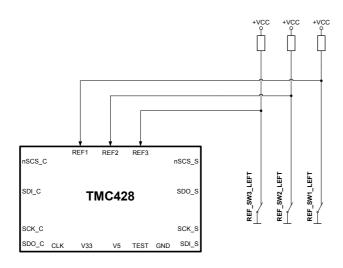

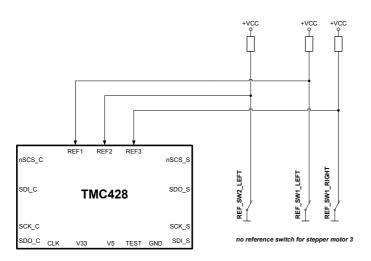

The TMC428 provides different modes for reference switch handling. In the default reference switch mode, the three reference switch inputs (**REF1**, **REF2**, **REF3**) are defined as left side reference switches, one for each stepper motor. In another mode, the 1<sup>st</sup> reference input (**REF1**) is defined as left reference switch input of motor number one, the 2<sup>nd</sup> reference input (**REF2**) is defined as left reference switch input of motor number one. In that mode, there is no reference switch input available for stepper motor three. With an external multiplexer 74HC157 any stepper motor may have a left and a right reference switch.

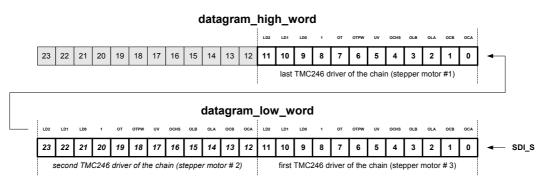

Many serial stepper motor drivers provide different status bits (driver active, inactive, ...) and error bits (short to ground, wire open, ...). To have access to those error bits, datagrams with a total length up to 48 bits sent back from the stepper motor driver chain to the TMC428 are buffered within two 24 bit wide registers. The microcontroller has direct access to these registers. Although, the TMC428 provides datagrams with up to 64 bits, only the last 48 bits sent back from the driver chain are buffered for read out by the microcontroller. This is because buffering of 3 times 16 bits is sufficient for a chain

of three stepper motor drivers (see Figure 2-1, page 3) and most other drivers sending back up to 16 bits. For a chain of three TMC236 / TMC239 / TMC246 / TMC249 all status bits are accessible. From the software point of view, the TMC428 provides a set of registers, accessed by a microcontroller (µC) via a serial interface in an uniform way. Each datagram contains address bits, a read-write selection bit, and data bits, to access the registers and the on-chip memory. Each time, the µC sends a datagram to the TMC428, it simultaneously receives a datagram from the TMC428. This simplifies the communication with the TMC428 and makes the programming easy. Most microcontrollers have an SPI<sup>TM</sup> hardware interface, which directly connects to the serial four wire microcontroller interface of the TMC428. For microcontrollers without SPI<sup>TM</sup> hardware, a software doing the serial communication is completely sufficient and can easily be implemented.

#### 2.3 Notation of Number Systems & Notation of Two to the Power of n

Decimal numbers are used as usual without additional identification. Binary numbers are identified by a prefixed % character. Hexadecimal numbers are identified by a prefixed \$ character. So, for example the decimal number 42 in the decimal system is written as %101010 in the binary number system, and it is written as \$2A in the hexadecimal number system. With this, TMC428 datagrams are written as 32 bit numbers (e.g. \$1234ABCD = %00010010001101001010101111001101). In addition to the basic arithmetic operators (+, -, \*, /) the operator *two to the power of n* is required at different sections of this data sheet. For better readability instead of 2<sup>n</sup> the notation 2<sup>n</sup> is used.

#### 2.4 Signal Polarities

Per default, signals– external and internal –are high active, but the polarity of some signals is programmable to be inverted. A pre-fixed lower case 'n' indicates low active signals (e.g. nSCS\_C, nSCS\_S). For example the polarity of nSCS\_S can be inverted by programming, but also the polarity of datagram bits can be inverted by programming (see section 9, page 26).

#### 2.5 Units of Motion Parameters

Motion parameters position, velocity, and acceleration are given as integer values within TMC428 specific units. Section 8.14 page 25 explains, how to calculate steps, steps per second, steps per second square from given TMC428 integer values. With a given stepper motor resolution one can calculate physical units for angle, angular velocity, angular acceleration.

#### 2.6 Representation of Signed Values by Two's Complement

Those motion parameters that have to cover negative and positive motion direction as well, are processed as signed numbers represented by two's complement as usual. Signed motion parameters are x\_target, x\_actual, v\_target, v\_actual, a\_actual. Limit motion parameters as v\_min, v\_max, a\_max, a\_threshold, are represented as unsigned binary numbers.

#### 2.7 Tables of Contents

A table of contents, a table of figures, and a table of tables are located at the end of the data sheet.

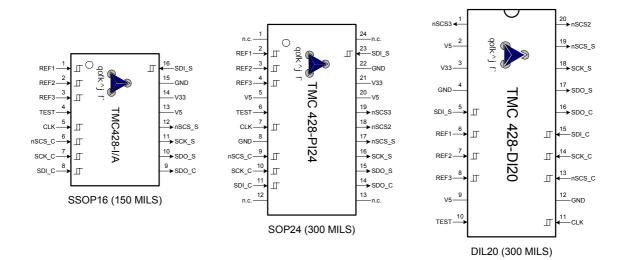

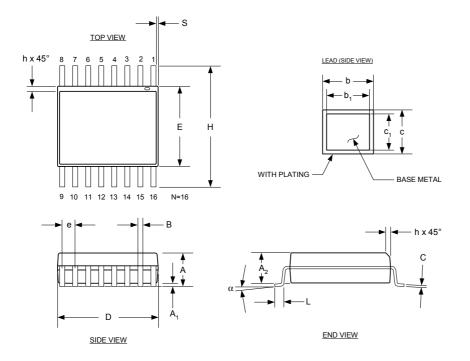

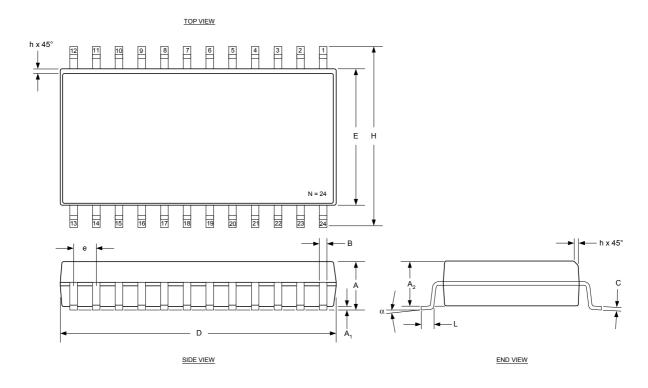

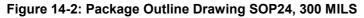

# **3** Package Variants

The TMC428 is available in three different package variants, qualified for the industrial temperature range. An additional variant is available for the automotive temperature range. The package outlines and dimensions are included within this data sheet (page 43-45.)

| part number | Package                                                 | JEDEC Drawing     |

|-------------|---------------------------------------------------------|-------------------|

| TMC428-I    | SSOP16 – 150 mils, 16 pins, plastic package, industrial | MO-137 (150 mils) |

| TMC428-A    | SSOP16 – 150 mils, 16 pins, plastic package, automotive | MO-137 (150 mils) |

| TMC428-PI24 | SOP24 – 300 mils, 24 pins, plastic package, industrial  | MS-013 (300 mils) |

| TMC428-DI20 | DIL20 – 300 mils, 20 pins, plastic package, industrial  | MS-001 (300 mils) |

Table 3-1: TMC428 package variants

### 4 Pinning

There are three package variants of the TMC428 available. The smaller SSOP16 package is sufficient for TRINAMIC stepper motor drivers (TMC236 / TMC239 / TMC246 / TMC249) with up to three drivers in a chain and for most SPI<sup>TM</sup> stepper motor drivers from other vendors. Some SPI<sup>TM</sup> stepper motor drivers from other vendors have no serial data output and can not simply be arranged in a daisy chain to drive more than one motor. The two package variants SOP24 and DIL20 have two additional driver selection outputs (**nSCS2**, **nSCS3**) for those stepper motor drivers without serial data output. All inputs are Schmitt-Trigger. Possibly unused inputs (**REF1**, **REF2**, **REF3**, **SDI\_S**) need to be connected to ground.

Figure 4-1: TMC428 pin out

| Pin          | SSOP16 | SOP24         | DIL20 | In/Out | Description                                                                                                                                                                                  |

|--------------|--------|---------------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset        | -      | -             | -     | -      | internal power-on reset                                                                                                                                                                      |

| CLK          | 5      | 7             | 11    | I      | clock input                                                                                                                                                                                  |

| nSCS_C       | 6      | 9             | 13    | I      | low active SPI chip select input driven from µC                                                                                                                                              |

| SCK_C        | 7      | 10            | 14    | I      | serial data clock input driven from µC                                                                                                                                                       |

| SDI_C        | 8      | 11            | 15    | I      | serial data input driven from µC                                                                                                                                                             |

| SDO_C / nINT | 9      | 14            | 16    | 0      | serial data output to $\mu$ C input / multiplexed nINTERRUPT<br>output if communication with $\mu$ C is idle (resp. nSCS_C = 1)<br><b>Important Note:</b> SDO_C will never be high impedance |

| nSCS_S       | 12     | 17            | 19    | 0      | SPI chip select signal to stepper motor driving chain                                                                                                                                        |

| nSCS2        | -      | 18            | 20    | 0      | SPI chip select signal (SOP24 & DIL20 package only)                                                                                                                                          |

| nSCS3        | -      | 19            | 1     | 0      | SPI chip select signal (SOP24 & DIL20 package only)                                                                                                                                          |

| SCK_S        | 11     | 16            | 18    | 0      | serial data clock output to SPI stepper motor driver chain                                                                                                                                   |

| SDO_S        | 10     | 15            | 17    | 0      | serial data output to SPI stepper motor driver chain                                                                                                                                         |

| SDI_S        | 16     | 23            | 5     | I      | serial data input from SPI stepper motor driver chain<br><b>Note:</b> pull-up/-down resistor at SDI_S avoids high<br>impedance                                                               |

| REF1         | 1      | 2             | 6     | I      | reference switch input 1                                                                                                                                                                     |

| REF2         | 2      | 3             | 7     | I      | reference switch input 2                                                                                                                                                                     |

| REF3         | 3      | 4             | 8     | I      | reference switch input 3                                                                                                                                                                     |

| V5           | 13     | 5, 20         | 2, 9  |        | +5V supply / +3.3V supply                                                                                                                                                                    |

| V33          | 14     | 21            | 3     |        | 470 nF ceramic capacitor pin / +3.3V supply                                                                                                                                                  |

| GND          | 15     | 8, 22         | 4, 12 |        | ground                                                                                                                                                                                       |

| TEST         | 4      | 6             | 10    | Ι      | must be connected to GND as close as possible to the chip                                                                                                                                    |

| n.c.         | -      | 1, 12, 13, 24 | -     | -      | not connected                                                                                                                                                                                |

Table 4-1: TMC428 pin out

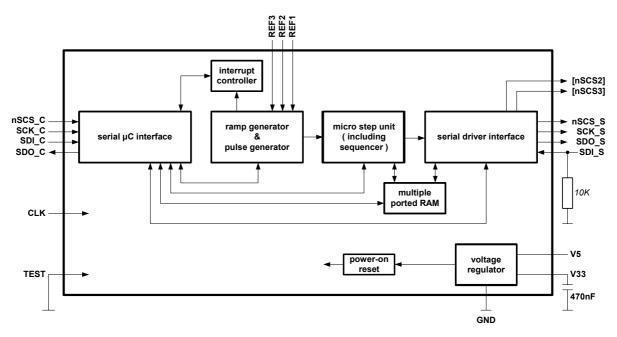

# 5 Functional Description and Block Diagram

From the software point of view, the TMC428 provides a set of registers of different units and on-chip RAM (see Figure 5-1), accessed via the serial  $\mu$ C interface in an uniform way. The serial interface uses just a simple protocol with fixed length datagrams for read and write access. The serial interface to the stepper motor driver chain has to be configured by an initialization sequence which writes the configuration into the on-chip RAM. Once configured the serial driver interface works autonomously. The internal multiple port RAM controller of the TMC428 takes care of access scheduling. So, the user may read and write registers and on-chip RAM at any time. The registers hold global configuration parameters and the motion parameters. The on-chip RAM stores the configuration of the serial driver interface and the microstep table.

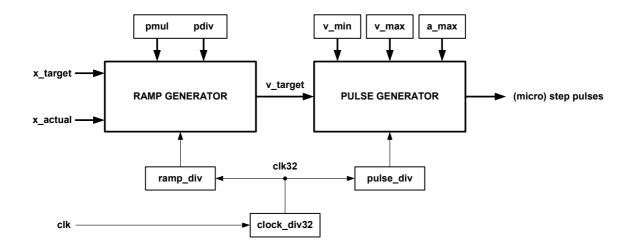

The ramp generator monitors the motion parameters stored in its registers and calculates velocity profiles controlling the pulse generator. The pulse generator then generates step pulses taking into account user defined motion parameter limits. The serial driver interface sends datagrams to the stepper motor driver chain whenever a step pulse comes. The microstep unit (including sequencer) processes step pulses from the pulse generator– representing microsteps, half steps, or full steps depending on the selected step resolution –and makes the results available to the serial driver interface. The ramp generator also interfaces the reference switch inputs. Unused reference switches have to be connected to ground. A pull-down resistor is necessary at the SDI\_S input of the TMC428 for those serial peripheral interface stepper motor drivers that set their serial data output to high impedance 'Z' while inactive.

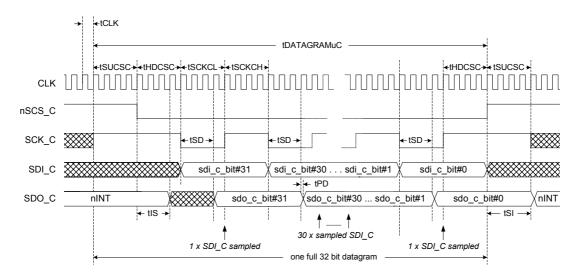

The interrupt controller continuously watches reference switches and ramp generator conditions and generates an interrupt if required. To save pins, the interrupt signal is multiplexed to the SDO\_C signal. This output becomes the low active interrupt signal called nINT while nSCS\_C is high (see Figure 6-1, page 8). So, if the microcontroller disables the interrupt during access to the TMC428 and enables the interrupt otherwise, the multiplexed interrupt output of the TMC428 behaves like a dedicated interrupt output. For polling, the TMC428 sends the status of the interrupt signal to the microcontroller with each datagram.

To drive a stepper motor to a new target position, one just has to write the target position into the associated register by sending a datagram to the TMC428. To run a stepper motor with a target velocity, one just has to write the velocity into the register assigned to the stepper motor.

Figure 5-1: TMC428 functional block diagram

## 6 Serial Peripheral Interfaces

The four pins named SCS\_C, SCK\_C, SDI\_C, SDO\_C form the serial microcontroller interface of the TMC428. The communication between the microcontroller and the TMC428 takes place via 32 bit datagrams of fixed length. Concerning communication, the  $\mu$ C is the master and the TMC428 is the slave, with the TMC428 in turn being the master for the stepper motor driver daisy chain. Similar to the microcontroller interface, the TMC428 uses a four wire serial interface for communication with the stepper motor driver daisy chain. The four pins named SCS\_S, SCK\_S, SDO\_S, SDI\_S form the serial stepper motor driver interface. Stepper motor drivers with parallel inputs can be used in connection with the TMC428 with some additional glue logic.

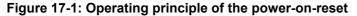

#### 6.1 Serial Peripheral Interface for µC

The serial microcontroller interface of the TMC428 behaves as a simple 32 bit shift register. It shifts serial data SDI\_C in with the rising edge of the clock signal SCK\_C and copies the content of the 32 bit shift register with the rising edge of the selection signal nSCS\_C into a buffer register. The serial interface of the TMC428 immediately sends back data read from registers or read from internal RAM via the signal SDO\_C. The signal SDO\_C can be sampled with the rising edge of SCK\_C, but SDO\_C becomes valid at least four CLK clock cycles after SCK\_C becomes low as outlined in the timing diagram Figure 6-1. For detailed timing parameters see Table 6-1, page 10. The SPI signals from the  $\mu$ C interface may be asynchronous to the clock signal CLK of the TMC428.

Because of on-the-fly processing of the input data stream, the serial microcontroller interface of the TMC428 requires the serial data clock signal SCK\_C to have a minimum low / high time of three clock cycles. The data signal SDI\_C driven by the microcontroller has to be valid at the rising edge of the serial data clock input SCK\_C. The maximum duration of the serial data clock period is unlimited.

While the  $\mu$ C interface of the TMC428 is idle, the SDO\_C signal is the (active low) interrupt status nINT of the integrated interrupt controller of the TMC428. The timing of the multiplexed interrupt status signal nINT is characterized by the parameters tIS an tSI (see Table 6-1, page 10).

<u>Hint:</u> If the microcontroller and the TMC428 work on different clock domains that run asynchronous to each other, the timing of the SPI interface of the microcontroller should be made conservative in the way that the length of one SPI clock cycle equals 8 or more clock cycles of the TMC428 clock CLK. This make the system robust concerning frequency drift, jitter, etc.

A complete serial datagram frame has a fixed length of 32 bit. While the data transmission from the microcontroller to the TMC428 is idle, the low active serial chip select input nSCS\_C and also the serial data clock signal SCK\_C are set to high. While the signal nSCS\_C is high, the TMC428 assigns the status of the internal low active interrupt signal named nINT to the serial data output SDO\_C (see Figure 6-1). The serial data input SDI\_C of the TMC428 has to be driven by the microcontroller.

**Important Hint:** In contrast to most other SPI<sup>TM</sup> compatible devices, the SDO\_C signal of the TMC428 is always driven. So, it will never be high impedance 'Z'.

The signal nSCS\_C has to be high for at least three clock cycles before starting a datagram transmission. To initiate a transmission, the signal nSCS\_C has to be set to low. Three clock cycles later the serial data clock may go low. The most significant bit (MSB) of a 32 bit wide datagram comes first and the least significant bit (LSB) is transmitted as the last one. A data transmission is finished by setting nSCS\_C high three or more CLK cycles after the last rising SCK\_C slope. So, nSCS\_C and SCK\_C change in opposite order from low to high at the end of a data transmission as these signals change from high to low at the beginning. The timing of the serial microcontroller interface is outlined in Figure 6-1.

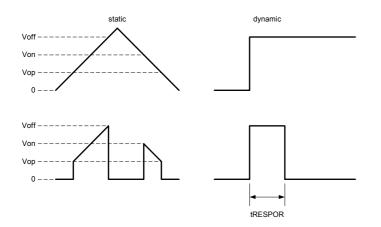

#### 6.2 Automatic Power-On Reset

The TMC428 performs an automatic power-on reset. For details see section Power-On-Reset, page 48. The TMC428 cannot be accessed before the power-on-reset is completed and the clock is stable. All register bits are initialized with '0' during power on reset, except the SPI clock pre-divider **clk2\_div** (see section 9.7, page 28) that is initialized with 15.

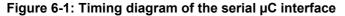

#### 6.3 Serial Peripheral Interface to Stepper Motor Driver Chain

The timing of the serial stepper motor interface is similar to that of the microcontroller interface. It directly connects to SPI<sup>TM</sup> smart power stepper motor drivers. The SPI<sup>TM</sup> datagram is configurable individually for each stepper motor driver chip of the daisy chain. It is simply configurable by sending a fixed sequence of datagrams to the TMC428 to initialize it after power-up. Once initialized, the TMC428 autonomously generates the datagrams for the stepper motor driver daisy chain without any additional interventions of the microcontroller.

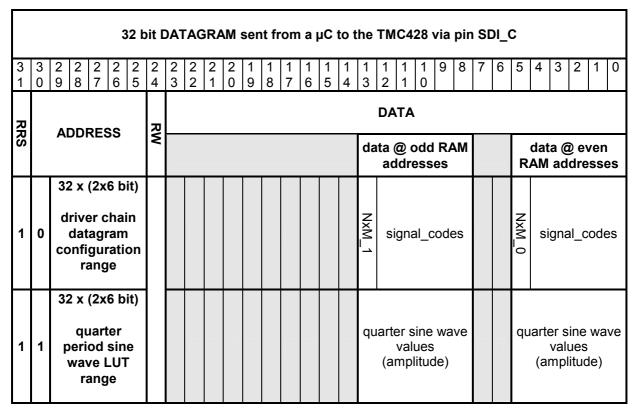

The SPI<sup>™</sup> datagram for each stepper motor driver is composed of so called *primary signal bits* provided by the microstep unit of the TMC428 individually for each stepper motor. Each primary signal bit is represented by a five bit code word called *primary signal code*. The order of primary signal bits forming the SPI<sup>™</sup> datagrams for the stepper motor driver daisy chain is defined by the order of primary signal code words in the configuration RAM area.

To switch to the next motor, an additional bit called *next motor bit* (NxM-Bit) is prefixed to the five bit wide primary signal code words. So, the total data word width is six bit. Each NxM-Bit effects an increment of an internal stepper motor address until the processing for all stepper motors within the daisy chain is completed. A parameter called **LSMD** (last stepper motor driver) defines the total number of stepper motors within the daisy chain. So, the codes written into the serial interface configuration RAM area represent the mapping of control signals provided by the microstep units to control bits of the drivers. It might be noted here, that configuring the serial driver interface is much easier as it might seem here. It is explained in detail, illustrated by examples below (see section 11 Stepper Motor Driver Datagram Configuration, page 34).

The timing of the serial driver interface is programmable in a wide range. The clock divider provides 16 up to 512 clock cycles (tCLK) for a serial driver interface data clock period. The default duration of a clock period (tSCKCL+tSCKCH) of the signal nSCS\_S is 16+16=32 clock periods of the clock signal CLK. The minimal duration of a serial interface clock period (tSCKCL+tSCKCH) is 8+8=16 clock cycles of signal CLK as outlined in Figure 6-2. Also, the polarities of the signals nSCS\_S and SCK\_S are programmable to use driver chips from other vendors with inverted polarities without additional glue logic.

The input SDI\_S of the serial driver interface must always be driven to a defined level. So, to avoid high impedance ('Z') at that input pin while the stepper motor driver chain is idle, a pull-up resistor or a pull-down resistor of 10 K $\Omega$  is required at that input.

| Symbol      | Parameter                                   | Min              | Тур | Max | Unit        |

|-------------|---------------------------------------------|------------------|-----|-----|-------------|

| tSUCSC      | Setup Clocks for nSCS_C                     | 3                |     | ∞   | CLK periods |

| tHDCSC      | Hold Clocks for nSCS_C                      | 3                |     | ~   | CLK periods |

| tSCKCL      | Serial Clock Low                            | 3                |     | ∞   | CLK periods |

| tSCKCH      | Serial Clock High                           | 3                |     | 8   | CLK periods |

| tSD         | SDO_C valid after SCK_C low                 | 2.5              |     | 3.5 | CLK periods |

| tIS         | nINTERRUPT status valid after nSCS_C low    | 2.5              |     |     | CLK periods |

| tSI         | SDO_C valid after nSCS_C high               |                  |     | 4.5 | CLK periods |

| tDAMAGRAMuC | Datagram Length                             | 3+3 + 32*6 = 198 |     | 8   | CLK periods |

| tDAMAGRAMuC | Datagram Length                             | 12.375           |     | ∞   | μs          |

| fCLK        | Clock Frequency                             | 0                |     | 16  | MHz         |

| tCLK        | Clock Period tCLK = 1 / fCLK                | 62.5             |     | 8   | ns          |

| tPD         | CLK-rising-edge-to-Output Propagation Delay |                  | 5   |     | ns          |

Table 6-1: Timing characteristics of the serial microcontroller interface

| Symbol       | Parameter                          | Min             | Тур | Мах                   | Unit        |

|--------------|------------------------------------|-----------------|-----|-----------------------|-------------|

| tSUSCSdrv    |                                    | 8               | 16  | 256                   | CLK periods |

| tHDSCSdrv    |                                    | 8               | 16  | 256                   | CLK periods |

| tCKSL        |                                    | 8               | 16  | 256                   | CLK periods |

| tCKSH        |                                    | 8               | 16  | 256                   | CLK periods |

| tDAMAGRAMdrv | Datagram Length                    | 8+8+1*16+8+8=48 |     | 512+64*512+512= 33792 | CLK periods |

| tDAMAGRAMdrv | Datagram Length @ fCLK = 16<br>MHz | 3               |     | 2112                  | μs          |

| tPD          | CLK-rising-edge to Outputs Delay   |                 | 5   |                       | ns          |

Table 6-2: Timing characteristics of the serial stepper motor driver interface

## 6.4 Datagram Structure

The microcontroller ( $\mu$ C) communicates with the TMC428 via the four wire (nSCS\_C, SCK\_C, SDI\_C, SDO\_C) serial interface. Each datagram sent to the TMC428 via the pin SDI\_C and each datagram received from the TMC428 via the pin SDO\_C is 32 bits long. The first bit sent is the MSB (most significant bit named sdi\_c\_bit#31 at Figure 6-1). The last bit sent is the LSB (least significant bit named sdi\_c\_bit#0 in Figure 6-1). During reception of a datagram, the TMC428 immediately sends back a datagram of the same length to the microcontroller. This datagram is the result of the request from the microcontroller.

With each 32 bit wide datagram the microcontroller sends to the TMC428, it simultaneously receives a 32 bit wide datagram. A read request is distinguished from a write request by one datagram bit named **RW**. The TMC428 immediately sends back requested read data in the lower 24 datagram bits. Status bits are sent back in the higher 8 datagram bits. Datagrams sent from the microcontroller to the TMC428 have the form:

| MSB    |        |        |        |        |        | 32     | bit    | DA | TA     | GR     | AM     | se     | nt     | fror   | nμ     | C t    | o tł   | ne T   | M      | 242    | 28 v   | 'ia p | oin | SD | I_C |   |   |   |   |   | LSB |

|--------|--------|--------|--------|--------|--------|--------|--------|----|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-----|----|-----|---|---|---|---|---|-----|

| 3<br>1 | 3<br>0 | 2<br>9 | 2<br>8 | 2<br>7 | 2<br>6 | 2<br>5 | 2<br>4 | 2  | 2<br>2 | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 9     | 8   | 7  | 6   | 5 | 4 | 3 | 2 | 1 | 0   |

| RRS    |        | A      | DDI    | RES    | SS     | J      | RW     |    |        |        | J      | J      |        |        | Ū      | Ū      |        |        | DA     | TA     |        |       |     |    |     |   |   |   |   |   |     |

Table 6-3 : 32 bit DATAGRAM structure sent from µC (MSB sent first)

The 32 bit wide datagrams sent to the TMC428 are assorted in four groups of bits: **RRS** (register RAM select) selecting either registers or on-chip RAM; **ADDRESS** bits addressing memory within the register set or within the RAM area; **RW** (read / not write (**RW=1** : **read** / **RW=0** : **write**)) bit distinguishing between read access and write access; **DATA** bits for write access– for read access these bits are *don't care* and should be set to '0'. Different internal registers of the TMC428 have different lengths. So, for some registers only a subset of these 24 data bits is used. Unused data bits should be set to '0' for clearness. Some addresses select more than a single register mapped together into the 24 data bit space.

The 32 bit wide datagrams received by the  $\mu$ C from the TMC428 contain two groups of bits: **STATUS BITS** and **DATA BITS**. The status bits, sent back with each datagram, carry the most important information about internal states of the TMC428 and the settings of the reference switches. These datagrams have the form:

| MSB    |        |        |        |        | 32        | bit    | DA        | TA     | GR     | AM     | se     | nt k   | oac    | k fi   | om     | th     | e T    | МС     | 428        | 3 to   | μC     | ; vi | a pi | in S | SDC | )_C | ; |   |   |   | LSB |

|--------|--------|--------|--------|--------|-----------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|--------|--------|------|------|------|-----|-----|---|---|---|---|-----|

| 3<br>1 | 3<br>0 | 2<br>9 | 2<br>8 | 2<br>7 | 2<br>6    | 2<br>5 | 2<br>4    | 2<br>3 | 2<br>2 | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2     | 1<br>1 | 1<br>0 | 9    | 8    | 7    | 6   | 5   | 4 | 3 | 2 | 1 | 0   |

|        | S      | STA    | TU     | SE     | BITS      | S      |           |        |        |        |        |        |        |        |        |        |        | DA     | <b>ATA</b> | BI     | TS     |      |      |      |     |     |   |   |   |   |     |

|        | _      | SI     | //3    | SI     | <b>M2</b> | S      | <b>M1</b> |        |        |        |        |        |        |        |        |        |        |        |            |        |        |      |      |      |     |     |   |   |   |   |     |

| nINT   | CDGW   | RS3    | xEQt3  | RS2    | xEQt2     | RS1    | xEQt1     |        |        |        |        |        |        |        |        |        |        |        |            |        |        |      |      |      |     |     |   |   |   |   |     |

Table 6-4: 32 bit DATAGRAM structure received by µC (MSB received first)

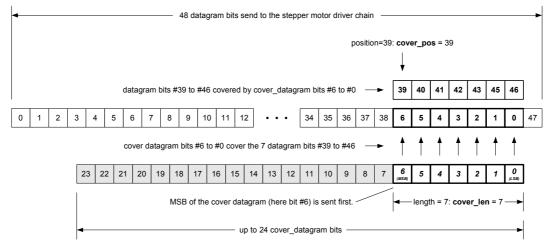

The status bit **nINT** is the internal low active interrupt controller output signal. Handling of interrupt conditions without using interrupt techniques is possible by polling this status bit. The interrupt signal is also directly available at the SDO\_C pin of the TMC428 if nSCS\_C is high. The pin SDO\_C may directly be connected to an interrupt input of the microcontroller. Since the SDO\_C / nINT output is multiplexed, the microcontroller has to disable its interrupt input while it sends a datagram to the TMC428, because the SDO\_C signal- driven by the TMC428 -alternates during datagram transmission. For initialization purposes, the TMC428 enables direct communication between the microcontroller and the stepper motor driver chain by sending a so called cover datagram (see sections 9.2 and 9.3). The position cover\_position and actual length cover\_len of a cover datagram is specified by writing them into a common register. Writing an up to 24 bit wide cover datagram to the register cover datagram will fade in that cover datagram into the next datagram sent to the stepper motor driver chain. As a default setting, the TMC428 only sends datagrams on demand. Optionally, continuous update- periodic sending of datagrams to the stepper motor driver chain -is also possible. So, the status bit named **CDGW** (cover datagram waiting) is a handshake signal for the microcontroller in regard to the datagram covering mechanism. This feature is necessary to enable direct data transmission from a microcontroller to the stepper motor driver chips for initialization purposes. The CDGW status bit also gives the status of the datagram high word and datagram low word (see section 9.1).

The status bits **RS3**, **RS2**, **RS1** represent the settings of the reference switches. But, the reference switch inputs REF3, REF2, REF1 are not mapped directly to these status bits. Rather, the reference switch inputs may have different functions, depending on programming (see pages 21 - 23). The three status bits **xEQt3**, **xEQt2**, **xEQt1** indicate individually for each stepper motor, if it has reached its target position. The status bits **RS3**, **RS2**, **RS1** and bits **xEQt3**, **xEQt1** can trigger an interrupt or enable simple polling techniques.

# 6.5 Simple Datagram Examples

The % prefix- normally indicating binary representation in this data sheet -is omitted for the following datagram examples. Assuming, one would like to write (RW=0) to a register (RRS=0) at the address %<u>001101</u> the following data word %0000 0000 0000 0001 0010 0011, one would have to send the following 32 bit datagram

#### 0<u>110011</u>000000000000000000100100011

to the TMC428. With inactive interrupt (nINT=1), no cover datagram waiting (**CDGW**=0), all reference switches inactive (RS3=0, RS2=0, RS1=0), and all stepper motors at target position (xEQt3=1, xEQt2=1, xEQt1=1) the status bits would be %<u>10010101</u> the TMC428 would send back the 32 bit datagram:

####

To read (RW=1) back the register written before, one would have to send the 32 bit datagram

####

to the TMC428 and would get back from it the datagram

#### <u>10010101</u>0000000000000000100100011.

Write (RW=0) access to on-chip RAM (RRS=1) to an address %<u>111111</u> occurs similar to register access, but with RRS=1. To write two 6 bit data words %100001 and %100011 to successive pair-wise RAM addresses %<u>111111</u>0 and %<u>111111</u>1 (%100001 to %<u>111111</u>0 and %100011 to %<u>111111</u>) which are commonly addressed by one datagram (see pages 13 and 33), one would have to send the datagram

#### 1<u>111111</u>**0**000000000010001100100001.

# 7 Address Space Partitions

The address space is partitioned in different ranges. Each of the up to three stepper motors has a set of registers individually assigned to it, arranged within a contiguous address space. An additional set of registers within the address space holds some global parameters common for all stepper motors. One dedicated global parameter register is essential for the configuration of the serial four wire stepper motor driver interface. One half of the on-chip RAM address space holds the configuration parameters for the stepper motor driver chain. The other half of the on-chip RAM address space is provided to store a microstep table if required. The first seven datagram bits ( $sdi_c_bit#31$  and  $sdi_c_bit#30$  ...  $sdi_c_bit#25$ , respectively RRS and ADDRESS) address the whole address space of the TMC428.

| address ran | ges (ir | ncl. RRS)                | assignment                                             |            |

|-------------|---------|--------------------------|--------------------------------------------------------|------------|

| %000 0000   |         | % <b>0</b> 00 1111       | 16 registers for stepper motor #1                      |            |

| %001 0000   |         | % <b>0</b> 01 1111       | 16 registers for stepper motor #2                      | registers  |

| %010 0000   |         | %010 1111                | 16 registers for stepper motor #3                      | with up to |

| %011 0000   |         | %011 1110                | 15 common registers                                    | 24 bits    |

|             |         | %011 1111                | 1 global parameter register                            |            |

| %100 0000   |         | %101 1111                | 32 addresses of 2x6 bit for driver chain configuration | RAM        |

| %110 0000   |         | % <mark>1</mark> 11 1111 | 32 addresses of 2x6 bit for microstep table            | 128x6 bit  |

Table 7-1: TMC428 address space partitions

The stepper motors are controlled directly by writing motion parameters into associated registers. Only one register write access is necessary to change a target motion parameter. E.g. to change the target position of one stepper motor, the microcontroller has to send only one 32 bit datagram to the TMC428. The same is true for changing a target velocity. Some parameters are packed together in a single data word at a single address. Those parameters– initialized once and unchanged during operation –have to be changed commonly. Access to on-chip RAM addresses concern two successive RAM addresses. So, always two data words are modified with each write access to the on-chip RAM. Once initialized after power-up, the content of the RAM is usually left unchanged.

#### 7.1 Read and Write

Read and write access is selected by the RW bit (sdi\_c\_bit#24) of the datagram sent from the  $\mu$ C to the TMC428. The on-chip configuration RAM and the registers are writeable with read-back option. Some addresses are read-only. Write access (**RW**=0) to some of those read-only registers triggers additional functions, explained in detail later.

# 7.2 Register Set

The register address mapping is given in Table 7-2 on page 14. These registers are initialized internally during power-up. During power-up initialization, the TMC428 sends no datagrams to the stepper motor driver chain.

**Note:** The RAM has to be initialized before writing target parameters to the register set.

#### 7.3 RAM Area

The RAM address mapping is given in Table 10-1 page 34. The on-chip RAM is *NOT* initialized internally during power-up. This has to be done by the microcontroller before operation.

**Note:** There are unused addresses within the address space of the TMC428. Access to these addresses has no effect. How ever, access should be avoided, because this address space may be used for future devices.

**Important Hint:** All register bits are initialized with '0' during power on reset, except the SPI clock predivider **clk2\_div** (see section 9.7, page 28) that is initialized with 15.

|        |        |        |        |          | 3      | 82 b   | oit C        | DAT    | <b>FAG</b> | GRA    | M:     | sen    | nt fr  | om     | n a      | μC     | to t   | he          | e T | гмс            | 42  | 28     | via      | pir      | n SI     | _וכ     | С         |          |      |        |     |    |

|--------|--------|--------|--------|----------|--------|--------|--------------|--------|------------|--------|--------|--------|--------|--------|----------|--------|--------|-------------|-----|----------------|-----|--------|----------|----------|----------|---------|-----------|----------|------|--------|-----|----|

| 3<br>1 | 3<br>0 | 2<br>9 | 2<br>8 | 2<br>7   | 2<br>6 | 2<br>5 | 2<br>4       | 2<br>3 | 2<br>2     | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6   | 1<br>5 | 1<br>4 | 1<br>3      |     | 1 ´<br>2 ´     |     | 1<br>0 | 9        | 8        | 7        | 6       | 5         | 4        | 3    | 2      | 1   | 0  |

| - RRS  | 0      |        |        | ,<br>RES |        | 5      | r<br>RW      | 5      | 2          | 1      | U      | 3      | 0      | ,      | 0        | J      |        | 5           |     |                |     |        |          |          |          |         |           |          |      |        |     |    |

|        | sm     | nda    |        | ID       |        |        |              |        |            |        | th     | ree    | ste    | epp    | er       | mo     | tor    |             |     | ster           |     |        | s (S     | SMC      | )A=      | {00     | , 01      | I, 1     | 0})  |        |     |    |

|        |        |        | 0      | 0        | 0      | 0      |              |        |            |        |        |        |        |        |          |        |        |             | _   | _tar           | _   |        |          |          |          |         |           |          |      |        |     |    |

|        |        |        | 0<br>0 | 0<br>0   | 0<br>1 | 1<br>0 |              |        |            | 1      |        | 1      |        |        | 1        |        |        |             | X_  | _act           | ua  |        |          |          | -        |         | m         | in       |      |        |     |    |

|        |        |        | 0      | 0        | 1      | 1      |              |        |            |        |        |        |        |        |          |        |        |             |     |                |     |        |          |          | -        |         | <br>ma    |          |      |        |     |    |

|        |        |        | 0      | 1        | 0      | 0      |              |        |            |        |        |        |        |        |          |        | 1      |             |     |                |     |        |          |          | , I      | _       | arge      |          |      |        |     |    |

|        | 0      | 0      | 0      |          | 0      | 1      | _            |        |            |        |        |        |        |        |          |        | 1      |             |     |                |     |        |          |          |          |         | ctua      |          |      |        |     |    |

|        | 0      | 0      | 0      | 1        | 1      | 0      | N۶           |        |            |        |        |        |        |        |          |        |        |             |     |                |     |        |          |          |          | -       | ma        |          |      |        |     |    |

|        | 0      | 1      | 0      | 1        | 1      | 1      | 0            |        |            |        |        |        |        |        |          |        |        |             |     |                |     |        |          |          | a        | a_a     | _<br>ctua | al       |      |        |     |    |

|        | 4      | ~      | 1      | 0        | 0      | 0      | RW=0 : WRITE |        | is         | _ag    | tat    |        | is     | _ale   | eat      |        | i      | S_'         | v0  | )              |     |        |          |          | á        | a_th    | ires      | hol      | d    |        |     |    |

|        | 1      | 0      | 1      | 0        | 0      | 1      | RI           |        |            |        |        |        |        |        |          | 1      |        |             |     | pn             |     |        |          |          |          |         |           |          |      | рс     | liv |    |

|        |        |        | 1      | 0        | 1      | 0      |              |        |            |        |        |        |        |        | lp       |        |        |             |     |                | _   | _      | cor      | nf       |          |         |           |          |      |        |     | n  |

|        |        |        | 1      | 0        | 1      | 1      | acc          |        |            |        |        |        |        |        |          |        |        |             |     | upt_           |     |        |          |          |          | i       | nte       | rrup     | ot_f | lags   |     |    |

|        |        |        | 1      | 1        | 0      | 0      | access /     |        |            |        |        |        |        |        |          | p      | ulse   | <u>e_</u> ( | di  | /              | ra  | amj    | o_d      |          |          |         |           |          |      | l      | JSr | S  |

| 0      |        |        | 1<br>1 | 1<br>1   | 0<br>1 | 1<br>0 | ר<br>ד       |        |            |        |        |        |        |        |          |        |        |             |     | latcl          | ~~  | d      |          | a        | x_re     | er_t    | ole       | ran      | се   |        |     |    |

|        |        |        | -      | JD       |        | 0      | RW=          |        |            |        |        |        |        |        | <u> </u> | mn     | n      |             |     | iste           |     |        | мг       | ۰۵=      | 11)      |         |           |          |      |        |     |    |

|        |        |        | 0      | 0        | 0      | 0      |              |        |            |        |        |        |        |        | 00       |        |        |             |     | m_l            |     |        |          |          | <u> </u> |         |           |          |      |        |     |    |

|        |        |        | 0      | 0        | 0      | 1      | R            |        |            |        |        |        |        |        |          | -      |        | -           |     | n_h            |     |        |          |          |          |         |           |          |      |        |     |    |

|        | 1      | 1      | 0      | 0        | 1      | 0      | READ         | cw     |            |        |        |        |        |        |          |        | 1      |             |     | over           | -   | _      |          |          |          |         |           |          | CO/  | /er    | len |    |

|        |        |        | 0      | 0        | 1      | 1      | ac           |        |            |        |        |        |        |        |          |        | C      | 2VC         |     | _dat           |     |        |          |          |          |         |           |          |      |        | -   |    |

|        |        |        | 1      | 0        | 0      | 0      | acces        |        |            |        |        |        |        |        |          |        |        | рс          | w   | ver-c          | do  | wr     | ١        |          |          |         |           |          |      |        |     |    |

|        |        |        | 1      | 1        | 1      | 0      | ö            |        |            |        |        |        |        |        |          |        |        |             |     |                |     |        |          |          |          |         | 13        | r3       | 12   | r2     | 11  | r1 |

|        |        |        |        |          |        |        |              |        |            |        |        |        |        |        |          |        |        |             |     |                |     |        |          |          |          |         | ро        | larit    | ties |        |     |    |

|        |        |        |        |          |        |        |              |        |            | 5      | F      |        |        |        | cont_u   |        |        |             |     |                |     |        |          |          | S        |         |           |          |      |        |     |    |

|        | 1      | 1      | 1      | 1        | 1      | 1      |              |        |            | mot    | refmi  |        |        |        | ЦЦ       |        |        |             | cl  | k2_            | div | v      |          |          | Cor      | DA      | 믭         | P        | SC   | nSCS_S | LS  | MD |

|        |        |        |        |          |        |        |              |        |            | 1r     | x      |        |        |        | pdate    |        |        |             |     |                |     |        |          |          | mInd     | С<br>¦⁄ | Þ         | Ā        | ×    | S.     |     |    |

|        |        |        |        |          |        |        |              |        |            |        |        |        |        |        | ଜି       |        |        |             |     |                |     |        |          |          | ٩        | 'ΑΒ     | ω         | ω        | ŝ    | 'v     |     |    |

| 7      |        | I      |        |          |        | L      |              |        |            | I      | I      |        |        |        |          |        |        |             |     |                |     |        |          |          |          |         | I         | 1        | I    | I      |     |    |

| RRS    |        | A      | DDF    | RES      | SS     |        | RW           |        |            |        |        |        |        |        |          |        |        |             | 0   | DAT            | A   |        |          |          |          |         |           |          |      |        |     |    |

| 3<br>1 | 3      | 2      | 2      | 2<br>7   | 2<br>6 | 2      | 2            | 2<br>3 | 2<br>2     | 2      | 2      | 1      | 1      | 1      | 1<br>6   | 1<br>5 | 1      | 1<br>3      |     | 1 <sup>2</sup> |     | 1      | 9        | 8        | 7        | 6       | 5         | 4        | 3    | 2      | 1   | 0  |

|        | 0      | 9      | 8      | 1        | Ø      | 5      | 4            | 3      | 2          | 1      | 0      | 9      | 8      | 7      | Ø        | э      | 4      | 3           |     | 2 ′            |     | 0      | <u> </u> | <u> </u> |          |         |           | <u> </u> |      |        | I   |    |

Table 7-2: TMC428 register address mapping

# 8 Register Description

The registers hold binary coded numbers. Some are unsigned (positive) numbers, some are signed numbers in two's complement, and some are control bits or single flags. The functionality of different registers depends on the ramp mode (s. page 21).

# 8.1 x\_target (IDX=%0000)

This register holds the current target position in units of full steps, respectively microsteps. The unit of the target position depends on the setting of the associated microstep resolution register **usrs**. If the difference **x\_target - x\_actual** is unequal zero, the TMC428 moves the stepper motor in that direction of **x\_target** so that the difference becomes zero. The condition | **x\_target - x\_actual** | <  $2^{23}$  must be satisfied for motion into the correct direction. Both, target position **x\_target** and current position **x\_actual** may be altered on the fly. Usually **x\_target** is modified to start a positioning. To move from one position to another, the ramp generator of TMC428 automatically generates ramp profiles in consideration of the velocity limits **v\_min** and **v\_max** and acceleration limit **a\_max**.

<u>Note:</u> The registers **x\_target**, **x\_actual**, **v\_min**, **v\_max**, **and a\_max** are initialized with zero after power up. Thus, no step pulses are generated because motion is prohibited.

## 8.2 x\_actual (IDX=%0001)

The current position of each stepper motor is available by read out of the registers called **x\_actual**. The actual position can be overwritten by the microcontroller. This feature is for reference switch position calibration under control of the microcontroller.

#### 8.3 v\_min (IDX=%0010)

This register holds the absolute value of the velocity at or below which the stepper motor can be stopped abruptly. The parameter **v\_min** is relevant only for deceleration while reaching a target position. It should be set greater than zero. This control value allows to reach the target position faster because the stepper motor is not slowed down below **v\_min** before the target is reached. Also consider, that due to the finite numerical representation of integral relations, the target position can not be reached exactly, if the calculated velocity is less than one, before the target is reached. So, setting **v\_min** to at least one assures reaching each target position exactly. The unit of velocity parameters (**v\_max**, **v\_target**, and **v\_actual**) is steps per time unit. The scale of velocity parameters (**v\_min**, **v\_max**, **v\_target**, **v\_actual**) is defined by the parameter **pulse\_div** (see page 25 for details) and depends on the clock frequency of the TMC428.

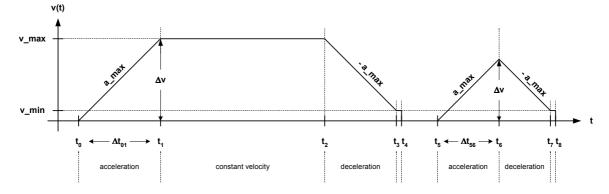

Figure 8-1: Velocity ramp parameters and velocity profiles

### 8.4 v\_max (IDX=%0011)

This parameter sets the maximum motor velocity. The absolute value of the velocity will not exceed this limit, except if the limit **v\_max** is changed during motion to a value below the current velocity.

<u>Note</u>: To set target position **x\_target** and current position **x\_actual** to an equivalent value (e.g. to set both to zero at a reference point), the assigned stepper motor should be stopped first, and the parameter **v\_max** should be set to zero to hold the assigned stepper motor at rest before writing into the register **x\_target** and **x\_actual**.

## 8.5 v\_target (IDX=%0100)

In modes RAMP\_MODE and SOFT\_MODE this register holds the current target velocity calculated internally by the ramp generator. In mode VELOCITY\_MODE a target velocity can be written into this register. Then the associated stepper motor accelerates until it reaches the target velocity specified. In VELOCITY\_MODE the velocity is changed according to the motion parameter limits if the register **v\_target** is changed. In HOLD\_MODE the register **v\_target** is ignored.

#### 8.6 v\_actual (IDX=%0101)

This read-only register holds the current velocity of the associated stepper motor. Internally, the ramp generator of the TMC428 processes with 20 bits while only 12 bits can be read out as **v\_actual**. So, an actual velocity of zero *read out* by the microcontroller means that the current velocity is in an interval between zero and one. Because of this, the actual velocity should not be used to detect a stop of a stepper motor. For stop detection there is a dedicated bit within the interrupt register, which can simply be read out by the micro processor or generate an interrupt. Writing zero to register **v\_actual**, which is possible in HOLD\_MODE only, immediately stops the associated stepper motor, because hidden bits are set to zero with each write access to the register **v\_actual**. In HOLD\_MODE only, this register is a read-write register. In HOLD\_MODE, motion parameters are ignored and the microcontroller has the full control to generate a ramp. In that mode, the TMC428 only handles the microstepping and datagram generation for the associated stepper motor of the daisy chain.

# 8.7 a\_max (IDX=%0110)

The absolute value of the maximum acceleration is defined by this register. It ranges from 0 to 2047. The unit of the acceleration is change of step frequency per time unit divided by 256. The scale of acceleration parameters (**a\_max**, **a\_actual**, **a\_threshold**) is defined by the parameter **ramp\_div** (see section 8.14, page 25 for details) and depends on the clock frequency of the TMC428. Setting **a\_max** to zero during motion of the stepper motor results in the inability of the stepper motor to stop, because it cannot change its velocity.

#### 8.7.1 a\_max\_lower\_limit & a\_max\_upper\_limit for ramp\_div ≠ pulse\_div

Under special conditions, the parameter **a\_max** might have a lower limit (>1) and might an upper limit (<2047) concerning *deceleration* in **RAMP\_MODE** and **SOFT\_MODE** if the difference between **ramp\_div** and **pulse\_div** is more than one. This is because the deceleration ramp is internally limited to 2^19 steps respectively microsteps, which is sufficient for most applications. The lower limit concerning the deceleration is given by

#### a\_max\_lower\_limit = 2^( ramp\_div - pulse\_div -1 )

With **v\_max** set to 2048 /  $\sqrt{2}$  ( $\approx$  1448) or lower, the **a\_max\_lower\_limit** is half of this value. If **ramp\_div** - **pulse\_div** - 1  $\leq$  0 the limit **a\_max\_lower\_limit** is 1 and the parameter **a\_max** may be set to down to 1 and of course to 0. On the other side, the upper limit of **a\_max** is given by

```

a_max_upper_limit = 2^{(ramp_div - pulse_div + 12) - 1}

```

So, if **ramp\_div** - **pulse\_div** +  $1 \ge 0$  the **a\_max\_upper\_limit** is > 2048 and the parameter **a\_max** might be set to any value up to 2047.

<u>Important Note</u>: So, a\_max can be set without restrictions within its range of 0 to 2047 for those combinations of ramp\_div and pulse\_div with | ramp\_div and pulse\_div |  $\leq 1$ .

The parameter **a\_max** must not be set below **a\_max\_lower\_limit** except **a\_max** is set to 0. The condition **a\_max**  $\ge$  **a\_max\_lower\_limit** as well as **a\_max**  $\le$  **a\_max\_upper\_limit** must be satisfied to reach any target position without oscillations. If that condition is not satisfied, oscillations around a target position may occur. For description of the parameters **ramp\_div** and **pulse\_div** see page 25.

So, **a\_max\_lower\_limit** and **a\_max\_upper\_limit** restrict the allowed range of **a\_max** only for those cases where **ramp\_div** is non-equal to **pulse\_div** and differ more than one. These both limits of **a\_max** concern the deceleration phase for **RAMP\_MODE** and **SOFT\_MODE** only. As long as **ramp\_div**  $\geq$  **pulse\_div** – **1** is valid, any value of **a\_max** within its range (0,1, ..., 2047) is allowed and there exists a valid pair {**pmul, pdiv**} for each **a\_max**. Qualitative verbalized, this is because the acceleration scaling determined by **ramp\_div** is compatible with the step velocity scaling determined by **pulse\_div**. In other words, large **ramp\_div** stands for low acceleration where large **pulse\_div** stands for low velocity and low acceleration is compatible with low speed and high speed as well, but high acceleration is more compatible with high speed.

**Important Note:** Changing at least one parameter out of the triple {**a\_max**, **ramp\_div**, **pulse\_div**} requires re-calculation of the parameter pair {**pmul**, **pdiv**} to update the associated register. For description of the parameters **pmul** and **pdiv** see section 8.10, page 18.

#### 8.8 a\_actual (IDX=%0111)

The actual acceleration, which the TMC428 actually applies to a stepper motor, can be read out by the microcontroller from this read-only register for monitoring purposes. The actual acceleration is used to select scale factors for the coil currents. Internally, it is updated with each clock. The returned value **a\_actual** is smoothed to avoid oscillations of the readout value. Thus, returned **a\_actual** values should not be used directly for precise calculations.

#### 8.9 is\_agtat & is\_aleat & is\_v0 & a\_threshold (IDX=%1000)

These parameters represent current scaling values  $I_s$  and are applied to the motor depending on the ramp phase: The parameter **is\_agtat** is applied if the acceleration (a) is greater than (gt) a threshold acceleration (a<sub>t</sub>). This is to increase current during acceleration phases. The parameter **is\_aleat** is applied if the acceleration is lower than or equal to (le) the threshold acceleration. This is the nominal motor current. The third parameter **is\_v0** is applied if the stepper motor is at rest, to save power, to keep it cool, and to avoid noise probably caused by chopper drivers. The parameter **a\_threshold** is the threshold used to compare with the current acceleration to select the current scale factor. The three parameters **is\_agtat**, **is\_aleat**, and **is\_v0** are bit vectors of three bit width. One of these is selected conditionally and assigned to an interim bit vector **i\_scale**. The current scaling factor  $I_s$  is defined in Table 8-1.

|   | i_scale |   |     | ls     |   |

|---|---------|---|-----|--------|---|

| 0 | 0       | 0 | 1   | = 100  | % |

| 0 | 0       | 1 | 1/8 | = 12.5 | % |

| 0 | 1       | 0 | 2/8 | = 25   | % |

| 0 | 1       | 1 | 3/8 | = 37.5 | % |

| 1 | 0       | 0 | 4/8 | = 50   | % |

| 1 | 0       | 1 | 5/8 | = 62.5 | % |

| 1 | 1       | 0 | 6/8 | = 75   | % |

| 1 | 1       | 1 | 7/8 | = 87.5 | % |

Table 8-1: Coil current scale factors

**Important Notes:** The maximum current scaling factor 1 is selected by **i\_scale** = %000. This is the power-on default. The minimum current scaling factor 1/8 = 0.125 is selected by **i\_scale** = %001. The current scaling factor  $I_s$  proportionally reduces the effective number of microsteps per full step. For example, with **i\_scale** = %100 (= 4/8 = 50%) the number of effective microsteps per full step is halved.

One of the three scale factors **is\_agtat**, **is\_aleat**, and **is\_v0** is selected according to Table 8-2. If the velocity is zero, the parameter **is\_v0** is used for scaling. If the velocity is not zero, either **is\_aleat** or **is\_agtat** is used for scaling, depending on the absolute value of the acceleration and the acceleration threshold **a\_threshold**.

| v = 0 |                              | I <sub>s</sub> := is_v0    |

|-------|------------------------------|----------------------------|

| v ≠ 0 | a   ≤ a <sub>threshold</sub> | I <sub>s</sub> := is_aleat |

| V + U | a   > a <sub>threshold</sub> | I <sub>s</sub> := is_agtat |

#### Table 8-2: Current scale selection scheme

The automatic motion dependent current scale feature of the TMC428 is provided primarily for microstep operation. It may also be applied for full step or half step drivers, if those provide current control bits. For those drivers, one could initialize the microstep table with a constant function, square function or sine wave using the two most significant DAC bits.

The configuration bit **continuous\_update** of the **stepper motor global parameter register** (Table 9-1, page 28) must be set to '1' to make sure that the coil current is scaled for v=0 if all motors are at rest.

## 8.10 pmul & pdiv (IDX=%1001)

The stepper motors are driven with a trapezoidal velocity profile, which may become triangular if the maximum velocity is not reached (see Figure 8-1, page 15). Depending on the difference between the target position **x\_target** and the actual position **x\_actual**, the ramp generator continuously calculates target velocities **v\_target** for the pulse generator (see Figure 8-2, page 19). The pulse generator then generates (micro) step pulses taking into account the motion parameter limits (**v\_min**, **v\_max**, **a\_max**). With a target velocity proportional to the difference of target position **x\_target** and current position **x\_actual**, the stepper motor approaches the target position. This also works, if the target position is changed during motion. The stepper motor moves to a target position until the difference between the target position **x\_target** and the current position **x\_actual** vanishes.

With the right proportionality factor **p**, target positions are quickly reached and without overshooting them. The proportionality factor primarily depends on the acceleration limit **a\_max** and on the two clock divider parameters **pulse\_div** and **ramp\_div**. These two separate clock divider parameters– set to the same value for most applications –give an extremely wide dynamic range for acceleration and velocity. These two *separate* parameters allow reaching very high velocities with very low acceleration.

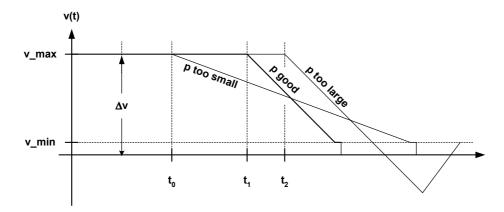

If the proportionality factor  $\mathbf{p}$  is set too small, this results in a slow approach to the target position. If set too large, it causes overshooting and even oscillations around the target position. The calculation of the proportionality factor is simple:

The representation of the proportionality factor **p** by the two parameters **p\_mul** and **p\_div** is some kind of a fixed point representation. It is

p = p\_mul / p\_div

with

p\_mul = {128, 128+1, 128+2, 128+3, ..., 128+127}

and

$p_{div} = \{2^3, 2^4, 2^5, ..., 2^{14}, 2^{15}, 2^{16}\}.$

Instead of direct storage of the parameters **p\_mul** and **p\_div**, the TMC428 stores two parameters called **pmul** and **pdiv**, with

$p_mul = 128 + pmul$  and  $p_div = 2^{3+pdiv} = 2^{(3+pdiv)}$

where

The reason why **p\_mul** ranges from 128 to 255 is, that **p** is divided by **p\_div** which is a power of two ranging from 8 to 65536. So, values of **p** less than 128 can be achieved by increasing **p\_div**.

**Note:** The parameters **pmul** and **pdiv** share a single address (IDX=%1001, see Table 7-2, page 14). The MSB of **p\_mul** is fixed set to '1'. So, sending **pmul** internally sets **p\_mul = 128 + pmul**. In other words, %10000000 = 128 is ORed as bit vector with the content of the register **pmul**.

#### Figure 8-2: Ramp generator and pulse generator

The parameter **p** has to be calculated for a given acceleration. This calculation is not done by the TMC428 itself, because this task has to be done only once for a given acceleration limit. The acceleration limit is a stepper motor parameter, which is usually fixed in most applications. If the acceleration limit has to be changed nevertheless, the microcontroller could calculate on demand a pair of **p\_mul** and **p\_div** for each acceleration limit **a\_max** and given **ramp\_div** and **pulse\_div**. Also, pre-calculated pairs of **p\_mul** and **p\_div** read from a table maybe sufficient.

#### 8.11 Calculation of p\_mul and p\_div

The proportionality factor  $\mathbf{p} = \mathbf{p_mul} / \mathbf{p_div}$  depends on the acceleration limit **a\_max** and frequency pre-divider parameters **ramp\_div** and **pulse\_div**. So, a pair of **p\_mul / p\_div** has to be calculated once for each provided acceleration limit **a\_max**. There may exist more than one valid pair of **p\_mul** and **p\_div** for a given **a\_max**. To accelerate, the ramp generator accumulates the acceleration value to the actual velocity with each time step. Internally, the absolute value of the velocity is represented by 11+8 = 19 bits, while only the most significant 11 bits and the sign are used as input for the step pulse generator. So, there are  $2^{11} = 2048$  values possible to specify a velocity, ranging from 0 to 2047. The ramp generator accumulates **a\_max** divided by  $2^8 = 256$  at each time step to the velocity during acceleration phases. So, the acceleration from velocity = 0 to maximum velocity = 2047 spans over 2048\* 256 / **a\_max** pulse generator clock pulses. Within that acceleration phase, the pulse generator generates S =  $\frac{1}{2} * 2048* 256$  / **a\_max** \* T steps for the (micro) step unit. The parameter T is the clock

divider ratio T =  $2^{ramp\_div} / 2^{pulse\_div} = 2^{ramp\_div - pulse\_div} = 2^{(ramp\_div-pulse\_div)}$ . During acceleration, the velocity has to be increased until the velocity limit **v\_max** is reached or deceleration is required to reach the target position exactly (see Figure 8-1). The TMC428 automatically decelerates, if required using the difference between current position and target position and the proportionality parameter **p**, which has to be **p** = 2048 / S. With this, one gets p = 2048 / ( (  $\frac{1}{2} * 2048 * 256 / a\_max$ ) \* 2^(ramp\\_div-pulse\\_div)). This expression can be simplified to

#### p = a\_max / ( 128 \* 2^( ramp\_div-pulse\_div ) ).

To avoid overshooting, the parameter **p\_mul** should be made approximately 5% smaller than calculated. Alternatively, one can arrange **p** reduced by an amount of 5%. If the proportionality parameter **p** is too small, the target position will be reached slower, because the slow down ramp starts earlier. The target position is approached with minimal velocity **v\_min**, whenever the internally calculated target velocity becomes less than **v\_min**. With a good parameter **p** the minimal velocity **v\_min** is reached a couple of steps before the target position. With parameter **p** set a little bit to large and small **v\_min** overshooting of one step respectively one microstep may occur. Decrementation of the parameter **pmul** avoids such one-step overshooting.

<u>Note:</u> Changing at least one parameter out of the triple {a\_max, ramp\_div, pulse\_div} requires recalculation of the parameter pair {pmul, pdiv} to update the associated register if necessary.

Figure 8-3: Proportionality parameter p and outline of velocity profile(s)

On first approach, to represent the parameter  $p = p_mul / p_div = (128+pmul) / 2^(3+pdiv)$  one chooses a pair of pmul and pdiv that approximates p, with pmul in range 0 ... 127 representing p\_mul in range 128 ... 255 and pdiv one out of {0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13} representing p\_div one out of {8, 16, 32,64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384, 32786, 65536}. There are only 128 \* 14 = 1792 pairs of (pmul, pdiv). So, one can simply try all possible pairs (pmul, pdiv) with a program and choose a matching pair. To find a pair, one calculates

p = a\_max / ( 128 \* 2^( ramp\_div-pulse\_div ) )

and

p' = p\_mul / p\_div = (128+pmul) / 2^(3+pdiv)

and

q = p / p'

for each pair (**pmul**, **pdiv**) and select one of the pairs satisfying the condition **0.95** < **q** < **1.0**. So, the value **q** interpreted as a function **q(a\_max, ramp\_div, pulse\_div, pmul, pdiv)** gives the quality criterion required. Although **q** = **1.0** indicates that (**pmul**, **pdiv**) perfectly represents the desired **p** for a given **a\_max**, this could cause overshooting because of finite numerical precision. In case of high

resolution microstepping, overshooting of one microstep is negligible in most applications. To avoid overshooting, use **pmul-1** instead of the selected **pmul** or select a pair (**pmul, pdiv**) with **q = 0.95**. The first given source code example 'pmulpdiv.c' showing programming in C language based on this brute force approach. Some conversions of the base present equations help to reduce the calculation effort drastically.

#### 8.11.1 Optimized Calculation of p\_mul and p\_div

With the equations above, one can simplify the calculation of the parameters **pmul** and **pdiv** using the expression

with

```

p = a_max / ( 128 * 2^( pulse_div - ramp_div ) ).

```

To avoid overshooting, use

$$p_reduced = p * (1 - p_reduction[%])$$

with **p\_reduction** approximately 5% instead of unreduced **p**. With this, one gets

#### pmul = p\_reduced \* 2^3 \* 2^pdiv - 128 = 0.95 \* p \* 2^3 \* 2^pdiv - 128.

With this, **pmul** becomes a function of the parameter **pdiv**. To find a valid pair {**pmul**, **pdiv**} one just has to choose that pair {**pmul**, **pdiv**} out of 14 pairs for **pdiv** = {0, 1, 2, 3, ..., 13} with **pmul** within the valid range  $0 \le pmul \le 127$ . An example 'pmulpdiv.c' showing programming in C language can be found on page 51. This source code can directly be copied from the PDF datasheet file.

# 8.12 lp & ref\_conf & ramp\_mode (rm) (IDX=%1010)

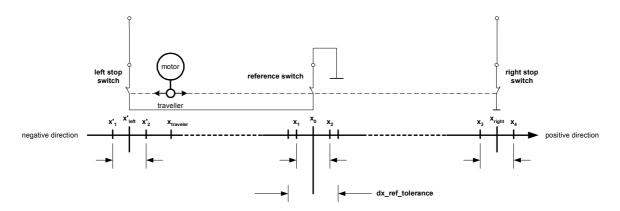

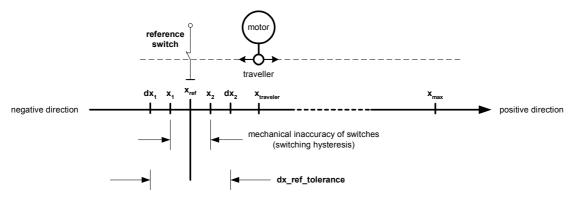

The bit called **Ip** (latched position) is a read only status bit. The configuration words **ref\_conf** and **ramp\_mode** are accessed via a common address, because these parameters normally are initialized only once. The configuration bits **ref\_conf** select the behavior of the reference switches, while the two bits **ramp\_mode** (**rm**) select one of the four possible stepping modes.