# TOSHIBA

## TC86R4600 64-bit RISC Microprocessor

1 9 9 4 - 1 9 9 5

P R E L I M I N A R Y D A T A S H E E T

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

#### Published in November, 1994

Toshiba products described in this document are not authorized for use as critical components in life support systems without the written consent of the appropriate officer of Toshiba America, Inc. Life support systems are either systems intended for surgical implant in the body or systems which sustain life. A critical component is any component of a life support system whose failure to perform may cause a malfunction or failure of the life support system, or may affect its safety or effectiveness.

The information in this document has been carefully checked and is believed to be reliable. However, no responsibility can be assumed for innacuracies that may not have been caught. All information in this document is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent lrights of Toshiba or any third parties.

This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or re-export, directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

Brand names and product names mentioned herein may be trademarks or registered trademarks of their respective companies.

# TOSHIBA

## TC86R4600 64-bit RISC Microprocessor

## Features

- Available in 100 MHz and 133 MHz versions

- True 64-bit microprocessor

- 64-bit integer operations

- 64-bit floating-point operations

- 64-bit registers

- 64-bit virtual address space

- High-performance microprocessor

- 100 peak MIPS at 100MHz

- 33 peak MFLOPs at 100MHz

- 68 SPECint92 at 100MHz

- 60 SPECfp92 at 100 MHz

- Two-way set associative caches

- High level of integration

- 64-bit integer CPU

- 64-bit floating-point unit

- 16KB instruction cache; 16KB data cache

- Flexible MMU with large TLB

- Low-power operation

- 3.3V power supply

- 2.5W @ 100MHz, 3.3V (internal, No Load)

- Standby mode reduces internal power to 60mW

- Standard operating system support includes Microsoft Windows NT<sup>™</sup>

- Fully software compatible with R4000 RISC processor family

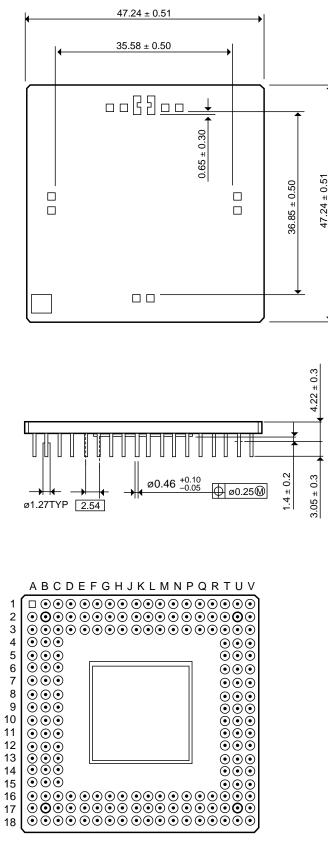

- Available in CQFP 208-pin (Ceramic QFP) or R4000PC/R4400PC pin-compatible 179-pin PGA

- Pipeline operates at 2x input clock frequency

- 64GB physical address space

- Processor family for a wide variety of applications

- Desktop workstations and "green" PCs

- Deskside or departmental servers

- Notebooks

- High-performance embedded applications

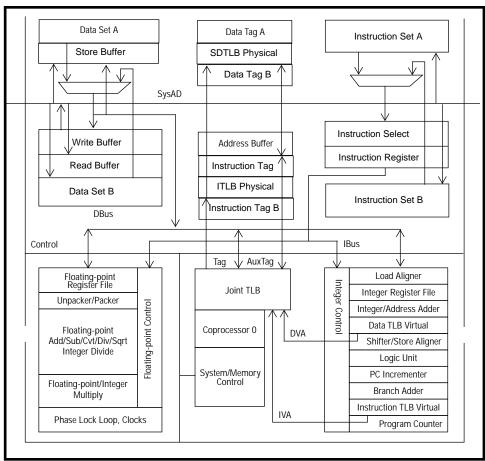

Figure 1. TC86R4600 Block Diagram

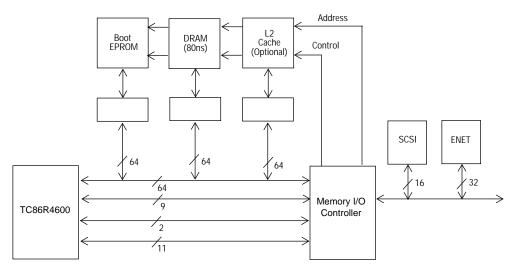

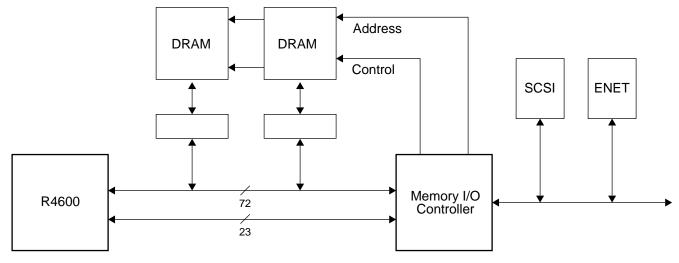

Figure 2. Typical System Block Diagram

## Description

The R4600 supports a wide variety of processor based applications, from 32-bit desktop or notebook systems through high-performance, 64-bit OLTP systems. Compatible with the TC86R4400PC family for both hardware and software, the R4600 will serve in many of the same applications, but in addition supports low-power operation for applications such as notebook computers. It does not provide integrated secondary cache and multiprocessor support as found in the R4000SC and R4000MC, but it is possible to build an external secondary cache. However, the large on-chip two-way set associative caches make this unnecessary for most applications.

The R4600 brings R4000SC performance levels to the R4000PC package, while at the same time providing lower cost and lower power requirements. These performance levels are achieved by providing larger on-chip caches that are two-way set associative, fewer pipeline stalls, and early restart for data cache misses. The result is 68 SPECint92 and 60 SPECfp92 (exact figures are system dependent) for 100MHz devices.

The R4600 provides complete upward application-software compatibility with the TC85R3000 family of microprocessors as well as the TC86R4000 family of microprocessors. Microsoft Windows NT and UNISOFT Unix V.4 operating systems insure the availability of thousands of applications programs, geared to provide a complete solution to a large number of processing needs. An array of development tools facilitates the rapid development of R4600-based systems, enabling a wide variety of customers to take advantage of the MIPS Open Architecture philosophy.

Together with the R4000 family, the R4600 provides a compatible, timely, and necessary evolution path from 32-bit to true 64-bit computing. The original design objectives of the R4000 clearly mandated this evolution path; the result is a true 64-bit processor fully compatible with 32-bit operating systems and applications. The 64-bit computing and addressing capability of the R4600 enables a wide variety of capabilities previously limited by a smaller address space. For example, the large address space allows operating systems with extensive file mapping; direct access to large files can occur without explicit I/O calls. Applications such as large CAD databases, multi-media, and high-quality image storage and retrieval all directly benefit from the enlarged address space.

This data sheet provides an overview of the features and architecture of the R4600 CPU. Further information on development support, application notes, and complementary products are also available from your local Toshiba sales representative.

#### Hardware Overview

The R4600 family brings a high level of integration designed for high-performance computing. The key elements of the R4600 are briefly described below.

#### Pipeline

The R4600 uses a 5-stage pipeline similar to the R3000. The simplicity of this pipeline allows the R4600 to be lower cost and lower power than super-scalar or super-pipelined processors. Unlike the R3000, the R4600 does virtual to physical address translation in parallel with cache access. This allows the R4600 to operate at twice the frequency of the R3000 and to support a larger TLB for address translation.

Compared to the 8-stage R4000 pipeline, the R4600 is more efficient (requires fewer stalls).

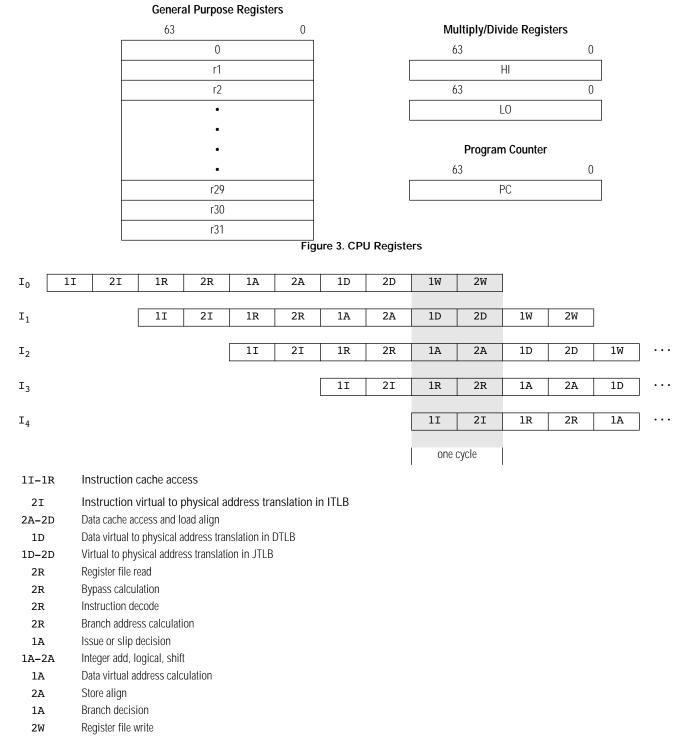

Figure 3 on page 3 shows the R4600 pipeline.

#### **Integer Execution Engine**

The R4600 implements the extended MIPS instruction set architecture, and thus is fully upward compatible with applications running on the earlier generation parts. The R4600 includes the same additions to the instruction set as found in the R4000 family of microprocessors, targeted at improving performance and capability while maintaining binary compatibility with earlier processors. The extensions result in better code density, greater multiprocessing support, improved performance for commonly used code sequences in operating system kernels, and faster execution of floating-point intensive applications. All resource dependencies are made transparent to the programmer, insuring transportability among implementations of the MIPS instruction set architecture.

In addition to the instruction extensions detailed above, new instructions have been defined to take advantage of the 64-bit architecture of the processor.

Figure 4. R4600 Pipeline

The MIPS integer unit implements a load/store architecture with single cycle ALU operations (logical, shift, add, sub) and an autonomous multiply/divide unit. The register resources include 32 general purpose orthogonal integer registers, the HI/LO result registers for the integer multiply/divide unit, and the program counter. In addition, the on-chip floating-point co-processor adds 32 floating-point registers, and a floating-point control/status register.

## **Register File**

The R4600 has 32 general purpose registers. These registers are used for scalar integer operations and address calculation. The register file consists of two read ports and one write port, and is fully bypassed to minimize operation latency in the pipeline.

## ALU

The R4600 ALU consists of the integer adder and logic unit. The adder performs address calculations in addition to arithmetic operations, and the logic unit performs all logical and shift operations. Each of these units is highly optimized and can perform an operation in a single pipeline cycle.

## Integer Multiply/Divide

The R4600 uses the floating-point unit to perform integer multiply and divide. The results of the operation are placed in the *HI* and *LO* registers. The values can then be transferred to the general purpose register file using the MFHI/MFLO instructions. Table 1 below shows the number of processor internal cycles required between an integer multiply or divide and a subsequent MFHI or MFLO operation, in order that no interlock or stall occurs.

| Table 1: Integer | multiply/divide cycles |

|------------------|------------------------|

|------------------|------------------------|

|      | 32-bit | 64-bit |

|------|--------|--------|

| MULT | 10     | 12     |

| DIV  | 42     | 74     |

## Floating-Point Co-Processor

The R4600 incorporates an entire floating-point co-processor on chip, including a floating-point register file and execution units. The floating-point co-processor forms a "seamless" interface with the integer unit, decoding and executing instructions in parallel with the integer unit.

## **Floating-Point Units**

The R4600 floating-point execution unit supports single and double precision arithmetic, as specified in the IEEE Standard 754. The execution unit is broken into a separate multiply unit and a combined add/convert/divide/square root unit. Overlap of multiplies and add/subtract is supported. The multiplier is partially pipelined, allowing a new multiply to begin every 6 cycles.

As in the R3000 and R4000, the R4600 maintains fully precise floating-point exceptions while allowing both overlapped and pipelined operations. Precise exceptions are extremely important in mission-critical environments, such as ADA, and highly desirable for debugging in any environment. The floating-point unit's operation set includes floatingpoint add, subtract, multiply, divide, square root, conversion between fixed-point and floating-point format, conversion among floating-point formats, and floating-point compare. These operations comply with the IEEE Standard 754.

Table 2 below gives the latencies of some of the floatingpoint instructions in internal processor cycles.

| Operation  | Single<br>Precision | Double<br>Precision |

|------------|---------------------|---------------------|

| ADD        | 4                   | 4                   |

| SUB        | 4                   | 4                   |

| MUL        | 8                   | 8                   |

| DIV        | 31                  | 60                  |

| SQRT       | 30                  | 59                  |

| CMP        | 3                   | 3                   |

| FIX        | 4                   | 4                   |

| FLOAT      | 6                   | 6                   |

| ABS        | 1                   | 1                   |

| MOV        | 1                   | 1                   |

| NEG        | 1                   | 1                   |

| LWC1, LDC1 | 2                   | 2                   |

| SWC1, SDC1 | 1                   | 1                   |

**Table 2: Floating-Point Cycles**

## Floating-Point General Register File

The floating-point register file is made up of sixteen 64-bit registers which can also be viewed as thirty-two 32-bit registers. With the LDC1 and SDC1 instructions the floating-point unit can take advantage of the 64-bit wide data cache and issue a co-processor load or store doubleword instruction in every cycle.

The floating-point control register space contains two registers-one for determining configuration and revision information for the co-processor and one for control and status information. These are primarily involved with diagnostic software, exception handling, state saving and restoring, and control of rounding modes.

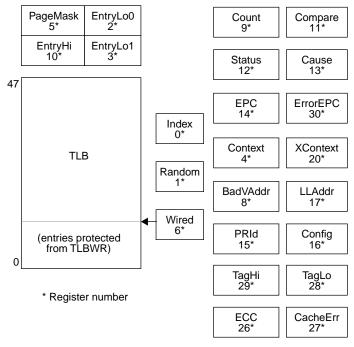

## System Control Co-processor (CP0)

The system control co-processor in the MIPS architecture is responsible for the virtual memory sub-system, the exception control system, and the diagnostics capability of the processor. In the MIPS architecture, the system control co-processor (and thus the kernel software) is implementation dependent. The R4600 CP0 is essentially identical to that of the R4000PC, except that the WatchLo and WatchHi registers are no longer present and the Index CACHE ops use an extra address bit to select one of the two sets (the R4000 caches are direct mapped, instead of twoway set associative). The Memory Management Unit controls the virtual memory system page mapping. It consists of an instruction address translation buffer (the ITLB), a data address translation buffer (the DTLB), a joint TLB (the JTLB), and co-processor registers used for the virtual memory mapping sub-system.

#### System Control Co-Processor Registers

The R4600 incorporates all system control co-processor (CP0) registers on-chip. These registers provide the path through which the virtual memory system's page mapping is examined and changed, exceptions are handled, and operating modes are controlled (kernel vs. user mode, interrupts enabled or disabled, cache features). In addition, the R4600 includes registers to implement a real-time cycle counting facility, to aid in cache diagnostic testing, and to assist in data error detection.

Figure 4 on page 5 shows the CP0 registers.

#### Virtual to Physical Address Mapping

The R4600 provides three modes of virtual addressing:

- user mode

- supervisor mode

- kernel mode

This mechanism is available to system software to provide a secure environment for user processes. Bits in a status register determine which virtual addressing mode is used. In the user mode, the R4600 provides a single, uniform virtual address space of 256GB (2GB for 32-bit mode).

When operating in the kernel mode, four distinct virtual address spaces, totalling 1024GB (4GB in 32-bit mode), are simultaneously available and are differentiated by the high-order bits of the virtual address.

The R4600 processors also support a supervisor mode in which the virtual address space is 256.5GB (2.5GB in 32-bit mode), divided into three regions based on the high-order bits of the virtual address.

Figure 5 on page 6 shows the address space layout for 32-bit operation.

When the R4600 is configured as a 64-bit microprocessor, the virtual address space layout is an upward compatible extension of the 32-bit virtual address space layout.

#### Joint TLB

For fast virtual-to-physical address decoding, the R4600 uses a large, fully associative TLB which maps 96 virtual pages to their corresponding physical addresses. The TLB is organized as 48 pairs of even-odd entries, and maps a virtual address and address space identifier into the large, 64GB physical address space.

Two mechanisms are provided to assist in controlling the amount of mapped space, and the replacement characteristics of various memory regions. First, the page size can be configured, on a per-entry basis, to map a page size of 4KB to 16MB (in multiples of 4). A CPO register is loaded with the page size of a mapping, and that size is entered into the TLB when a new entry is written. Thus, operating systems can provide special purpose maps; for example, a typical frame buffer can be memory mapped using only one TLB entry. The second mechanism controls the replacement algorithm when a TLB miss occurs. The R4600 provides a random replacement algorithm to select a TLB entry to be written with a new mapping; however, the processor provides a mechanism whereby a system specific number of mappings can be locked into the TLB, and thus avoid being randomly replaced. This facilitates the design of real-time systems, by allowing deterministic access to critical software.

The joint TLB also contains information to control the cache coherency protocol for each page. Specifically, each page has attribute bits to determine whether the coherency algorithm is: uncached, non-coherent write-back, non-coherent write-through write-allocate, non-coherent write-through no write-allocate. Non-coherent write-back is typically used for both code and data on the R4600; the write-through modes support more efficient frame buffer accesses than the R4000 family. The coherent modes are supported for R4000 compatibility and generate different transaction types on the system interface; cache coherency is not supported however.

#### Instruction TLB

The R4600 also incorporates a 2-entry instruction TLB. Each entry maps a 4KB page. The instruction TLB improves performance by allowing instruction address translation to occur in parallel with data address translation. When a miss occurs on an instruction address translation, the least-recently used ITLB entry is filled from the JTLB. The operation of the ITLB is invisible to the user.

Figure 5. The R4600 CP0 Registers

## Data TLB

The R4600 also incorporates a 4-entry data TLB. Each entry maps a 4KB page. The data TLB improves performance by allowing data address translation to occur in parallel with data address translation. When a miss occurs on a data address translation, the DTLB is filled from the JTLB. The DTLB refill is pseudo-LRU: the least recently used entry of the least recently used half is filled. The operation of the DTLB is invisible to the user.

| 0xFFFFFFFF<br>0xE0000000 | Kernel virtual address space<br>(kseg3)<br>Mapped, 0.5GB             |

|--------------------------|----------------------------------------------------------------------|

| 0xDFFFFFFF<br>0xC0000000 | Supervisor virtual address space<br>(sseg)<br>Mapped, 0.5GB          |

| 0xBFFFFFFF<br>0xA0000000 | Uncached kernel physical address space<br>(kseg1)<br>Unmapped, 0.5GB |

| 0x9FFFFFFF<br>0x80000000 | Cached kernel physical address space<br>(kseg0)<br>Unmapped, 0.5GB   |

| 0x7FFFFFFF               | Kernel user virtual address space<br>(kuseg)<br>Mapped, 2.0GB        |

| 0x00000000               |                                                                      |

Figure 6. Kernel Mode Virtual Addressing (32-bit mode)

#### **Cache Memory**

In order to keep the R4600's high-performance pipeline full and operating efficiently, the R4600 incorporates on-chip instruction and data caches that can be accessed in a single processor cycle. Each cache has its own 64-bit data path and can be accessed in parallel. For example, the cache subsystem provides the integer and floating-point units with an aggregate bandwidth of 1.6GB per second at a system clock frequency of 50MHz.

## Instruction Cache

The R4600 incorporates a two-way set associative on-chip instruction cache. This virtually indexed, physically tagged cache is 16KB in size and is protected with word parity.

Because the cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access, thus further increasing performance by allowing these two operations to occur simultaneously. The tag holds a 24-bit physical address and valid bit, and is parity protected.

The instruction cache is 64-bits wide, and can be refilled or accessed in a single processor cycle. Instruction fetches require only 32 bits per cycle, for a peak instruction bandwidth of 400MB/sec. Sequential accesses take advantage of the 64-bit fetch to reduce power dissipation, and cache miss refill writes 64 bits per cycle to minimize the cache miss penalty. The line size is eight instructions (32 bytes) to maximize performance.

## Data Cache

For fast, single cycle data access, the R4600 includes a 16KB onchip data cache that is two-way set associative with a fixed 32byte (eight words) line size.

The data cache is protected with byte parity and its tag is protected with a single parity bit. It is virtually indexed and physically tagged to allow simultaneous address translation and data cache access

The normal write policy is writeback, which means that a store to a cache line does not immediately cause memory to be updated. This increases system performance by reducing bus traffic and eliminating the bottleneck of waiting for each store operation to finish before issuing a subsequent memory operation. Software can, however, select write-through on a per-page basis when it is appropriate, such as for frame buffers.

Associated with the data cache is the store buffer. When the R4600 executes a store instruction, this single-entry buffer gets written with the store data while the tag comparison is performed. If the tag matches, then the data is written into the data cache in the next cycle that the data cache is not accessed (the next non-load cycle). The store buffer allows the R4600 to execute a store every processor cycle and to perform back-to-back stores without penalty.

#### Write buffer

Writes to external memory, whether cache miss writebacks or stores to uncached or write-through addresses, use the on-chip write buffer. The write buffer holds up to four 64-bit address and data pairs. The entire buffer is used for a data cache writeback and allows the processor to proceed in parallel with memory update. For uncached and write-through stores, the write buffer significantly increases performance over the R4000 family of processors.

#### System Interface

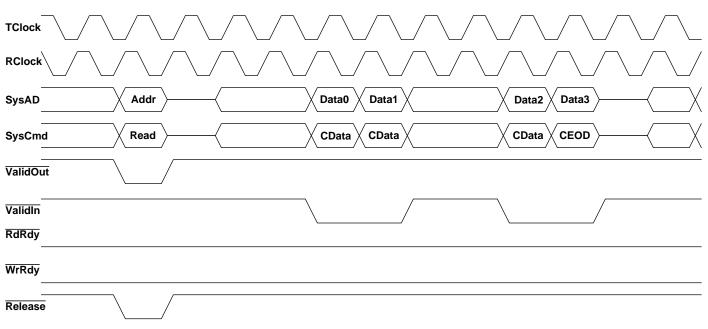

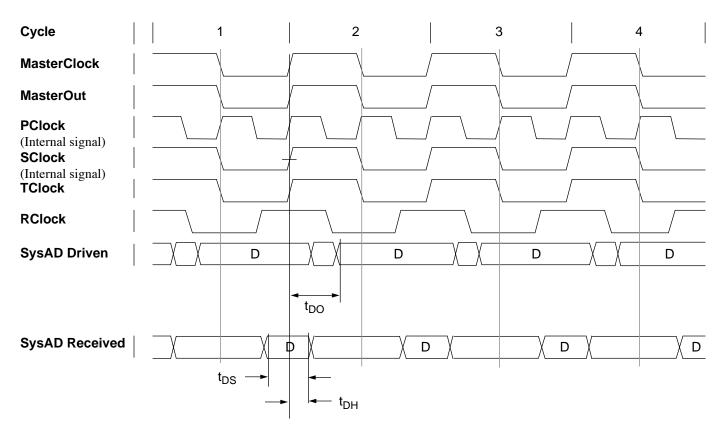

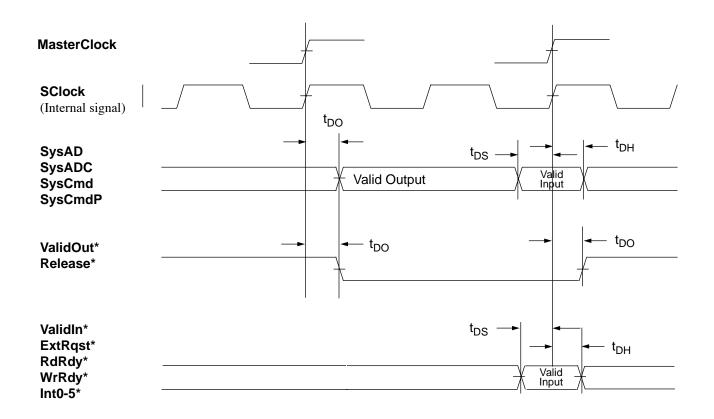

The R4600 supports a 64-bit system interface that is compatible with the R4000PC system interface. This interface operates from two clocks provided by the R4600, TClock[1:0] and RClock[1:0]. The TClock and RClock frequencies are derived from the internal (2x input clock) clock by dividing by: 8, 6, 4, 3, or 2.

The interface consists of a 64-bit Address/Data bus with 8 check bits and a 9-bit command bus protected with parity. In addition, there are 8 handshake signals and 6 interrupt inputs. The interface has a simple timing specification and is capable of transferring data between the processor and memory at a peak rate of 400MB/sec at 50MHz.

Figure 6 on page 7 shows a typical system using the R4600. In this example two banks of DRAMs are used to supply and accept data with a DDxxDDxx data pattern.

#### System Address/Data Bus

The 64-bit System Address Data (SysAD) bus is used to transfer addresses and data between the R4600 and the rest of the system. It is protected with an 8-bit parity check bus, SysADC.

The system interface is configurable to allow easier interfacing to memory and I/O systems of varying frequencies. The data rate and the bus frequency at which the R4600 transmits data to the system interface are programmable via boot time mode control bits (note, however that early versions of the R4600 will fix the system interface clock divisor at 2). Also, the rate at which the processor receives data is fully controlled by the external device. Therefore, either a low cost interface requiring no read or write buffering or a faster, high performance interface can be designed to communicate with the R4600. Again, the system designer has the flexibility to make these price/performance trade-offs.

#### System Command Bus

The R4600 interface has a 9-bit System Command (SysCmd) bus. The command bus indicates whether the SysAD bus carries an address or data. If the SysAD carries an address, then the SysCmd bus also indicates what type of transaction is to take place (for example, a read or write). If the SysAD carries data, then the SysCmd bus also gives information about the data (for example, this is the last data word transmitted, or the cache state of this data line is clean exclusive). The SysCmd bus is bidirectional to support both processor requests and external requests to the R4600. Processor requests are initiated by the R4600 and responded to by an external device. External requests are issued by an external device and require the R4600 to respond.

The R4600 supports one to eight byte and block transfers on the SysAD bus. In the case of a sub-doubleword transfer, the low-order three address bits gives the byte address of the transfer, and the SysCmd bus indicates the number of bytes being transferred.

#### Handshake Signals

There are eight handshake signals on the system interface. Two of these, RdRdy and WrRdy are used by an external device to indicate to the R4600 whether it can accept a new read or write transaction. The R4600 samples these signals before de-asserting the address on read and write requests.

Figure 7. Typical Desktop System Block Diagram

ExtRqst and Release are used to transfer control of the SysAD and SysCmd buses between the processor and an external device. When an external device needs to control the interface, it asserts ExtRqst. The R4600 responds by asserting Release to release the system interface to slave state.

ValidOut and ValidIn are used by the R4600 and the external device respectively to indicate that there is a valid command or data on the SysAD and SysCmd buses. The R4600 asserts Valid-Out when it is driving these buses with a valid command or data, and the external device drives ValidIn when it has control of the buses and is driving a valid command/data identifier or data.

#### Non-overlapping System Interface

The R4600 requires a non-overlapping system interface, compatible with the R4000PC. This means that only one processor request may be outstanding at a time and that the request must be serviced by an external device before the R4600 issues another request. The R4600 can issue read and write requests to an external device, and an external device can issue read and write requests to the R4600.

The R4600 asserts ValidOut and simultaneously drives the address and read command on the SysAD and SysCmd buses. If the system interface has RdRdy asserted, then the processor tristates its drivers and releases the system interface to slave state by asserting Release. The external device can then begin sending the data to the R4600.

Figure 6 on page 8 shows a processor block read request and the external agent read response. The read latency is 4 cycles (ValidOut to ValidIn), and the response data pattern is DDxxDD. Figure 8 on page 9 shows a processor block write.

## **External Requests**

The R4600 responds to requests issued by an external device. The requests can take several forms. An external device may need to supply data in response to an R4600 read request or it may need to gain control over the system interface bus to access other resources which may be on that bus. It also may issue requests to the processor, such as a request for the R4600 to write to the R4600 interrupt register.

The following is a list of the supported external requests:

- Read

- Write

- Null

#### **Boot-Time Options**

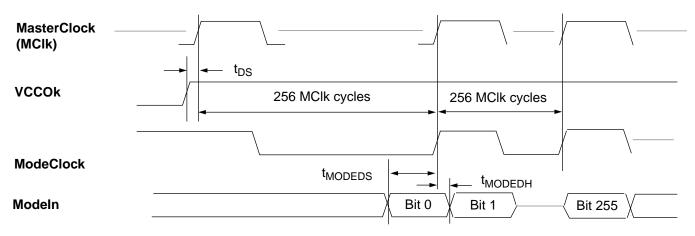

Fundamental operational modes for the processor are initialized by the boot-time mode control interface. The boot-time mode control interface is a serial interface operating at a very low frequency (MasterClock divided by 256). The low frequency operation allows the initialization information to be kept in a low cost EPROM; alternatively the twenty or so bits could be generated by the system interface ASIC.

Immediately after the VCCOk signal is asserted, the processor reads a serial bit stream of 256 bits to initialize all fundamental operational modes. After initialization is complete, the processor continues to drive the serial clock output, but no further initialization bits are read.

#### JTAG Interface

For compatibility with the R4000PC, the R4600 supports the JTAG interface pins, with the serial input connected to serial output. Boundary scan is not supported.

Figure 8. Processor Block Read

## **Boot-Time Modes**

The boot-time serial mode stream is defined in Table 3 below. Bit 0 is the bit presented to the processor when VCCOk is deasserted; bit 255 is the last.

#### Table 3: Boot-time mode stream

| Mode bit | Description                                                                                                                                                                                                                                                                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | reserved (must be zero)                                                                                                                                                                                                                                                                 |

| 41       | Writeback data rate<br>$0 \rightarrow D$ ,<br>$1 \rightarrow DDx$ ,<br>$2 \rightarrow DDxx$ ,<br>$3 \rightarrow DxDx$ ,<br>$4 \rightarrow DDxxx$ ,<br>$5 \rightarrow DDxxxx$ ,<br>$6 \rightarrow DxxDxx$ ,<br>$8 \rightarrow DxxxDxxx$ ,<br>$8 \rightarrow DxxxDxxx$ ,<br>9-15 reserved |

| 75       | Clock divisor (only divide by 2 supported in initial parts)<br>$0 \rightarrow 2$ ,<br>$1 \rightarrow 3$ ,<br>$2 \rightarrow 4$ ,<br>$3 \rightarrow 5$ ,<br>$4 \rightarrow 6$ ,<br>$5 \rightarrow 7$ ,<br>$6 \rightarrow 8$ ,<br>7 reserved                                              |

| 8        | $0 \rightarrow \text{Little endian}, 1 \rightarrow \text{Big endian}$                                                                                                                                                                                                                   |

| Mode bit | Description                                                                                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 109      | $00 \rightarrow R4000 \text{ compatible}$<br>$01 \rightarrow \text{reserved},$<br>$10 \rightarrow \text{pipelined writes},$<br>$11 \rightarrow \text{write re-issue}$                |

| 11       | Disable the timer interrupt on Int[5].                                                                                                                                               |

| 12       | reserved (must be zero)                                                                                                                                                              |

| 1413     | Output driver strength<br>$10 \rightarrow 100\%$ strength (fastest),<br>$11 \rightarrow 83\%$ strength<br>$00 \rightarrow 67\%$ strength<br>$01 \rightarrow 50\%$ strength (slowest) |

| 15       | $0 \rightarrow PLL \text{ enabled},$<br>1 $\rightarrow PLL \text{ disabled}$                                                                                                         |

| 25516    | must be zero                                                                                                                                                                         |

## Table 3: Boot-time mode stream (Continued)

| $\overline{\}$ |

|----------------|

| $\$            |

|                |

|                |

|                |

|                |

|                |

|                |

|                |

|                |

Figure 9. Processor Block Write

## Differences from the R4000PC

The interface between R4600 and external logic is a subset of the R4000PC interface, with two extensions for increased non-block write bandwidth. Interface logic meets or exceeds the JEDEC Standard for low-voltage CMOS-compatible (LVCMOS) VLSI digital circuits. Compatibility with the LVBO and perhaps LVTTL standards is desirable, but uncertain at this time.

The input clock for R4600 is multiplied by 2 by an on-chip PLL to produce the internal clock. R4600 will generate output clocks and operate its system interface at 1/2, 1/3, 1/4, 1/6, and 1/8 the frequency of the internal clock. For example, the R4600 at its 100MHz internal execute rate requires a 50MHz input clock, and supports either 50MHz, 33 MHz, 25 MHz, 16 MHz, or 12 MHz system interfaces. The input clock must be constant frequency for PLL operation. The PLL is expected to operate at frequencies from one fourth the maximum frequency to the maximum frequency.

The differences between the R4000PC and R4600 are as follows:

- Because the primary cache line is fixed at 32 bytes, only 32 byte block transfers will be supported.

- R4600 will not support JTAG.

- The R4600 serial configuration data stream will not be R4000PC compatible; different values for the bit stream will be required. The configuration protocol will remain the same. There will be approximately 20 configuration node bits for customers to control, located at the head of the configuration stream. There will be additional bits for debugging purposes that customers must set to zero.

- For graphics performance, R4600 will support two new interface protocols to double the non-block write bandwidth of the part. The new protocols will be enabled by two new mode bits; the default is to remain compatible with existing R4000PC systems. The use of these options will double peak output power consumption.

- The R4000 has feedback-controlled dynamic slew rate control output drivers. R4600 will use simple CMOS output drivers.

#### Non-block write enhancements

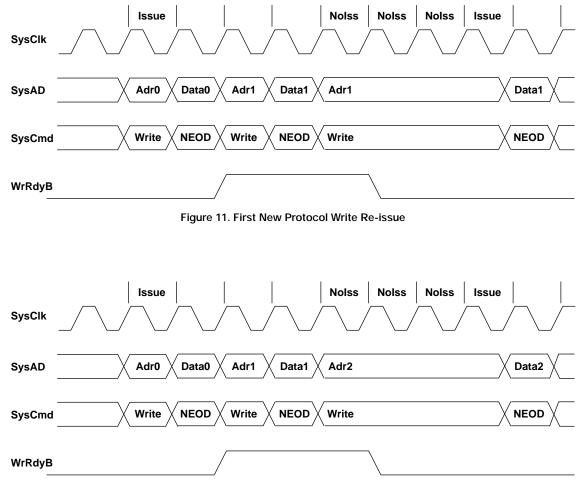

The R4000PC interface protocol requires that WrRdyB be asserted two system cycles prior to the issue of a write. An external agent that deasserts WrRdyB immediately upon receiving the write that fills its buffer therefore stops a write that would start four system cycles after the first. The R4000 leaves two null system cycles after a write address/data pair to give the external agent time to stop its next write. This situation is illustrated in the following figure:

| SysClk |            | Nolss Nolss N | olss   Issue |

|--------|------------|---------------|--------------|

| SysAD  | Adr0 Data0 | Adr1          | Data1        |

| SysCmd | Write      | Write         | NEOD         |

| WrRdyB |            |               |              |

Figure 10. R4000 PC Compatible Nonblock Write Protocol

An address/data pair every four system cycles is not sufficently high performance for all applications. For this reason, R4600 provides two new protocol options that modify the R4000 interface protocol to allow an address/data pair every two system cycles. The first protocol allows WrRdyB to be deasserted during the address cycle and forces a write to be reissued. The second leaves the sample point of WrRdyB unchanged and requires that the external agent accept one more write than the R4000 protocol. The first new protocol, write reissue, is illustrated in the figure below. Writes issue when WrRdyB is asserted both two cycles prior to the address cycle and during the address cycle.

The second new protocol, pipelined writes, maintains the R4000 write issue rule (issue if WrRdyB asserted two cycles prior to the address cycle), but simply eliminates the two null cycles between writes. The external agent is then required to accept one more write after it deasserts WrRdyB:

Figure 12. The Second New Protocol Pipelined Writes

| Tables 4 to     | 10 highlight some | of the differences | between the Re | 4600 and the R4000PC.     |

|-----------------|-------------------|--------------------|----------------|---------------------------|

| $100105 \pm 10$ | 10 mgmgnt some    | of the uniterences | between the R  | 1000  and  me  K 10001  C |

#### R4000PC R4600 I/O LVCMOS (3.3V ± 0.3V) R46003: LVCMOS (3.3V±0.3V) same and 208-pin CQFP (ceramic QFP) Package 179-pin ceramic PGA JTAG no ves Block transfer sizes 16B or 32B 32B SClock divisor 2, 3, 4, 6, or 8 2, 3, 4, 6, or 8 Non-block writes max throughput of 4 SClock cycles two new system interface protocol options that support 2 SClock cycle throughput (remains 4 in compatibility mode) Serial configuration as described in R4000 User's Guide different, as described in Table 3 Address bits 63..56 on bits 19..12 of virtual address zero reads and writes Uncached and writeuncached stores stall until sent on system uncached and write-though stores buffered through stores interface in 4-entry write buffer SysADC parity only same SysADC for non-data cycles zero on R4000, parity on R4400 zero Parity error during writeback use Cache Error exception output bad parity Error bit in data identifier of Bus Error if error bit set for any doubleword Only check error bit of first doubleword; all read responses other error bits ignored Parity error on read data Bus Error if parity error in any doubleword bad parity written to cache; take Cache Error exception if bad parity occurs on doublewords that the processor is waiting for Block writes 1-2 null cycles between address and data 0 cycles between address and data Release after Read Request variable latency 0 latency data bus undefined SysAD value for x cycles of data bus maintains last D cycle value writeback data pattern SysAD bus use after last D ? unused for trailing x cycles (e.g. DDxxDDxx, cycle of writeback not DDxxDDxx) Output slew rate dynamic feedback control simple CMOS output buffers with 2-bit static strength control driven high, do not connect IOOut output output slew rate control feedback loop output (reserved for future output) should be corrected to high IOIn input output slew rate control input (reserved for future input) do not connect GrpRunB Output same (reserved for future output) should be connected to VCC GrpStallB input same (reserved for future input) indicates compare mismatch driven high, do not connect FaultB output pin (reserved for future output)

#### Table 4: System interface comparison between R4000PC and R4600

|                                   | R4000PC                                                                                               | R4600                                                                                          |

|-----------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Cache Sizes                       | 8KB Instruction cache, 8KB Data cache                                                                 | 16KB Instruction cache, 16KB Data cache                                                        |

| Cache Line Sizes                  | software selectable between 16B and 32B                                                               | fixed at 32B                                                                                   |

| Cache Index                       | vAddr <sub>120</sub>                                                                                  | same                                                                                           |

| Cache Tag                         | pAddr <sub>3512</sub>                                                                                 | same                                                                                           |

| Cache Organization                | direct mapped                                                                                         | 2-way set associative                                                                          |

| Data cache write policy           | write-allocate and write-back                                                                         | write-allocate or not based on TLB entry,<br>write-through or write-back based on TLB<br>entry |

| Data cache miss                   | stall, output address, copy dirty data to write-<br>back buffer, refill cache, output write-back data | same, with FIFO to select the set to refill                                                    |

| Data order for block reads        | sub-block ordering                                                                                    | same                                                                                           |

| Data order for block writes       | sequential                                                                                            | same                                                                                           |

| Instruction cache miss<br>restart | restart after all data received and written to cache                                                  | same                                                                                           |

| Data cache miss restart           | restart after all data received and written to cache                                                  | restart on first doubleword, send subsequent doublewords to response buffer                    |

| Instruction Tag                   | 2-bit cache state                                                                                     | 1-bit cache state                                                                              |

| Cache miss overhead               | 5-8? cycles                                                                                           | 3-4? cycles                                                                                    |

| Instruction cache parity          | 1 parity bit per 8 data bits                                                                          | 1 parity bit per 32 data bits                                                                  |

| Data cache parity                 | 1 parity bit per 8 data bits                                                                          | same                                                                                           |

## Table 5: Cache comparison between R4000PC and R4600

## Table 6: TLB comparison between R4000PC and R4600

|                                         | R4000PC                                                             | R4600                                                                                      |

|-----------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Instruction virtual address translation | 2-entry ITLB                                                        | same                                                                                       |

| ITLB miss                               | 1 cycle penalty, refilled from JTLB, LRU replacement                | 1 cycle on branch, jump, and ERET, 2 cycles otherwise, refilled from JTLB, LRU replacement |

| Data virtual address transla-<br>tion   | done directly in JTLB                                               | 4-entry DTLB                                                                               |

| DTLB miss                               | n.a.                                                                | 1 cycle penalty, refilled from JTLB, pseudo-<br>LRU replacement                            |

| JTLB                                    | 48 entries of even/odd page pairs, fully associative                | same                                                                                       |

| Page size                               | 4KB, 16KB,, 16MB                                                    | same                                                                                       |

| Multiple entry match in JTLB            | sets TS in Status and disables TLB until<br>Reset to prevent damage | no damage for multiple match; no detection or shutdown implemented                         |

| Virtual address size                    | VSIZE = 40                                                          | same                                                                                       |

| Physical address size                   | PSIZE = 36                                                          | same                                                                                       |

|                                                               | R4000PC                                          | R4600                                                |

|---------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------|

| ALU latency                                                   | 1 cycle                                          | 1 cycle                                              |

| Load latency                                                  | 3 cycles                                         | 2 cycles                                             |

| Branch latency                                                | 4 cycles (2 cycle penalty for taken branches)    | 2 cycles (no penalty for taken branches)             |

| Store buffer                                                  | 2 doublewords                                    | 1 doubleword                                         |

| Integer multiply                                              | integer multiply hardware, 1 cycle to issue      | done in floating-point multiplier, 4 cycles to issue |

| Integer divide                                                | done in integer datapath adder, slips until done | done in floating-point adder, 4 cycles to issue      |

| Integer multiply                                              | HI and LO available at the same time             | LO available one cycle before HI                     |

| Integer divide                                                | HI and LO available at the same time             | HI available one cycle before LO                     |

| HI and LO hazards                                             | yes, HI and LO written early in pipeline         | no, HI and LO written after W                        |

| MFHI/MFLO latency                                             | 1 cycle                                          | 2 cycles                                             |

| SLLV, SRLV, SRAV                                              | 2 cycles to issue                                | 1 cycle to issue                                     |

| DSLL, DSRL, DSRA,<br>DSLL32, DSRL32,<br>DSRA32, DSLLV, DSRLV, | 2 cycles to issue                                | 1 cycle to issue                                     |

## Table 7: Pipeline comparison between R4000PC and R4600

## Table 8: Co-processor 0 comparison between R4000PC and R4600

|                                        | R4000PC                                                                                      | R4600                                                                                                      |

|----------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| WatchLo, WatchHi                       | implemented                                                                                  | unimplemented                                                                                              |

| Config                                 | as described in MIPS R-Series Architecture                                                   | subset                                                                                                     |

| Status                                 | as described in <i>MIPS R-Series Architecture</i> , but RP not functional                    | NO TS OF RP                                                                                                |

| Low-power standby mode                 | no                                                                                           | WAIT instruction disables internal clock, freez-<br>ing pipeline and other state; resume on inter-<br>rupt |

| MFC0/MTC0 hazard                       | only hazardous for certain cp0 register com-<br>binations                                    | always hazardous detected and 1-cycle slip<br>inserted                                                     |

| EntryLo0, EntryLo1                     | as described in MIPS R-Series Architecture                                                   | two new cache algorithms added to C field for<br>non-coherent write-through                                |

| TagLo, TagHi, ECC <b>,</b><br>CacheErr | R4000SC bits implemented but meaningless                                                     | Only bits meaningful on R4000PC imple-<br>mented                                                           |

| TagLo                                  | as described in MIPS R-Series Architecture                                                   | bits 53 used for reserved bits $ITag_{2825}$ , bit 2 used for F bit                                        |

| Exceptions                             | as described in <i>MIPS R-Series Architecture</i><br>(VCEI and VCED not possible in R4000PC) | VCEI, VCED, and WATCH exceptions not<br>implemented                                                        |

| Index CACHE ops<br>I Fill CACHE op     | use $vAddr_{124}$ to select line                                                             | use vAddr <sub>13</sub> to select set, vAddr <sub>125</sub> to select line of set                          |

| Index Store Tag CACHE op               | Status.CE ignored                                                                            | TagLo.P stored if Status.CE set                                                                            |

| PRId                                   | Imp = 0x04                                                                                   | Imp = 0x20                                                                                                 |

DSRAV

|                                    | R4000PC                                                                                 | R4600                                      |

|------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------|

| Possible exception stall           | only for operands that can cause exceptions                                             | some simplifications in detection hardware |

| Floating-point divide              | separate divide unit                                                                    | done in floating-point adder               |

| Floating-point square root         | done in floating-point adder                                                            | same                                       |

| Converts to/from 64-bit<br>integer | uses unimplemented for integer operands/<br>results with more than 53 bits of precision | handles full 64-bit operands and results   |

| Floating-point registers           | Status.FR enables all 32 floating point regis-<br>ters                                  | same                                       |

| FCR0                               | Imp = 0x05                                                                              | Imp = 0x20                                 |

## Table 9: Co-processor 1 comparison between R4000PC and R4600

## Table 10: R4000PC Errata comparison with R4600

|                                          | R4000PC errata                                   | R4600                                                                             |

|------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|

| COPz rs field illegal                    | FPE unimplemented exception for COP1 (incorrect) | reserved instruction exception, as described in <i>MIPS R-Series Architecture</i> |

| BCz rt field illegal                     | FPE unimplemented exception for COP1 (incorrect) | reserved instruction exception, as described in <i>MIPS R-Series Architecture</i> |

| Address error check for<br>xkseg         | C00000FFFFFFFFF<br>(incorrect)                   | C00000FF7FFFFFFF<br>(correct)                                                     |

| PTEBase field of Context<br>and XContext | same bits<br>(incorrect)                         | same                                                                              |

## **Pin Description**

The following is a list of interface, interrupt, and miscellaneous pins available on the R4600.

| Pin Name            | Туре         | Description                                                                                                                                                                                               |

|---------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System interface:   |              | ·                                                                                                                                                                                                         |

| ExtRqst*            | Input        | External request<br>Signals that the system interface needs to submit an external request.                                                                                                                |

| Release*            | Output       | Release interface<br>Signals that the processor is releasing the system interface to slave state.                                                                                                         |

| RdRdy*              | Input        | Read Ready<br>Signals that an external agent can now accept a processor read request.                                                                                                                     |

| WrRdy*              | Input        | Write Ready<br>Signals that an external agent can now accept a processor write request.                                                                                                                   |

| ValidIn*            | Input        | Valid Input<br>Signals that an external agent is now driving a valid address or data on the SysAD bus and a valid command or data identifier<br>on the SysCmd bus.                                        |

| ValidOut*           | Output       | Valid output<br>Signals that the processor is now driving a valid address or data on the SysAD bus and a valid command or data identifier on<br>the SysCmd bus.                                           |

| SysAD(63:0)         | Input/Output | System address/data bus<br>A 64-bit address and data bus for communication between the processor and an external agent.                                                                                   |

| SysADC(7:0)         | Input/Output | System address/data check bus<br>An 8-bit bus containing parity check bits for the SysAD bus.                                                                                                             |

| SysCmd(8:0)         | Input/Output | System command/data identifier bus<br>A 9-bit bus for command and data identifier transmission between the processor and an external agent.                                                               |

| SysCmdP             | Input/Output | System command/data identifier bus parity<br>A single, even-parity bit for the SysCmd bus.                                                                                                                |

| Clock/control inter | face:        | ·                                                                                                                                                                                                         |

| MasterClock         | Input        | Master clock<br>Master clock input at the processor operating frequency.                                                                                                                                  |

| MasterOut           | Output       | Master clock out<br>Master clock output aligned with MasterClock.                                                                                                                                         |

| RClock(1:0)         | Output       | Receive clocks<br>Two identical receive clocks at the system interface frequency.                                                                                                                         |

| TClock(1:0)         | Output       | Transmit clocks<br>Two identical transmit clocks at the system interface frequency.                                                                                                                       |

| IOOut               | Output       | Reserved for future output<br>Always HIGH.                                                                                                                                                                |

| IOIn                | Input        | Reserved for future input<br>Should be driven high.                                                                                                                                                       |

| SyncOut             | Output       | Synchronization clock out<br>Synchronization clock output. Must be connected to SyncIn through an interconnect that models the interconnect between<br>MasterOut, TClock, RClock, and the external agent. |

| SyncIn              | Input        | Synchronization clock in<br>Synchronization clock input. See SyncOut.                                                                                                                                     |

| Fault*              | Output       | Fault<br>Always HIGH.                                                                                                                                                                                     |

| Pin Name              | Туре   | Description                                                                                                                                                                                                                                                                        |

|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VccP                  | Input  | Quiet Vcc for PLL<br>Quiet Vcc for the internal phase locked loop.                                                                                                                                                                                                                 |

| VssP                  | Input  | Quiet VSS for PLL<br>Quiet Vss for the internal phase locked loop.                                                                                                                                                                                                                 |

| Interrupt interface   |        |                                                                                                                                                                                                                                                                                    |

| Int*(5:0)             | Input  | Interrupt<br>Six general processor interrupts, bit-wise ORed with bits 5:0 of the interrupt register.                                                                                                                                                                              |

| NMI*                  | Input  | Non-maskable interrupt<br>Non-maskable interrupt, ORed with bit 6 of the interrupt register.                                                                                                                                                                                       |

| JTAG interface:       |        |                                                                                                                                                                                                                                                                                    |

| JTDI                  | Input  | JTAG data in<br>JTAG serial data in.                                                                                                                                                                                                                                               |

| JTCK                  | Input  | JTAG clock input<br>JTAG serial clock input.                                                                                                                                                                                                                                       |

| JTDO                  | Output | JTAG data out<br>JTAG serial data out.                                                                                                                                                                                                                                             |

| JTMS                  | Input  | JTAG command<br>JTAG command signal, signals that the incoming serial data is command data.                                                                                                                                                                                        |

| Initialization interf | ace:   |                                                                                                                                                                                                                                                                                    |

| VCCOk                 | Input  | VCC is OK<br>When asserted, this signal indicates to the R4600 that the 3.3V (5.0V) power supply has been above 3.0V (4.5V) for more<br>than 100 milliseconds and will remain stable. The assertion of VCCOk initiates the reading of the boot-time mode control<br>serial stream. |

| ColdReset*            | Input  | Cold reset<br>This signal must be asserted for a power on reset or a cold reset. The clocks SClock, TClock, and RClock begin to cycle and<br>are synchronized with the de-assertion edge of ColdReset. ColdReset must be de-asserted synchronously with MasterOut.                 |

| Reset*                | Input  | Reset<br>This signal must be asserted for any reset sequence. It may be asserted synchronously or asynchronously for a cold reset, or<br>synchronously to initiate a warm reset. Reset must be deasserted synchronously with MasterOut.                                            |

| ModeClock             | Output | Boot-mode clock<br>Serial boot-mode data clock output at the system clock frequency divided by two hundred and fifty six.                                                                                                                                                          |

| Modeln                | Input  | Boot-mode data in<br>Serial boot-mode data input.                                                                                                                                                                                                                                  |

## **Electrical Characteristics**

#### Absolute Maximum Ratings Table 11. TC86R4600-100

$V_{SS} = 0V (GND)$

| Parameter                  | Symbol           | Ratings                     | Unit |

|----------------------------|------------------|-----------------------------|------|

| Supply Voltage             | V <sub>CC</sub>  | -0.5 ~ +4.6                 | V    |

| Input Voltage              | V <sub>IN</sub>  | -0.5 ~ V <sub>CC</sub> +0.5 | V    |

| Operating Case Temperature | T <sub>C</sub>   | 0 ~ +85                     | °C   |

| Storage Temperature        | T <sub>STG</sub> | -55 ~ +125                  | °C   |

## Table 11. TC86R4600-133

$V_{SS} = 0V (GND)$

| Parameter                  | Symbol           | Ratings                  | Unit |

|----------------------------|------------------|--------------------------|------|

| Supply Voltage             | V <sub>CC</sub>  | -0.5 ~ +4.6              | V    |

| Input Voltage              | V <sub>IN</sub>  | $-0.5 \sim V_{CC} + 0.5$ | V    |

| Operating Case Temperature | T <sub>C</sub>   | 0 ~ +85                  | °C   |

| Storage Temperature        | T <sub>STG</sub> | -55 ~ +125               | °C   |

#### NOTE:

1. If LSI is used above the maximum ratings, permanent destruction of LSI can result. In addition, it is desireable to use LSI for normal operation under the recommended condition. If these conditions are exceeded, reliability of LSI may be adversely affected.

### **Recommended Operation Conditions**

#### Table 12. TC86R4600-100

$V_{SS} = 0V (GND)$

| Parameter             | Symbol          | Conditions       | Min. | Max. | Unit |

|-----------------------|-----------------|------------------|------|------|------|

| Operating Temperature | T <sub>C</sub>  | Case temperature | 0    | 85   | °C   |

| Supply Voltage        | V <sub>CC</sub> |                  | 3.14 | 3.46 | V    |

## Table 13. TC86R4600-133

$V_{SS} = 0V (GND)$

| Parameter             | Symbol          | Conditions       | Min. | Max. | Unit |

|-----------------------|-----------------|------------------|------|------|------|

| Operating Temperature | T <sub>C</sub>  | Case temperature | 0    | 85   | °C   |

| Supply Voltage        | V <sub>CC</sub> |                  | 3.14 | 3.46 | V    |

## **DC Characteristics**

## Table 14. TC86R4600-100

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter                        | Symbol                       | Conditions                        | Min.                | Max.                  | Unit |

|----------------------------------|------------------------------|-----------------------------------|---------------------|-----------------------|------|

| Output Low Voltage               | V <sub>OL</sub>              | <sub>OUT</sub> = 4mA              |                     | 0.4                   |      |

| Output High Voltage              | V <sub>OH</sub>              | I <sub>OUT</sub> = -4mA           | 2.4                 |                       | V    |

| Input Low Voltage                | V <sub>IL</sub>              |                                   | -0.5                | 0.2 V <sub>CC</sub>   | v    |

| Input High Voltage               | V <sub>IH</sub>              |                                   | 0.7 V <sub>CC</sub> | V <sub>CC</sub> + 0.5 |      |

| Input Leakage                    | I <sub>IN</sub>              | $0 \le V_{\rm IN} \le V_{\rm CC}$ |                     | ±2                    | μΑ   |

| Input Capacitance                | C <sub>IN</sub>              |                                   |                     | 10                    | pF   |

| Output Capacitance               | C <sub>OUT</sub>             |                                   |                     | 10                    | р    |

| Operating Current                | I <sub>CC</sub> <sup>1</sup> | C <sub>L</sub> = 0 pF *1          |                     | TBD                   |      |

| Operating Current                | I <sub>CC</sub> <sup>2</sup> | C <sub>L</sub> = 50 pF *2         |                     | TBD                   | mA   |

| Operating Current (Standby mode) | lcc <sup>3</sup>             | $C_L = 50 pF$                     |                     | TBD                   |      |

## Table 15. TC86R4600-133

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter                        | Symbol                       | Conditions                        | Min.                | Max.                  | Unit |

|----------------------------------|------------------------------|-----------------------------------|---------------------|-----------------------|------|

| Output Low Voltage               | V <sub>OL</sub>              | <sub>OUT</sub> = 4mA              |                     | 0.4                   |      |

| Output High Voltage              | V <sub>OH</sub>              | I <sub>OUT</sub> = -4mA           | 2.4                 |                       | V    |

| Input Low Voltage                | V <sub>IL</sub>              |                                   | -0.5                | 0.2 V <sub>CC</sub>   |      |

| Input High Voltage               | V <sub>IH</sub>              |                                   | 0.7 V <sub>CC</sub> | V <sub>CC</sub> + 0.5 |      |

| Input Leakage                    | I <sub>IN</sub>              | $0 \le V_{\rm IN} \le V_{\rm CC}$ |                     | ±2                    | μΑ   |

| Input Capacitance                | C <sub>IN</sub>              |                                   |                     | 10                    | рF   |

| Output Capacitance               | C <sub>OUT</sub>             |                                   |                     | 10                    | pi   |

| Operating Current                | I <sub>CC</sub> <sup>1</sup> | C <sub>L</sub> = 0 pF *1          |                     | TBD                   |      |

| Operating Current                | I <sub>CC</sub> <sup>2</sup> | C <sub>L</sub> = 50 pF *2         |                     | TBD                   | mA   |

| Operating Current (Standby mode) | I <sub>CC</sub> <sup>3</sup> | $C_L = 50 pF$                     |                     | TBD                   |      |

(\*1)  $C_L = 0 \text{ pF}$  No sysAd activity (\*2)  $C_L = 50 \text{ pF}$  Pipelined write

## **AC Characteristics**

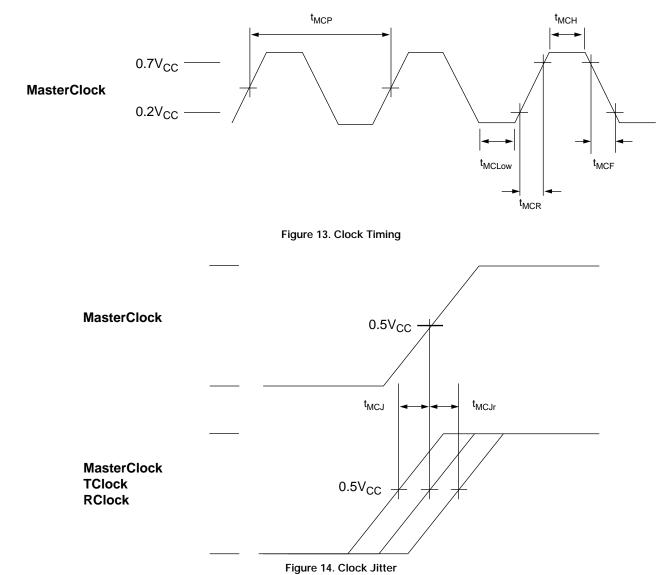

## **Clock Timing**

## Table 16. TC86R4600-100

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter                                                  | Symbol               | Conditions             | Min. | Max.                   | Unit |

|------------------------------------------------------------|----------------------|------------------------|------|------------------------|------|

| MasterClock High                                           | t <sub>MCH</sub>     | Transition $\leq 5$ ns | 4.0  |                        | 20   |

| MasterClock Low                                            | t <sub>MCL</sub>     | Transition ≤ 5ns       | 4.0  |                        | ns   |

| MasterClock Frequency (*1)                                 | f <sub>MCK</sub>     |                        | 25   | 50                     | MHz  |

| MasterClock Period                                         | t <sub>MCP</sub>     |                        | 20   | 40                     | ns   |

| Clock Jitter for MasterClock                               | t <sub>JIN</sub>     |                        |      | ±250                   | ps   |

| Clock Jitter for MasterOut, SyncOut,<br>TClock, and RClock | t <sub>MCJ</sub>     |                        |      | ±500                   | ps   |

| MasterClock Rise Time                                      | t <sub>MCR</sub>     |                        |      | 5.0                    |      |

| MasterClock Fall Time                                      | t <sub>MCF</sub>     |                        |      | 5.0                    | ns   |

| ModeClock Period                                           | t <sub>MODECKP</sub> |                        |      | 256 x t <sub>MCP</sub> |      |

## Table 17. TC86R4600-133

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter                                                  | Symbol               | Conditions        | Min. | Max.                   | Unit |

|------------------------------------------------------------|----------------------|-------------------|------|------------------------|------|

| MasterClock High                                           | t <sub>MCH</sub>     | Transition ≤ 5 ns | 3.0  |                        | ns   |

| MasterClock Low                                            | t <sub>MCL</sub>     | Transition ≤ 5ns  | 3.0  |                        | ns   |

| MasterClock Frequency (*1)                                 | f <sub>MCK</sub>     |                   | 25   | 67                     | MHz  |

| MasterClock Period                                         | t <sub>MCP</sub>     |                   | 15   | 40                     | ns   |

| Clock Jitter for MasterClock                               | t <sub>JIN</sub>     |                   |      | ±250                   | ps   |

| Clock Jitter for MasterOut, SyncOut,<br>TClock, and RClock | t <sub>MCJ</sub>     |                   |      | ±500                   | ps   |

| MasterClock Rise Time                                      | t <sub>MCR</sub>     |                   |      | 4.0                    |      |

| MasterClock Fall Time                                      | t <sub>MCF</sub>     |                   |      | 4.0                    | ns   |

| ModeClock Period                                           | t <sub>MODECKP</sub> |                   |      | 256 x t <sub>MCP</sub> |      |

$(\ast 1)$  Operation of the R4600 is only guaranteed with the Phase Lock Loop enabled.

## System Interface (\*1)

## Table 18. TC86R4600-100

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter        | Symbol          | Conditions                                         | Min. | Max. | Units |

|------------------|-----------------|----------------------------------------------------|------|------|-------|

| Data Output (*2) | +               | mode 1413 = 10 (fastest)                           | 1.0  | 9    | ns    |

| Data Output (*2) | t <sub>DO</sub> | mode 1413 = 01 (slowest)                           | 2.0  | 15   | ns    |

| Data Setup       | t <sub>DS</sub> | t <sub>RISE</sub> = 5ns<br>t <sub>FALL</sub> = 5ns | 3.5  |      | ns    |

| Data Hold        | t <sub>DH</sub> | t <sub>RISE</sub> = 5ns<br>t <sub>FALL</sub> = 5ns | 1.5  |      | ns    |

## Table 19. TC86R4600-133

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter        | Symbol          | Conditions                                         | Min. | Max. | Units |

|------------------|-----------------|----------------------------------------------------|------|------|-------|

| Data Output (*2) | +               | mode 1413 = 10 (fastest)                           | 1.0  | 9    | ns    |

|                  | <sup>t</sup> DO | mode 1413 = 01 (slowest)                           | 2.0  | 12   | ns    |

| Data Setup       | t <sub>DS</sub> | t <sub>RISE</sub> = 5ns<br>t <sub>FALL</sub> = 5ns | 3.5  |      | ns    |

| Data Hold        | t <sub>DH</sub> | t <sub>RISE</sub> = 5ns<br>t <sub>FALL</sub> = 5ns | 1.5  |      | ns    |

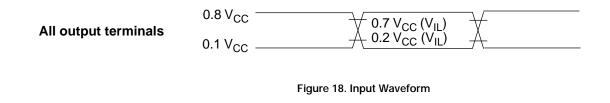

(\*1) Timings are measured from 1.5V of the clock to 1.5V of the signal.

(\*2) Capacitive load for all output timings is 50pF.

#### **Boot Time Interface Parameters**

#### Table 20. TC86R4600-100

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter       | Symbol              | Conditions | Min. | Max. | Units              |

|-----------------|---------------------|------------|------|------|--------------------|

| Mode Data Setup | t <sub>MODEDS</sub> |            | 3    |      | MasterClock cycles |

| Mode Data Hold  | t <sub>MODEDH</sub> |            | 0    |      | MasterClock cycles |

## Table 21. TC86R4600-133

$(T_C = 0^{\circ}C \sim 85^{\circ}C, V_{CC} = 3.3V \pm 5\%)$

| Parameter       | Symbol              | Conditions | Min. | Max. | Units              |

|-----------------|---------------------|------------|------|------|--------------------|

| Mode Data Setup | t <sub>MODEDS</sub> |            | 3    |      | MasterClock cycles |

| Mode Data Hold  | t <sub>MODEDH</sub> |            | 0    |      | MasterClock cycles |

## **Timing Diagrams**

- Note: (1) Timing measuring is based on the 50% point of all signals.

- (2) The above figure shows the signal waveforms when no deviation of output signals created in PLL from MasterClock is assumed.

Figure 15. Processor Clock, PClock to SClock Divisor of 2

Figure 16. System Interface Timing

TOSHIBA AMERICA ELECTRONIC COMPONENTS, INC.

Figure 17. Boot Time Interface Timing

AC Testing Terminal Load Condition

All output terminals

| $\rightarrow$ | – 1.5V - | ¥  |

|---------------|----------|----|

| /\            |          | /\ |