# TSB15LV01/TSB15LV01I

Video Signal Processor With IEEE-1394 Link Layer Controller

# Data Manual

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

# **Contents**

| Se | ection |           | Title                                     | Page |

|----|--------|-----------|-------------------------------------------|------|

| 1  | Introd | duction . |                                           | 1–1  |

|    | 1.1    | Feature   | s                                         | 1–2  |

|    | 1.2    | Function  | nal Block Diagram                         | 1–3  |

|    | 1.3    | Termina   | ıl Assignments                            | 1–4  |

|    | 1.4    | Termina   | Il Functions                              | 1–5  |

| 2  | Detai  | led Desci | ription                                   | 2–1  |

|    | 2.1    | 1394 Int  | terface                                   | 2–1  |

|    |        | 2.1.1     | Isochronous Versus Asynchronous Protocols | 2–1  |

|    |        | 2.1.2     | Packet Format/Protocol                    | 2–1  |

|    |        | 2.1.3     | 1394 Serial Bus Management Capabilities   | 2–6  |

|    |        | 2.1.4     | PHY/Link Interface                        |      |

|    |        | 2.1.5     | Enabling the Transmission of Video        | 2–7  |

|    | 2.2    | Sensor    | Interface                                 | 2–7  |

|    |        | 2.2.1     | CCD Interface                             | 2–8  |

|    |        | 2.2.2     | Analog Front End Interface                | 2–8  |

|    |        | 2.2.3     | CCD/AFE Timing                            | 2–12 |

|    | 2.3    | STAT In   | terface                                   | 2-21 |

|    | 2.4    | Motor C   | Control Interface                         | 2-23 |

|    |        | 2.4.1     | Motor Driver Timing                       | 2-23 |

|    |        | 2.4.2     | Positioning System                        | 2-24 |

|    |        | 2.4.3     | Pushbutton Interface                      | 2-24 |

|    | 2.5    | EEPRO     | M Interface                               | 2-25 |

|    | 2.6    | Video S   | ignal Processor                           | 2-26 |

|    |        | 2.6.1     | De-Mosaicing                              | 2-26 |

|    |        | 2.6.2     | Brightness                                | 2-27 |

|    |        | 2.6.3     | Gain and Exposure                         | 2-27 |

|    |        | 2.6.4     | Sharpness and Saturation                  | 2–28 |

|    |        | 2.6.5     | White Balance                             | 2-29 |

|    |        | 2.6.6     | Gamma                                     | 2-29 |

|    |        | 2.6.7     | YUV Conversion                            | 2-29 |

|    |        | 2.6.8     | Antiblooming                              | 2-30 |

|    |        | 2.6.9     | Backlight Compensation                    | 2-30 |

|    |        | 2.6.10    | White Spot Compensation                   |      |

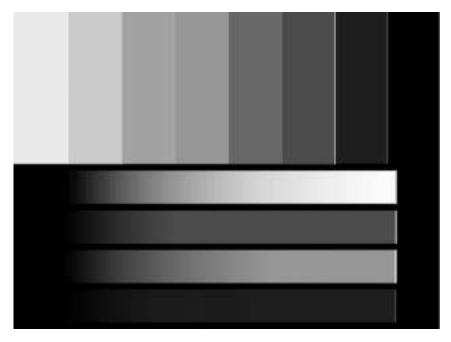

|    |        | 2.6.11    | Test Pattern                              | 2-31 |

| 3  | Addre  | ess Spac  | e                                         | 3–1  |

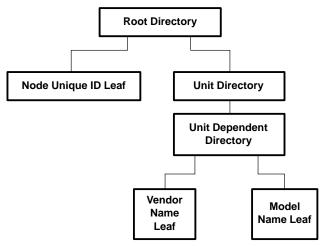

|    | 3.1    | 1394 No   | ode Memory Architecture                   | 3–1  |

|    | 3.2    | Top-Lev   | rel Memory Maps                           | 3–2  |

|                                       | 3.3     | Register Detail                                                    | 3–5  |  |  |  |

|---------------------------------------|---------|--------------------------------------------------------------------|------|--|--|--|

|                                       |         | 3.3.1 1394 Memory                                                  |      |  |  |  |

|                                       |         | 3.3.2 Inquiry Registers                                            |      |  |  |  |

|                                       |         | 3.3.3 Control and Configuration Registers                          |      |  |  |  |

| 4                                     |         | ical Characteristics                                               | 4–1  |  |  |  |

|                                       | 4.1     | Absolute Maximum Ratings Over Operating Free-Air Temperature Range | 4–1  |  |  |  |

|                                       | 4.2     | Recommended Operating Conditions                                   |      |  |  |  |

|                                       | 4.3     | Electrical Characteristics Over Recommended Ranges of              | 4.0  |  |  |  |

| _                                     | A !! -  | Supply Voltage and Operating Free-Air Temperature                  |      |  |  |  |

| 5                                     |         | cation Information                                                 |      |  |  |  |

| 6                                     | wecha   |                                                                    | 0-1  |  |  |  |

|                                       |         |                                                                    |      |  |  |  |

|                                       |         | List of Illustrations                                              |      |  |  |  |

| Fig                                   | ure     | Title                                                              | Page |  |  |  |

| 2-                                    | 1 Top-L | Level Sensor Interface Signal Flow                                 | 2–8  |  |  |  |

| 2-2                                   | 2 TLV9  | 90 Block Diagram                                                   | 2–9  |  |  |  |

| 2–3                                   | 3 AFE   | Serial Interface Timing                                            | 2–11 |  |  |  |

| 2-4                                   | 4 Sens  | or Interface Timing for ICX098/LZ24BP Sensor, Full Frame           | 2–13 |  |  |  |

| 2-                                    | 5 Sens  | or Interface Timing for ICX084 Sensor, Full Frame                  | 2–14 |  |  |  |

| 2-6                                   | 3 Sens  | or Interface Timing for TC237 Sensor, Full Frame                   | 2–15 |  |  |  |

| 2-7                                   | 7 Sens  | or Interface Timing for ICX098/LZ24BP Sensor,                      |      |  |  |  |

|                                       |         | art of Frame Data                                                  |      |  |  |  |

| 2–8                                   | 3 Sens  | or Interface Timing for ICX084 Sensor, Start of Frame              | 2–17 |  |  |  |

| 2-9                                   | 9 Sens  | or Interface Timing for TC237 Sensor, Start of Frame               | 2–18 |  |  |  |

| 2-                                    |         | sor Interface Timing for ICX098/LZ24BP/ICX084 Sensor,              |      |  |  |  |

| _                                     |         | art of Line                                                        |      |  |  |  |

|                                       |         | sor Interface Timing for TC237 Sensor, Start of Line               |      |  |  |  |

|                                       |         | sor Interface Timing for All Sensors, Horizontal Drive             |      |  |  |  |

| 2–13 STATn Motor Select Pulses        |         |                                                                    |      |  |  |  |

| 2–14 Read Timing 2–2                  |         |                                                                    |      |  |  |  |

|                                       |         | e Timing                                                           |      |  |  |  |

|                                       |         | n and Exposure Automatic and Manual Controls                       |      |  |  |  |

|                                       |         | 315LV01 Built-In Test Pattern                                      |      |  |  |  |

| 3–1 TSB15LV01 Root Directory Tree 3–2 |         |                                                                    |      |  |  |  |

# **List of Tables**

| Table Title                                                        | Page |

|--------------------------------------------------------------------|------|

| 2–1 Isochronous Data Block Packet Format                           | 2–2  |

| 2–2 Data Payload Per Isochronous Packet                            | 2–2  |

| 2–3 Video Data Payload Structure                                   |      |

| 2-4 Data Structure for Y, R, G, and B Data Components              | 2–4  |

| 2–5 Data Structure for U and V Data Components                     | 2–4  |

| 2-6 Asynchronous Quadlet Write Request Packet Format               | 2–4  |

| 2–7 Asynchronous Block Write Request Packet Format                 | 2–5  |

| 2-8 Asynchronous Quadlet Read Request Packet Format                | 2–6  |

| 2-9 Asynchronous Block Read Request Packet Format                  | 2–6  |

| 2-10 Approved CCD Sensors and Recommended Drivers                  | 2–8  |

| 2-11 Values Transmitted to AFE via Serial Interface                | 2–11 |

| 2–12 AFE Interface Timing Parameters                               | 2–11 |

| 2–13 ICX098/LZ24BP Full Frame Timing Parameters                    | 2-13 |

| 2–14 ICX084 Full Frame Timing Parameters                           | 2–14 |

| 2–15 TC237 Full Frame Timing Parameters                            | 2–15 |

| 2–16 ICX098/LZ24BP Frame Start Timing Parameters                   | 2–16 |

| 2–17 ICX084 Frame Start Timing Parameters                          | 2–17 |

| 2–18 TC237 Frame Start Timing Parameters                           | 2–18 |

| 2-19 ICX098/LZ24BP/ICX084 Line Start Timing Parameters             | 2-19 |

| 2–20 TC237 Line Start Timing Parameters                            | 2-20 |

| 2–21 Horizontal Drive Timing Parameters                            | 2-21 |

| 2–22 Status Terminal Functions Determined by STATn Register Fields | 2-22 |

| 2–23 Stepper Drive Table                                           | 2-24 |

| 2–24 EEPROM Interface Timing Parameters                            | 2-26 |

| 2–25 CCD Sensor Processing Adjustments                             | 2-26 |

| 2–26 Backlight Compensation Hot Regions                            | 2-30 |

| 3–1 TSB15LV01 Register Groupings                                   | 3–1  |

| 3–2 1394 Address Components                                        | 3–1  |

| 3–3 Top-Level Memory Map: 1394 Memory (Core CSRs)                  | 3–2  |

| 3-4 Top-Level Memory Map: 1394 Memory (Device Configuration ROM)   | 3–3  |

| 3–5 Top-Level Memory Map: Inquiry Registers                        | 3–4  |

| 3–6 Top-Level Memory Map: Control Registers                        | 3–5  |

| 3–7 Top-Level Memory Map: Configuration Registers                  | 3–5  |

| 3–8 Implemented Core CSRs                                          |      |

| 3–9 Serial-Bus-Dependent CSRs                                      |      |

| 3–10 Base Configuration ROM                                        |      |

| 3–11 Node Unique ID Leaf                                           |      |

| 3–12 | Unit Directory                                         | 3–7  |

|------|--------------------------------------------------------|------|

| 3–13 | Unit-Dependent Directory                               | 3–7  |

| 3–14 | Vendor Name Leaf                                       | 3–7  |

| 3–15 | Model Name Leaf                                        | 3–7  |

| 3–16 | Video Format Memory Map                                | 3–8  |

| 3–17 | Video Format Register Proper Values for TSB15LV01      | 3–8  |

| 3–18 | Video Format Field Descriptions                        | 3–8  |

| 3–19 | Video Mode Memory Map                                  | 3–9  |

| 3-20 | Video Mode Proper Values for TSB15LV01                 | 3–9  |

| 3–21 | Video Mode Field Descriptions                          | 3–9  |

| 3–22 | Video Frame Rate Memory Map                            | 3-10 |

| 3–23 | Video Frame Rate Proper Values for TSB15LV01           | 3-10 |

| 3–24 | Video Frame Rate Field Descriptions                    | 3-10 |

| 3–25 | Memory Map for Basic Function Register                 | 3–11 |

| 3–26 | Basic Function Register Proper Values for TSB15LV01    | 3–11 |

| 3–27 | Field Descriptions for Basic Function Register         | 3-11 |

| 3–28 | Memory Map for Feature Presence Registers              | 3–12 |

| 3–29 | Feature Presence Registers Proper Values for TSB15LV01 | 3–12 |

| 3-30 | Field Descriptions for Feature Presence Registers      | 3–12 |

| 3–31 | Memory Map for Feature Elements Inquiry Registers      | 3–13 |

| 3–32 | Feature Elements Registers Proper Values for TSB15LV01 | 3-14 |

| 3–33 | Field Descriptions for Feature Elements Registers      | 3–14 |

| 3–34 | Camera Initialize Register Memory Map                  | 3–15 |

| 3–35 | Camera Initialize Register Field Descriptions          | 3–15 |

| 3-36 | Memory Map for Camera Registers                        | 3–15 |

| 3–37 | Field Descriptions for Camera Registers                | 3–16 |

| 3–38 | Memory Map for Feature Control Registers               | 3–17 |

| 3–39 | Field Descriptions for Feature Registers               | 3–18 |

| 3–40 | Configuration Register Memory Map                      | 3–19 |

| 3–41 | Field Descriptions for Configuration Registers         | 3–20 |

|      |                                                        |      |

# 1 Introduction

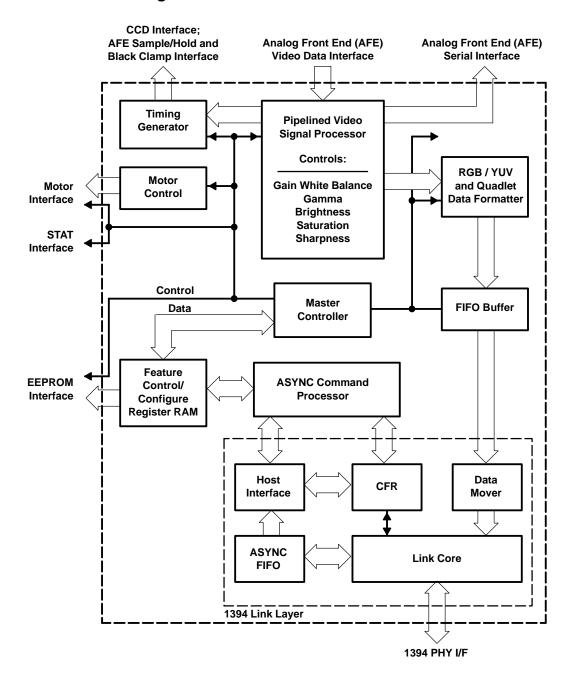

The TSB15LV01 is a video signal processor integrated with a 1394 link layer controller. It is designed to be the center of a host-controlled, full-motion color camera when coupled with a 1394 PHY, CCD sensor and driver, analog front end, and an external EEPROM device. A camera based on the TSB15LV01 is compliant with the IEEE 1394a standard and the 1394 Trade Association's Digital Camera specification, Draft 1.04.

The TSB15LV01 offers the advantage of 24-bit true-color digital video processing. This gives superior video quality at higher sustained data rates. Isochronous transfer of the video data and asynchronous control of the camera are accomplished via the 1394 high-speed serial bus, operating at data rates of up to 400 Mbits/s. This bus allows noncompressed full-motion digital video at rates of 30 frames/sec. Use of this serial connection eliminates the need for expensive video capture cards. The chipset supports the YUV 4:1:1, YUV 4:2:2, YUV 4:4:4, and RGB 24-bit formats.

The video signal processor (VSP) portion of the device incorporates proprietary digital image processing techniques, implemented with an advanced digital signal processing (DSP) ASIC. These techniques enable a camera to achieve excellent color accuracy and resolution. The use of a custom advanced CMOS ASIC process allows for both the advanced digital image processing techniques and for advanced color space conversion. This allows the multiple output formats required for a multipurpose video conferencing camera. Use of this advanced, low-power CMOS process also enables the camera to be powered by a notebook computer operating on battery power. The device is designed to work with CCDs that have a pixel resolution of 640(H) y 480(V). This resolution meets the VGA square pixel standards.

The 1394 link layer controller is capable of up to 400 Mbits/s operation and is compatible with both the IEEE 1394–1995 and 1394a standards. The TSB15LV01 implements all registers and address space required by the 1394 Trade Association's Digital Camera specification, Draft 1.04 (hereafter referred to as the Digital Camera Specification).

The device supports packet speeds of up to 400 Mbits/s, but the maximum bandwidth consumed by the device is 200 Mbits/s. This means that a TSB15LV01-based camera leaves at least 200 Mbits/s available to other functions.

With its balance of features and low cost, a system based on TSB15LV01 is well-suited for applications such as:

- PC Video Camera

- Video Conferencing

- Video Capture

- Still Picture Capture

- Set-Top Boxes

- Video Phone

- Gaming

- Webcam

- Robotics

- Security

# 1.1 Features

- Compatible With 1394 Trade Association's Digital Camera Specification, Draft 1.04

- 1394a Link Layer Controller With 400 Mbits/s Capability

- Support for Several CCD Sensors

- Sony ICX084AK, ICX098AK

- Sharp LZ24BP

- Texas Instruments TC237

- Integrated CCD (Charge-Coupled Device) and CDS (Correlated Double Sampling) Pulse Timer With Programmable Pulse Skew

- Video Controls

- Brightness (Auto/Manual)

- Exposure (Auto/Manual)

- Sharpness (Manual)

- Saturation (Manual)

- White Balance (Auto/Manual)

- Gamma (Manual)

- Backlight Compensation (Manual)

- Three Stepper Motor Controls for Focus/Zoom/Tilt or Other Motorized Functions

- EEPROM Interface

- Programmable Status/Test Terminals

- Seamlessly Connects to TI's 1394 Physical Layer Devices

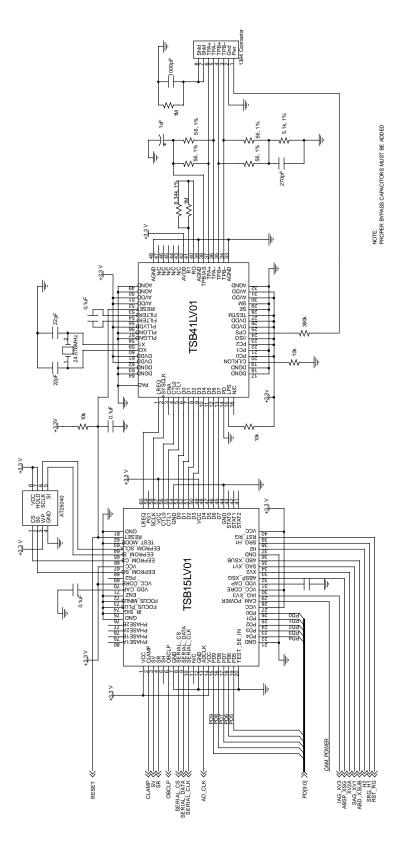

# 1.2 Functional Block Diagram

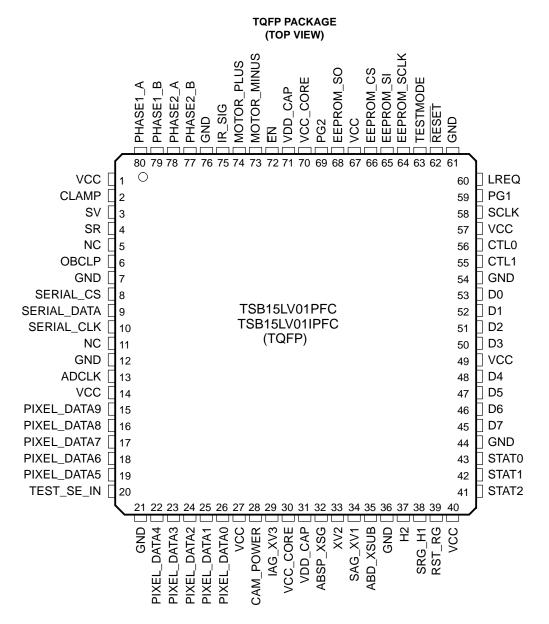

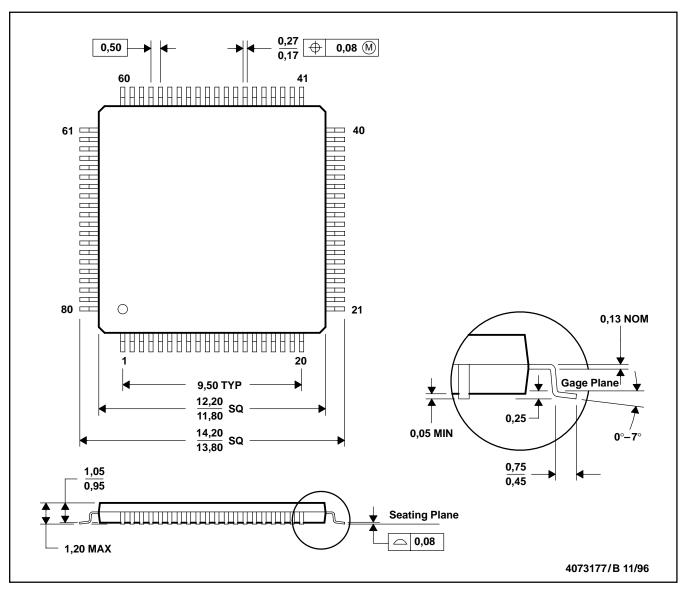

# 1.3 Terminal Assignments

NC - No internal connection

# 1.4 Terminal Functions

| TERMINAL                    |                 |     |                                                                                                                                                                                                                    |  |  |

|-----------------------------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.                    |                 | 1/0 | DESCRIPTION                                                                                                                                                                                                        |  |  |

|                             |                 |     | Analog Front End (AFE) Interface                                                                                                                                                                                   |  |  |

| ADCLK                       | 13              | 0   | ADC clock. Triggers the AFE's analog/digital converter to sample the amplifier output, and clocks the digital data out of the AFE to the TSB15LV01.                                                                |  |  |

| CLAMP                       | 2               | 0   | Pulse that instructs AFE to electrically clamp the ac-coupled pixel pulse to a fixed reference voltage.                                                                                                            |  |  |

| OBCLP                       | 6               | 0   | Optical Black Clamp pulse. Instructs the AFE to clamp its ADC output to a digital black reference value. Samples occur during the <i>black pixel</i> portion of the CCD's image signal.                            |  |  |

| PIXEL_DATA9-<br>PIXEL_DATA0 | 15-19,<br>22-26 | I   | Data bus that inputs processed video data from the AFE's analog/digital converter. PIXEL_DATA_IN9 is the MSB of these 10 bits.                                                                                     |  |  |

| SERIAL_CS                   | 8               | 0   | Serial interface chip select. Allows programming of AFE control registers. Signifies the beginning of data transmission on SERIAL_DATA.                                                                            |  |  |

| SERIAL_DATA                 | 9               | 0   | Serial interface digital data input. Allows programming of AFE control registers.                                                                                                                                  |  |  |

| SERIAL _CLK                 | 10              | 0   | Serial interface clock. Allows programming of AFE control registers. Clocks data out of SERIAL_DATA.                                                                                                               |  |  |

| SR                          | 4               | 0   | CCD reset-pedestal sampling pulse. Triggers the AFE to sample the reset pedestal of the pixel pulse received from the CCD image sensor.                                                                            |  |  |

| SV                          | 3               | 0   | CCD video data sampling pulse. Triggers the AFE to sample the data pedestal of the pixel pulse received from the CCD image sensor.                                                                                 |  |  |

|                             |                 |     | CCD Interface                                                                                                                                                                                                      |  |  |

| ABD_XSUB                    | 35              | 0   | Image area clear bias. Goes high to clear the image area. This pulse performs an <i>electronic shutter</i> function, controlling the integration time of the CCD image. Performed at the beginning of every frame. |  |  |

| ABSP_XSG                    | 32              | 0   | Antiblack smear. Goes low to increase the pixel well size during parallel transfer.                                                                                                                                |  |  |

| H2                          | 37              | 0   | Horizontal transfer 2. Horizontal charge transfer control for CCD.                                                                                                                                                 |  |  |

| IAG_XV3                     | 29              | 0   | Image-area gate/vertical transfer 3. Charge transfer control for CCD.                                                                                                                                              |  |  |

| RST_RG                      | 39              | 0   | Reset gate. Reset pulse for the CCD's charge-detection amplifier, generated for every pixel moved out of the CCD.                                                                                                  |  |  |

| SAG_XV1                     | 34              | 0   | Storage-area gate/vertical transfer 1. Charge transfer control for CCD.                                                                                                                                            |  |  |

| SRG_H1                      | 38              | 0   | Serial register gate/horizontal transfer 1. Horizontal charge transfer control for CCD.                                                                                                                            |  |  |

| XV2                         | 33              | 0   | Vertical transfer 2. Charge transfer control for CCD.                                                                                                                                                              |  |  |

|                             |                 |     | PHY Interface                                                                                                                                                                                                      |  |  |

| CTL1,<br>CTL0               | 55<br>56        | 1/0 | Control 1 and control 0 of the PHY-link control bus.                                                                                                                                                               |  |  |

| D[70]                       | 45-48,<br>50-53 | I/O | Data signals of the PHY-link data bus. Data is expected on D0-D1 at 100 Mbits/s, D0-D3 at 200 Mbits/s, and D0-D7 at 400 Mbits/s. D0 is the MSB.                                                                    |  |  |

| LREQ                        | 60              | I/O | Makes bus requests and accesses to the PHY.                                                                                                                                                                        |  |  |

| RESET                       | 62              | I   | Reset, active low. The asynchronous reset to the link controller.                                                                                                                                                  |  |  |

| SCLK                        | 58              | -   | System clock. SCLK is a 49.152-MHz clock supplied by the PHY.                                                                                                                                                      |  |  |

| EE                          |                 |     | EEPROM Interface                                                                                                                                                                                                   |  |  |

| EEPROM_CS                   | 66              | 0   | EEPROM chip select.                                                                                                                                                                                                |  |  |

| EEPROM_SCLK                 | 64              | 0   | EEPROM serial data clock.                                                                                                                                                                                          |  |  |

| EEPROM_SI                   | 65              | 0   | EEPROM serial data output.                                                                                                                                                                                         |  |  |

| EEPROM_SO                   | 68              | - 1 | EEPROM serial data input.                                                                                                                                                                                          |  |  |

| TERMINAL                |                                        | 1/0 |                                                                                                                                                                          |  |  |

|-------------------------|----------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                    | NAME NO.                               |     | DESCRIPTION                                                                                                                                                              |  |  |

|                         |                                        |     | Motor Control Interface                                                                                                                                                  |  |  |

| IR_SIG                  | 75                                     | I   | Position feedback from infrared detectors on motorized mechanisms. Applies to the stepper motor currently selected by the STATn terminals.                               |  |  |

| MOTOR_MINUS             | 73                                     | I   | Negative pushbutton input. Applies to the stepper motor currently selected by the STATn terminals.                                                                       |  |  |

| MOTOR_PLUS              | 74                                     | I   | Positive pushbutton input. Applies to the stepper motor currently selected by the STATn terminals.                                                                       |  |  |

| PHASE2_B                | 77                                     | 0   | Drive signal for stepper motors, phase 2, signal B. Applies to the stepper motor currently selected by the STATn terminals.                                              |  |  |

| PHASE2_A                | 78                                     | 0   | Drive signal for stepper motors, phase 2, signal A. Applies to the stepper motor currently selected by the STATn terminals.                                              |  |  |

| PHASE1_B                | 79                                     | 0   | Drive signal for stepper motors, phase 1, signal B. Applies to the stepper motor currently selected by the STATn terminals.                                              |  |  |

| PHASE1_A                | 80                                     | 0   | Drive signal for stepper motors, phase 1, signal A. Applies to the stepper motor currently selected by the STATn terminals.                                              |  |  |

|                         |                                        |     | Miscellaneous Interface                                                                                                                                                  |  |  |

| CAM_POWER               | 28                                     | 0   | Power switch. Toggles with bit in <i>CAMERA_POWER_CNTL</i> register, which is low upon device power up. Used to instruct system power supply to enter power saving mode. |  |  |

| EN                      | 72                                     | I   | Regulator enable. When low, the device supply power regulator is active. Should be kept low during normal operation.                                                     |  |  |

| GND                     | 7, 12,<br>21, 36,<br>44, 54,<br>61, 76 |     | Connect to ground.                                                                                                                                                       |  |  |

| NC                      | 5, 11                                  |     | No connect                                                                                                                                                               |  |  |

| PG1, PG2                | 59, 69                                 |     | No connect                                                                                                                                                               |  |  |

| STAT2<br>STAT1<br>STAT0 | 41<br>42<br>43                         | I/O | Status signals                                                                                                                                                           |  |  |

| TEST_SE_IN              | 20                                     | ı   | Factory test terminal. Connect to ground.                                                                                                                                |  |  |

| TESTMODE                | 63                                     | I   | Factory test terminal. Connect to ground.                                                                                                                                |  |  |

|                         |                                        |     | Power/Ground                                                                                                                                                             |  |  |

| VCC_CORE                | 30,70                                  |     | Connect to 3.3 V.                                                                                                                                                        |  |  |

| VCC                     | 1, 14,<br>27, 40,<br>49, 57,<br>67     |     | Connect to 3.3 V.                                                                                                                                                        |  |  |

| VDD_CAP                 | 31,71                                  |     | Mid-supply. Connect to ground through a 0.1-μF capacitor.                                                                                                                |  |  |

# 2 Detailed Description

# 2.1 1394 Interface

The 1394 interface is used to connect the camera to external devices using the IEEE 1394 serial bus. This bus is currently capable of speeds up to 400 Mbits/s and provides adequate bandwidth in which to transmit a quality uncompressed video signal. It is assumed that the reader has a moderate level of familiarity with the 1394 serial bus.

The TSB15LV01 serves as the application, transaction, and link layers of a 1394 node. This greatly simplifies implementation of the 1394 node, since only the physical layer remains to be implemented. This can be accomplished by placing a 1394 PHY, such as the TSB41LV01, between the TSB15LV01 and the 1394 connector. The 1394 interface on the TSB15LV01 provides a glueless interface to the PHY.

Note that while the device supports s400 1394 packets, the maximum bandwidth consumed by the device is 200 Mbits/s. This means that a TSB15LV01-based camera leaves at least 200 Mbits/s available to other functions, assuming all devices on the bus use s400 packets.

This section is not designed to be a tutorial on 1394. It is assumed that the reader has a basic knowledge of the 1394 serial bus. For more information on the 1394 bus, see the 1394 standard.

# 2.1.1 Isochronous Versus Asynchronous Protocols

There are two types of packets used in the 1394 link layer: isochronous and asynchronous. The TSB15LV01 uses *isochronous* packets to send video data to the bus and *asynchronous* packets to exchange control/status information with the bus.

An isochronous transaction delivers a consistent amount of data that is transferred at regular 125-µs intervals, with simplified addressing. Reception of an acknowledge packet is not required. Allocated flows of isochronous data are referred to as *channels*. Because the packets are assured to be delivered regularly, a constant data rate is achieved, making it ideal for video. In order to assure this bandwidth, a node must first request allocation of the bus resources from the node serving as the bus manager. The TSB15LV01 expects this to be performed by the node receiving the video data, referred to as the *host node*. The TSB15LV01 is capable of being an isochronous *talker*. However, it is not capable of listening to a channel of isochronous data. It is capable of transmitting isochronous data on channels 0 to 15 only.

An asynchronous transaction delivers a variable amount of data to a specific address. An acknowledge packet must be received from the designated target node, assuring delivery of the packet. This protocol allows packets to be sent without any prior permission or allocation. However, isochronous packets receive priority in order to maintain a consistent data rate. The TSB15LV01 is capable of sending and receiving asynchronous packets with a payload of up to 32 quadlets per packet. All request packets received by the device are answered with a response packet. If a request packet is received between a request and its corresponding response packet, the device acknowledges that packet with a *busy* acknowledge code.

# 2.1.2 Packet Format/Protocol

# 2.1.2.1 Isochronous Packet Format/Protocol

All video data sent from the camera is done so using isochronous communication. Before data can be sent, the node residing in the host must first request allocation of bus resources from the node serving as the bus manager. It must then configure the TSB15LV01's control and configuration registers. After the first CCD image integration cycle that follows completion of configuration, the camera will begin to send video data.

The full isochronous packet structure is shown in Table 2–1. This packet structure is defined by the 1394 standard.

Table 2-1. Isochronous Data Block Packet Format

| 0-7                                                            | 8–15                                             |       | 16-23   | 24-   | 31 |  |  |

|----------------------------------------------------------------|--------------------------------------------------|-------|---------|-------|----|--|--|

| data_l                                                         | data_length                                      |       | channel | tCode | sy |  |  |

|                                                                | heade                                            | er_Cl | RC      |       |    |  |  |

|                                                                | data payload quadlet 1<br>data payload quadlet 2 |       |         |       |    |  |  |

|                                                                | •                                                |       |         |       |    |  |  |

|                                                                | ·<br>·                                           |       |         |       |    |  |  |

| last quadlet of data payload (padded with zeroes if necessary) |                                                  |       |         |       |    |  |  |

|                                                                | data_CRC                                         |       |         |       |    |  |  |

The fields are defined as:

• data\_length The number of bytes in the data payload field

• tg The tag field is set to zero

• channel The isochronous channel number, as programmed in the ISO\_CHANNEL\_CNTL register

• tCode The transaction code. The code for an isochronous data block transaction is 1010b.

• **sy** Synchronization value. For the first isochronous packet of a frame, this is set to 0001b. For all other isochronous packets, this is set to zero.

• data payload Contains the digital video information

Isochronous data is formatted differently for each video transfer mode. Table 2–2 lists all supported transfer modes. For each mode, the table lists the total number of bits representing a single pixel. It also gives the data payload per packet for each mode, in terms of lines, pixels, and quadlets. The payload varies for each frame rate.

Every video component, Y, U, V, R, G, and B, has 8-bit data.

Table 2-2. Data Payload Per Isochronous Packet

| MODE   | VIDEO FORMAT         | FRAME RATE (Frame per Second) |                  |       |       |

|--------|----------------------|-------------------------------|------------------|-------|-------|

| MODE   | VIDEO FORMAT         | 30                            | 15               | 7.5   | 3.75  |

| Mode_0 | 160 x 120 YUV(4:4:4) | 1/2 L                         | 1/4 L            | 1/8 L |       |

|        | 24 bits/pixel        | 80 P                          | 40 P             | 20 P  |       |

|        |                      | 60 Q                          | 30 Q             | 15 Q  |       |

| Mode_1 | 320 x 240 YUV(4:2:2) | 1 L                           | 1/2 L            | 1/4 L | 1/8 L |

|        | 16 bits/pixel        | 320 P                         | 160 P            | 80 P  | 40 P  |

|        |                      | 160 Q                         | 80 Q             | 40 Q  | 20 Q  |

| Mode_2 | 640 x 480 YUV(4:1:1) | 2 L†                          | 1 L              | 1/2 L | 1/4 L |

|        | 12 bits/pixel        | 1280 P                        | 640 P            | 320 P | 160 P |

|        |                      | 480 Q                         | 240 Q            | 120 Q | 60 Q  |

| Mode_3 | 640 x 480 YUV(4:2:2) |                               | 1 L <sup>†</sup> | 1/2 L | 1/4 L |

|        | 16 bits/pixel        |                               | 640 P            | 320 P | 160 P |

|        |                      |                               | 320 Q            | 160 Q | 80 Q  |

| Mode_4 | 640 x 480 RGB        |                               | 1 L <sup>†</sup> | 1/2 L | 1/4 L |

|        | 24 bits/pixel        |                               | 640 P            | 320P  | 160P  |

|        |                      |                               | 480 Q            | 240Q  | 120Q  |

| Mode_5 | 640 x 480 Y (Mono)   | 2 L†                          | 1 L              | 1/2 L | 1/4 L |

|        | 8 bits/pixel         | 1280P                         | 640 P            | 320 P | 160 P |

|        |                      | 320 Q                         | 160 Q            | 80 Q  | 40 Q  |

TRequires s200 or faster packet speed, as programmed in the ISO\_CHANNEL/SPEED\_CNTL register. The others can use s100 as well.

Key: L: Lines/packet

P: Pixel/packet

Q: Quadlet/packet

# 2.1.2.2 Isochronous Video Payload

Each transfer mode requires a different data format structure, each defining how the pixels are combined to build 32-bit quadlets. Table 2–3 shows the payload structure for each mode, with the quadlets broken down into individual bytes. This data payload structure is slightly different for every video mode. In the table, *N* is the number of pixels/packet, as shown in Table 2–2.

Table 2-3. Video Data Payload Structure

| 0–7                                  | 0-7 8-15 16-23 24-31    |                         |                         |  |  |

|--------------------------------------|-------------------------|-------------------------|-------------------------|--|--|

| YUV (4:4:4) forma                    |                         | 10-23                   | 24-31                   |  |  |

| U <sub>0</sub>                       | Y 0                     | <b>v</b> <sub>0</sub>   | U <sub>1</sub>          |  |  |

| Y <sub>1</sub>                       | V <sub>1</sub>          | <b>U</b> <sub>2</sub>   | Y <sub>2</sub>          |  |  |

|                                      |                         |                         |                         |  |  |

| V 2                                  | U <sub>3</sub>          | Y 3                     | V <sub>3</sub>          |  |  |

|                                      |                         |                         |                         |  |  |

|                                      |                         |                         |                         |  |  |

| U <sub>N-4</sub>                     | Y <sub>N-4</sub>        | V <sub>N-4</sub>        | U <sub>N-3</sub>        |  |  |

| Y <sub>N-3</sub>                     | <b>v</b> <sub>N-3</sub> | U <sub>N-2</sub>        | Y <sub>N-2</sub>        |  |  |

| <b>v</b> <sub>N-2</sub>              | U <sub>N-1</sub>        | Y <sub>N-1</sub>        | <b>v</b> <sub>N-1</sub> |  |  |

|                                      | t (Mode_1, Mode_3)      |                         | -                       |  |  |

| U <sub>0</sub>                       | Y <sub>0</sub>          | v <sub>0</sub>          | Y 1                     |  |  |

| U <sub>2</sub>                       | Y 2                     | V <sub>2</sub>          | Y 3                     |  |  |

| U <sub>4</sub>                       | Y 4                     | V <sub>4</sub>          | Y <sub>5</sub>          |  |  |

| - 4                                  |                         | · ·                     | . · · ·                 |  |  |

|                                      |                         |                         |                         |  |  |

| •                                    |                         |                         |                         |  |  |

| U <sub>N-6</sub>                     | Y <sub>N-6</sub>        | <b>v</b> <sub>N-6</sub> | Y <sub>N-5</sub>        |  |  |

| U <sub>N-4</sub>                     | Y <sub>N-4</sub>        | v <sub>N-4</sub>        | Y <sub>N-3</sub>        |  |  |

| U <sub>N-2</sub>                     | Y <sub>N-2</sub>        | <b>v</b> <sub>N-2</sub> | Y <sub>N-1</sub>        |  |  |

| YUV (4:1:1) forma                    | t (Mode_2)              |                         |                         |  |  |

| <b>U</b> 0                           | <b>Y</b> 0              | Y 1                     | <b>v</b> <sub>0</sub>   |  |  |

| Y 2                                  | Y 3                     | U 4                     | Y 4                     |  |  |

| Y 5                                  | V 4                     | Υ <sub>6</sub>          | Y 7                     |  |  |

|                                      |                         |                         |                         |  |  |

|                                      |                         |                         |                         |  |  |

| •                                    |                         |                         |                         |  |  |

| U <sub>N-8</sub>                     | Y <sub>N-8</sub>        | Y <sub>N-7</sub>        | V <sub>N-8</sub>        |  |  |

| Y <sub>N-6</sub>                     | Y <sub>N-5</sub>        | U <sub>N-4</sub>        | Y N-4                   |  |  |

| Y <sub>N-3</sub>                     | V <sub>N-4</sub>        | Y <sub>N-2</sub>        | Y <sub>N-1</sub>        |  |  |

| RGB format (Mode                     |                         | T                       | I                       |  |  |

| <b>R</b> 0                           | <b>G</b> <sub>0</sub>   | В 0                     | R <sub>1</sub>          |  |  |

| G <sub>1</sub>                       | B <sub>1</sub>          | <b>R</b> <sub>2</sub>   | <b>G</b> <sub>2</sub>   |  |  |

| <b>B</b> <sub>2</sub>                | <b>R</b> 3              | <b>G</b> 3              | <b>B</b> <sub>3</sub>   |  |  |

|                                      |                         |                         |                         |  |  |

|                                      | •                       | •                       | •                       |  |  |

| R <sub>N-4</sub>                     | G <sub>N-4</sub>        | В <sub>N-4</sub>        | R <sub>N-3</sub>        |  |  |

|                                      | B <sub>N-2</sub>        | R <sub>N-2</sub>        | G N-2                   |  |  |

| G <sub>N-3</sub><br>B <sub>N-2</sub> | R <sub>N-1</sub>        |                         |                         |  |  |

| <b>□</b> N-2                         | IV [N-]                 | <b>G</b> <sub>N-1</sub> | B <sub>N-1</sub>        |  |  |

Table 2–3. Video Data Payload Structure (Continued)

| 0-7                      | 8 –15                   | 16–23            | 24-31            |  |  |

|--------------------------|-------------------------|------------------|------------------|--|--|

| Y (Mono) format (Mode_5) |                         |                  |                  |  |  |

| Υ 0                      | Y 1                     | U <sub>2</sub>   | <b>Y</b> 3       |  |  |

| Y 4                      | <b>v</b> <sub>5</sub>   | Y <sub>6</sub>   | <b>Y</b> 7       |  |  |

|                          |                         |                  |                  |  |  |

|                          | •                       |                  |                  |  |  |

| •                        |                         |                  |                  |  |  |

| Y <sub>N-8</sub>         | Y <sub>N-7</sub>        | <b>U</b> N-6     | Y <sub>N-5</sub> |  |  |

| Y <sub>N-4</sub>         | <b>v</b> <sub>N-3</sub> | Y <sub>N-2</sub> | Y <sub>N-1</sub> |  |  |

Table 2–4 shows the data structure for Y, R, G, and B video data components. All components are unsigned 8-bit values.

Table 2-4. Data Structure for Y, R, G, and B Data Components

|         | SIGNAL LEVEL (Decimal) | DATA (Hexadecimal) |

|---------|------------------------|--------------------|

| Highest | 255                    | 0xFF               |

|         | 254                    | 0xFE               |

|         | :                      | :                  |

|         | 1                      | 0x01               |

| Lowest  | 0                      | 0x00               |

Table 2–5 shows the data structure for U and V video data components. Both components are signed 8-bit values.

Table 2-5. Data Structure for U and V Data Components

|            | SIGNAL LEVEL (Decimal) | DATA (Hexadecimal) |

|------------|------------------------|--------------------|

| Highest(+) | 127                    | 0xFF               |

|            | 126                    | 0xFE               |

|            | :                      | :                  |

|            | 1                      | 0x81               |

| Lowest     | 0                      | 0x80               |

|            | -1                     | 0x7F               |

|            | :                      | :                  |

|            | -127                   | 0x01               |

| Highest(-) | -128                   | 0x00               |

# 2.1.2.3 Asynchronous Packet Format/Protocol

Asynchronous packets are used to read status information from the TSB15LV01 and write control information to it. These packets are formatted as defined by the 1394 standard. All reads and writes should correlate with the memory maps as shown in section 3, Address Space.

Asynchronous reads and writes can be performed either as quadlets or as blocks. Blocks can be read in sizes of up to 32 quadlets per packet. The structure of a quadlet write request packet is shown in Table 2–6, while the structure of a block write request packet is shown in Table 2–7.

Table 2-6. Asynchronous Quadlet Write Request Packet Format

| 0-7          | 8–15        | 16-23     |    | 24-                | 31  |  |  |

|--------------|-------------|-----------|----|--------------------|-----|--|--|

| destina      | ation_ID    | tl        | rt | tCode              | pri |  |  |

| sour         | source_ID   |           |    | destination_offset |     |  |  |

|              | destination | on_offset |    |                    |     |  |  |

| quadlet data |             |           |    |                    |     |  |  |

| header_CRC   |             |           |    |                    |     |  |  |

The fields are defined as:

- destination ID 10-bit busID concatenated with 6-bit nodeID

- **tl** Transaction label, specified by the host that identifies this transaction. This optional value is returned in the response packet.

- rt Retry code. Indicates whether this packet is an attempted retry and defines retry protocol.

- tCode Transaction code. The code for an asynchronous write request for quadlet data is 0000b.

- pri Not used.

- source ID Identifies host node by specifying its bus and physical ID

- destination offset Address location within TSB15LV01 address space

- quadlet\_data Contains the value being written to the addressed location

- header CRC CRC value for the header

Table 2–7. Asynchronous Block Write Request Packet Format

| 0-7                          | 8–15           | 16-23  |       | 16-23      |     | 24- | 31 |

|------------------------------|----------------|--------|-------|------------|-----|-----|----|

| destina                      | destination_ID |        |       | tCode      | pri |     |    |

| source_ID destination_offset |                |        |       |            |     |     |    |

| destination_offset           |                |        |       |            |     |     |    |

| data_                        | length         | extend | ded_t | tcode (000 | 0)  |     |    |

|                              | header         | _CRC   |       |            |     |     |    |

|                              | data I         | olock  |       |            |     |     |    |

|                              |                |        |       |            |     |     |    |

| ·                            |                |        |       |            |     |     |    |

| last quadlet of data block   |                |        |       |            |     |     |    |

The fields are defined as:

- **destination ID** 10 bit busID concatenated with 6-bit nodeID.

- tl Transaction label, specified by the host that identifies this transaction. This optional value is returned in the response packet.

- rt Retry code. Indicates whether this packet is an attempted retry and defines retry protocol.

- tCode Transaction code. The code for an asynchronous write request for block data is 0001b.

- pri Not used.

- source\_ID Identifies host node by specifying its bus and physical ID

- destination offset Address location within TSB15LV01 address space

- data length Specifies the amount of data being sent in the data field. Maximum size is 128 bytes.

- extended\_tcode Reserved during write request packets

- header CRC CRC value for the header

- data\_field Contains the value being written to the addressed location

- data CRC CRC value for the data field

The structure of a quadlet read request packet is shown in Table 2–8, while the structure of a block read request packet is shown in Table 2–9.

Table 2-8. Asynchronous Quadlet Read Request Packet Format

| 0-7                | 8-15     | 16-23              |    | 24-   | ·31 |  |

|--------------------|----------|--------------------|----|-------|-----|--|

| destina            | ation_ID | tl                 | rt | tCode | pri |  |

| sour               | ce_ID    | destination_offset |    |       |     |  |

| destination_offset |          |                    |    |       |     |  |

| header_CRC         |          |                    |    |       |     |  |

The fields are defined as:

- destination\_ID 10-bit busID concatenated with 6-bit nodeID

- tl Transaction label is specified by the host that identifies this transaction. This optional value is returned in the response packet.

- rt Retry code. Indicates whether this packet is an attempted retry and defines retry protocol.

- tCode Transaction code. The code for an asynchronous read request for quadlet data is 0100b.

- pri Not used.

- source ID Identifies host node by specifying its bus and physical ID

- destination\_offset Address location within TSB15LV01 address space

- header\_CRC CRC value for the header

Table 2-9. Asynchronous Block Read Request Packet Format

| 0-7                                | 8-15     | 16-23 |    | 24-   | 31  |

|------------------------------------|----------|-------|----|-------|-----|

| destina                            | ation_ID | tl    | rt | tCode | pri |

| source_ID destination_offset       |          |       |    |       |     |

| destination_offset                 |          |       |    |       |     |

| data_length extended_tcode (0000h) |          |       |    | )h)   |     |

| header_CRC                         |          |       |    |       |     |

The fields are defined as:

- destination\_ID 10-bit busID concatenated with 6-bit nodeID.

- tl Transaction label is specified by the host that identifies this transaction. This value is reflected in the

response packet that corresponds to this request packet.

- rt. Retry code. Indicates whether this packet is an attempted retry and defines retry protocol.

- tCode Transaction code. The code for an asynchronous read request for block data is 0101b.

- pri Not used

- source\_ID Identifies host node by specifying its bus and physical ID

- destination\_offset Address location within TSB15LV01 address space

- data\_length Specifies the amount of data being sent in the data field. Maximum size is 128 bytes.

- extended\_transaction\_code Reserved during write request packets

- header\_CRC CRC value for the header

#### 2.1.3 1394 Serial Bus Management Capabilities

Nodes on the 1394 bus may be called on to serve in a number of bus management roles following a bus reset event. The TSB15LV01 is not designed to serve as the isochronous resource manager, a full bus manager, or the cycle master. The contents of the configuration ROM should reflect this level of capability.

#### 2.1.4 PHY/Link Interface

The PHY/link interface consists of the signals that connect the TSB15LV01, which serves as the link layer of the 1394 node, to a physical layer device, or PHY. This interface carries all data, control, and status information that is transferred between the two layers.

To take full advantage of the TSB15LV01's capabilities, a 400-Mbits/s PHY device should be used, such as TI's TSB41LV01.

# 2.1.4.1 Principles of Operation

The TSB15LV01 PHY/link interface consists of the SCLK, CTL0-CTL1, D0-D7, LREQ, and RESET terminals. The PHY's SYSCLK terminal provides a 49.152-MHz interface clock to the TSB15LV01's SCLK terminal. All control and data signals are synchronized to, and sampled on, the rising edge of SYSCLK.

The CTL0 and CTL1 terminals form a bidirectional control bus, which controls the flow of information and data between the PHY and TSB15LV01.

The D0-D7 terminals form a bidirectional data bus, which is used to transfer status information, control information, or packet data between the devices. In s100 operation only the D0 and D1 terminals are used; in s200 operation only the D0-D3 terminals are used; and in s400 operation all D0-D7 terminals are used for data transfer. When the PHY is in control of the D0-D7 bus, unused Dn terminals are driven low during s100 and s200 operations. When the TSB15LV01 is in control of the D0-D7 bus, unused Dn terminals are ignored by the PHY.

The LREQ terminal is used by the TSB15LV01 to send serial service requests to the PHY in order to request access to the serial-bus for packet transmission.

The PHY normally controls the CTL0-CTL1 and D0-D7 bidirectional buses. The TSB15LV01 is allowed to drive these buses only after it has been granted permission to do so by the PHY. There are three operations that may occur on the PHY-link interface: link service request, data transmit, and data receive. The TSB15LV01 issues a service request when it wants to request the PHY to gain control of the 1394 serial bus in order to transmit a packet.

The PHY may initiate a status transfer autonomously. The PHY initiates a receive operation whenever a packet is received from the 1394 serial bus. The PHY initiates a transmit operation after winning control of the serial bus following a bus request by the TSB15LV01. The transmit operation is initiated when the PHY grants control of the interface to the TSB15LV01.

For details on how the PHY/link interface operates, consult the 1394 specification.

#### 2.1.5 Enabling the Transmission of Video

# 2.1.5.1 Enabling Isochronous Video Streaming

To enable the streaming of isochronous video data, the function control registers must be configured properly, as described in section 3.3.3.1.2. The last register to be written should be the *CAMERA\_POWER\_CNTL* register, which asserts the CAM\_POWER terminal (activating the CCD circuitry, if the signal is utilized), begins processing data from the AFE interface, and begins transmitting isochronous data.

# 2.1.5.2 Enabling One-Shot Video Transmission

Alternatively to transmitting an isochronous stream of video data, the one-shot feature can be utilized. With this feature, a single frame is sent using the same isochronous packet structure. It is activated by asserting the *one\_shot* field of the *ONE\_SHOT\_CNTL* register. Note that in order to use this feature, isochronous video streaming should be disabled via the *ISO\_EN\_CNTL* register.

When the feature is activated, the device automatically powers up the camera, activates isochronous transmission, sends a single image, then deactivates isochronous data and powers down the camera.

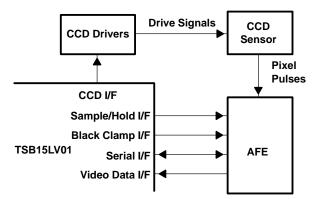

# 2.2 Sensor Interface

The TSB15LV01 obtains its raw video data from a charge-coupled device (CCD) sensor. This information is sent to an analog front end (AFE) that amplifies the analog video information provided by the CCD, performs correlated double sampling (CDS) and gain, and converts it to a digital format recognizable by the TSB15LV01.

Figure 2-1 shows the top-level signal flow in the sensor interface.

Figure 2-1. Top-Level Sensor Interface Signal Flow

#### 2.2.1 CCD Interface

## 2.2.1.1 General Description

The video data is sourced by a CCD sensor. The TSB15LV01 contains a CCD timing generator for the approved sensors. Some of these signals must pass through a driver circuit to undergo voltage shifting.

Because the timing of the CCD interface is closely integrated with the timing of the analog front end, this topic is discussed jointly in section 2.2.3, *CCD/AFE Timing*.

# 2.2.1.2 Configuring for Different CCD Sensors

The TSB15LV01 is designed to be used with several different CCD sensors and contains the necessary logic to drive each of them. The *ccd\_sel* field of the *AFE\_SETUP\_CNFG* register must be set to the correct value, identified in section 3.3.3.2, Configuration Registers. If this field selects the TC237 CCD, field *color\_bw* of *VIDEO\_OPTIONS\_CNFG* register must also be set to *black and white*, since this is a black and white sensor. Otherwise, it should be set to *color*.

#### 2.2.1.3 External Pulse Drivers

As with nearly all CCD applications, the TSB15LV01 requires use of a dedicated driver chip for the vertical drive pulses. This device performs level-shifting to high-voltage rails, as well as some logic functions. Table 2–10 shows the approved sensors with their recommended driver devices.

Table 2–10. Approved CCD Sensors and Recommended Drivers

| SENSOR                               | DRIVER                           |

|--------------------------------------|----------------------------------|

| Sony ICX084AK 1/3" color sensor      | Sony CXD1267AN                   |

| Sony ICX098AK 1/4" color sensor      | Sony CXD1267AN                   |

| Sharp LZ24BP 1/4" color sensor       | Sony CXD1267AN or Sharp LR36685N |

| TI TC237 1/3" black and white sensor | TI TMC57253                      |

In addition, an external driver for horizontal pulses is required in order to drive the capacitive load of the CCD sensor. A CMOS inverter device is recommended, such as the TI SN74LVCU04A.

# 2.2.2 Analog Front End Interface

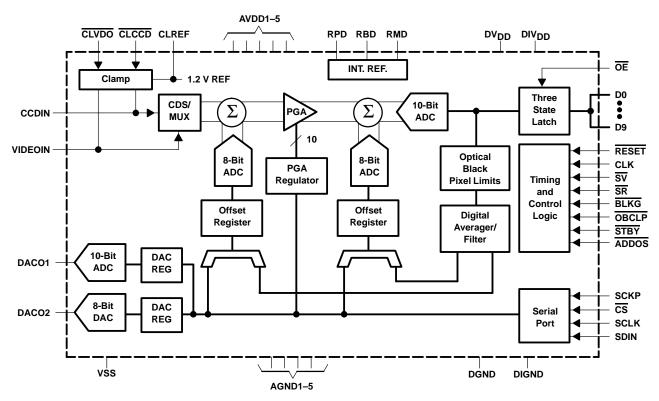

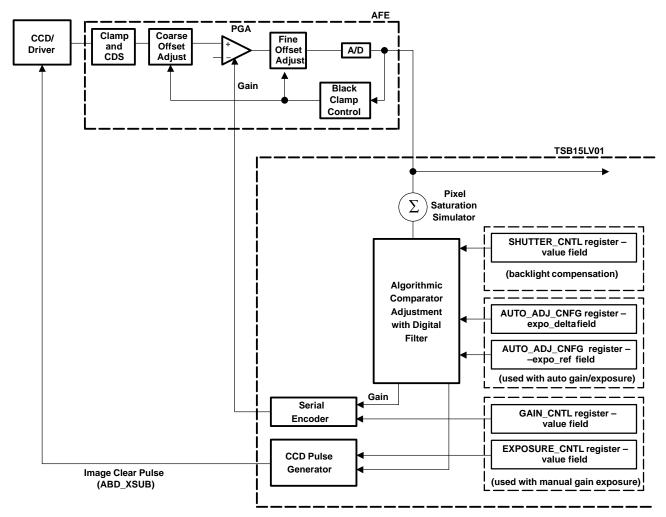

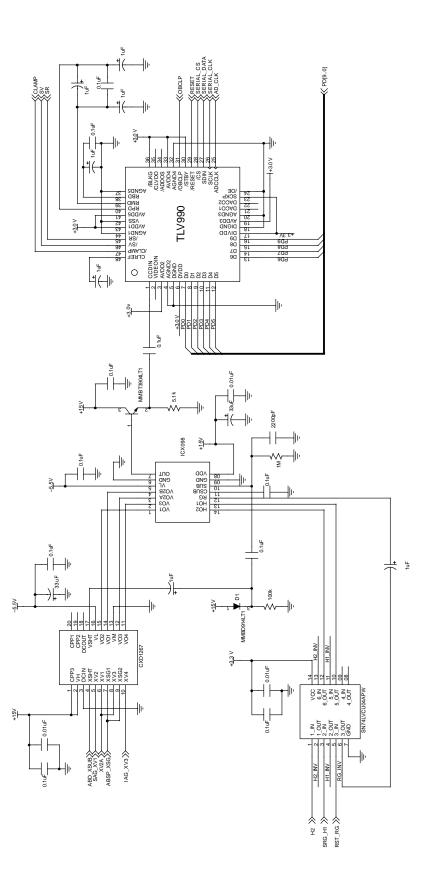

Circuitry must be used in a TSB15LV01-based system that processes the pixel pulses received from the CCD and converts them to digital data readable by the TSB15LV01. This circuit is referred to as the analog front end (AFE). The TSB15LV01 is designed to be used with the TLV990 AFE device.

## 2.2.2.1 AFE Function

Figure 2-2 shows the block diagram of the TLV990.

Figure 2-2. TLV990 Block Diagram

At the beginning of each image line, the AFE resets the dc bias of the incoming video data. It then performs correlated double sampling (CDS), which effectively extracts the video data from the pixel pulse and removes the most significant forms of noise. It then enters a programmable gain array (PGA) prior to conversion to digital form via a 10-bit analog/digital converter (ADC).

Before and after the PGA are offset correction circuits that maximize dynamic range of the video signal. The one prior to the PGA is considered the *coarse* adjustment offset, while the one after the PGA is considered the *fine* adjustment offset. These offset values are based either on the internal black clamping process or on values received from the TSB15LV01 via the serial interface, depending on the brightness mode. Digital/analog converters (DACs) in the AFE circuitry decode these values and apply them to the video signal flow. The TLV990 also contains a number of other registers that control operation of the device, which the TSB15LV01 is able to program.

The TSB15LV01 contains an interface to the AFE that is divided into four sections. The first is the sample/hold interface, which provides the timing signals necessary for sampling of the pixel pulses. The second is the black clamping interface. The third is the serial interface, which programs control values into the AFE. The fourth is the video data interface, which is a 10-bit parallel port that receives the video from the ADC after it has been converted.

## 2.2.2.2 Sample/Hold Interface

This interface provides the signals necessary for dc bias clamping and correlated double sampling (CDS) of the CCD pixel pulse.

The AFE should be capacitively coupled to the CCD output signal. At the beginning of each image line, the AFE must clamp this signal to a reference voltage, thereby properly setting the dc bias of the incoming video data. To accomplish this, the TSB15LV01 sends the CLAMP terminal low. This occurs during the CCD's dummy pixel output, prior to the active data pixels. CLAMP is held low only for a few pixels, but due to very low leakage current from this node, the clamped bias holds for the duration of the line.

During the active pixels portion of the line, reset pedestal and video data pedestal of the pixel pulses are sampled. The data pedestal is subtracted from the reset pedestal prior to amplification. The SR signal supplies the sampling pulse for the reset pedestal, while SV supplies the sampling pulse for the video data pedestal.

# 2.2.2.3 Black Clamping Interface

The dc offset is directly related to the brightness of the image. The dc offset can be controlled automatically or manually. When the TSB15LV01 is configured for autobrightness, it utilizes the black clamping feature of the TLV990.

In autobrightness mode, the AFE uses an internal feedback loop to adjust the offset. It adjusts the black pixels until they match a digital value received from the TSB15LV01 via the serial interface. When the TSB15LV01 sends the OBCLP terminal low, the AFE begins to acquire the digital pixel values produced by the ADC, average them, and compare them to the black reference value. If the values are not equal, the AFE attempts to make them equal by altering the *fine* adjustment offset value, which changes the offset that is summed with the signal prior to the ADC. If the necessary adjustment is out of range for the fine offset, the AFE can use the *coarse* adjustment. The adjustments are applied until the pixel data equals the black reference value.

The TSB15LV01 sends the OBCLP pulse during a time in which it knows the selected CCD is sending its *black* pixels. The number of lines per image and the number of pixels per line that should be sampled are stored in internal registers, programmed by the TSB15LV01 from the *lines\_smpl* and *pix\_smpl* fields, respectively, of the *VIDEO OPTIONS CNFG* register.

See section 2.6.6, *Brightness*, for more information on dc offset control.

#### 2.2.2.4 Serial Interface

The TLV990 contains several control registers. The serial interface of the TSB15LV01 provides a means of programming these values. Table 2–11 shows the values that are transmitted from the TSB15LV01 to the TLV990.

Table 2-11. Values Transmitted to AFE via Serial Interface

| Source Within the TSB15LV01                      | TLV990 Target Register             | Covered in Section       |

|--------------------------------------------------|------------------------------------|--------------------------|

| Gain/exposure control loop (auto mode)           |                                    |                          |

| GAIN_CNTL register (manual mode)                 | PGA register                       | 2.6.8, Gain and Exposure |

| Blooming_value field of DAC_OFFSET_CNFG register | User DAC1 register                 | 2.6.7, Anti-Blooming     |

| Brightness control loop (auto mode)              |                                    |                          |

| BRIGHTNESS_CNTL register (manual mode)           | Coarse dc offset DAC register      |                          |

| Brightness control loop (auto mode)              |                                    |                          |

| BRIGHTNESS_CNTL register (manual mode)           | Fine dc offset DAC register        | 2.6.6, Brightness        |

| Offset_level field of DAC_OFFSET_CNFG register   | Optical black level register       |                          |

| Lines_smpl field of AFE_SETUP_CNFG register      |                                    |                          |

| pixels_smpl field of AFE_SETUP_CNFG register     | Optical black calibration register |                          |

Gain and offset (brightness) sources depend on whether the respective modes are manual or automatic.

The *lines\_smpl* and *pix\_smpl* fields of *AFE\_SETUP\_CNFG* register control the lines per image, and pixels per line, respectively, that are to be averaged (see section 2.2.2.3, *Black Clamping Interface*, for more information). The *offset\_level* field of the *DAC\_OFFSET\_CNFG* register is the digital black reference value to which the dc offset is normalized.

The TLV990 contains two general purpose DACs with external outputs. One of these, DAC1, can be used to convert a digital code (sourced from the TSB15LV01's *DAC\_OFFSET\_CNFG* register) to an analog signal, which can be routed to the sensor for use in antiblooming. The second DAC, DAC2, is generally not utilized, but can be controlled from the TSB15LV01 as well.

See the TLV990 data sheet (literature number SLAS298) for more information about the target registers.

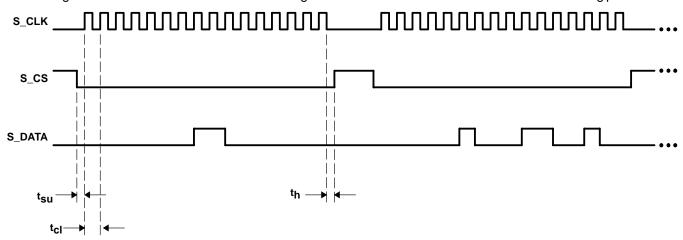

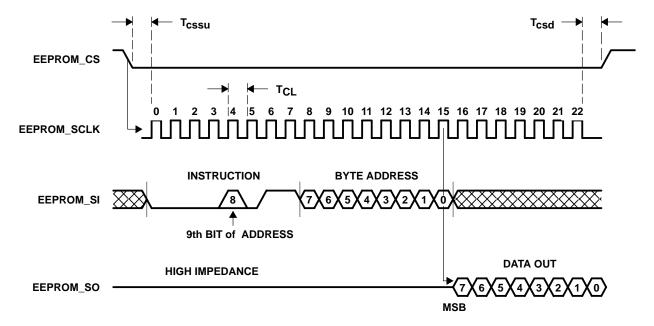

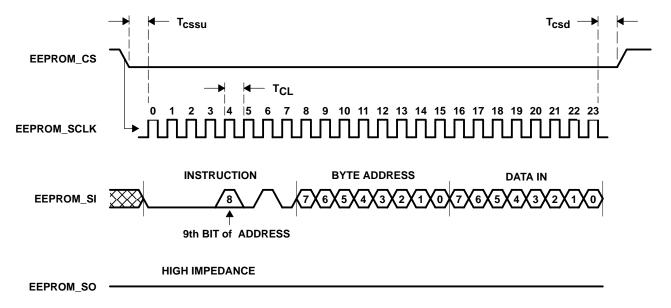

The timing of the AFE serial interface is shown in Figure 2–3. Table 2–12 shows the AFE interface timing parameters.

Figure 2–3. AFE Serial Interface Timing

Table 2-12. AFE Interface Timing Parameters

|                 | MIN | TYP | MAX | UNIT |

|-----------------|-----|-----|-----|------|

| t <sub>su</sub> |     | 82  |     | ns   |

| t <sub>Cl</sub> |     | 164 |     | ns   |

| th              |     | 82  |     | ns   |

In Figure 2-3, two words are being written by the TSB15LV01 to the AFE. Each word represents a value being written to an AFE register address. The number of values written depends on the mode. For example, if autoexposure is being used, different parameters are being programmed to the AFE than if the mode is manual.

#### 2.2.2.5 Video Data Interface

A 10-bit parallel interface is used to move the video data from the AFE ADC to the TSB15LV01. Data is clocked in with ADCLK.

# 2.2.3 CCD/AFE Timing

# 2.2.3.1 General Description

The timing of these interfaces takes into consideration two asynchronous, periodic events. The first event is the integration of light in the sensor, which occurs at a frequency dictated by the camera's frame rate. The second event is the beginning of a 1394 isochronous cycle, which determines when video data is transmitted from the TSB15LV01. The TSB15LV01 reconciles these two events in a way that produces optimal video quality while minimizing the amount of memory necessary to store the pixel data.

When the integration cycle is complete, the pixel charges are transferred out of the active region of the sensor. For the TC237, which is a full frame transfer CCD, this is the parallel transfer of charge from the image area to the storage area. For the other sensors, which are interline CCDs, this is the transfer of charge to the vertical shift registers. Several dummy/black lines are subsequently clocked and processed by the AFE.

At this point, timing waits for the next 1394 isochronous cycle. As data is clocked out onto the serial bus, more data is needed and therefore clocked out of the sensor and into the TSB15LV01. This method of processing reconciles the two asynchronous, periodic events. It also minimizes the size of the internal FIFO needed to buffer the data stream, since data is only taken from the CCD as it is needed.

The data is packetized on the bus such that there is a period of time between frames in which no data remains to be clocked out of the sensor, and no data is being transferred on the serial bus. During such periods of inactivity, the TSB15LV01 may clock pixels out of the serial register while ignoring the resulting processed data from the AFE. This results in lines of blank dummy pixels being clocked out of the CCD at regular intervals. This action is taken because extended idle periods can allow the CCD serial register to accumulate dark current. Clocking these pixels also keeps a constant dc level at the AFE ac-coupling capacitor.

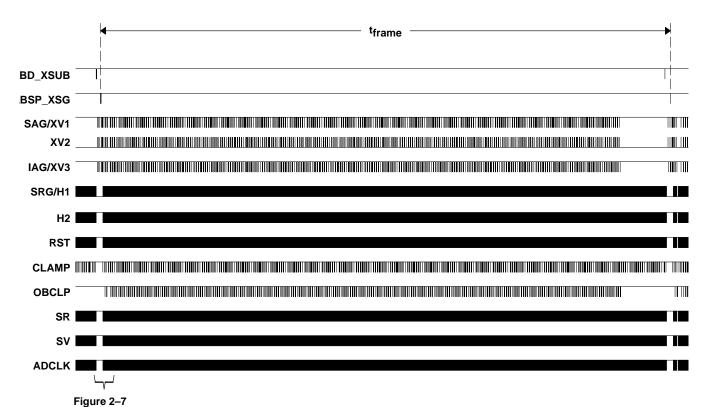

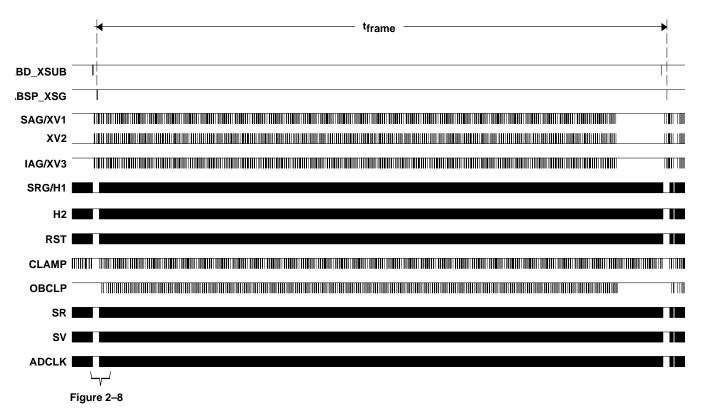

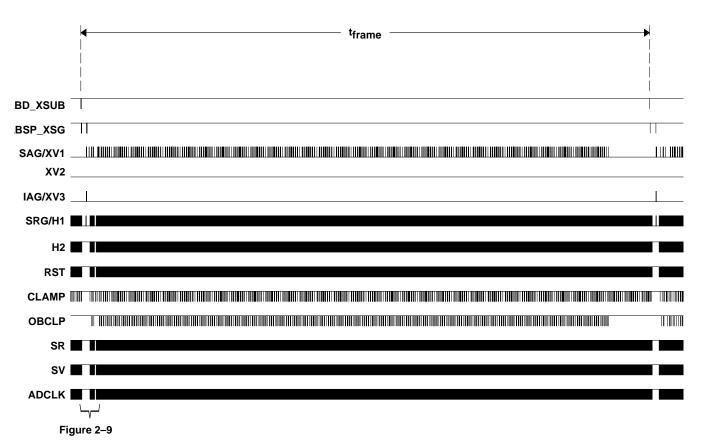

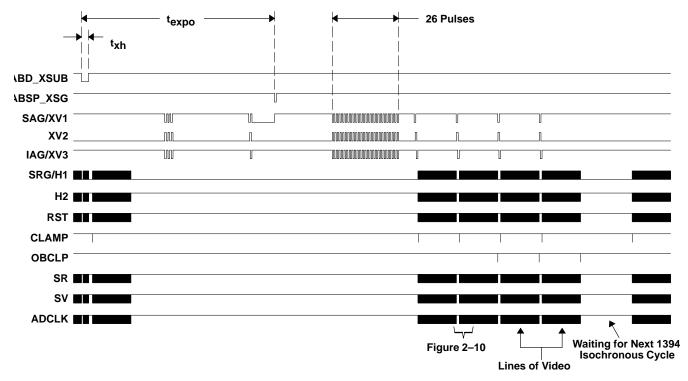

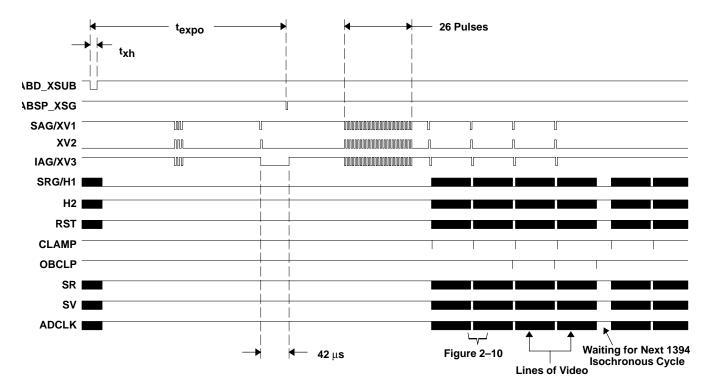

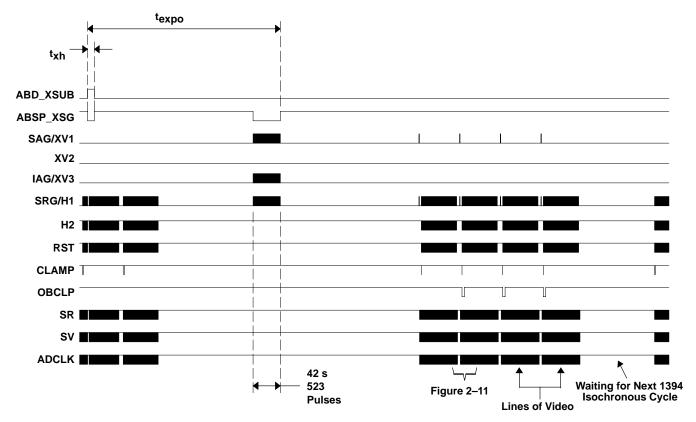

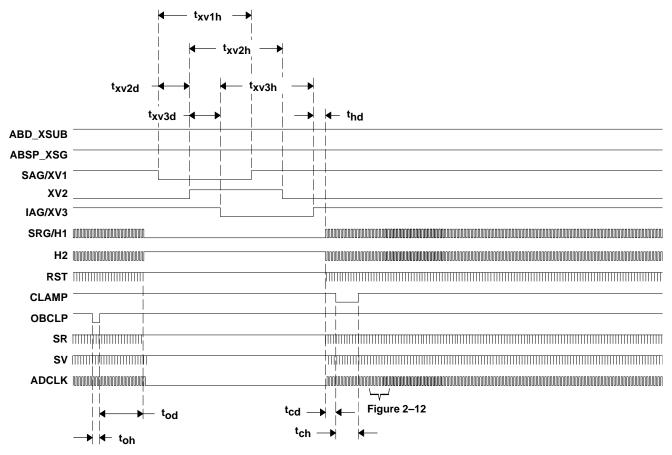

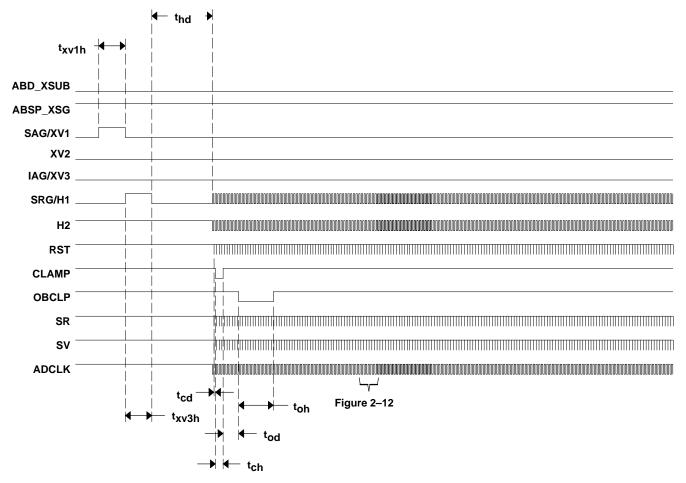

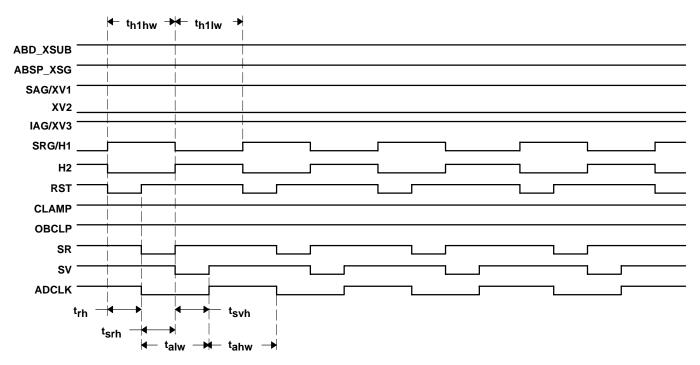

Figures 2-4 through 2-12 show the sensor interface for each approved sensor. For each sensor, there are four views shown. The first view contains the timing for the acquisition and transfer of a full frame of video. The second view is a magnified portion of the start frame. The third view is a magnified portion of the start of a line, while the fourth view is a magnified portion of the horizontal drive pulses. In some cases, the pulses are identical for the different sensor options, so they are consolidated under a single figure. In all figures, the mode is YUV 4:1:1 640 x 480, at 30 frames per second, with minimum exposure time.

Note that these signals are intended to be processed by one of the recommended driver devices before reaching the CCD. In addition to level-shifting, these devices perform logic on the signals. Therefore, the signals at the sensor are different than the ones shown in Figures 2-4 through 2-12.

Figure 2–4. Sensor Interface Timing for ICX098/LZ24BP Sensor, Full Frame Table 2–13. ICX098/LZ24BP Full Frame Timing Parameters

|                    |                                     | MIN | TYP  | MAX | UNIT |

|--------------------|-------------------------------------|-----|------|-----|------|

| <sup>t</sup> frame | Frame period (@ 30 frames per sec.) |     | 33.3 |     | ms   |

Figure 2–5. Sensor Interface Timing for ICX084 Sensor, Full Frame Table 2–14. ICX084 Full Frame Timing Parameters

|                    |                                       | MIN | TYP  | MAX | UNIT |

|--------------------|---------------------------------------|-----|------|-----|------|

| t <sub>frame</sub> | Frame period (@ 30 frames per second) |     | 33.3 |     | ms   |

Figure 2–6. Sensor Interface Timing for TC237 Sensor, Full Frame Table 2–15. TC237 Full Frame Timing Parameters

|                    |                                       | MIN | TYP  | MAX | UNIT |

|--------------------|---------------------------------------|-----|------|-----|------|

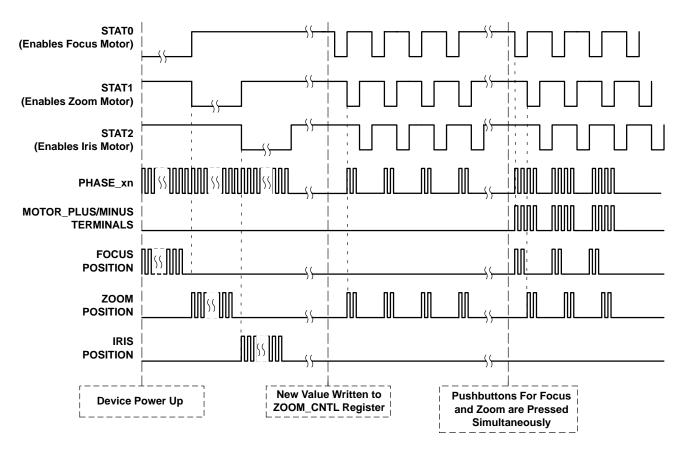

| t <sub>frame</sub> | Frame period (@ 30 frames per second) |     | 33.3 |     | ms   |