# TSB12C01A Data Manual

# IEEE 1394-1995 High-Speed Serial-Bus Link-Layer Controller

SLLS219B November 1998

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

# **Contents**

| Pa | ge |

|----|----|

|    |    |

| Se | ction                           | Title                                                                                                                                                                                                                                                          | Page                                                                              |

|----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1  | Ove<br>1.1<br>1.2<br>1.3<br>1.4 | Description .<br>Features .<br>1.2.1 Link .<br>1.2.2 Physical-Link Interface .<br>1.2.3 Host Bus Interface .<br>1.2.4 General .<br>Terminal Assignments .                                                                                                      | 1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-2                                     |

| 2  | <b>Arch</b> 2.1                 | 2.1.1       Physical Interface         2.1.2       Transmitter         2.1.3       Receiver         2.1.4       Transmit and Receive FIFOs         2.1.5       Cycle Timer         2.1.6       Cycle Monitor         2.1.7       Cyclic Redundancy Check (CRC) | 2–1<br>2–1<br>2–2<br>2–2<br>2–2<br>2–3<br>2–3<br>2–3                              |

| 3  | <b>Inter</b><br>3.1<br>3.2      | Internal Register Definitions         3.2.1 Version/Revision Register         3.2.2 Node-Address/Transmitter Acknowledge Register                                                                                                                              | 3-1<br>3-2<br>3-3<br>3-3<br>3-5<br>3-7<br>3-8<br>3-8<br>3-8<br>3-8<br>3-9<br>3-10 |

|    | 3.3                             | FIFO Access       3         3.3.1 General       3         3.3.2 ATF Access       3         3.3.3 ITF Access       3         3.3.4 General-Receive-FIFO (GRF)       3         3.3.5 RAM Test Mode       3                                                       | 3–11<br>3–11<br>3–12<br>3–12<br>3–12                                              |

iii

| 4 | TSB   | 12C01A Data Formats                                                    | 4–1 |

|---|-------|------------------------------------------------------------------------|-----|

|   | 4.1   | Asynchronous Transmit (Host Bus to TSB12C01A)                          | 4–1 |

|   |       | 4.1.1 Quadlet Transmit                                                 |     |

|   |       | 4.1.2 Block Transmit                                                   | 4–1 |

|   |       | 4.1.3 Quadlet Receive                                                  | 4–2 |

|   |       | 4.1.4 Block Receive                                                    | 4–3 |

|   | 4.2   | Isochronous Transmit (Host Bus to TSB12C01A)                           | 4–5 |

|   | 4.3   | Isochronous Receive (TSB12C01A to Host Bus)                            |     |

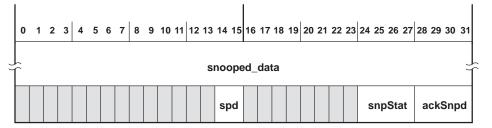

|   | 4.4   | Snoop                                                                  | 4–6 |

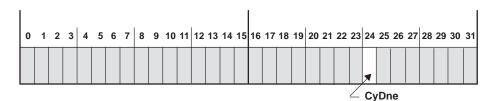

|   | 4.5   | CycleMark                                                              | 4–7 |

|   | 4.6   | Phy Configuration                                                      | 4–7 |

|   | 4.7   | Link-On                                                                | 4–8 |

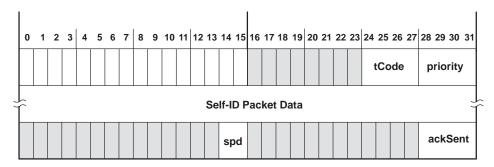

|   | 4.8   | Receive Self-ID                                                        | 4–9 |

| 5 | Elec  | trical Characteristics                                                 | 5–1 |

| - | 5.1   | Absolute Maximum Ratings Over Free-Air Temperature Range               |     |

|   | 5.2   | Recommended Operating Conditions                                       |     |

|   | 5.3   | Electrical Characteristics Over Recommended Ranges of Supply Voltage   |     |

|   |       | and Operating Free-Air Temperature                                     | 5–2 |

|   | 5.4   | Host-Interface Timing Requirements                                     |     |

|   | 5.5   | Host-Interface Switching Characteristics Over Operating Free-Air       |     |

|   |       | Temperature Range                                                      | 5–3 |

|   | 5.6   | Phy-Interface Timing Requirements Over Operating Free-Air              |     |

|   |       | Temperature Range                                                      | 5–3 |

|   | 5.7   | Phy-Interface Switching Characteristics Over Operating Free-Air        |     |

|   |       | Temperature Range                                                      | 5–4 |

|   | 5.8   | Miscellaneous Timing Requirements Over Operating Free-Air              |     |

|   |       | Temperature Range                                                      | 5–4 |

|   | 5.9   | Miscellaneous Signal Switching Characteristics Over Operating Free-Air |     |

|   |       | Temperature Range                                                      | 5–4 |

| 6 | Para  | ameter Measurement Information                                         |     |

| 7 |       | 12C01A to 1394 Phy Interface Specification                             |     |

| ' | 7.1   | Introduction                                                           |     |

|   | 7.2   |                                                                        |     |

|   | 7.3   | Block Diagram                                                          |     |

|   | 7.4   | Operational Overview                                                   |     |

|   |       | 7.4.1 Phy Interface Has Control of the Bus                             |     |

|   |       | 7.4.2 TSB12C01A Has Control of the Bus                                 |     |

|   | 7.5   |                                                                        | 7–2 |

|   |       | 7.5.1 LREQ Transfer                                                    |     |

|   |       | 7.5.2 Bus Request                                                      |     |

|   |       | 7.5.3 Read/Write Requests                                              |     |

|   | 7.6   | Status                                                                 |     |

|   |       | 7.6.1 Status Request                                                   |     |

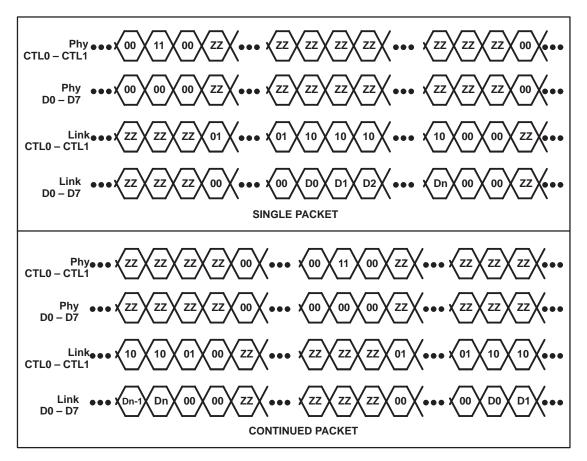

|   |       | 7.6.2 Transmit                                                         | 7–5 |

|   |       |                                                                        | 7-6 |

|   | 7.7   |                                                                        | 7-6 |

| 0 |       | , ,                                                                    |     |

| 8 | INIEC | hanical Data                                                           | 0-1 |

# List of Illustrations

| Figure                                                                      | Title                                                                                                                                                                                                                                                                                                                                                                             | Page                                                        |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1–1                                                                         | TSB12C01A Terminal Functions                                                                                                                                                                                                                                                                                                                                                      | 1–4                                                         |

| 2–1                                                                         | TSB12C01A Block Diagram                                                                                                                                                                                                                                                                                                                                                           | 2–1                                                         |

| 3–1<br>3–2<br>3–3                                                           | Internal Register Map<br>Interrupt Logic Diagram Example<br>TSB12C01A Controller-FIFO-Access Address Map                                                                                                                                                                                                                                                                          | 3–6                                                         |

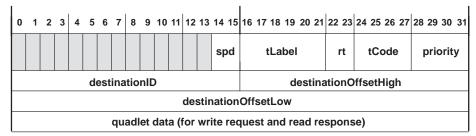

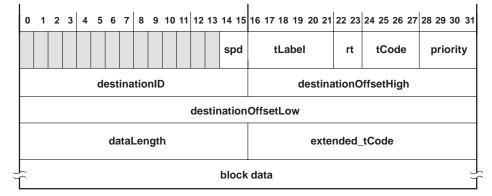

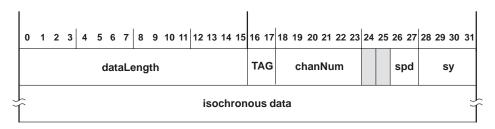

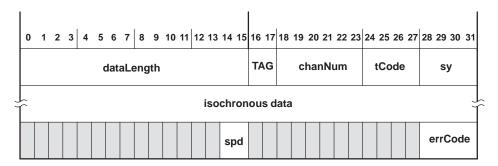

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11 | Quadlet-Transmit Format<br>Block-Transmit Format<br>Quadlet-Receive Format<br>Block-Receive Format<br>Isochronous-Transmit Format<br>Isochronous-Receive Format<br>Snoop Format<br>CycleMark Format<br>Phy Configuration Format<br>Link-On Format<br>Receive Self-ID Format                                                                                                       | 4-2<br>4-3<br>4-4<br>4-5<br>4-5<br>4-6<br>4-7<br>4-7<br>4-8 |

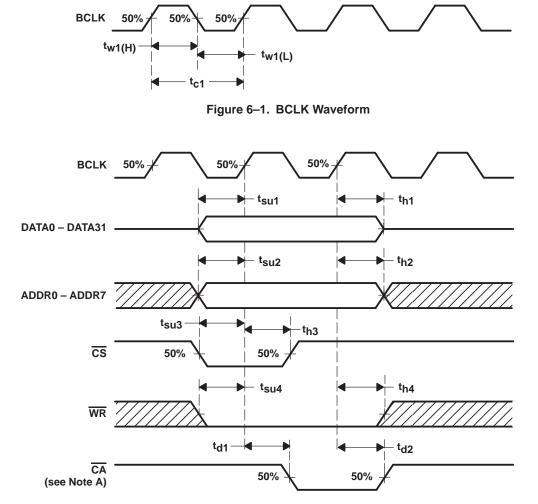

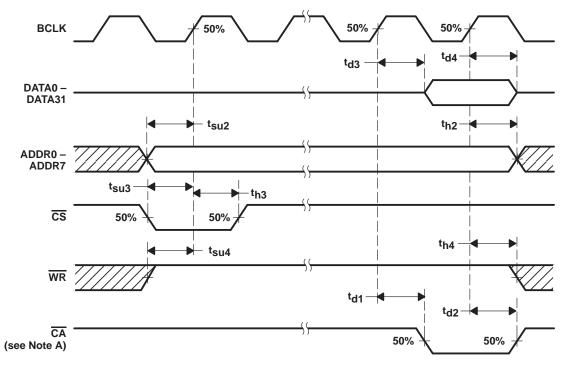

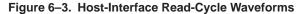

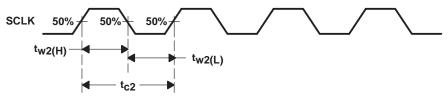

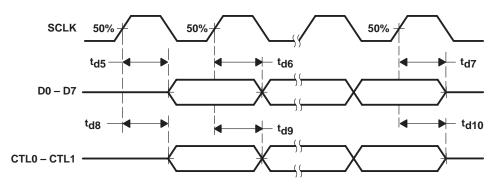

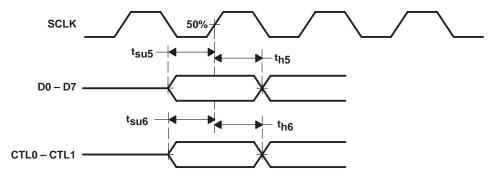

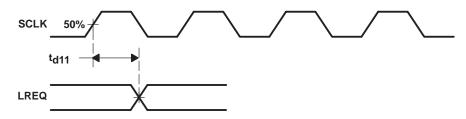

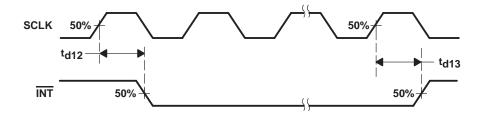

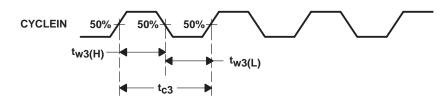

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-10         | BCLK Waveform         Host-Interface Write-Cycle Waveforms         Host-Interface Read-Cycle Waveforms         SCLK Waveform         TSB12C01A-to-Phy-Layer Transfer Waveforms         Phy Layer-to-TSB12C01A Transfer Waveforms         TSB12C01A Link-Request-to-Phy-Layer Waveforms         Interrupt Waveform         CYCLEIN Waveform         CYCLEIN and CYCLEOUT Waveforms | 6-1<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-4        |

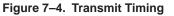

| 7–1<br>7–2<br>7–3<br>7–4<br>7–5                                             | Functional Block Diagram of the TSB12C01A to Phy Layer                                                                                                                                                                                                                                                                                                                            | 7–6<br>7–6<br>7–7                                           |

# **List of Tables**

| Table                                                                       | Title                                                                                                                                                                                                                                                                                                                                                                                | Page                                                         |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 1–1                                                                         | Terminal Functions                                                                                                                                                                                                                                                                                                                                                                   | 1–4                                                          |

| 3–1<br>3–2<br>3–3<br>3–4<br>3–5<br>3–6<br>3–7<br>3–8<br>3–9<br>3–10<br>3–11 | Version/Revision Register Field Descriptions                                                                                                                                                                                                                                                                                                                                         | 3–3<br>3–3<br>3–6<br>3–8<br>3–8<br>3–8<br>3–9<br>3–9<br>3–10 |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11 | Quadlet-Transmit Format         Block-Transmit Format Functions         Quadlet-Receive Format Functions         Block-Receive Format Functions         Isochronous-Transmit Functions         Isochronous-Receive Functions         Snoop Functions         CycleMark Functions         Phy Configuration Functions         Link-On Functions         Isochronous-Receive Functions | 4–2<br>4–3<br>4–4<br>4–5<br>4–6<br>4–6<br>4–7<br>4–8<br>4–8  |

| 7–1<br>7–2<br>7–3<br>7–4<br>7–5<br>7–6<br>7–7<br>7–8<br>7–9<br>7–10         | Phy Interface Control of Bus Functions                                                                                                                                                                                                                                                                                                                                               | 7–2<br>7–2<br>7–3<br>7–3<br>7–3<br>7–3<br>7–3<br>7–5         |

# 1 Overview

# 1.1 Description

The TSB12C01A is an IEEE 1394-1995 standard (from now on referred to only as 1394) high-speed serial-bus link-layer controller that allows for easy integration into an I/O subsystem. The TSB12C01A transmits and receives correctly formatted 1394 packets and generates and inspects the 32-bit cyclic redundancy check (CRC). The TSB12C01A is capable of being a cycle master and supports reception of isochronous data on two channels. It interfaces directly to the TSB11C01, TSB11LV01, and TSB21LV03 physical-layer chips and can support bus speeds of 100, 200, and 400 Mb/s. The TSB12C01A has a generic 32-bit host bus interface, which makes connection to most 32-bit host buses very simple. The TSB12C01A has software-adjustable FIFOs for optimal FIFO size and performance characterization and allows for variable-size asynchronous-transmit FIFO (ATF), isochronous-transmit FIFO (ITF), and general-receive FIFO (GRF).

This document is not intended to serve as a tutorial on 1394; users should refer to the IEEE 1394-1995 serial bus for detailed information regarding the 1394 high-speed serial bus.

# 1.2 Features

The following are features of the TSB12C01A.

#### 1.2.1 Link

- Complies With IEEE-1394-1995 Standard

- Transmits and Receives Correctly Formatted 1394 Packets

- Supports Isochronous Data Transfer

- Performs Function of Cycle Master

- Generates and Checks 32-Bit CRC

- Detects Lost Cycle-Start Messages

- Contains Asynchronous, Isochronous, and General-Receive FIFOs

#### 1.2.2 Physical-Link Interface

- Interfaces Directly to the TSB11C01, TSB11LV01, TSB14C01, and TSB21LV03 Phy Chips

- Supports Speeds of 100, 200, and 400 Mb/s

- Implements the Physical-Link Interface Described in Annex J of the IEEE 1394-1995 Standard

- Supports TI Bus Holder Isolation External Implementation

#### 1.2.3 Host Bus Interface

- Provides Chip Control With Directly Addressable Registers

- Is Interrupt Driven to Minimize Host Polling

- Has a Generic 32-Bit Host Bus Interface

#### 1.2.4 General

- Requires a Single 5-V ±5% Power Supply

- Manufactured with Low-Power CMOS Technology

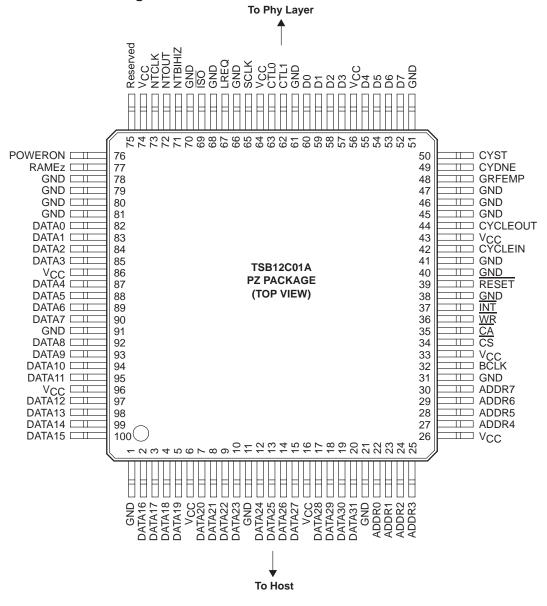

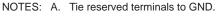

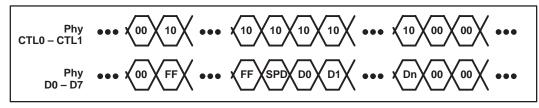

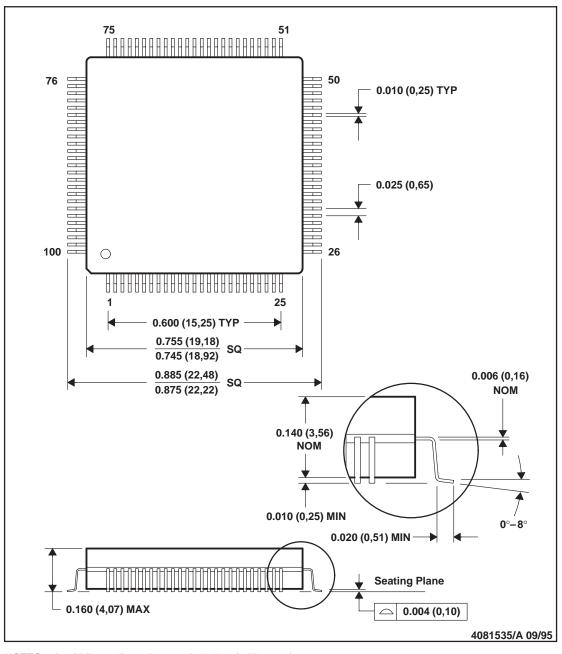

- Packaged in a 100-Pin Thin Quad Flat Package (TQFP) (PZ Package) for 0°C to 70°C and -40°C to 85°C Operation

- Packaged in a 100-Pin Ceramic Quad Flat Package (WN Package) for -55°C to 125°C Operation

#### **1.3 Terminal Assignments**

B. Bit 0 is the most significant bit (MSB).

B. Bit 0 is the most significant bit (MSB).

## **1.4 Terminal Functions**

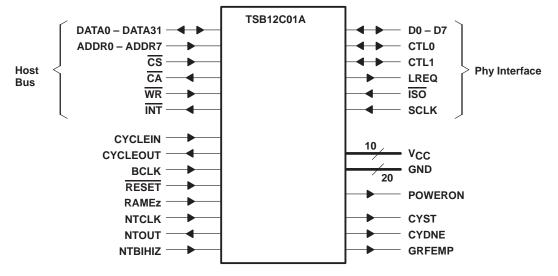

| Figure 1–1. | TSB12C01A | <b>Terminal Functions</b> |

|-------------|-----------|---------------------------|

|-------------|-----------|---------------------------|

|  | Table | 1–1. | Terminal | <b>Functions</b> |

|--|-------|------|----------|------------------|

|--|-------|------|----------|------------------|

| TERM              | TERMINAL                                                           |     |                                                                                                                                                                                                                                                                |  |  |

|-------------------|--------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                   |                                                                    |     | DESCRIPTION                                                                                                                                                                                                                                                    |  |  |

| NAME              | NO.                                                                |     |                                                                                                                                                                                                                                                                |  |  |

|                   |                                                                    |     | Host Bus Interface                                                                                                                                                                                                                                             |  |  |

| ADDR0 –<br>ADDR7  | 22-25<br>27-30                                                     | I   | Address 0 through address 7. Host bus address bus bits 0 through 7 that address the quadlet-aligned FIFOs and configuration registers. The two least significant address lines, 6 and 7, must be grounded.                                                     |  |  |

| CA                | 35                                                                 | 0   | Cycle acknowledge (active low). $\overline{CA}$ is a TSB12C01A control signal to the host bus.<br>When asserted (low), access to the configuration registers or FIFO is complete.                                                                              |  |  |

| CS                | 34                                                                 | I   | Cycle start (active low). $\overline{\text{CS}}$ is a host bus control signal to enable access to the configuration registers or FIFO.                                                                                                                         |  |  |

| DATA0 –<br>DATA31 | 2-5<br>7-10<br>12-15<br>17-20<br>82-85<br>87-90<br>92-95<br>97-100 | I/O | Data 0 through 31. DATA is a host bus data bus bits 0 through 31.                                                                                                                                                                                              |  |  |

| INT               | 37                                                                 | 0   | Interrupt (active low). When INT is asserted (low), the TSB12C01A notifies the host bus that an interrupt has occurred.                                                                                                                                        |  |  |

| WR                | 36                                                                 | I   | Read/write enable. When $\overline{WR}$ is deasserted (high) in conjunction with $\overline{CS}$ , a read from the TSB12C01A is requested. When $\overline{WR}$ is asserted (low) in conjunction with $\overline{CS}$ , a write to the TSB12C01A is requested. |  |  |

| TERMINAL   |                                                                                                             |     |                                                                                                                                                                                                                                                                                                                                  |  |

|------------|-------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME NO.   |                                                                                                             | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                      |  |

|            |                                                                                                             |     | Phy Interface                                                                                                                                                                                                                                                                                                                    |  |

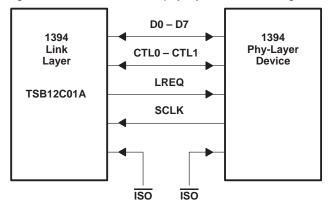

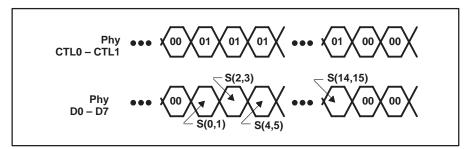

| CTL1, CTL0 | 62, 63                                                                                                      | I/O | Control 1 and control 0 of the phy-link control bus. CTL1 and CTL0 indicate the four operations that can occur in this interface (see Section 7 of this document or Annex J of the IEEE 1394-1995 standard for more information about the four operations).                                                                      |  |

| D0 – D7    | 52-55<br>57-60                                                                                              | I/O | Data 0 through data 7 of the phy-link data bus. Data is expected on D0 – D1 for 100 Mb/s packets, D0 – D3 for 200 Mb/s, and D0 – D7 for 400 Mb/s.                                                                                                                                                                                |  |

| ISO        | 69                                                                                                          | I   | Isolation barrier (active low). This ISO is asserted (low) when an isolation barrier is present.                                                                                                                                                                                                                                 |  |

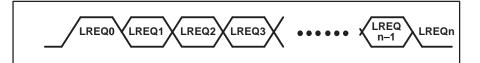

| LREQ       | 67                                                                                                          | 0   | Link request. LREQ is a TSB12C01A output that makes bus requests and accesses the phy layer.                                                                                                                                                                                                                                     |  |

| POWERON    | 76                                                                                                          | 0   | Power on indicator to phy interface. When active, POWERON has a clock output with 1/32 of the BCLK frequency and indicates to the phy interface that the TSB12C01A is powered. This terminal can be connected to the link power status (LPS) terminal on the TI phy devices to provide an indication of the LLC power condition. |  |

| SCLK       | 65                                                                                                          | I   | System clock. SCLK is a 49.152-MHz clock from the phy, that generates the 24.576-MHz clock.                                                                                                                                                                                                                                      |  |

|            |                                                                                                             |     | Miscellaneous Signals                                                                                                                                                                                                                                                                                                            |  |

| BCLK       | 32                                                                                                          | I   | Bus clock. BCLK is the host bus clock used in the host-interface module of the TSB12C01A. It is asynchronous to SCLK.                                                                                                                                                                                                            |  |

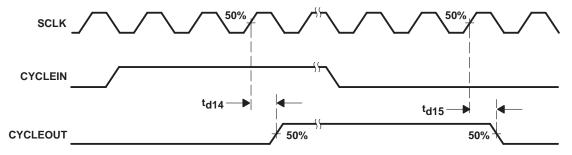

| CYCLEIN    | 42                                                                                                          | I   | Cycle in. CYCLEIN is an optional external 8,000-Hz clock used as the cycle clock, and it should only be used when attached to the cycle-master node. It is enabled by the cycle source bit and should be tied high when not used.                                                                                                |  |

| CYCLEOUT   | 44                                                                                                          | 0   | Cycle out. CYCLEOUT is the TSB12C01A version of the cycle clock. It is based on the timer controls and received cycle-start messages.                                                                                                                                                                                            |  |

| CYDNE      | 49                                                                                                          | 0   | Status of CyDne bit. When the RevAEn bit of the control register is set, CYDNE indicates the value of the CyDne bit of the interrupt register. When RevAEn is cleared, CYDNE is a 3-state output.                                                                                                                                |  |

| CYST       | 50                                                                                                          | 0   | Status of CySt bit. When the RevAEn bit of the control register is set, CYST indicates the value of the CySt bit of the interrupt register. When RevAEn is cleared, CYST is a 3-state output.                                                                                                                                    |  |

| GND        | $\begin{array}{c} 1,11,\\ 21,31,\\ 38,40,\\ 41,\\ 45-47,\\ 51,61,\\ 66,68,\\ 70,\\ 78-81,\\ 91 \end{array}$ |     | Ground reference                                                                                                                                                                                                                                                                                                                 |  |

| GRFEMP     | 48                                                                                                          | 0   | Status of Empty bit. When the RevAEn bit of the control register is set, GRFEMP indicates the value of the Empty bit of the GRF status register. When RevAEn is cleared, GRFEMP is a 3-state output.                                                                                                                             |  |

| RAMEz      | 77                                                                                                          | I   | RAM 3-state enable. When RAMEz is deasserted (low), FIFOs are enabled. When RAMEz is asserted, the FIFOs are 3-state outputs. (This is a manufacturing test-mode condition and should be grounded under normal operating conditions.)                                                                                            |  |

# Table 1–1. Terminal Functions (Continued)

| TERMINAL |                                                | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                               |  |

|----------|------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.                                            | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                               |  |

| NTBIHIZ  | 71                                             | Ι   | NAND-tree bidirectional 3-state output. When NTBIHIZ is deasserted (low), the bidirectional I/Os operate in a normal state. When NTBIHZ is asserted (high), the bidirectional I/Os are in the 3-state output mode. (This is a manufacturing test-mode condition and should be grounded under normal operating conditions. |  |

| NTCLK    | 73                                             | I   | NAND clock input. The NAND-tree clock is used for $V_{\mbox{IH}}$ and $V_{\mbox{IL}}$ manufacturing tests. (This input should be grounded under normal operating conditions.)                                                                                                                                             |  |

| NTOUT    | 72                                             | 0   | NAND-tree output. This output should remain open under normal operating conditions.                                                                                                                                                                                                                                       |  |

| RESET    | 39                                             | I   | Reset (active low). RESET is the asynchronous reset to the TSB12C01A.                                                                                                                                                                                                                                                     |  |

| Vcc      | 6, 16, 26,<br>33, 43, 56,<br>64, 74, 86,<br>96 |     | 5-V $\pm$ 5% power supplies                                                                                                                                                                                                                                                                                               |  |

## Table 1–1. Terminal Functions (Continued)

# 2 Architecture

# 2.1 Functional Block Diagram

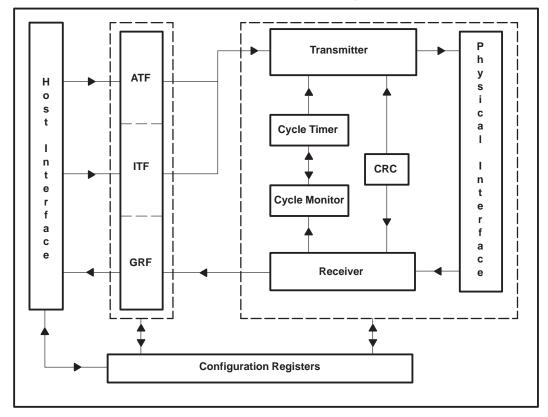

The functional block architecture of the TSB12C01A is shown in Figure 2–1.

Figure 2–1. TSB12C01A Block Diagram

#### 2.1.1 Physical Interface

The physical (phy) interface provides phy-level services to the transmitter and receiver. This includes gaining access to the serial bus, sending packets, receiving packets, and sending and receiving acknowledge packets.

The phy interface module also interfaces to the phy chip and conforms to the phy-link interface specification described in Annex J of the IEEE 1394-1995 standard (refer to Section 7 of this document for more information).

# 2.1.2 Transmitter

The transmitter retrieves data from either the ATF or the ITF and creates correctly formatted serial-bus packets to be transmitted through the phy interface. When data is present at the ATF interface to the transmitter, the TSB12C01A phy interface arbitrates for the serial bus and sends a packet. When data is present at the ITF interface to the transmitter, the TSB12C01A arbitrates for the serial bus during the next isochronous cycle. The transmitter autonomously sends the cycle-start packets when the chip is a cycle master.

#### 2.1.3 Receiver

The receiver takes incoming data from the phy interface and determines if the incoming data is addressed to this node. If the incoming packet is addressed to this node, the CRC of the packet is checked. If the header CRC is good, the header is confirmed in the GRF. For block and isochronous packets, the remainder of the packet is confirmed one quadlet at a time. The receiver places a status quadlet in the GRF after the last quadlet of the packet is confirmed in the GRF. The status quadlet contains the error code for the packet. The error code is the acknowledge code that is sent for that packet. For broadcast packets that do not need acknowledge packets, the error code is the acknowledge code take the transaction layer whether or not the data CRC is good or bad. When the header CRC is bad, the header is flushed and the rest of the packet is ignored.

When a cycle-start message is received, it is detected and the cycle-start message data is sent to the cycle timer. The cycle-start messages are not placed in the GRF like other quadlet packets. At the end of an isochronous cycle and if the cycle mark enable (CyMrkEn) bit of the control register is set , the receiver inserts a cycle-mark packet in the GRF to indicate the end of the isochronous cycle.

#### 2.1.4 Transmit and Receive FIFOs

The TSB12C01A contains two transmit FIFOs (asynchronous and isochronous) and one receive FIFO (general receive). Each of these FIFOs is one quadlet wide and their length is software adjustable. These software-adjustable FIFOs allow customization of the size of each FIFO for individual applications. The sum of all FIFOs cannot be larger than 509 quadlets. To understand how to set the size of the FIFOs, see subsections 3.2.11 through 3.2.13. The transmit FIFOs are write only from the host bus interface, and the receive FIFO is read only from the host bus interface.

An example of how to use software-adjustable FIFOs follows:

In applications where isochronous packets are large and asynchronous packets are small, the implementer can set the ITF and GRF to a large size (200 quadlets each) and set the ATF to a smaller size (100 quadlets). Notice that the sum of all FIFOs is less than or equal to 509 quadlets.

#### 2.1.5 Cycle Timer

The cycle timer is used by nodes that support isochronous data transfer. The cycle timer is a 32-bit cycle-timer register. Each node with isochronous data-transfer capability has a cycle-timer register as defined in the IEEE 1394-1995 standard. In the TSB12C01A, the cycle-timer register is implemented in the cycle timer and is located in IEEE-1212 initial register space at location 200h and can also be accessed through the local bus at address 14h. The low-order 12 bits of the timer are a modulo 3072 counter, which increments once every 24.576-MHz clock periods (or 40.69 ns). The next 13 higher-order bits are a count of 8, 000-Hz (or 125  $\mu$ s)cycles, and the highest 7 bits count seconds.

The cycle timer contains the cycle-timer register. The cycle-timer register consists of three fields: cycle offset, cycle count, and seconds count. The cycle timer has two possible sources. First, if the cycle source (CySrc) bit in the configuration register is set, then the CYCLEIN input causes the cycle count field to increment for each positive transition of the CYCLEIN input (8 kHz) and the cycle offset resets to all zeros. CYCLEIN should only be the source when the node is cycle master. When the cycle-count field increments, CYCLEOUT is generated. The timer can also be disabled using the cycle-timer-enable bit in the control register. See subsection 3.2.5 for more information.

The second cycle-source option is when the CySrc bit is cleared. In this state, the cycle-offset field of the cycle-timer register is incremented by the internal 24.576-MHz clock. The cycle timer is updated by the reception of the cycle-start packet for the noncycle master nodes. Each time the cycle-offset field rolls over, the cycle-count field is incremented and the CYCLEOUT signal is generated. The cycle-offset field in the cycle-start packet is used by the cycle-master node to keep all nodes in phase and running with a nominal isochronous cycle of 125  $\mu$ s.

CYCLEOUT indicates to the cyclemaster node that it is time to send a cycle-start packet. And, on noncyclemaster nodes, CYCLEOUT indicates that it is time to expect a cycle-start packet. The cycle-start bit is set when the cycle-start packet is sent from the cyclemaster node or received by a noncyclemaster node.

## 2.1.6 Cycle Monitor

The cycle monitor is only used by nodes that support isochronous data transfer. The cycle monitor observes chip activity and handles scheduling of isochronous activity. When a cycle-start message is received or sent, the cycle monitor sets the cycle-started interrupt bit. It also detects missing cycle-start packets and sets the cycle-lost interrupt bit when this occurs. When the isochronous cycle is complete, the cycle monitor sets the cycle monitor instructs the transmitter to send a cycle-start message when the cycle-master bit is set in the control register.

# 2.1.7 Cyclic Redundancy Check (CRC)

The CRC module generates a 32-bit CRC for error detection. This is done for both the header and data. The CRC module generates the header and data CRC for transmitting packets and checks the header and data CRC for received packets. See the IEEE 1394-1995 standard for details on the generation of the CRC<sup>†</sup>.

#### 2.1.8 Internal Registers

The internal registers control the operation of the TSB12C01A. The register definitions are specified in Section 3.

#### 2.1.9 Host Bus Interface

The host bus interface allows the TSB12C01A to be easily connected to most host processors. This host bus interface consists of a 32-bit data bus and an 8-bit address bus. The TSB12C01A utilizes cycle-start and cycle-acknowledge handshake signals to allow the local bus clock and the 1394 clock to be asynchronous to one another. The TSB12C01A is interrupt driven to reduce polling.

<sup>†</sup> This is the same CRC used by the IEEE802 LANs and the X3T9.5 FDDI.

# **3** Internal Registers

# 3.1 General

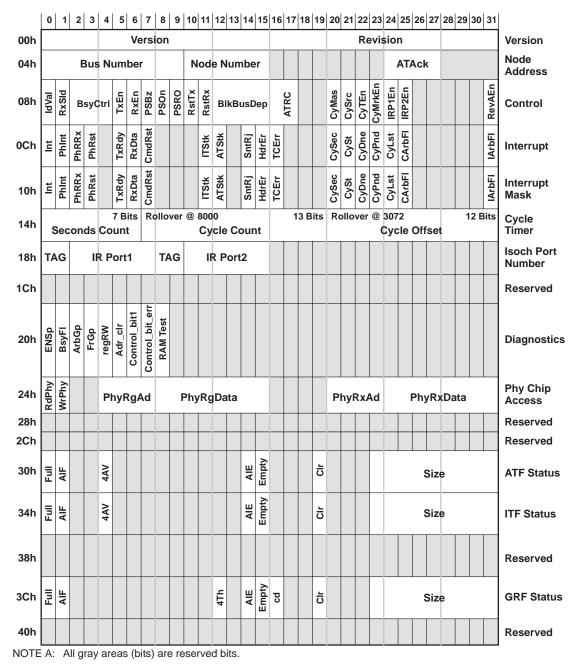

The host-bus processor directs the operation of the TSB12C01A through a set of registers internal to the TSB12C01A itself. These registers are read or written by asserting  $\overline{CS}$  with the proper address on ADDR0 – ADDR7 and asserting or deasserting WR depending on whether a read or write is needed. Figure 3–1 lists the register addresses; subsequent sections describe the function of the various registers.

# 3.2 Internal Register Definitions

The TSB12C01A internal registers control the operation of the TSB12C01A. The bit definitions of the internal registers are shown in Figure 3–1 and are described in subsections 3.2.1 through 3.2.13.

Figure 3–1. Internal Register Map

#### 3.2.1 Version/Revision Register

The version/revision register allows software to be written that supports multiple versions of the high-speed serial-bus link-layer controllers. This register is at address 00h and is read only. The initial value is 3031\_3041h.

| BITS  | ACRONYM  | FUNCTION NAME | DESCRIPTION               |

|-------|----------|---------------|---------------------------|

| 0-15  | Version  | Version       | Version of the TSB12C01A  |

| 16-31 | Revision | Revision      | Revision of the TSB12C01A |

Table 3–1. Version/Revision Register Field Descriptions

#### 3.2.2 Node-Address/Transmitter Acknowledge Register

The node-address/transmitter acknowledge register controls which packets are accepted/rejected, and it presents the last acknowledge received for packets sent from the ATF. This register is at offset 04h. The bus number and node number fields are read/write. The AT acknowledge (ATAck) received is normally read only. Setting the regRW bit in the diagnostic register makes these fields read/write. The initial value is FFFF\_0000h.

|       | i          | i                                              |                                                                                                                                                                                                                                                                                                           |

|-------|------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BITS  | ACRONYM    | FUNCTION NAME                                  | DESCRIPTION                                                                                                                                                                                                                                                                                               |

| 0-9   | BusNumber  | Bus number                                     | BusNumber is the 10-bit IEEE 1212 bus number that the TSB12C01A uses with the node number in the SOURCE address for outgoing packets and to accept or reject incoming packets. The TSB12C01A always accepts packets with a bus number equal to 3FFh.                                                      |

| 10-15 | NodeNumber | Node number                                    | NodeNumber is the 6-bit node number that the TSB12C01A uses<br>with the bus number in the source address for outgoing packets and<br>to accept or reject incoming packets. The TSB12C01A always<br>accepts packets with the node address equal to 3Fh. See<br>BlkBusDep bits in Table 3–3 for exceptions. |

| 16-23 | Reserved   | Reserved                                       | Reserved                                                                                                                                                                                                                                                                                                  |

| 24–27 | ATAck      | Address transmitter<br>acknowledge<br>received | ATAck is the last acknowledge received by the transmitting node in response to a packet sent from the asynchronous transmit-FIFO. When an acknowledge time out occurs, the value written to ATAck is 0h. See Table 6–13 in IEEE 1394-1995 standard for acknowledge codes.                                 |

| 28-31 | Reserved   | Reserved                                       | Reserved                                                                                                                                                                                                                                                                                                  |

Table 3–2.

Node-Address/Transmitter Acknowledge Register Field Descriptions

#### 3.2.3 Control Register

The control register dictates the basic operation of the TSB12C01A. This register is at address 08h and is read/write. The initial value is 0000\_0000h.

| BITS | ACRONYM | FUNCTION NAME            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0    | IdVal   | ID Valid                 | When IdVal is set, the TSB12C01A accepts packets addressed to<br>the IEEE 1212 address set (Node Number) in the node-address<br>register. When IdVal is cleared, the TSB12C01A accepts only<br>broadcast packets.                                                                                                                                                                   |  |  |

| 1    | RxSld   | Received self-ID packets | When RxSId is set, the self-identification packets generated by phy chips during bus initialization are received and placed into the GRF as a single packet. Each self-identification packet is composed of two quadlets, where the second quadlet is the logical inverse of the first. If ACK (4 bits) equals 1h, then the data is good. If ACK equals Dh, then the data is wrong. |  |  |

Table 3–3. Control-Register Field Descriptions

| BITS  | ACRONYM   | FUNCTION NAME                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|-----------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-4   | BsyCtrl   | Busy control                       | <ul> <li>These bits control which busy status (as described in IEEE 1394-1995 standard, the chip returns to incoming packets. The field is defined as follows:</li> <li>000 = follow normal busy/retry protocol, only send busy when necessary.</li> <li>001 = send busyA when it is necessary to send a busy acknowledge.</li> <li>010 = send busyB when it is necessary to send a busy acknowledge.</li> <li>011 = reserved</li> <li>100 = send a busy acknowledge to all incoming packets following the normal busy/retry protocol.</li> <li>101 = send a busy acknowledge to all incoming packets by sending a busyA acknowledge.</li> <li>110 = send a busy acknowledge to all incoming packets by sending a busyA acknowledge.</li> <li>111 = reserved</li> <li>111 = reserved</li> <li>When retry_X is received and the receiving node needs to send a busy acknowledge signal, it sends an ack_busy_X signal.</li> </ul> |

| 5     | TxEn      | Transmitter enable                 | When TxEn is cleared, the transmitter does not arbitrate or send packets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6     | RxEn      | Receiver enable                    | When RXEn is cleared, the receiver does not receive any packets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7     | PSBz      | Physical DMA<br>busy               | <ul> <li>When:</li> <li>1) PSOn is set,</li> <li>2) PSRO is cleared or the incoming packet is a read,</li> <li>3) destination offset is in the lower 4 Gbytes, and</li> <li>4) PSBz is set,</li> <li>the TSB12C01A sends a busy acknowledge to the incoming packet.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8     | PSOn      | Physical DMA on                    | When PSOn is set, the TSB12C01A uses PSRO and PSBz to determine acceptance of incoming request packets addressed to the lower 4 Gbytes of initial memory space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9     | PSRO      | Physical DMA read only             | When PSOn is set, the TSB12C01A uses PSRO to determine the acceptance of incoming write request packets addressed to the lower 4 Gbytes of initial memory space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10    | RstTx     | Reset transmitter                  | When RstTx is set, the entire transmitter resets synchronously. This bit clears itself.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11    | RstRx     | Reset receiver                     | When RstRx is set, the entire receiver resets synchronously. This bit clears itself.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12–15 | BlkBusDep | Block bus-<br>dependent<br>address | This field is used by the receiver to filter out broadcast packets to the bus-dependent area of CSR space. Setting the LSB of this field disables the reception of broadcast packets to the lowest 128 bytes of bus-dependent CSR space. Setting the MSB of this field disables the reception of broadcast packets to the highest 128 bytes of bus-dependent CSR space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16–17 | ATRC      | AT retry code                      | This field contains the last retry code received. This code is logically<br>ORed with the retry code field (00) in the transmit packet, and the packet<br>is resent. This alleviates the need to change the retry code in the transmit<br>packet. The retry encoding follows the IEEE 1394-1995 standard. The<br>retry code is as follows:00retry_o (new)01retry_X10retry_A11retry_B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 3–3. Control-Register Field Descriptions (Continued)

| BITS  | ACRONYM  | FUNCTION NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 18-19 | Reserved | Reserved           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 20    | CyMas    | Cycle master       | When CyMas is set and the TSB12C01A is attached to the root phy, the cyclemaster function is enabled. When the cycle_count field of the cycle timer register increments, the transmitter sends a cycle-start packet. This bit is not cleared upon bus reset. When another node is selected as root during a bus reset, the transaction layer in the now nonroot TSB12C01A node must clear this bit and the transaction layer in the TSB12C01a node selected as root must set this bit. |  |

| 21    | CySrc    | Cycle source       | When CySrc is set, the cycle_count field increments and the cycle_offset field resets for each positive transition of CYCLEIN. When CySrc is cleared, the cycle_count field increments when the cycle_offset field rolls over.                                                                                                                                                                                                                                                         |  |

| 22    | CyTEn    | Cycle-timer enable | When CyTEn is set, the cycle_offset field increments.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 23    | CyMrkEn  | Cycle mark enable  | When CyMrkEn is set, cycle marks are inserted into GRF at the end of each isochronous cycle (TSB12C01A compatible). When CyMrkEn is cleared, no cycle marks are generated.                                                                                                                                                                                                                                                                                                             |  |

| 24    | IRP1En   | IR port 1 enable   | When IRP1En is set, the receiver accepts isochronous packets when the channel number matches the value in the IR Port1 field.                                                                                                                                                                                                                                                                                                                                                          |  |

| 25    | IRP2En   | IR port 2 enable   | When IRP2En is set, the receiver accepts isochronous packets when the channel number matches the value in the IR Port2 field.                                                                                                                                                                                                                                                                                                                                                          |  |

| 26-30 | Reserved | Reserved           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 31    | RevAEn   | Rev A enable       | When set, RevAEn enables the output of GRFEMP, CYDNE, and CYST.<br>When not set, these outputs are in a high-impedance state, which makes<br>TSB12C01A pin-compatible with the TSB12C01. This bit is 0 on power<br>up.                                                                                                                                                                                                                                                                 |  |

Table 3–3. Control-Register Field Descriptions (Continued)

#### 3.2.4 Interrupt and Interrupt-Mask Registers

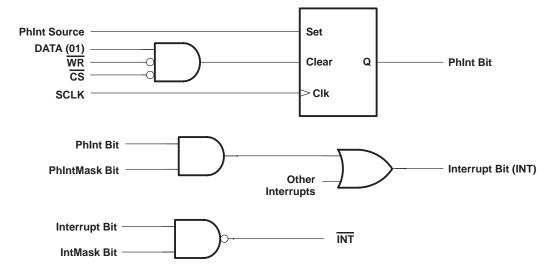

The interrupt and interrupt-mask registers work in tandem to inform the host bus interface when the state of the TSB12C01A changes. The interrupt register is at address 0Ch. The interrupt mask register is at address 10h. The interrupt mask register is read/write. Its initial value is 0000\_0000h. When regRW is cleared to 0, the interrupt register (except for the Int bit) is write to clear. When regRW (in diagonstics register at 20h) is set to 1, the interrupt register (including the Int bit) is read/write. Its initial value is 1000\_000h.

The interrupt bits all work the same. For example, when a phy interrupt occurs, the PhInt bit is set. When the PhIntMask bit is set, the Int bit is set. When the IntMask is set, the INT signal is asserted. The logic for the interrupt bits is shown in Figure 3–2. Table 3–4 defines the interrupt and interrupt-mask register field descriptions. As shown in Figure 3–2, the INT bit is the OR of interrupt bits 1 - 31. When all the interrupt bits are cleared, INT equals 0. When any of the interrupt bits are set, INT equals 1, even when the INT bit was just cleared.

| Figure 3–2. | Interrupt | Logic | Diagram | Example |

|-------------|-----------|-------|---------|---------|

|             |           |       |         |         |

| BITS | ACRONYM  | FUNCTION NAME                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|----------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Int      | Interrupt                            | Int contains the value of all interrupt and interrupt mask bits ORed together.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1    | PhInt    | Phy chip interrupt                   | When PhInt is set, the phy chip has signaled an interrupt through the Phy interface.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2    | PhyRRx   | Phy register<br>information received | When PhyRRx is set, a register value has been transferred to the phy chip access register (offset 24h) from the phy interface.                                                                                                                                                                                                                                                                                                                                                                           |

| 3    | PhRst    | Phy reset started                    | When PhRst is set, a phy-layer reconfiguration has started (1394 bus reset).                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4    | Reserved | Reserved                             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5    | TxRdy    | Transmitter ready                    | When TxRdy is set, the transmitter is idle and ready.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6    | RxDta    | Receiver has data                    | In normal mode and when set, RxDta indicates that the receiver has accepted a quadlet of data into the GRF interface. This bit is set each time a quadlet of data is accepted. However, during the self-ID portion of a bus reset, this bit is set after each complete self-ID packet is received into the GRF.                                                                                                                                                                                          |

| 7    | CmdRst   | Command reset received               | When CmdRst is set, the receiver has been sent a quadlet write request addressed to the RESET_START CSR register.                                                                                                                                                                                                                                                                                                                                                                                        |

| 8-10 | Reserved | Reserved                             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11   | ITStk    | Transmitter is stuck<br>(IT)         | When ITStk is set, the transmitter has detected invalid data at the isochronous transmit-FIFO interface.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12   | ATStk    | Transmitter is stuck<br>(AT)         | When ATStk is set, the transmitter has detected invalid data at the asynchronous transmit-FIFO interface. If the first quadlet of a packet is not written to the ATF_First or ATF_First&Update, the transmitter enters a state denoted by an ATStuck interrupt. An underflow of the ATF also causes an ATStuck interrupt. If this state is entered, no asynchronous packets can be sent until the ATF is cleared by way of the CLR ATF control bit. Isochronous packets can be sent while in this state. |

| BITS  | ACRONYM  | FUNCTION NAME                     | DESCRIPTION                                                                                                                                                                        |

|-------|----------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13    | Reserved | Reserved                          | Reserved                                                                                                                                                                           |

| 14    | SntRj    | Busy acknowledge sent by receiver | When SntRj is set, the receiver is forced to send a busy acknowledge to a packet addressed to this node because the GRF overflowed.                                                |

| 15    | HdrEr    | Header error                      | When HdrEr is set, the receiver detected a header CRC error on an incoming packet that may have been addressed to this node.                                                       |

| 16    | TCErr    | Transaction code<br>error         | When TCErr is set, the transmitter detected an invalid transaction code in the data at the transmit FIFO interface.                                                                |

| 17-19 | Reserved | Reserved                          | Reserved                                                                                                                                                                           |

| 20    | CySec    | Cycle second<br>incremented       | When CySec is set, the cycle-second field in the cycle-timer register<br>is incremented. This occurs approximately every second when the<br>cycle timer is enabled.                |

| 21    | CySt     | Cycle started                     | When CySt is set, the transmitter has sent or the receiver has received a cycle-start packet.                                                                                      |

| 22    | CyDne    | Cycle done                        | When CyDne is set, an arbitration gap has been detected on the bus after the transmission or reception of a cycle-start packet. This indicates that the isochronous cycle is over. |

| 23    | CyPnd    | Cycle pending                     | When CyPnd is set, the cycle-timer offset is set to 0 (rolled over or reset) and remains set until the isochronous cycle ends.                                                     |

| 24    | CyLst    | Cycle lost                        | When CyLst is set, the cycle timer has rolled over twice without the reception of a cycle-start packet. This occurs only when this node is not the cycle master.                   |

| 25    | CArbFl   | Cycle arbitration failed          | When CArbFI is set, the arbitration to send the cycle-start packet failed.                                                                                                         |

| 26-30 | Reserved | Reserved                          | Reserved                                                                                                                                                                           |