# TLC34075A Video Interface Palette

# Data Manual

SLAS058 April 1995

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of TI products in such applications is understood to be fully at the risk of the customer using TI devices or systems.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

This device includes circuits that are patented and circuit designs that have patents pending.

D4049, AUGUST 1992

Copyright © 1992, Texas Instruments Incorporated

Printed in the U.S.A.

# Contents

Title

Section

| Page |

|------|

|      |

| 1 | Intro | duction                                                                    |

|---|-------|----------------------------------------------------------------------------|

|   | 1.1   | Features                                                                   |

|   | 1.2   | Functional Block Diagram 1-2                                               |

|   | 1.3   | Terminal Assignments 1-3                                                   |

|   | 1.4   | Ordering Information                                                       |

|   | 1.5   | Terminal Functions 1-4                                                     |

| 2 | Deta  | iled Description                                                           |

|   | 2.1   | MPU Interface                                                              |

|   | 2.2   | Color Palette RAM                                                          |

|   |       | 2.2.1 Writing to the Color Palette RAM                                     |

|   |       | 2.2.2 Reading From the Color Palette RAM                                   |

|   |       | 2.2.3 Palette Page Register                                                |

|   | 2.3   | Input/Output Clock Selection and Generation 2-2                            |

|   |       | 2.3.1 SCLK                                                                 |

|   |       | 2.3.2 VCLK                                                                 |

|   | 2.4   | Multiplexing Scheme                                                        |

|   |       | 2.4.1 VGA Pass-Through Mode                                                |

|   |       | 2.4.2 Multiplexing Modes                                                   |

|   |       | 2.4.3 True Color Mode                                                      |

|   |       | 2.4.4 Special Nibble Mode                                                  |

|   |       | 2.4.5 Multiplex Control Register 2-8                                       |

|   |       | 2.4.6 Read Masking 2-11                                                    |

|   | 2.5   | Reset                                                                      |

|   |       | 2.5.1 Power-On Reset                                                       |

|   |       | 2.5.2 Hardware Reset                                                       |

|   |       | 2.5.3 Software Reset                                                       |

|   |       | 2.5.4 VGA Pass-Through Mode Default Conditions 2-11                        |

|   | 2.6   | Frame Buffer Interface                                                     |

|   | 2.7   | Analog Output Specifications                                               |

|   | 2.8   | HSYNC, VSYNC, and BLANK                                                    |

|   | 2.9   | Split Shift Register Transfer VRAMs and Special Nibble Mode                |

|   |       | 2.9.1 Split Shift Register Transfer VRAMs                                  |

|   | • • • | 2.9.2 Special Nibble Mode                                                  |

|   |       | MUXOUT Output                                                              |

|   | 2.11  | General Control Register                                                   |

|   |       | 2.11.1 HSYNCOUT and VSYNCOUT (Bits 0 and 1)                                |

|   |       | 2.11.2 Split Shift Register Transfer Enable (SSRT) and Special Nibble Mode |

|   |       | Enable (SNM) (Bits 2 and 3) 2-17                                           |

# Contents (Continued)

| Section | Title                                                                                                                                 | Page         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------|--------------|

|         | <ul> <li>2.11.3 Pedestal Enable Control (Bit 4)</li> <li>2.11.4 Sync Enable Control (Bit 5)</li> <li>2.11.5 MUXOUT (Bit 7)</li> </ul> | 2-17<br>2-17 |

| 2.12    | Test Register                                                                                                                         |              |

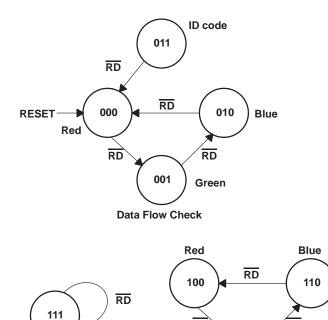

|         | 2.12.1 Frame Buffer Data Flow Test                                                                                                    |              |

|         | 2.12.2 Identification Code                                                                                                            |              |

|         | 2.12.3 Ones Accumulation Screen Integrity Test         2.12.4 Analog Test                                                             |              |

|         | 2.12.4 Analog Test                                                                                                                    | 2-19         |

| 3 Spec  | cifications                                                                                                                           | 3-1          |

| 3.1     | Absolute Maximum Ratings Over Operating Free-Air Temperature Range<br>(Unless Otherwise Noted)                                        | 3-1          |

| 3.2     | Recommended Operating Conditions                                                                                                      |              |

| 3.3     | Electrical Characteristics                                                                                                            |              |

| 3.4     | Operating Characteristics                                                                                                             | 3-3          |

| 3.5     | Timing Requirements                                                                                                                   | 3-4          |

| 3.6     | Switching Characteristics                                                                                                             | 3-5          |

|         | TL34075A-66, TLC34075A-85                                                                                                             |              |

|         | TL34075A-110, TLC34075A-135                                                                                                           |              |

| 3.7     | Timing Diagrams                                                                                                                       | 3-7          |

| Appendi | ix A SCLK/VCLK and the TMS340x0                                                                                                       | <b>A-1</b>   |

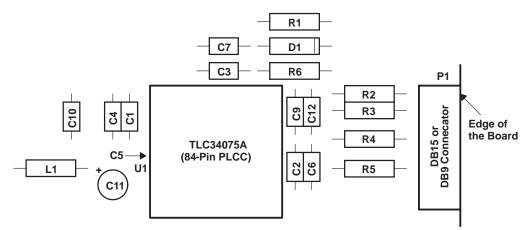

| Appendi | ix B PC Board Layout Considerations I                                                                                                 | B-1          |

| Appendi | ix C SCLK Frequency < VCLK Frequency                                                                                                  | C-1          |

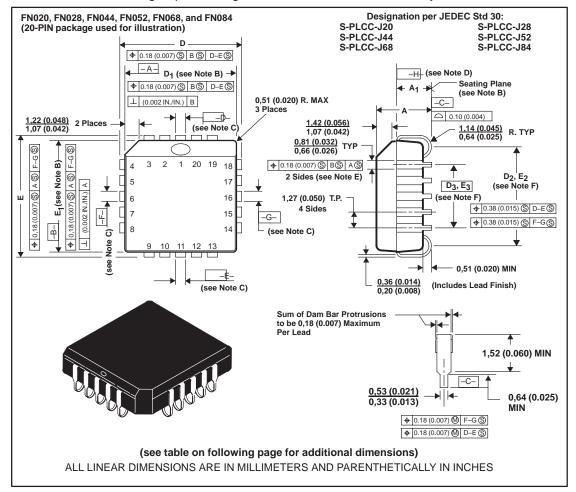

| Appendi | ix D Mechanical Data l                                                                                                                | D-1          |

ii

# List of Illustrations

| Figure | Title                                             | Page |

|--------|---------------------------------------------------|------|

| 1-1    | Functional Block Diagram                          | 1-2  |

| 1–2    | Terminal Assignments                              | 1-3  |

| 2-1    | DOTCLK/VCLK/SCLK Relationship                     | 2-3  |

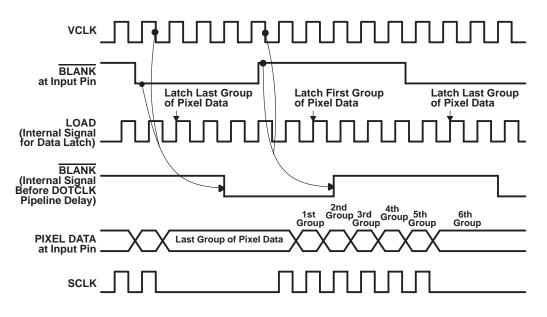

| 2-2    | SCLK/VCLK Control Timing                          | 2-5  |

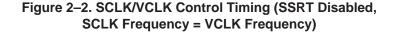

| 2–3    | SCLK/VCLK Control Timing                          | 2-6  |

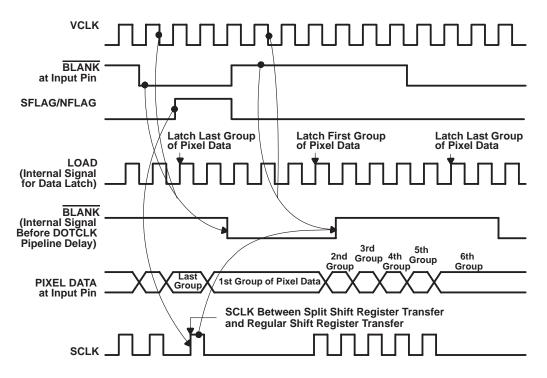

| 2–4    | SCLK/VCLK Control Timing                          | 2-6  |

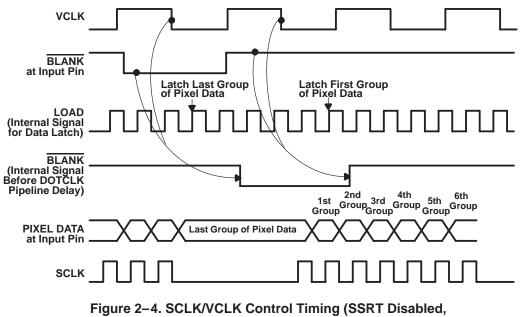

| 2–5    | SCLK/VCLK Control Timing                          | 2-7  |

| 2.6    | Equivalent Circuit of the IOG Current Output      | 2-12 |

| 2–7    | 7.5-IRE, 8-Bit Composite Video Output             | 2-13 |

| 2-8    | 0-IRE, 8-Bit Composite Video Output               | 2-13 |

| 2–9    | Relationship Between SFLAG/NFLAG, BLANK, and SCLK | 2-15 |

| 2–10   | SFLAG/NFLAG Timing in Special Nibble Mode         | 2-16 |

| 2–11   | Test Register Control Word State Diagrams         | 2-18 |

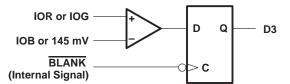

| 2–12   | Internal Comparator Circuitry for Analog Test     | 2-20 |

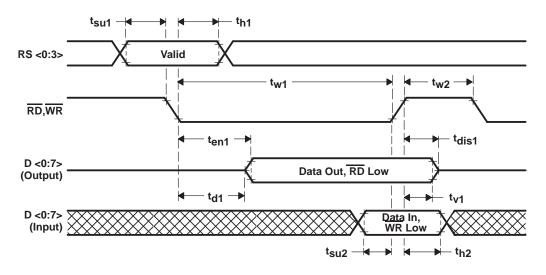

| 3–1    | MPU Interface Timing                              | 3-7  |

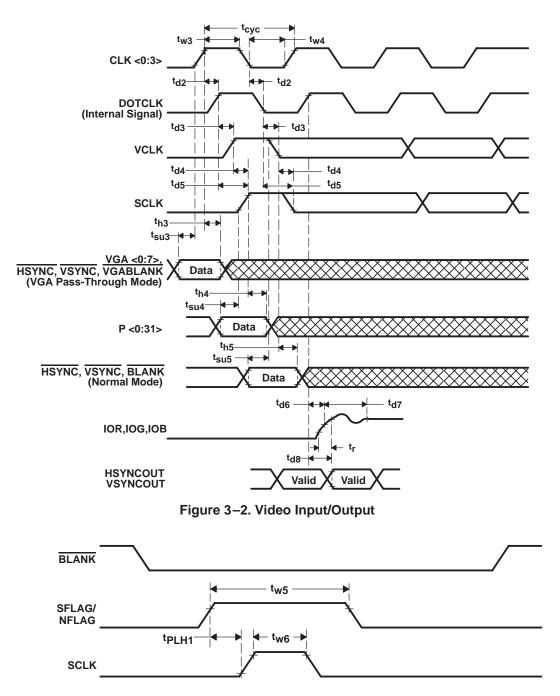

| 3–2    | Video Input/Output                                | 3-8  |

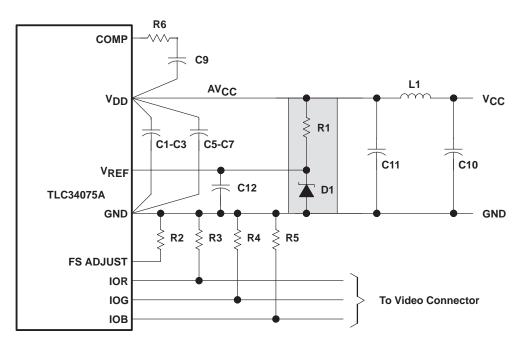

| 3–3    | SFLAG/NFLAG Timing                                | 3-8  |

# List of Tables

| Table | Title                                          | Page |

|-------|------------------------------------------------|------|

| 2-1   | Internal Register Map                          | 2-1  |

| 2-2   | Allocation of Palette Page Register Bits       | 2-2  |

| 2–3   | Input Clock Selection Register Format          | 2-3  |

| 2–4   | Output Clock Selection Register Format         | 2-4  |

| 2–5   | VCLK/SCLK Divide Ratio Selection               | 2-4  |

| 2–6   | Mode and Bus Width Selection                   | 2-9  |

| 2–7   | Pixel Data Distribution in Special Nibble Mode | 2-15 |

| 2-8   | General Control Register Bit Functions         | 2-17 |

| 2–9   | Test Mode Selection                            | 2-18 |

| 2–10  | Test Register Bit Definitions for Analog Test  | 2-20 |

| 2-11  | D<7:4> Bit Coding for Analog Comparisons       | 2-20 |

iv

.

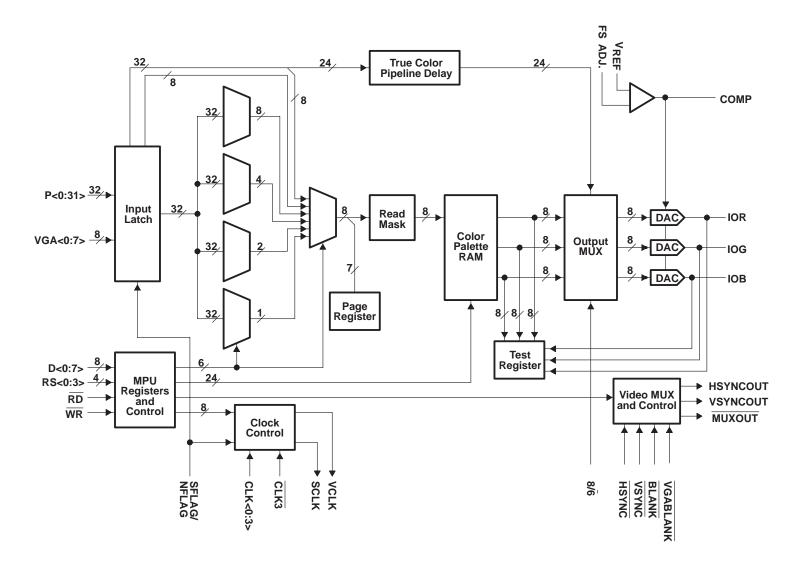

## 1 Introduction

The TLC34075A Video Interface Palette (VIP) is designed to provide lower system cost with a higher level of integration by incorporating all the high-speed timing, synchronizing, and multiplexing logic usually associated with graphics systems into one device, thus greatly reducing chip count. Since all high-speed signals (excluding the clock source) are contained on-chip, RF noise considerations are simplified. Maximum flexibility is provided through the pixel multiplexing scheme, which allows for 32-, 16-, 8-, and 4-bit pixel buses to be accommodated without any circuit modification. This enables the system to be easily reconfigured for varying amounts of available video RAM. Data can be split into 1, 2, 4, or 8 bit planes. The TLC34075A is software-compatible with the INMOS IMSG176/8 and Brooktree BT476/8 color palettes.

The TLC34075A features a separate VGA bus that allows data from the feature connector of most VGA-supported personal computers to be fed directly into the palette without the need for external data multiplexing. This allows a replacement graphics board to remain downward compatible by utilizing the existing graphics circuitry often located on the motherboard. The TLC34075A also provides a true color mode in which 24 (3 by 8) bits of color information are transferred directly from the pixel port to the DACs. This mode of operation supplies an overlay function using the 8 remaining bits of the pixel bus.

The TLC34075A has a 256-by-24 color lookup table with triple 8-bit video D/A converters capable of directly driving a doubly terminated 75- $\Omega$  line. Sync generation is incorporated on the green output channel. HSYNC and VSYNC are fed through the device and optionally inverted to indicate screen resolution to the monitor. A palette page register provides the additional bits of palette address when 1, 2, or 4 bit planes are used. This allows the screen colors to be changed with only one MPU write cycle.

Clocking is provided through one of four or five inputs (3 TTL- and either 1 ECL- or 2 TTL-compatible) and is software selectable. The video and shift clock outputs provide a software-selected divide ratio of the chosen clock input.

The TLC34075A can be connected directly to the serial port of VRAM devices, eliminating the need for any discrete logic. Support for split shift register transfers is also provided.

The TLC34075A is an optimized version of the original TLC34075 video interface palette. Because all of the critical speed paths have been strengthened on the device, a slightly higher  $I_{DD}$  current specification is required. The new specification also includes revised SCLK/VCLK timing and a clock counter reset function.

#### 1.1 Features

- Versatile multiplexing interface allows lower pixel bus rate

- High level of integration provides lower system cost and complexity

- Direct VGA pass-through capability

- Directly interfaces to TMS34010/TMS34020 and other graphics processors

- Triple 8-bit D/A converters

- 66-, 85-, 110-, and 135-MHz versions

- 256-word color palette RAM

- Palette page register

- On-chip voltage reference

- RS-343A-compatible outputs

- TTL-compatible inputs

- Standard MPU interface

- Pixel word mask

- On-chip clock selection

- True color (direct addressing) mode

- Directly interfaces to video RAM

- Supports split shift register transfers

- Software downward-compatible with INMOS IMSG176/8 and Brooktree BT476/8 color palettes

- TIGA<sup>™</sup>-software-standard compatible

- LinEPIC<sup>™</sup> 1-µm CMOS process

## 1.2 Functional Block Diagram

LinEPIC and TIGA are trademarks of Texas Instruments Incorporated.

Figure 1–1. Functional Block Diagram

-1 -¦3

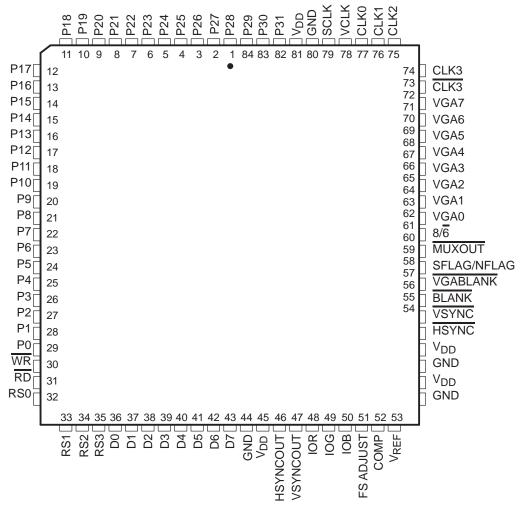

#### **1.3 Terminal Assignments**

#### 1.4 Ordering Information

TLC34075A – (X)XX AFN

#### Pixel clock frequency indicator —

MUST CONTAIN TWO OR THREE CHARACTERS:

- -66: 66-MHz pixel clock

- -85: 85-MHz pixel clock

- -110: 110-MHz pixel clock

- -135: 135-MHz pixel clock

#### Package

MUST CONTAIN TWO LETTERS:

FN: plastic, square, leaded chip carrier (formed leads)

# 1.5 Terminal Functions

| PIN NAME              | NO.               | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BLANK,<br>VGABLANK    | 60, 61            | I   | Blanking inputs. Two blanking inputs are provided in order to remove any external multiplexing of the signals that may cause data and blank to skew. When the VGA pass-through mode is set in the mux control register, the VGABLANK input is used for blanking; otherwise, BLANK is used.                                                                                               |  |

| CLK<0:2>              | 77, 76, 75        | I   | Dot clock inputs. Any of the three clocks can be used to drive the dot clock at frequencies up to 85 MHz. When VGA pass-through mode is active, CLK0 is used by default.                                                                                                                                                                                                                 |  |

| CLK3, CLK3            | 74, 73            | I   | Dual-mode dot clock input. This input is an ECL-compatible input, but a TTL clock may be used on either CLK3 or CLK3 if so selected in the input clock selection register. This input may be selected as the dot clock for any frequency of operation up to the device limit while in the ECL mode; it may only be used up to 85 MHz in the TTL mode.                                    |  |

| COMP                  | 52                | I   | Compensation input. This terminal provides compensation for the internal reference amplifier. A resistor and ceramic capacitor are required between this terminal and $V_{DD}$ . The resistor and capacitor must be as close to the device as possible to avoid noise pickup. Refer to Appendix B for more details.                                                                      |  |

| D<0:7>                | 36-43             | I/O | MPU interface data bus. Used to transfer data in and out of the register map and palette/overlay RAM.                                                                                                                                                                                                                                                                                    |  |

| FS ADJUST             | 51                | I   | Full-scale adjustment pin. A resistor connected between this pin and ground controls the full-scale range of the DACs.                                                                                                                                                                                                                                                                   |  |

| GND                   | 44, 54,<br>56, 80 |     | Ground. All GND pins must be connected. The analog and digital GND pins are connected internally.                                                                                                                                                                                                                                                                                        |  |

| HSYNCOUT,<br>VSYNCOUT | 46, 47            | 0   | Horizontal and vertical sync outputs of the true/complement gate mentioned in the HSYNC, VSYNC description below (see Section 2.8).                                                                                                                                                                                                                                                      |  |

| HSYNC, VSYNC          | 58, 59            | I   | Horizontal and vertical sync inputs. These signals are used to generate the sync level on the green current output. They are active-low inputs for the normal modes and are passed through a true/complement gate. For the VGA pass-through mode, they are passed through to HSYNCOUT and VSYNCOUT without polarity change as specified by the control register (see Section 2.8).       |  |

| IOR, IOG, IOB         | 48, 49, 50        | 0   | Analog current outputs. These outputs can drive a 37.5- $\Omega$ load directly (doubly terminated 75- $\Omega$ line), thus eliminating the need for any external buffering.                                                                                                                                                                                                              |  |

| MUXOUT                | 63                | 0   | MUX output control. This output pin is software programmable. It is set low to indicate to external devices that VGA pass-through mode is being used when the MUX control register value is set to 2Dh. If bit 7 of the general control register is set high after the mode is set, this output goes high. This pin is only used for external control; it affects no internal circuitry. |  |

| P<0:31>               | 29–1,<br>84–82    | I   | Pixel input port. This port can be used in various modes as shown in the MUX control register. It is recommended that unused pins be tied to ground to lower the device's power consumption.                                                                                                                                                                                             |  |

| RD                    | 31                | I   | Read strobe input. A low logic level on this pin initiates a read from the TLC34075A register map. Reads are performed asynchronously and are initiated on the falling edge of RD (see Figure 3–1).                                                                                                                                                                                      |  |

| RS<0:3>               | 32–35             | I   | Register select inputs. These pins specify the location in the register map that is to be accessed, as shown in Table 2–1.                                                                                                                                                                                                                                                               |  |

| SCLK                  | 79                | 0   | Shift clock output. This output is selected as a submultiple of the dot clock input. SCLK is gated off during blanking.                                                                                                                                                                                                                                                                  |  |

| PIN NAME        | NO.               | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFLAG/NFLAG     | 62                | I   | Split shift register transfer flag or nibble flag input. This pin has two functions. When the general control register bit $3 = 0$ and bit $2 = 1$ , split shift register transfer function is enabled and a low-to-high transition on this pin during a blank sequence initiates an extra SCLK cycle to allow a split shift register transfer in the VRAMs. When the general control register bit $3 = 1$ and bit $2 = 0$ , special nibble mode is enabled and this input is sampled at the falling edge of VCLK. A high value sampled indicates that the next SCLK rising edge should latch the high nibble of each byte of the pixel data bus; a low value sampled indicates that the low nibble of each byte of the pixel data bus should be latched (see Section 2.9). When the general control register bit $3 = 0$ and bit $2 = 0$ , this pin is ignored. The condition of bit $3 = 1$ , bit $2 = 1$ is not allowed, and device operation is unpredictable if they are so set. |

| VCLK            | 78                | 0   | Video clock output. User-programmable output for synchronization of the TLC34075A to a graphics processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DD</sub> | 45, 55,<br>57, 81 |     | Power. All $V_{DD}$ pins must be connected. The analog and digital $V_{DD}$ pins are connected internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VGA<0:7>        | 65-72             | I   | VGA pass-through bus. This bus can be selected as the pixel bus for VGA pass-through mode. It does not allow for any multiplexing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

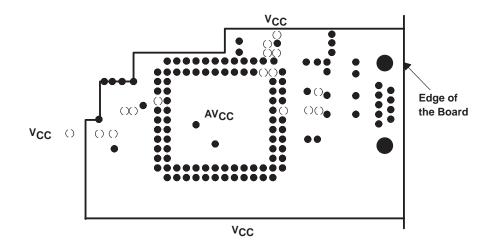

| VREF            | 53                |     | Voltage reference for DACs. An internal voltage reference of nominally 1.235 V is designed in. A 0.1- $\mu$ f ceramic capacitor between this terminal and GND is recommended for noise filtering using either the internal or an external reference voltage. The internal reference voltage can be overridden by an externally supplied voltage. The typical connection is shown in Appendix B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WR              | 30                | I   | Write strobe input. A low logic level on this pin initiates a write to the TLC34075A register map. Write transfers are asynchronous. The data written to the register map is latched on the rising edge of $\overline{\text{WR}}$ (see Figure 3–1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8/6             | 64                | Ι   | DAC resolution selection. This pin is used to select the data bus width (8 or 6 bits) for the DACs and is provided to maintain compatibility with the INMOS IMSG176/8 color palette. When this pin is at a high logic level, 8-bit bus transfers are used, with D<7> being the MSB and D<0> the LSB. For 6-bit bus operation, while the color palette still has the 8-bit information, D<5> shifts to the bit 2 position, and the two LSBs are filled with zeros at the output MUX to the DAC. When read in the 6-bit mode, the palette-holding register zeroes out the two MSBs.                                                                                                                                                                                                                                                                                                                                                                                                     |

NOTES: 1. Although leaving unused pins floating will not adversely affect device operation, tying unused pins to ground Iowers power consumption and, thus, is recommended.

All digital inputs and outputs are TTL-compatible, unless otherwise noted.

1-7

## 2 Detailed Description

### 2.1 MPU Interface

The processor interface is controlled via read and write strobes ( $\overline{RD}$ ,  $\overline{WR}$ ), four register select pins (RS<0:3>), and the 8/6 select pin. The 8/6 select pin is used to select between 8- or 6-bit operation and is provided in order to maintain compatibility with the IMSG176/8 color palette. This operation is carried out in order to utilize the maximum range of the DACs.

The internal register map is shown in Table 2–1. The MPU interface operates asynchronously, with data transfers being synchronized by internal logic. All the register locations support read and write operations.

| RS3 | RS2 | RS1 | RS0 | REGISTER ADDRESSED BY MPU             |

|-----|-----|-----|-----|---------------------------------------|

| L   | L   | L   | L   | Palette address register – write mode |

| L   | L   | L   | Н   | Color palette holding register        |

| L   | L   | Н   | L   | Pixel read mask                       |

| L   | L   | Н   | Н   | Palette address register – read mode  |

| L   | Н   | L   | L   | Reserved                              |

| L   | Н   | L   | Н   | Reserved                              |

| L   | Н   | Н   | L   | Reserved                              |

| L   | Н   | Н   | Н   | Reserved                              |

| Н   | L   | L   | L   | General control register              |

| Н   | L   | L   | Н   | Input clock selection register        |

| Н   | L   | Н   | L   | Output clock selection register       |

| Н   | L   | Н   | Н   | Mux control register                  |

| Н   | Н   | L   | L   | Palette page register                 |

| Н   | Н   | L   | Н   | Reserved                              |

| Н   | Н   | Н   | L   | Test register                         |

| Н   | Н   | Н   | Н   | Reset state                           |

Table 2–1. Internal Register Map

## 2.2 Color Palette RAM

The color palette RAM is addressed by two internal 8-bit registers, one for reading from the RAM and one for writing to the RAM. These registers are automatically incremented following a RAM transfer, allowing the entire palette to be read/written with only one access of the address register. When the address register increments beyond the last location in RAM, it is reset to the first location (address 0). Although all read and write accesses to the RAM are asynchronous to SCLK, VCLK, and the dot clock, they are performed within one dot clock and so do not cause any noticeable disturbance on the display.

The color palette RAM is 24 bits wide for each location (8 bits each for red, green, and blue). If 6-bit mode is chosen (8/6 = 1ow), the two MSBs are still written to the color palette RAM. However, if they are read back in the 6-bit mode, the two MSBs are set to 0 to maintain compatibility with the IMSG176/8 and BT476/8 color palettes. The output MUX shifts the six LSBs to the six MSB positions, fills the two LSBs with 0s, then feeds the eight bits to the DAC. With the 8/6 pin held low, data on the lowest six bits of the data bus are internally shifted up by two bits to occupy the upper six bits at the output MUX, and the bottom two bits are then zeroed. The test register and the ones accumulation register both take data before the output MUX to give the user the maximum flexibility.

The color palette RAM access methodology is described in the following two sections and is fully compatible with the IMSG176/8 and BT476/8 color palettes.

#### 2.2.1 Writing to the Color Palette RAM

To load the color palette RAM, the MPU must first write to the address register (write mode) with the address where the modification is to start. This action is followed by three successive writes to the palette-holding register with eight bits each of red, green, and blue data. After the blue data write cycle, the three bytes of color are concatenated into a 24-bit word and written to the color palette RAM location specified by the address register. The address register then increments to point to the next color palette RAM location, which the MPU may modify by simply writing another sequence of red, green, and blue data bytes. A block of color values in consecutive locations may be written to by writing the start address and performing continuous red, green, and blue write cycles until the entire block has been written.

### 2.2.2 Reading From the Color Palette RAM

Reading from the color palette RAM is performed by writing the location to be read to the address register. This action initiates a transfer from the color palette RAM into the holding register followed by an increment of the address register. Three successive MPU reads from the holding register produce red, green, and blue color data (six or eight bits, depending on the 8/6 mode) for the specified location. Following the blue read cycle, the contents of the color palette RAM at the address specified by the address register are copied into the holding register and the address register is again incremented. As with writing to the color palette RAM, a block of color values in consecutive locations may be read by writing the start address and performing continuous red, green, and blue read cycles until the entire block has been read.

#### 2.2.3 Palette Page Register

The 8-bit palette page register provides high-speed color changing by removing the need for color palette RAM reloading. When using 1, 2, or 4 bit planes, the additional planes are provided by the palette page register; e.g., when using four bit planes, the pixel inputs specify the lower four bits of the color palette RAM address with the upper four bits being specified by the palette register. This provides the capability of selecting from 16 palette pages with only one chip access, thus allowing all the screen colors to be changed at the line frequency. A bit-to-bit correspondence is used; therefore, in the above configuration, palette page register bits 7 through 4 map onto color palette RAM address bits 7 through 4, respectively. This is illustrated below.

NOTE: The additional bits from the palette page register are inserted before the read mask and hence, are subject to masking.

| NUMBER OF<br>BIT PLANES | msb | COLC | DR PAL | ETTE R | AM AD | DRESS | BITS | isb |

|-------------------------|-----|------|--------|--------|-------|-------|------|-----|

| 8                       | М   | М    | М      | М      | М     | М     | М    | М   |

| 4                       | P7  | P6   | P5     | P4     | М     | М     | Μ    | М   |

| 2                       | P7  | P6   | P5     | P4     | P3    | P2    | М    | М   |

| 1                       | P7  | P6   | P5     | P4     | P3    | P2    | P1   | М   |

Table 2–2. Allocation of Palette Page Register Bits

Pn = nth bit from palette page register

M = bit from pixel port

## 2.3 Input/Output Clock Selection and Generation

The TLC34075A provides a maximum of five clock inputs. Three are dedicated to TTL inputs; the other two can be selected as either one ECL input or two extra TTL inputs. The TTL inputs can be used for video rates up to 85 MHz, above which an ECL clock source must be used (although the ECL clock may also be used at lower frequencies). The dual-mode clock input (ECL/TTL) is primarily an ECL input but can be used as a TTL-compatible input if the input clock selection register is so programmed. The clock source used at power-up is CLK0; an alternative source can be selected by software during normal operation. This chosen clock input is used unmodified as the dot clock (representing the pixel rate to the monitor). The device does,

however, allow for user programming of the SCLK and VCLK outputs (shift and video clocks) via the output clock selection register. The input/output clock selection registers are shown in Tables 2–3, 2–4, and 2–5.

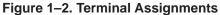

SCLK is designed to drive the VRAMs directly, and VCLK is designed to work with video control signals such as BLANK and the SYNCs. While SCLK and VCLK are designed as general-purpose shift clock and video clock, respectively, they also interface directly with the TMS340x0 GSP family. While SCLK and VCLK can be selected independently, there is still a relationship between the two. Internally, both SCLK and VCLK are generated from a common clock counter that increments on the rising edge of the DOTCLK. When VCLK is enabled and the VCLK and SCLK frequencies are programmed to be the same submultiple of the DOTCLK frequency, then VCLK and SCLK are in phase. When VCLK is enabled and the VCLK and SCLK frequencies are programmed to be different submultiples of the DOTCLK frequency, then there are simultaneous rising edges on the two waveforms at times determined by their frequency ratio (see Figure 2–1).

Appendix A discusses the SCLK/VCLK relationship specific to the TMS340x0 GSP.

|   | BIT | rs† |   |                                           |  |

|---|-----|-----|---|-------------------------------------------|--|

| 3 | 2   | 1   | 0 | FUNCTION <sup>‡</sup>                     |  |

| 0 | 0   | 0   | 0 | Select CLK0 as clock source§              |  |

| 0 | 0   | 0   | 1 | Select CLK1 as clock source               |  |

| 0 | 0   | 1   | 0 | Select CLK2 as clock source               |  |

| 0 | 0   | 1   | 1 | Select CLK3 as TTL clock source           |  |

| 0 | 1   | 0   | 0 | Select CLK3 as TTL clock source           |  |

| 1 | 0   | 0   | 0 | Select CLK3 and CLK3 as ECL clock sources |  |

Table 2–3. Input Clock Selection Register Format

<sup>†</sup>Register bits 4, 5, 6, and 7 are *don't care* bits.

<sup>‡</sup> When the clock selection is altered, a minimum 30-ns delay is incurred before the

new clocks are stabilized and running.

§ CLK0 is chosen at power-up to support the VGA pass-through mode.

The internal clock counter is initialized to value 0 any time the output clock-selection register (bits 5, 4, 2, 1) are all set to 1s. This provides a simple mechanism to synchronize multiple video interface palettes, by providing a known phase relationship for the various system clocks. One can write directly to the output clock selection register to cause this to occur, or any of the various resets (POR, hardware, software – see section 1.5) will also cause the appropriate bits to be written and the counters to reset. It is up to the user to provide some means of disabling the dot-clock input to the part while this reset is occurring, if multiple parts are to be synchronized.

|   |   | BIT | s† |   |   | FUNCTION <sup>‡</sup>                                     |  |  |

|---|---|-----|----|---|---|-----------------------------------------------------------|--|--|

| 5 | 4 | 3   | 2  | 1 | 0 | FUNCTION+                                                 |  |  |

| 0 | 0 | 0   | Х  | Х | Х | VCLK frequency = DOTCLK frequency                         |  |  |

| 0 | 0 | 1   | Х  | Х | Х | VCLK frequency = DOTCLK frequency/2                       |  |  |

| 0 | 1 | 0   | Х  | Х | Х | VCLK frequency = DOTCLK frequency/4                       |  |  |

| 0 | 1 | 1   | Х  | Х | Х | VCLK frequency = DOTCLK frequency/8                       |  |  |

| 1 | 0 | 0   | Х  | Х | Х | VCLK frequency = DOTCLK frequency/16                      |  |  |

| 1 | 0 | 1   | Х  | Х | Х | VCLK frequency = DOTCLK frequency/32                      |  |  |

| 1 | 1 | Х   | Х  | Х | Х | VCLK output held at logic high level (default condition)§ |  |  |

| Х | Х | Х   | 0  | 0 | 0 | SCLK frequency = DOTCLK frequency                         |  |  |

| Х | Х | Х   | 0  | 0 | 1 | SCLK frequency = DOTCLK frequency/2                       |  |  |

| Х | Х | Х   | 0  | 1 | 0 | SCLK frequency = DOTCLK frequency/4                       |  |  |

| Х | Х | Х   | 0  | 1 | 1 | SCLK frequency = DOTCLK frequency/8                       |  |  |

| Х | Х | Х   | 1  | 0 | 0 | SCLK frequency = DOTCLK frequency/16                      |  |  |

| Х | Х | Х   | 1  | 0 | 1 | SCLK frequency = DOTCLK frequency/32                      |  |  |

| Х | Х | Х   | 1  | 1 | Х | SCLK output held at logic level low (default condition)§  |  |  |

Table 2–4. Output Clock Selection Register Format

<sup>†</sup>Register bits 6 and 7 are *don't care* bits.

<sup>‡</sup>When the clock selection is altered, a minimum 30-ns delay is incurred before the new clocks are stabilized and running.

§ These lines indicate the power-up conditions required to support the VGA pass-through mode.

|              | (Output Clock Selection              | on Reg | lister v | alue in | Hex) |     |     |

|--------------|--------------------------------------|--------|----------|---------|------|-----|-----|

| SCLK<br>VCLK | BITS<br>2 0¶                         | 000    | 001      | 010     | 011  | 100 | 101 |

| BITS<br>53¶  | divide DOTCLK by<br>divide<br>DOTCLK | 1      | 2        | 4       | 8    | 16  | 32  |

| 000          | by 1                                 | 00     | 01       | 02      | 03   | 04  | 05  |

| 001          | 2                                    | 08     | 09       | 0A      | 0B   | 0C  | 0D  |

| 010          | 4                                    | 10     | 11       | 12      | 13   | 14  | 15  |

| 011          | 8                                    | 18     | 19       | 1A      | 1B   | 1C  | 1D  |

| 100          | 16                                   | 20     | 21       | 22      | 23   | 24  | 25  |

| 101          | 32                                   | 28     | 29       | 2A      | 2B   | 2C  | 2D  |

#### Table 2–5. VCLK/SCLK Divide Ratio Selection (Output Clock Selection Register Value in Hex)

¶ Output clock selection register bits

### 2.3.1 SCLK

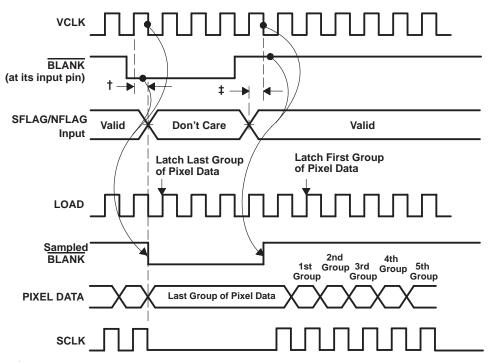

The TLC34075A latches data on the rising edge of the LOAD signal (LOAD is the same as SCLK but is not disabled while the BLANK signal is active). Therefore, SCLK must be set as a function of the pixel bus width and the number of bit planes. The SCLK frequency can be selected to be the same as the dot clock frequency or 1/2, 1/4, 1/8, 1/16, or 1/32 of the dot clock frequency. If SCLK is not used, the output is switched off and held low to protect against VRAM lock-up due to invalid SCLK frequencies. SCLK is also held low during the BLANK signal active period. The control timing has been designed to bring the first pixel data ready from the VRAM when BLANK is disabled and ready for the display. When split shift register transfer operation is used, SCLK is taken care of by working with SSRT input (see Section 2.9).

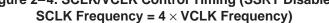

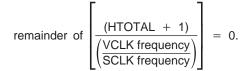

Refer to Figure 2–2 for the following timing explanation.

The falling edge of VCLK is used internally by the TLC34075A to sample and latch the BLANK input level. When BLANK goes low, SCLK is disabled as soon as possible. In other words, if the last SCLK pulse is at the high level while the sampled BLANK is low, SCLK is allowed to finish its cycle to low level, then SCLK is held low until the sampled BLANK goes back high to enable it again. The VRAM shift register should be updated during the BLANK active period, and the first SCLK pulse is used to clock the first valid pixel data from the VRAM. The internal pipeline delay of the BLANK input is designed to be in phase with data at the DAC output to the monitors. The logic described above works in situations wherein the SCLK period is shorter than, equal to, or longer than the VCLK period.

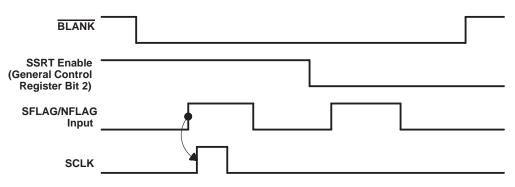

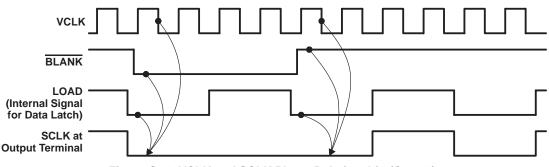

Figure 2–3 shows the case wherein the SSRT (split shift register transfer) function is enabled. One SCLK pulse with a minimum width of 15 ns is generated from the rising edge at the SFLAG input with specified delay. This is designed to meet the VRAM timing requirement, and this SCLK pulse replaces the first SCLK in the regular shift register transfer case as described above. Refer to Section 2.9 for the detailed explanation of the SSRT function.

The SCLK output waveform may vary at the time that the sampled BLANK input is low. Refer to Appendix C for details.

#### 2.3.2 VCLK

The VCLK frequency can be selected to be 1/1, 1/2, 1/4, 1/8, 1/16, or 1/32 of that of the dot clock, or it can be held at a high logic level. The default condition is for VCLK to be held at a high logic level. VCLK is not used in VGA pass-through mode.

VCLK is used by a GSP or custom-designed control logic to generate control signals (BLANK, HSYNC, and VSYNC). As can be seen from Figures 2–2, 2–3, 2–4, and 2–5, since the control signals are sampled by VCLK, it is obvious that VCLK has to be enabled.

NOTE: Either the SSRT function is disabled (general control register bit 2 = 0), or the SFLAG/NFLAG input is held low if the SSRT function is enabled (general control register bit 2 = 1).

NOTE: The SSRT function is enabled (general control register bit 2 = 1).

NOTE: Either the SSRT function is disabled (general control register bit 2 = 0), or the SFLAG/NFLAG input is held low if the SSRT function is enabled (general control register bit 2 = 1).

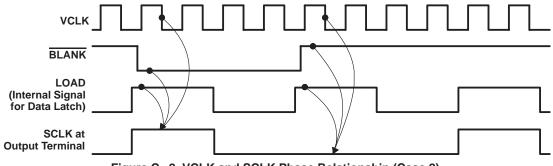

Figure 2–5. SCLK/VCLK Control Timing (SSRT Enabled, SCLK Frequency = 4 × VCLK Frequency)

#### 2.4 Multiplexing Scheme

The TLC34075A offers a highly versatile multiplexing scheme as illustrated in Table 2–6. The on-chip multiplexing allows the system to be reconfigured to the amount of RAM available. For example, if only 256K bytes of memory are available, an 800-by-600 mode with 4 bit planes (four bits per pixel) could be implemented using an 8-bit-wide pixel bus. If, at a later date, another 256K bytes are added to another eight bits of the pixel bus, the user has the option of using 8 bit planes at the same resolution or 4 bit planes at a 1024-by-768 resolution. When an additional 512K bytes is added to the remaining 16 bits of the pixel bus, the user has the option of 8 bit planes at 1024-by-768 or 4 bit planes at 1280 by 1024. All the above can be achieved without any hardware modification and without any increase in the speed of the pixel bus.

## 2.4.1 VGA Pass-Through Mode

Mode 0, the VGA pass-through mode, is used to emulate the VGA modes of most personal computers. The advantage of this mode is that the TLC34075A can take data presented on the feature connectors of most VGA-compatible PC systems into the device on a separate bus, thus requiring no external multiplexing. This feature is particularly useful for systems in which the existing graphics circuitry is on the motherboard. In this instance, it enables implementation of a drop-in graphics card that maintains compatibility with all existing software by using the on-board VGA circuitry but routing the emerging bit-plane data through the TLC34075A. This is the default mode at power-up. When the VGA pass-through mode is selected after the device is powered up, the clock selection register, the general control register, and the pixel read mask register are set to their default states automatically.

Since this mode is designed with the feature connector philosophy, all the timing is referenced to CLK0, which is used by default for VGA pass-through mode. For all the other normal modes, CLK <0:3> are the oscillator sources for DOTCLK, VCLK, and SCLK; all the data and control timing is referenced to SCLK.

#### 2.4.2 Multiplexing Modes

In addition to the VGA pass-through mode, there are four multiplexing modes available, all of which are referred to as normal modes. In each normal mode, a pixel bus width of 8, 16, or 32 bits may be used. Modes 1, 2, and 3 also support a pixel bus width of 4 bits. Data should always be presented on the least significant bits of the pixel bus. For example, when a 16-bit-wide pixel bus is used and there are 8 bits per pixel, each 8-bit pixel should be presented on P<0:7>. All the unused pixel bus pins should be connected to GND.

Mode 1 uses a single bit plane to address the color palette. The pixel port bit is fed into bit 0 of the palette address, with the 7 high-order address bits being defined by the palette page register (see Section 2.2.3). This mode has uses in high-resolution monochrome applications such as desktop publishing. This mode allows the maximum amount of multiplexing (a 32:1 ratio), thus giving a pixel bus rate of only 4 MHz at a screen resolution of 1280 by 1024. Although only a single bit plane is used, alteration of the palette page register at the line frequency allows 256 different colors to be displayed simultaneously with 2 colors per line.

Mode 2 uses 2 bit planes to address the color palette. The 2 bits are fed into the low-order address bits of the palette with the 6 high-order address bits being defined by the palette page register (see Section 2.2.3). This mode allows a maximum divide ratio of 16:1 on the pixel bus and is a 4-color alternative to mode 1.

Mode 3 uses 4 bit planes to address the color palette. The 4 bits are fed into the low-order address bits of the palette with the 4 high-order address bits being defined by the palette page register (see Section 2.2.3). This mode provides 16 pages of 16 colors and can be used at SCLK divide ratios of 1 to 8.

Mode 4 uses 8 bit planes to address the color palette. Since all 8 bits of palette address are specified from the pixel port, the page register is not used. This mode allows dot-clock-to-SCLK ratios of 1:1 (8-bit bus), 2:1 (16-bit bus) or 4:1 (32-bit bus). Therefore, in a 32-bit configuration, a 1024-by-768 pixel screen can be implemented with an external data rate of only 16 MHz.

#### 2.4.3 True Color Mode

Mode 5 is true color mode, in which 24 bits of data are transferred from the pixel port directly to the DACs with the same amount of pipeline delay as the overlay data and the control signals (BLANK and SYNCs). In this mode, overlay is provided by using the remaining 8 bits of the pixel bus to address the palette RAM, resulting in a 24-bit RAM output that is then used as overlay information to the DACs. When all the overlay inputs (P<0:7>) are at a low logic level or the pixel read mask register is loaded with the value 0, no overlay information is displayed; when a nonzero value is input with the pixel read mask enabled, the color palette RAM is addressed and the resulting data is then fed through to the DACs, receiving priority over the true color data.

The true-color-mode data input only works in the 8-bit mode. In other words, if only 6 bits are used, the 2 MSB inputs for each color should be tied to GND. However, the palette, which is used by the overlay input, is still governed by the 8/6 input pin, and the output MUX selects 8 bits of data or 6 bits of data accordingly.

In the true color mode, P<15:8> pass red data, P<23:16> pass green data, and P<31:24> pass blue data.

#### 2.4.4 Special Nibble Mode

Mode 6 is special nibble mode, which is enabled when the general control register SNM bit (bit 3) is set to 1 and the general control register SSRT bit (bit 2) is set to 0 (see Section 2.11). When special nibble mode is enabled, it takes precedence over the other modes, and the mux control register setup is ignored. The SFLAG/NFLAG input is then used as a nibble flag to indicate which nibble of each byte holds the pixel data. Special nibble mode is a variation of the 4-bit pixel mode with a 16-bit pixel width. All 32 inputs (P0 through P31) are connected as 4 bytes, but the 16-bit data bus is composed of either the lower or upper nibble of each of the 4 bytes. For more detailed information, refer to Section 2.9.2. Since this mode uses 4 bit planes for each pixel, they are fed into the low-order address bits of the palette, with the 4 high-order address bits being defined by the palette page register (see Section 2.2.3).

#### 2.4.5 Multiplex Control Register

The multiplexer is controlled via the 8-bit multiplex control register. The bit fields of the register are in Table 2–6.

| MODE | MU | X CON | TROL F | REGIST | FER BI | rs† | DATA BITS<br>PER<br>PIXEL <sup>‡</sup> | PIXEL BUS<br>WIDTH | SCLK<br>DIVIDE<br>RATIO§ | PIXEL<br>LATCHING<br>SEQUENCE¶                                                                                 |

|------|----|-------|--------|--------|--------|-----|----------------------------------------|--------------------|--------------------------|----------------------------------------------------------------------------------------------------------------|

|      | 5  | 4     | 3      | 2      | 1      | 0   |                                        |                    |                          |                                                                                                                |

| 0#   | 1  | 0     | 1      | 1      | 0      | 1   | 8                                      | 8                  | 1                        | 1) VGA<7:0>                                                                                                    |

|      | 0  | 1     | 0      | 0      | 0      | 0   | 1                                      | 4                  | 4                        | 1) P<0><br>2) P<1><br>3) P<2><br>4) P<3>                                                                       |

|      | 0  | 1     | 0      | 0      | 0      | 1   | 1                                      | 8                  | 8                        | 1) P<0><br>2) P<1><br><br>8) P<7>                                                                              |

| 1    | 0  | 1     | 0      | 0      | 1      | 0   | 1                                      | 16                 | 16                       | 1) P<0><br>2) P<1><br><br>16) P<15>                                                                            |

|      | 0  | 1     | 0      | 0      | 1      | 1   | 1                                      | 32                 | 32                       | 1) P<0><br>2) P<1><br><br>32) P<31>                                                                            |

|      | 0  | 1     | 0      | 1      | 0      | 0   | 2                                      | 4                  | 2                        | 1) P<1:0><br>2) P<3:2>                                                                                         |

|      | 0  | 1     | 0      | 1      | 0      | 1   | 2                                      | 8                  | 4                        | <ol> <li>1) P&lt;1:0&gt;</li> <li>2) P&lt;3:2&gt;</li> <li>3) P&lt;5:4&gt;</li> <li>4) P&lt;7:6&gt;</li> </ol> |

| 2    | 0  | 1     | 0      | 1      | 1      | 0   | 2                                      | 16                 | 8                        | 1) P<1:0><br>2) P<3:2><br><br>8) P<15:14>                                                                      |

|      | 0  | 1     | 0      | 1      | 1      | 1   | 2                                      | 32                 | 16                       | 1) P<1:0><br>2) P<3:2><br>;<br>16) P<31:30>                                                                    |

|      | 0  | 1     | 1      | 0      | 0      | 0   | 4                                      | 4                  | 1                        | 1) P<3:0>                                                                                                      |

|      | 0  | 1     | 1      | 0      | 0      | 1   | 4                                      | 8                  | 2                        | 1) P<3:0><br>2) P<7:4>                                                                                         |

| 3    | 0  | 1     | 1      | 0      | 1      | 0   | 4                                      | 16                 | 4                        | 1) P<3:0><br>2) P<7:4><br>3) P<11:8><br>4) P<15:12>                                                            |

|      | 0  | 1     | 1      | 0      | 1      | 1   | 4                                      | 32                 | 8                        | 1) P<3:0><br>2) P<7:4><br><br>8) P<31:28>                                                                      |

Table 2–6. Mode and Bus Width Selection

| MODE | MUX CONTROL REGISTER BITS <sup>†</sup> |   |   |   |   | тѕ† | DATA BITS<br>PER<br>PIXEL <sup>‡</sup> | PIXEL BUS<br>WIDTH | SCLK<br>DIVIDE<br>RATIO <sup>§</sup> | PIXEL<br>LATCHING<br>SEQUENCE¶                                       |

|------|----------------------------------------|---|---|---|---|-----|----------------------------------------|--------------------|--------------------------------------|----------------------------------------------------------------------|

|      | 5                                      | 4 | 3 | 2 | 1 | 0   |                                        |                    |                                      |                                                                      |

|      | 0                                      | 1 | 1 | 1 | 0 | 0   | 8                                      | 8                  | 1                                    | 1) P<7:0>                                                            |

| 4    | 0                                      | 1 | 1 | 1 | 0 | 1   | 8                                      | 16                 | 2                                    | 1) P<7:0><br>2) P<15:8>                                              |

|      | 0                                      | 1 | 1 | 1 | 1 | 0   | 8                                      | 32                 | 4                                    | 1) P<7:0><br>2) P<15:8><br>3) P<23:16><br>4) P<31:24>                |

| 5    | 0                                      | 0 | 1 | 1 | 0 | 1   | 24                                     | 32                 | 1                                    | 1) P<31:8>                                                           |

| 6    | 0                                      | 1 | 1 | 1 | 1 | 1   | 4                                      | 16                 | 4                                    | NFLAG = 0:<br>1) P<3:0><br>2) P<11:8><br>3) P<19:16><br>4) P<27:24>  |

|      |                                        |   |   |   |   |     |                                        |                    |                                      | NFLAG = 1:<br>1) P<7:4><br>2) P<15:12><br>3) P<23:20><br>4) P<31:28> |

Table 2–6. Mode and Bus Width Selection (Continued)

<sup>†</sup>Bits 6 and 7 are *don't care* bits.

<sup>‡</sup> This is the number of bits of pixel port (or VGA port in mode 1) information used as color data for each displayed pixel, often referred to as the number of bit planes. This may be color palette address data (Modes 0–4 and 6) or DAC data (mode 5).

S The SCLK divide ratio is the number used for the output clock selection register. It indicates the number of pixels per bus load, or the number of pixels associated with each SCLK pulse. For example, with a 32-bit pixel bus width and 8 bit planes, 4 pixels comprise each bus load. The SCLK divide ratio is not automatically set by mode selection, but must be written to the output clock selection register.

<sup>¶</sup> For each operating mode, the pixel latching sequence indicates the sequence in which pixel port or VGA port data are latched into the device. The latching sequence is initiated by a rising edge on SCLK. For modes in which multiple groups of data are latched, the SCLK rising edge latches all the groups, and the pixel clock shifts them out starting with the low-numbered group. For example, in mode 3 with a 16-bit pixel bus width, the rising edge of SCLK latches all the data groups, and the pixel clock shifts them out in the order P<3:0>, P<7:4>, P<11:8>, P<15:12>.

<sup>#</sup> Mode 0 is VGA pass-through mode.

Mode 5 is true color mode, in which 24 bits of color information are transferred directly from the pixel port to the DACs; overlay is implemented with the remaining 8 bits of the pixel bus. The distribution of pixel port data to the DACs is as follows: P<31:24> are passed to the blue DAC, P<23:16> are passed to the green DAC, and P<15:8> are passed to the red DAC. P<7:0> are used to generate overlay data; this operation can be disabled by either grounding P<7:0> or by clearing the read mask (see Section 1.4.5).

☆ Mode 6 is special nibble mode, the only mode in which the pixel bus width is not equal to the actual physical width, in bits, of the pixel bus. In this mode, the pixel bus is physically 32 bits wide; depending on the value of SFLAG/NFLAG, either the upper or lower nibble of each of the four physical bytes is selected to comprise the 16 bits of pixel data (equal to four 4-bit pixels).

NOTE: Although leaving unused pins floating will not adversely affect device operation, tying unused pins to ground lowers power consumption and, thus, is recommended.

#### 2.4.5 Multiplex Control Register (Continued)

As an example of how to use Table 2–6, suppose that the design goals specify a system with eight data bits per pixel and the lowest possible SCLK rate. Table 2–6 shows that, for non-VGA-pass-through operation, only mode 4 supports an eight-bit pixel depth. The lowest-possible SCLK rate within mode 4 is 1:4. This set of conditions is selected by writing the value 1Eh to the mux control register. The pixel latching sequence column shows that, in this mode, P<7:0> should be connected to the earliest-displayed pixel plane, followed by P<15:8>, P<23:16>, and then P<31:24> as the last displayed pixel plane. Assuming that VCLK is programmed as DOTCLK/4, Table 2–5 shows that the 1:4 SCLK ratio is selected by writing the value 12h to the output clock selection register. The special nibble mode should also be disabled (see Sections 2.9.2 and 2.11.2).

When the multiplex control register is loaded with 2Dh, the TLC34075A enters the VGA pass-through mode (the same condition as the default power-up mode). Please refer to Section 2.5.4 for more details.

#### 2.4.6 Read Masking

The read mask register is used to enable or disable a pixel address bit from addressing the color palette RAM. Each palette address bit is logically ANDed with the corresponding bit from the read mask register before addressing the palette. This function is performed after the addition of the page register bits and, therefore, a zeroing of the read mask results in one unique palette location (location 0) and is not affected by the palette page register contents.

### 2.5 Reset

There are 3 ways to reset the TLC34075A:

- 1. Power-on reset

- 2. Hardware reset

- 3. Software reset

The default reset condition is VGA mode, and the values for each register are shown in Section 2.5.4. Note also that, when the TLC34075A is reset, the SCLK and VCLK counters are reset. See Section 2.3.

## 2.5.1 Power-On Reset

The TLC34075A contains a power-on reset circuit. Once the voltage levels have stabilized following power-on reset, the device is in the VGA pass-through mode.

#### 2.5.2 Hardware Reset

The TLC34075A resets whenever RS<3:0> = HHHH and a rising edge occurs on the  $\overline{WR}$  input. The more rising  $\overline{WR}$  edges occur, the more reliable the TLC34075A is reset. This scheme (bursting  $\overline{WR}$  strobes until the power supply voltage stablizes) is suggested at power-up if a hardware reset approach is used.

#### 2.5.3 Software Reset

Whenever the mux control register is set for VGA pass-through mode after power-up, all registers are initialized accordingly. Since VGA pass-through mode is the default condition at power-up and hardware reset, the act of selecting the VGA pass-through mode through programming the mux control register is viewed as a software reset. Therefore, whenever mux control register bits <5:0> are set to 2Dh, the TLC34075A initiates a software reset.

## 2.5.4 VGA Pass-Through Mode Default Conditions

The value contained in each register after hardware or software reset is shown below:

| Mux control register:            | 2Dh |

|----------------------------------|-----|

| Input clock selection register:  | 00h |

| Output clock selection register: | 3Fh |

| Palette page register:           | 00h |

General control register:03hPixel read mask register:FFhPalette address register:xxhPalette holding register:xxhTest register:(Pointing to color palette red value)

### 2.6 Frame Buffer Interface

The TLC34075A provides two clock signals for controlling the frame buffer interface: SCLK and VCLK. SCLK can be used to clock out data directly from the VRAM shift registers. Split shift register transfer functionality is also supported. VCLK is used to clock and synchronize control inputs like HSYNC, VSYNC, and BLANK.

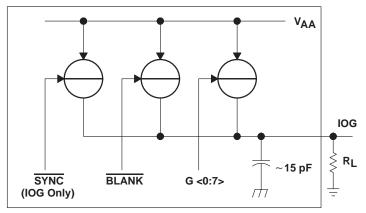

The pixel data presented at the inputs is latched at the rising edge of SCLK in normal mode or the rising edge of CLK0 in VGA pass-through mode. Control inputs HSYNC, VSYNC, and BLANK are sampled and latched at the falling edge of VCLK in normal mode, while HSYNC, VSYNC, and VGABLANK are latched at the rising edge of CLK0 in VGA pass-through mode. Both data and control signals are lined up at the DAC outputs to the monitors through the internal pipeline delay, so external glue logic is not required. The outputs of the DACs are capable of directly driving a 37.5- $\Omega$  load, as in the case of a doubly terminated 75- $\Omega$  cable. See Figures 2–7 and 2–8 for nominal output levels.

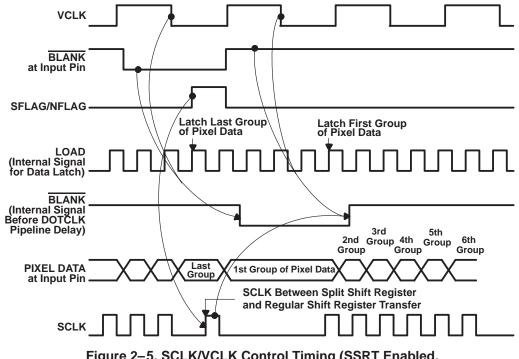

## 2.7 Analog Output Specifications

The DAC outputs are controlled by current sources (three for IOG and two each for IOR and IOB) as shown in Figure 2–6. In the normal case, there is a 7.5-IRE difference between blank and black levels, which is shown in Figure 2–7. If a 0-IRE pedestal is desired, it can be selected by resetting bit 4 of the general control register (see Section 2.11.3). The video output for a 0-IRE pedestal is shown in Figure 2–8.

Figure 2–6. Equivalent Circuit of the IOG Current Output

NOTE: 75- $\Omega$  doubly terminated load. V<sub>REF</sub> = 1.235 V, R<sub>SET</sub> = 523  $\Omega$ . RS-343A levels and tolerances are assumed.

#### 2.7 Analog Output Specifications (Continued)

A resistor ( $R_{SET}$ ) is needed to connect the FS ADJ pin to GND to control the magnitude of the full-scale video signal. The IRE relationships in Figures 2–7 and 2–8 are maintained regardless of the full-scale output current.

The relationship between R<sub>SET</sub> and the full-scale output current IOG is:

$R_{SET}(\Omega) = K1 \times V_{REF}(V) / IOG (mA)$

The full-scale output current on IOR and IOB for a given R<sub>SET</sub> is:

IOR, IOB (mA) = K2  $\times$  V<sub>REF</sub> (V) / R<sub>SET</sub> ( $\Omega$ )

where K1 and K2 are defined as:

|          | IO           | G            | IOR, IOB     |              |  |

|----------|--------------|--------------|--------------|--------------|--|

| PEDESTAL | 8-BIT OUTPUT | 6-BIT OUTPUT | 8-BIT OUTPUT | 6-BIT OUTPUT |  |

| 7.5-IRE  | K1 = 11,294  | K1 = 11,206  | K2 = 8,067   | K2 = 7,979   |  |

| 0-IRE    | K1 = 10,684  | K1 = 10,600  | K2 = 7,462   | K2 = 7,374   |  |

## 2.8 HSYNC, VSYNC, and BLANK

For the normal modes, HSYNC and VSYNC are active-low pulses, and they are passed through true/complement gates to the HSYNCOUT and VSYNCOUT outputs. The output polarities of HSYNCOUT and VSYNCOUT can be programmed through the general control register. However, for the VGA pass-through mode, the polarities needed for monitors are already provided at the feature connector from which HSYNC and VSYNC are sourced, so the TLC34075A just passes HSYNC and VSYNC through to HSYNCOUT and VSYNCOUT without polarity change. As described in Section 2.3 and Figures 2–2 through 2–5, the BLANK, HSYNC, and VSYNC inputs are sampled and latched on the falling edge of VCLK in the normal modes, and they are latched on the rising edge of the CLK0 input in the VGA pass-through mode. Refer to Figure 3–2 for the detailed timing.

The HSYNC and VSYNC inputs are used for both the VGA pass-through and normal modes. If the application uses both VGA pass-through and normal modes, an external multiplexer is needed to select HSYNC and VSYNC between VGA pass-through mode and normal mode. The MUXOUT signal is designed for this purpose (see Sections 2.10 and 2.11).

The HSYNC, VSYNC, and BLANK signals have internal pipeline delays to align the data at the outputs. Due to the sample and latch timing delay, it is possible to have active SCLK pulses after the BLANK input becomes active. The relationship between VCLK and SCLK and the internal VCLK sample and latch delay need to be carefully reviewed and programmed. See Section 2.3 and Figures 2–2 and 2–3 for more details.

As shown in Figure 2–6 for the IOG DAC output, active HSYNC and VSYNC signals turn off the sync current source (after the pipeline delay) independent of the BLANK signal level. In real applications, HSYNC and VSYNC should only be active (low) when BLANK is active (low).

To alter the polarity of the HSYNCOUT and VSYNCOUT outputs in the normal modes, the MPU must set or clear the corresponding bits in the general control register (see Section 2.11.1). Again, these two bits affect only the normal modes, not the VGA pass-through mode. These bits default to 1.

### 2.9 Split Shift Register Transfer VRAMs and Special Nibble Mode

#### 2.9.1 Split Shift Register Transfer VRAMs

The TLC34075A directly supports split shift register transfer (SSRT) VRAMs. In order to allow the VRAMs to perform a split shift register transfer, an extra SCLK cycle must be inserted during the blank sequence. This is initiated when the SSRT enable bit (bit 2 in the general control register) is set to 1, the SNM bit (bit 3 in the general control register) is reset to 0 (see Section 2.11), and a rising edge on the SFLAG/NFLAG input pin is detected. An SCLK pulse is generated within 20 ns of the rising edge of the SFLAG/NFLAG signal. A minimum 15-ns high logic level duration is provided to satisfy all of the –15 VRAM requirements. By controlling the SFLAG/NFLAG rise time, the delay time from the rising edge of the VRAM TRG signal to SCLK can be satisfied. The relationship between the SCLK, SFLAG/NFLAG, and BLANK signals is as follows:

Figure 2–9. Relationship Between SFLAG/NFLAG, BLANK, and SCLK

If SFLAG/NFLAG is designed as an R-S latch set by split shift register transfer timing and reset by BLANK going high, the delay from BLANK high to SFLAG/NFLAG low cannot exceed one-half of one SCLK cycle; otherwise, the SCLK generation logic may fail.

If the SSRT function is enabled but SFLAG/NFLAG is <u>held low</u>, SCLK runs as if the SSRT function is disabled. The SFLAG/NFLAG input is not qualified by the BLANK signal and needs to be held low whenever an SSRT SCLK pulse is not desired. Refer to Section 2.3.1 and Figures 2–2 through 2–8 for more system details.

### 2.9.2 Special Nibble Mode

Special nibble mode is enabled when the SNM bit (bit 3 in the general control register) is set to 1 and the SSRT bit (bit 2 in the general control register) is reset to 0 (see Section 2.11). Special nibble mode provides a variation of the 4-bit pixel mode with a 16-bit bus width. While all 32 inputs (P<0:31>) are connected as 4 bytes, the 16-bit data bus is composed of the lower or upper nibble of each of the 4 bytes, depending on the level of the SFLAG/NFLAG input. The pixel data is distributed to 16-bit data bus as shown in Table 2–7.

| SNM BIT = 1,    | SSRT BIT = 0    |

|-----------------|-----------------|

| SFLAG/NFLAG = 1 | SFLAG/NFLAG = 0 |

| P<7:4>          | P<3:0>          |

| P<15:12>        | P<11:8>         |

| P<23:20>        | P<19:16>        |

| P<31:28>        | P<27:24>        |

Table 2–7. Pixel Data Distribution in Special Nibble Mode

The SFLAG/NFLAG value is not latched by the TLC34075A. Therefore, it should stay at the same level during the whole active display period, changing levels only during the BLANK signal active time. Refer to Figure 2–10, which is similar to Figure 2–2 except that the BLANK signal timing reference to SFLAG/NFLAG is explained. The SFLAG/NFLAG input has to meet the setup time and hold the data long enough to ensure that no pixel data is missed.

Special nibble mode operates at the line frequency when BLANK is active. However, the typical application of this mode is double frame buffers with pixel data width of 4 bits. While one frame buffer is being displayed on the monitor, the other frame buffer can be used to accept new picture information. SFLAG/NFLAG is used to indicate which frame buffer is being displayed.

SNM and SSRT must be mutually exclusive. Unpredictable operation occurs if both the SNM and SSRT bits are set to 1. The mux control register should be set up as shown in Table 2–6 (see Section 2.4.5). However, the SNM bit takes precedence over the other mux control register selections. In other words, if the mux control register is set up for another mode but special nibble mode is still enabled in the general control register, the input multiplex circuit takes whatever SCLK divide ratio the mux control register specifies and performs the nibble operation, causing operational failure.

During special nibble mode, the input mux circuit latches all 8-bit inputs but only passes on the specified nibble. The specified nibble is stored in the 4 LSBs of the next register pipe after the input latch, and the 4 MSBs are zeroed in that register. The register pipe contents are then passed to the read mask block. With this structure, the palette page register still functions normally, providing good flexibility to users.

If the general control register bit 3 = 0 and bit 2 = 0, both split shift register transfers and special nibble mode are disabled and the SFLAG/NFLAG input is ignored.

<sup>†</sup> CAUTION:

If the data is not held valid until SCLK and BLANK both go low, the last few pixels could be missed.