TL16C552 DUAL ASYCHRONOUS COMMUNICATIONS ELEMENT WITH FIFO SLLS102B – DECEMBER 1990 – REVISED MARCH 1996

- IBM PC/AT<sup>™</sup> Compatible

- Two TL16C550 ACEs

- Enhanced Bidirectional Printer Port

- 16-Byte FIFOs Reduce CPU Interrupts

- Independent Control of Transmit, Receive, Line Status, and Data Set Interrupts on Each Channel

- Individual Modem Control Signals for Each Channel

- Programmable Serial Interface Characteristics for Each Channel:

- 5-, 6-, 7-, or 8-bit Characters

- Even-, Odd-, or No-Parity Bit Generation and Detection

- 1-, 1 1/2-, or 2-Stop Bit Generation

- 3-State TTL Drive for the Data and Control Bus on Each Channel

- Hardware and Software Compatible With TL16C452

## description

### description

The TL16C552 is an enhanced dual channel version of the popular TL16C550 asynchronous communications element (ACE). The device serves two serial input/output interfaces simultaneously in microcomputer or microprocessor-based systems. Each channel performs serial-to-parallel conversion on data characters

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

IBM PC/AT is a trademark of International Business Machines Corporation.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### description (continued)

received from peripheral devices or modems and parallel-to-serial conversion on data characters transmitted by the CPU. The complete status of each channel of the dual ACE can be read at any time during functional operation by the CPU. The information obtained includes the type and condition of the transfer operations being performed and the error conditions.

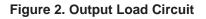

In addition to its dual communications interface capabilities, the TL16C552 provides the user with a fully bidirectional parallel data port that fully supports the parallel Centronics-type printer. The parallel port and the two serial ports provide IBM PC/AT-compatible computers with a single device to serve the three system ports.

A programmable baud rate generator is included that can divide the timing reference clock input by a divisor between 1 and  $(2^{16} - 1)$ .

The TL16C552 is housed in a 68-pin plastic leaded chip carrier.

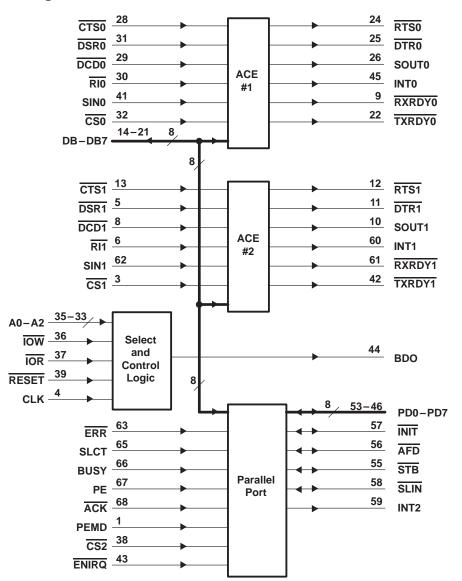

#### functional block diagram

SLLS102B - DECEMBER 1990 - REVISED MARCH 1996

## **Terminal Functions**

| TERMIN        |            | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO.        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACK           | 68         | Ι   | Line printer acknowledge. ACK goes low to indicate a successful data transfer has taken place. It generates a printer port interrupt during its positive transition.                                                                                                                                                                                                                                                                                   |

| AFD           | 56         | I/O | Line printer autofeed. $\overline{\text{AFD}}$ is an open-drain line that provides the printer with an active-low signal when continuous form paper is to be autofed to the printer. This terminal has an internal pullup resistor to V <sub>DD</sub> of approximately 10 k $\Omega$ .                                                                                                                                                                 |

| A0, A1, A2    | 35, 34, 33 | I   | Address lines A0–A2. A0, A1, and A2 select the internal registers during CPU bus operations. See Table 2 for the decode of the serial channels and Table 13 for the decode of the parallel printer port.                                                                                                                                                                                                                                               |

| BDO           | 44         | 0   | Bus buffer output. BDO is an active-high output that is asserted when either serial channel or the parallel port is read. This output can control the system bus driver (74LS245).                                                                                                                                                                                                                                                                     |

| BUSY          | 66         | I   | Line printer busy. BUSY is an input line from the printer that goes high when the printer is not ready to accept data.                                                                                                                                                                                                                                                                                                                                 |

| CLK           | 4          | I   | Clock input. CLK is an external clock input to the baud rate divisor of each ACE.                                                                                                                                                                                                                                                                                                                                                                      |

| CS0, CS1, CS2 | 32, 3, 38  | I   | Chip selects. $\overline{CS0}$ , $\overline{CS1}$ , and $\overline{CS2}$ act as an enable for the write and read signals for the serial channels 1 ( $\overline{CS0}$ ) and 2 ( $\overline{CS1}$ ). $\overline{CS2}$ enables the signals to the printer port.                                                                                                                                                                                          |

| CTSO, CTS1    | 28, 13     | Ι   | Clear to send inputs. The logical state of $\overline{\text{CTS0}}$ or $\overline{\text{CTS1}}$ is reflected in the CTS bit of the modem status register (CTS is bit 4 of the modem status register, written MSR4) of each ACE. A change of state in either CTS terminal, since the previous reading of the associated modem status register, causes the setting of delta clear to send ( $\Delta$ CTS) bit (MSR0) of each modem status register.      |

| DB0 – DB7     | 14 – 21    | I/O | Data bits DB0 – DB7. The data bus provides eight 3-state I/O lines for the transfer of data, control, and status information between the TL16C552 and the CPU. These lines are normally in a high-impedance state except during read operations. D0 is the least significant bit (LSB) and is the first serial data bit to be received or transmitted.                                                                                                 |

| DCD0, DCD1    | 29, 8      | I   | Data carrier detect. DCD is a modem input. Its condition can be tested by the CPU by reading the MSR7 (DCD) bit of the modem status registers. The MSR3 (delta data carrier detect or $\triangle$ DCD) bit of the modem status register indicates whether the DCD input has changed states since the previous reading of the modem status register. DCD has no affect on the receiver.                                                                 |

| DSR0, DSR1    | 31, 5      | I   | Data set ready inputs. The logical state of DSR0 and DSR1 is reflected in MSR5 of its associated modem status register. The MSR1 (delta data set ready or $\Delta$ DSR) bit indicates whether the associated DSR terminal has changed states since the previous reading of the modem status register.                                                                                                                                                  |

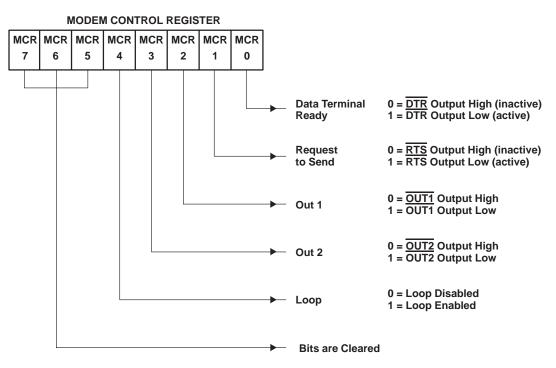

| DTR0, DTR1    | 25, 11     | 0   | Data terminal ready lines. DTR0 and DTR1 can be asserted low by setting modem control register bit 0 (MCR0) of its associated ACE. This signal is asserted high by clearing the DTR bit (MCR0) or whenever a reset occurs. When active (low), the DTR terminal indicates that its ACE is ready to receive data.                                                                                                                                        |

| ENIRQ         | 43         | I   | Parallel port interrupt source mode selection. When ENIRQ is low, the PC/AT mode of interrupts is enabled. In this mode, the INT2 output is internally connected to the ACK input. When the ENIRQ input is tied high, the INT2 output is internally tied to the PRINT signal in the line printer status register. INT2 is latched high on rising edge of ACK.                                                                                          |

| ERR           | 63         | I   | Line printer error. ERR is an input line from the printer. The printer reports an error by holding this line low during the error condition.                                                                                                                                                                                                                                                                                                           |

| GND           | 7, 27, 54  |     | Ground (0 V). All terminals must be tied to ground for proper operation.                                                                                                                                                                                                                                                                                                                                                                               |

| INIT          | 57         | I/O | Line printer initialize. INIT is an open-drain line that provides the printer with an active-low signal, which allows the printer initialization routine to be started. This terminal has an internal pullup resistor to $V_{DD}$ of approximately 10 k $\Omega$ .                                                                                                                                                                                     |

| ĪOR           | 37         | I   | Input/output read strobe. $\overline{\text{IOR}}$ is an active-low input that enables the selected channel to output data to the data bus (DB0–DB7). The data output depends upon the register selected by the address inputs A0, A1, A2, and chip select. Chip select 0 ( $\overline{\text{CS0}}$ ) selects ACE #1, chip select 1 ( $\overline{\text{CS1}}$ ) selects ACE #2, and chip select 2 ( $\overline{\text{CS2}}$ ) selects the printer port. |

| IOW           | 36         | I   | Input/output write strobe. $\overline{IOW}$ is an active-low input causing data from the data bus to be input to either ACE or to the parallel port. The destination depends upon the register selected by the address inputs A0, A1, A2, and chip selects $\overline{CS0}$ , $\overline{CS1}$ , and $\overline{CS2}$ .                                                                                                                                |

## TL16C552 DUAL ASYCHRONOUS COMMUNICATIONS ELEMENT WITH FIFO SLLS102B – DECEMBER 1990 – REVISED MARCH 1996

**Terminal Functions (continued)**

| TERMIN            | AL     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.    | 0   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTO, INT1        | 45, 60 | 0   | Serial channel interrupts. INT0 and INT1 are 3-state serial channel interrupt outputs (enabled by bit 3 of the MCR) that go active (high) when one of the following interrupts has an active (high) condition and is enabled by the interrupt enable register of its associated channel: receiver error flag, received data available, transmitter holding register empty, and modem status. The interrupt is cleared upon appropriate service. When reset, the interrupt output is in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INT2              | 59     | 0   | Printer port interrupt. INT2 is an active-high, 3-state output generated by the positive transition of ACK. It is enabled by bit 4 of the write control register. Upon a reset, the interrupt output is in the high-impedance state. Its mode is also controlled by ENIRQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PD0-PD7           | 53-46  | I/O | Parallel data bits $(0-7)$ . These eight lines (PD0-PD7) provide a byte wide input or output port to the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PE                | 67     | 1   | Printer paper empty. PE is an input line from the printer that goes high when the printer runs out of paper.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PEMD              | 1      | I   | Printer enhancement mode. When low, PEMD enables the write data register to the PD0–PD7 lines. A high on this signal allows direction control of the PD0–PD7 port by the DIR bit in the control register. PEMD is usually tied low for the printer operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RESET             | 39     | I   | Reset. When low, RESET forces the TL16C552 into an idle mode in which all serial data activities are suspended. The modem control register along with its associated outputs are cleared. The line status register is cleared except for the THRE and TEMT bits, which are set. All functions of the device remain in an idle state until programmed to resume serial data activities. This input has a hysteresis level of typically 400 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RTS0, RTS1        | 24, 12 | 0   | Request to send outputs. RTSx is asserted low by setting MCR1, bit 1 of its UARTs modem control register. Both RTSx terminals are set by RESET. A low on the RTSx terminal indicates that its ACE has data ready to transmit. In half-duplex operations, RTSx controls the direction of the line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RXRDY0,<br>RXRDY1 | 9, 61  | 0   | Receiver ready. RXRDY0 and RXRDY1 are receiver direct memory access (DMA) signaling terminals. One of two types of DMA signaling can be selected using FIFO control register bit 3 (FCR3) when operating in the FIFO mode. Only DMA mode 0 is allowed when operating in the TL16C450 mode. For signal transfer DMA (a transfer is made between CPU bus cycles), mode 0 is used. Multiple transfers that are made continuously until the receiver FIFO has been emptied are supported by mode 1.<br>Mode 0. RXRDYx is active (low) when in the FIFO mode (FCR0=1, FCR3=0) or when in the TL16C450 mode (FCR0=0) and the receiver FIFO or receiver holding register contain at least one character. When there are no more characters in the receiver FIFO or receiver holding register, the RXRDYx terminal goes inactive (high).<br>Mode 1. RXRDYx goes active (low) in the FIFO mode (FCR0=1) when FCR3=1 and the time-out or trigger levels have been reached. It goes inactive (high) when the FIFO or receiver holding register is empty. |

| RI0, RI1          | 30, 6  | 1   | Ring indicator inputs. RIO and RI1 are modem control inputs. Their condition is tested by reading MSR6 (RI) of each ACE. The modem status register outputs trailing edge of ring indicator (TERI or MSR2) that indicates whether either input has changed states from high to low since the previous reading of the modem status register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SIN0, SIN1        | 41, 62 | 1   | Serial data inputs. SIN0 and SIN1 are serial data inputs that move information from the communication line or modem to the TL16C552 receiver circuits. Mark (set) is a high state and a space (cleared) is low state. Data on the serial data inputs is disabled when operating in the loop mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SLCT              | 65     | 1   | Printer selected. SLCT is an input line from the printer that goes high when the printer has been selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SLIN              | 58     | I/O | Line printer select. SLIN is an open-drain input that selects the printer when it is active (low). This terminal has an internal pullup resistor to $V_{DD}$ of approximately 10 k $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOUT0, SOUT1      | 26, 10 | 0   | Serial data outputs. SOUT0 and SOUT1 are the serial data outputs from the ACE transmitter circuitry. A mark is a high state and a space is a low state. Each SOUT is held in the mark condition when the transmitter is disabled, when RESET is true (low), when the transmitter register is empty, or when in the loop mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**Terminal Functions (continued)**

| TERMIN            | NAL                                                                                                                                                                                |                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO.          |                                                                                                                                                                                    | 1/0                                                                                                                                                                                                                                                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| STB               | 55                                                                                                                                                                                 | I/O                                                                                                                                                                                                                                                          | <ul> <li>Printer strobe. STB is an open-drain line that provides communication between the TL16C552 and printer. When it is active (low), it provides the printer with a signal to latch the data currently on the parallel port. This terminal has an internal pullup resistor to V<sub>DD</sub> of approximately 10 kΩ.</li> <li>3-state control. TRI controls the 3-state control of all I/O and output terminals. When TRI is asserted all I/O and outputs become high impedance, allowing board level testers to drive the outputs with overdriving the internal buffers. This terminal is level sensitive, is a CMOS input, and is pulled do</li> </ul> |  |  |  |

| TRI               | 2                                                                                                                                                                                  | all I/O and outputs become high impedance, allowing board level testers to drive the outputs with overdriving the internal buffers. This terminal is level sensitive, is a CMOS input, and is pulled d with an internal resistor that is approximately 5 kΩ. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| TXRDY0,<br>TXRDY1 | 22, 42                                                                                                                                                                             | 0                                                                                                                                                                                                                                                            | Transmitter ready. TXRDY0 and TXRDY1 are transmitter ready signals. Two types of DMA signaling are available. Either can be selected using FCR3 when operating in the FIFO mode. Only DMA mode 0 is allowed when operating in the TL16C450 mode. Single-transfer DMA (a transfer is made between CPU bus cycles) is supported by mode 0. Multiple transfers that are made continuously until the transmitter FIFO has been filled are supported by mode 1.                                                                                                                                                                                                    |  |  |  |

|                   |                                                                                                                                                                                    |                                                                                                                                                                                                                                                              | Mode 0. When in the FIFO mode (FCR0=1, FCR3=0) or in the TL16C450 mode (FCR0=0) and there are no characters in the transmitter holding register or transmitter FIFO, $\overline{\text{TXRDY}}$ are active (low). Once $\overline{\text{TXRDY}}$ is activated (low), it goes inactive after the first character is loaded into the holding register of transmitter FIFO.                                                                                                                                                                                                                                                                                       |  |  |  |

|                   | Mode 1. TXRDYx goes active (low) if in the FIFO mode (FCR0=1) when FCR3=1 and t characters in the transmitter FIFO. When the transmitter FIFO is completely full, TXRDYx g (high). |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| V <sub>DD</sub>   | 23, 40, 64                                                                                                                                                                         |                                                                                                                                                                                                                                                              | Power supply. V <sub>DD</sub> is the power supply requirement is 5 V $\pm$ 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>DD</sub> (see Note 1)   | 0.5 V to V <sub>DD</sub> + 0.3 V |

|------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub>                  | 0.5 V to 7 V                     |

| Output voltage range, VO                             | 0.5 V to V <sub>DD</sub> + 0.3 V |

| Continuous total power dissipation                   |                                  |

| Operating free-air temperature range, T <sub>A</sub> | –10°C to 70°C                    |

| Storage temperature range, T <sub>stg</sub>          | –65°C to 150°C                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage levels are with respect to ground (VSS).

### recommended operating conditions

|                                                      | MIN  | NOM | MAX             | UNIT |

|------------------------------------------------------|------|-----|-----------------|------|

| Supply voltage, V <sub>DD</sub>                      | 4.75 | 5   | 5.25            | V    |

| Clock high-level input voltage, VIH(CLK)             | 2    |     | V <sub>DD</sub> | V    |

| Clock low-level input voltage, VIL(CLK)              | -0.5 |     | 0.8             | V    |

| High-level input voltage, VIH                        | 2    |     | V <sub>DD</sub> | V    |

| Low-level input voltage, VIL                         | -0.5 |     | 0.8             | V    |

| Clock frequency, f <sub>clock</sub>                  |      |     | 8               | MHz  |

| Operating free-air temperature range, T <sub>A</sub> | 0    |     | 70              | °C   |

# electrical characteristics over recommended ranges of operating free-air temperature and supply voltage

|                 | PARAMETER                     | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                        | MIN | MAX | UNIT |

|-----------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| Vон             | High-level output voltage     | $\begin{split} I_{OH} &= -0.4 \text{ mA for DB0-DB7,} \\ I_{OH} &= -2 \text{ mA for PD0-PD7,} \\ I_{OH} &= -0.4 \text{ mA for INIT, AFD, STB, and SLIN (see Note 2),} \\ I_{OH} &= -0.4 \text{ mA for all other outputs} \end{split}$                                                                                                                                  | 2.4 |     | V    |

| VOL             | Low-level output voltage      | $\begin{split} &I_{OL} = 4 \text{ mA for DB0-DB7,} \\ &I_{OL} = 12 \text{ mA for PD0-PD7,} \\ &I_{OL} = 10 \text{ mA for INIT, AFD, STB, and SLIN (see Note 2),} \\ &I_{OL} = 2 \text{ mA for all other outputs} \end{split}$                                                                                                                                          |     | 0.4 | V    |

| Ц               | Input current                 | $V_{DD}$ = 5.25 V, All other terminals are floating                                                                                                                                                                                                                                                                                                                    |     | ±10 | μΑ   |

| II(CLK)         | Clock input current           | V <sub>I</sub> = 0 to 5.25 V                                                                                                                                                                                                                                                                                                                                           |     | ±10 | μΑ   |

| I <sub>OZ</sub> | High-impedance output current | $V_{DD}$ = 5.25 V, $V_{O}$ = 0 with chip deselected, or $V_{O}$ = 5.25 V with chip and write mode selected                                                                                                                                                                                                                                                             |     | ±20 | μA   |

| IDD             | Supply current                | $ \begin{array}{c c} V_{DD} = 5.25 \text{ V}, \\ \hline SIN0, \text{ SIN1,} \\ \hline DSR0, \\ \hline DSR0, \\ \hline DSR1, \\ \hline DCD0, \\ \hline DCD1, \\ \hline CTS0, \\ \hline CTS1, \\ \hline CTS1, \\ \hline Other inputs at 0.8 \text{ V}, \\ \hline Baud rate generator f_{Clock} = 8 \text{ MHz}, \\ \hline Baud rate = 56 \text{ kbit/s} \\ \end{array} $ |     | 50  | mA   |

NOTE 2: These four terminals contain an internal pullup resistor to V<sub>DD</sub> of approximately 10 kΩ.

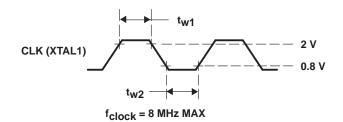

# clock timing requirements over recommended ranges of operating free-air temperature and supply voltage

|                 |                                                                     | MIN  | MAX | UNIT |

|-----------------|---------------------------------------------------------------------|------|-----|------|

| t <sub>w1</sub> | Pulse duration, CLK high (external clock, 8 MHz max) (see Figure 1) | 55   |     | ns   |

| tw2             | Pulse duration, CLK low (external clock, 8 MHz max) (see Figure 1)  | 55   |     | ns   |

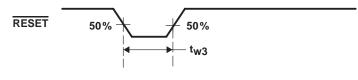

| t <sub>w3</sub> | Pulse duration, master (RESET) low (see Figure 16)                  | 1000 |     | ns   |

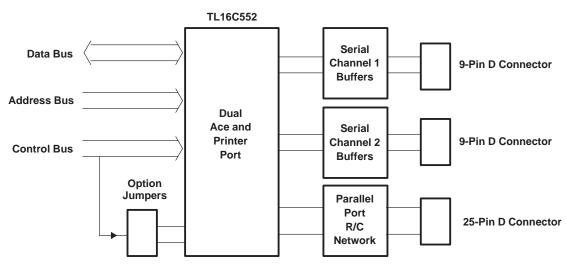

# read cycle timing requirements over recommended ranges of operating free-air temperature and supply voltage (see Figure 4)

|                  |                                                                               | MIN | MAX | UNIT |

|------------------|-------------------------------------------------------------------------------|-----|-----|------|

| t <sub>w4</sub>  | Pulse duration, IOR low                                                       | 80  |     | ns   |

| t <sub>su1</sub> | Setup time, chip select valid before IOR low (see Note 3)                     | 15  |     | ns   |

| t <sub>su2</sub> | Setup time, A2-A0 valid before IOR low (see Note 3)                           | 15  |     | ns   |

| t <sub>h1</sub>  | Hold time, A2–A0 valid after IOR high (see Note 3)                            | 20  |     | ns   |

| t <sub>h2</sub>  | Hold time, chip select valid after IOR high (see Note 3)                      | 20  |     | ns   |

| <sup>t</sup> d1  | Delay time, t <sub>SU2</sub> + t <sub>W4</sub> + t <sub>d2</sub> (see Note 4) | 175 |     | ns   |

| t <sub>d2</sub>  | Delay time, IOR high to IOR or IOW low                                        | 80  |     | ns   |

NOTES: 3. The internal address strobe is always active.

4. In the FIFO mode,  $t_{d1}$  = 425 ns (min) between reads of the receiver FIFO and the status registers (IIR and LSR).

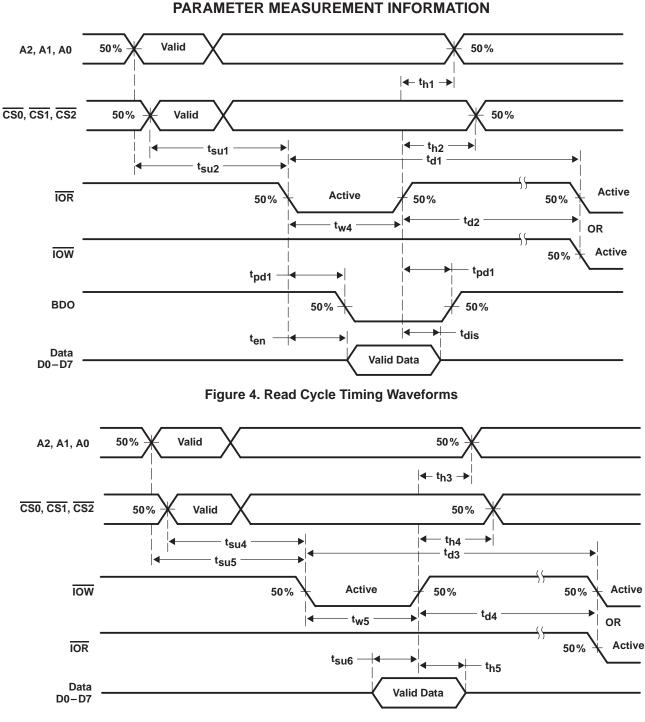

# write cycle timing requirements over recommended ranges of operating free-air temperature and supply voltage (see Figure 5)

|                  |                                                                  | MIN | MAX | UNIT |

|------------------|------------------------------------------------------------------|-----|-----|------|

| t <sub>w5</sub>  | Pulse duration, IOW low                                          | 80  |     | ns   |

| t <sub>su4</sub> | Setup time, chip select valid before IOW low (see Note 3)        | 15  |     | ns   |

| t <sub>su5</sub> | Setup time, A2-A0 valid before IOW low (see Note 3)              | 15  |     | ns   |

| t <sub>su6</sub> | Setup time, D0-D7 valid before IOW high                          | 15  |     | ns   |

| t <sub>h3</sub>  | Hold time, A2-A0 valid after IOW high (see Note 3)               | 20  |     | ns   |

| t <sub>h4</sub>  | Hold time, chip select valid after IOW high (see Note 3)         | 20  |     | ns   |

| t <sub>h5</sub>  | Hold time, D0–D7 valid after IOW high                            | 15  |     | ns   |

| t <sub>d3</sub>  | Delay time, t <sub>su5</sub> + t <sub>w5</sub> + t <sub>d4</sub> | 175 |     | ns   |

| t <sub>d4</sub>  | Delay time, IOW high to IOW or IOR low                           | 80  |     | ns   |

NOTE 3: The internal address strobe is always active.

# read cycle switching characteristics over recommended ranges of operating free-air temperature and supply voltage (see Figure 4)

|                  | PARAMETER                                                                   | TEST CONDITIONS                     | MIN | MAX | UNIT |

|------------------|-----------------------------------------------------------------------------|-------------------------------------|-----|-----|------|

| <sup>t</sup> pd1 | Propagation delay time from IOR high to BDO high or from IOR low to BDO low | C <sub>L</sub> = 100 pF, See Note 5 |     | 60  | ns   |

| t <sub>en</sub>  | Enable time from IOR low to D0-D7 valid                                     | C <sub>L</sub> = 100 pF, See Note 5 |     | 60  | ns   |

| t <sub>dis</sub> | Disable time from IOR high to D0-D7 released                                | C <sub>L</sub> = 100 pF, See Note 5 | 0   | 60  | ns   |

NOTE 5: VOL and VOH (and the external loading) determine the charge and discharge time.

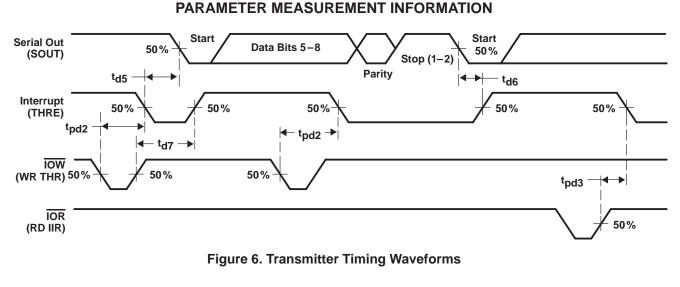

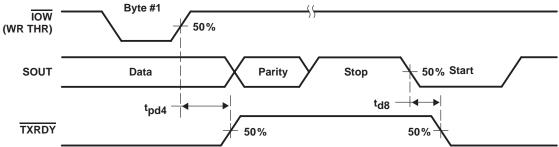

# transmitter switching characteristics over recommended ranges of operating free-air temperature and supply voltage (see Figures 6, 7, and 8)

|                  | PARAMETER                                                           | TEST CONDITIONS         | MIN | MAX | UNIT           |

|------------------|---------------------------------------------------------------------|-------------------------|-----|-----|----------------|

| <sup>t</sup> d5  | Delay time, interrupt THRE low to SOUT low at start                 |                         | 8   | 24  | RCLK<br>cycles |

| <sup>t</sup> d6  | Delay time, SOUT low at start to interrupt THRE high                | See Note 6              | 8   | 8   | RCLK<br>cycles |

| <sup>t</sup> d7  | Delay time, IOW (WR THR) high to interrupt THRE high                | See Note 6              | 16  | 32  | RCLK<br>cycles |

| <sup>t</sup> d8  | Delay time, SOUT low at start to TXRDY low                          | C <sub>L</sub> = 100 pF |     | 8   | RCLK<br>cycles |

| t <sub>pd2</sub> | Propagation delay time from IOW (WR THR) low to interrupt THRE low  | C <sub>L</sub> = 100 pF |     | 140 | ns             |

| tpd3             | Propagation delay time from IOR (RD IIR) high to interrupt THRE low | C <sub>L</sub> = 100 pF |     | 140 | ns             |

| tpd4             | Propagation delay time from IOW (WR THR) high to TXRDY high         | C <sub>L</sub> = 100 pF |     | 195 | ns             |

NOTE 6: When the transmitter interrupt delay is active, this delay si lengthened by one character time minus the last stop bit time.

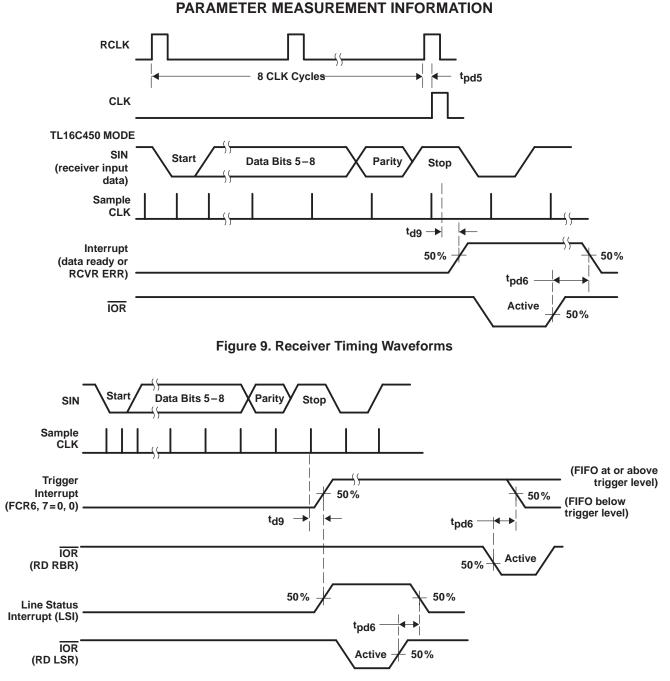

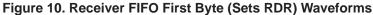

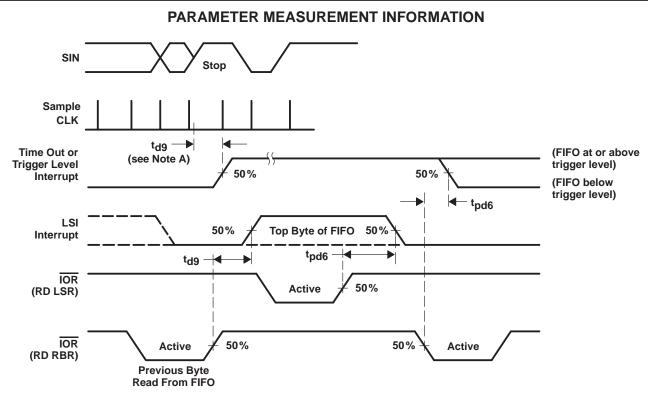

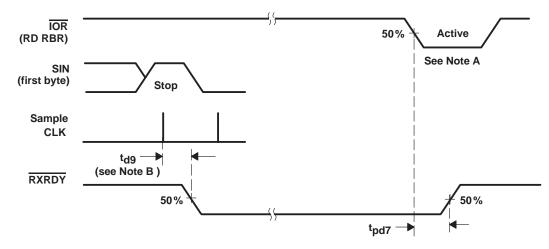

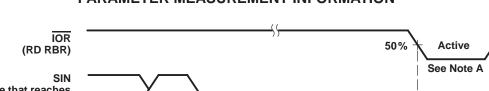

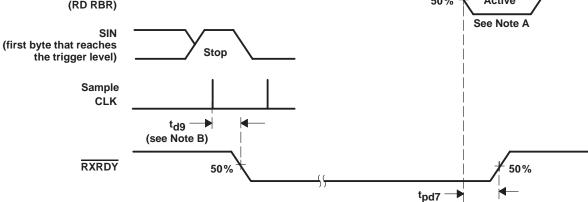

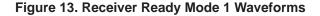

# receiver switching characteristics over recommended ranges of operating free-air temperature and supply voltage (see Figures 9, 10, 11, 12 and 13)

|                  | PARAMETER                                                                   | TEST CONDITIONS         | MIN MAX | UNIT          |

|------------------|-----------------------------------------------------------------------------|-------------------------|---------|---------------|

| t <sub>d9</sub>  | Delay time from stop to INT high                                            | See Note 7              | 1       | RCLK<br>cycle |

| t <sub>pd5</sub> | Propagation delay time from RCLK high to sample CLK high                    |                         | 100     | ns            |

| t <sub>pd6</sub> | Propagation delay time from IOR (RD RBR/RD LSR) high to reset interrupt low | C <sub>L</sub> = 100 pF | 150     | ns            |

| tpd7             | Propagation delay time from IOR (RD RBR) low to RXRDY high                  |                         | 150     | ns            |

NOTE 7: The receiver data available indication, the overrun error indication, the trigger level interrupts and the active RXRDY indication is delayed three RCLK cycles in the FIFO mode (FCR0 = 1). After the first byte has been received, status indicators (PE, FE, BI) is delayed three RCLK cycles. These indicators are updated immediately for any further bytes received after RD RBR goes active. There are eight RCLK cycle delays for trigger change level interrupts.

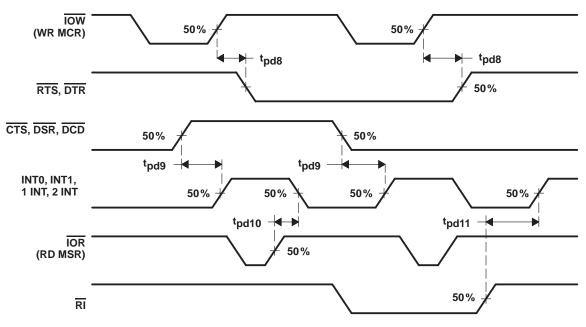

# modem control switching characteristics over recommended ranges of operating free-air temperature and supply voltage (see Figure 14)

|                   | PARAMETER                                                                     | TEST CONDITIONS         | MIN MA | X UNIT |

|-------------------|-------------------------------------------------------------------------------|-------------------------|--------|--------|

| t <sub>pd8</sub>  | Propagation delay time from IOW (WR MCR) high to RTS (DTR) low/high           | C <sub>L</sub> = 100 pF | 1(     | 0 ns   |

| t <sub>pd9</sub>  | Propagation delay time from modem input (CTS, DSR) low/high to interrupt high | C <sub>L</sub> = 100 pF | 1      | 0 ns   |

| <sup>t</sup> pd10 | Propagation delay time from IOR (RD MSR) high to interrupt low                | C <sub>L</sub> = 100 pF | 14     | 0 ns   |

| <sup>t</sup> pd11 | Propagation delay time from RI high to interrupt high                         | C <sub>L</sub> = 100 pF | 1      | 0 ns   |

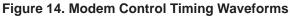

# parallel port timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figure 15)

|                  |                                       | MIN        | MAX       | UNIT |

|------------------|---------------------------------------|------------|-----------|------|

| t <sub>su7</sub> | Setup time, data valid before STB low | 1          |           | μs   |

| <sup>t</sup> h6  | Hold time, data valid after STB high  | 1          |           | μs   |

| t <sub>w6</sub>  | Pulse duration, STB low               | 1          | 500       | μs   |

| <sup>t</sup> d10 | Delay time, BUSY high to ACK low      | Defined by | y printer |      |

| td11             | Delay time, BUSY low to ACK low       | Defined by | y printer |      |

| tw6              | Pulse duration, ACK low               | Defined by | y printer |      |

| t <sub>w7</sub>  | Pulse duration, BUSY high             | Defined by | y printer |      |

| <sup>t</sup> d12 | Delay time, BUSY high after STB high  | Defined by | y printer |      |

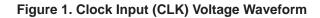

## PARAMETER MEASUREMENT INFORMATION

<sup>†</sup>Includes scope and jig capacitance

SLLS102B - DECEMBER 1990 - REVISED MARCH 1996

Figure 5. Write Cycle Timing Waveforms

SLLS102B - DECEMBER 1990 - REVISED MARCH 1996

Figure 7. Transmitter Ready Mode 0 Timing Waveforms

Figure 8. Transmitter Ready Mode 1 Timing Waveforms

SLLS102B - DECEMBER 1990 - REVISED MARCH 1996

SLLS102B - DECEMBER 1990 - REVISED MARCH 1996

#### Figure 11. Receiver FIFO After First Byte (After RDR Set) Waveforms

Figure 12. Receiver Ready Mode 0 Waveforms

NOTES: A. This is the reading of the last byte in the FIFO.

B. When FCR0=1, then  $t_{d9}$  = 3 RCLK cycles. For a time-out interrupt,  $t_{d9}$  = 8 RCLK cycles.

SLLS102B – DECEMBER 1990 – REVISED MARCH 1996

## PARAMETER MEASUREMENT INFORMATION

#### NOTES: A. This is the reading of the last byte in the FIFO.

B. When FCR0=1, then  $t_{d9}$  = 3 RCLK cycles. For a trigger change level interrupt,  $t_{d9}$  = 8 RCLK

## PARAMETER MEASUREMENT INFORMATION

Figure 16. RESET Voltage Waveform

Three types of information are stored in the internal registers used in the ACE: control, status, and data. Mnemonic abbreviations are shown in the Table 1 for the registers.

| CONTROL                   | MNEMONIC | STATUS                | MNEMONIC | DATA                         | MNEMONIC |

|---------------------------|----------|-----------------------|----------|------------------------------|----------|

| Line control register     | LCR      | Line status register  | LSR      | Receiver buffer register     | RBR      |

| FIFO control register     | FCR      | Modem status register | MSR      | Transmitter holding register | THR      |

| Modem control register    | MCR      |                       |          |                              |          |

| Divisor latch LSB         | DLL      |                       |          |                              |          |

| Divisor latch MSB         | DLM      |                       |          |                              |          |

| Interrupt enable register | IER      |                       |          |                              |          |

## Table 1. Internal Register Types With Mnemonics

The address, read, and write inputs are used with the divisor latch access bit (DLAB) in the line control register (bit 7) to select the register to be written to or read from (see Table 2).

| DLAB | A2 | A1 | A0 | MNEMONIC | REGISTER                                      |

|------|----|----|----|----------|-----------------------------------------------|

| L    | L  | L  | L  | RBR      | Receiver buffer register (read only)          |

| L    | L  | L  | L  | THR      | Transmitter holding register (write only)     |

| L    | L  | L  | Н  | IER      | Interrupt enable register                     |

| Х    | L  | Н  | L  | IIR      | Interrupt identification register (read only) |

| Х    | L  | Н  | L  | FCR      | FIFO control register (write only)            |

| Х    | L  | Н  | Н  | LCR      | Line control register                         |

| Х    | Н  | L  | L  | MCR      | Modem control register                        |

| Х    | Н  | L  | Н  | LSR      | Line status register                          |

| Х    | Н  | Н  | L  | MSR      | Modem status register                         |

| Х    | Н  | Н  | Н  | SCR      | Scratch register                              |

| н    | L  | L  | L  | DLL      | Divisor latch (LSB)                           |

| н    | L  | L  | Н  | DLM      | Divisor latch (MSB)                           |

Table 2. Register Selection<sup>†‡</sup>

<sup>†</sup>X = irrelevant, L = low level, H = high level

<sup>‡</sup> The serial channel is accessed when either  $\overline{CS0}$  or  $\overline{CS1}$  is low.

Individual bits within the registers are referred to by the register mnemonic and the bit number in parenthesis. As an example, LCR7 refers to line control register bit 7.

The transmitter buffer register and receiver buffer register are data registers that hold from five to eight bits of data. If less than eight data bits are transmitted, data is right justified to the LSB. Bit 0 of a data word is always the first serial data bit received and transmitted. The ACE data registers are double buffered so that read and write operations may be performed when the ACE is performing the parallel-to-serial or serial-to-parallel conversion.

### accessible registers

The system programmer, using the CPU, has access to and control over any of the ACE registers that are summarized in Table 2. These registers control ACE operations, receive data, and transmit data. Descriptions of these registers follow Table 3.

| ADDRESS | REGISTER            |                                           |                                | REGISTER BIT NUMBER                                   |                                |                                                      |                                                              |                                                                               |                                                                 |

|---------|---------------------|-------------------------------------------|--------------------------------|-------------------------------------------------------|--------------------------------|------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|

| ADDRE55 | MNEMONIC            | BIT 7                                     | BIT 6                          | BIT 5                                                 | BIT 4                          | BIT 3                                                | BIT 2                                                        | BIT 1                                                                         | BIT 0                                                           |

| 0       | RBR<br>(read only)  | Data<br>Bit 7<br>(MSB)                    | Data<br>Bit 6                  | Data<br>Bit 5                                         | Data<br>Bit 4                  | Data<br>Bit 3                                        | Data<br>Bit 2                                                | Data<br>Bit 1                                                                 | Data<br>Bit 0<br>(LSB)                                          |

| 0       | THR<br>(write only) | Data<br>Bit 7                             | Data<br>Bit 6                  | Data<br>Bit 5                                         | Data<br>Bit 4                  | Data<br>Bit 3                                        | Data<br>Bit 2                                                | Data<br>Bit 1                                                                 | Data<br>Bit 0                                                   |

| 0†      | DLL                 | Bit 7                                     | Bit 6                          | Bit 5                                                 | Bit 4                          | Bit 3                                                | Bit 2                                                        | Bit 1                                                                         | Bit 0                                                           |

| 1†      | DLM                 | Bit 15                                    | Bit 14                         | Bit 13                                                | Bit 12                         | Bit 11                                               | Bit 10                                                       | Bit 9                                                                         | Bit 8                                                           |

| 1       | IER                 | 0                                         | 0                              | 0                                                     | 0                              | (EDSSI)<br>Enable<br>modem<br>status<br>interrupt    | (ERLSI)<br>Enable<br>receiver<br>line<br>status<br>interrupt | (ETBEI)<br>Enable<br>transmitter<br>holding<br>register<br>empty<br>interrupt | (ERBFI)<br>Enable<br>received<br>data<br>available<br>interrupt |

| 2       | FCR<br>(write only) | Receiver<br>Trigger<br>(MSB)              | Receiver<br>Trigger<br>(LSB)   | Reserved                                              | Reserved                       | DMA<br>mode<br>select                                | Tranmitter<br>FIFO<br>reset                                  | Receiver<br>FIFO<br>reset                                                     | FIFO<br>Enable                                                  |

| 2       | IIR<br>(read only)  | FIFOs<br>Enabled <sup>‡</sup>             | FIFOs<br>Enabled <sup>‡</sup>  | 0                                                     | 0                              | Interrupt ID<br>Bit (2)‡                             | Interrupt ID<br>Bit (1)                                      | Interrupt ID<br>Bit (0)                                                       | 0 If<br>interrupt<br>pending                                    |

| 3       | LCR                 | (DLAB)<br>Divisor latch<br>access bit     | Set<br>break                   | Stick<br>parity                                       | (EPS)<br>Even parity<br>select | (PEN)<br>Parity<br>enable                            | (STB)<br>Number of<br>stop bits                              | (WLSB1)<br>Word length<br>select bit 1                                        | (WLSB0)<br>Word length<br>select bit 0                          |

| 4       | MCR                 | 0                                         | 0                              | 0                                                     | Loop                           | Enable<br>external<br>interrupt<br>(INT0 or<br>INT1) | OUT1<br>(an unused<br>internal<br>signal)                    | (RTS)<br>Request<br>to send                                                   | (DTR)<br>Data<br>terminal<br>ready                              |

| 5       | LSR                 | Error in<br>receiver<br>FIFO <sup>‡</sup> | (TEMT)<br>Transmitter<br>empty | (THRE)<br>Transmitter<br>holding<br>register<br>empty | (BI)<br>Break<br>interrupt     | (FE)<br>Framing<br>error                             | (PE)<br>Parity<br>error                                      | (OE)<br>Overrun<br>error                                                      | (DR)<br>Data<br>ready                                           |

| 6       | MSR                 | (DCD)<br>Data carrier<br>detect           | (RI)<br>Ring<br>indicator      | (DSR)<br>Data set<br>ready                            | (CTS)<br>Clear<br>to send      | (∆DCD)<br>Delta<br>data carrier<br>detect            | (TERI)<br>Trailing<br>edge ring<br>indicator                 | (∆DSR)<br>Delta<br>data set<br>ready                                          | (∆CTS)<br>Delta<br>clear<br>to send                             |

| 7       | SCR                 | Bit 7                                     | Bit 6                          | Bit 5                                                 | Bit 4                          | Bit 3                                                | Bit 2                                                        | Bit 1                                                                         | Bit 0                                                           |

#### Table 3. Summary of Accessible Registers

† DLAB = 1

<sup>‡</sup>These bits are always 0 when FIFOs are disabled.

## FIFO control register (FCR)

This write-only register is at the same location as the IIR. It enables and clears the FIFOs, sets the trigger level of the receiver FIFO, and selects the type of DMA signaling. The contents of FCR are described in Table 3 and the following bulleted list.

- Bit 0: FCR0 enables both the transmitter and receiver FIFOs. All bytes in both FIFOs can be reset by clearing FCR0. Data is cleared automatically from the FIFOs when changing from the FIFO mode to the TL16C450 mode and vice versa. Programming of other FCR bits is enabled by setting FCR0=1.

- Bit 1: FCR1=1 clears all bytes in the receiver FIFO and resets the counter. This does not clear the shift register.

- Bit 2: FCR2=1 clears all bytes in the transmitter FIFO and resets the counter. This does not clear the shift register.

- Bit 3: FCR3=1 changes the RXRDY and TXRDY terminals from mode 0 to mode 1 when FCR0=1.

- Bits 4 and 5: These two bits are reserved for future use.

- Bits 6 and 7: These two bits set the trigger level for the receiver FIFO interrupt as shown in Table 4.

| В | IT | RECEIVER FIFO         |

|---|----|-----------------------|

| 7 | 6  | TRIGGER LEVEL (BYTES) |

| 0 | 0  | 01                    |

| 0 | 1  | 04                    |

| 1 | 0  | 08                    |

| 1 | 1  | 14                    |

### Table 4. Receiver FIFO Trigger Level

### FIFO interrupt mode operation

The following receiver status occurs when the receiver FIFO and receiver interrupts are enabled:

- 1. LSR0 is set when a character is transferred from the shift register to the receiver FIFO. When the FIFO is empty, it is cleared.

- 2. IIR = 06 receiver line status interrupt has higher priority than the received data available interrupt IIR = 04.

- 3. Receive data available interrupt is issued to the CPU when the programmed trigger level is reached by the FIFO. As soon as the FIFO drops below its programmed trigger level, it is cleared.

- 4. IIR = 04 (receive data available indication) also occurs when the FIFO reaches its trigger level. It is cleared when the FIFO drops below the programmed trigger level.

The following receiver FIFO character time-out status occurs when receiver FIFO and receiver interrupts are enabled.

## FIFO interrupt mode operation (continued)

- 1. A FIFO timeout interrupt occurs when the following conditions exist:

- a. Minimum of one character in FIFO

- b. Last received serial character was longer than four continuous previous character times ago (if two stop bits are programmed, the second one is included in the time delay).

- c. The last CPU read of the FIFO was more than four continuous character times earlier. At 300 baud and 12-bit characters, the FIFO time-out interrupt causes a latency of 160 ms maximum from received character to interrupt issued.

- 2. By using the RCLK input for a clock signal, the character times can be calculated. (The delay is proportional to the baud rate.)

- 3. The time-out timer is reset after the CPU reads the receiver FIFO or after a new character is received, when there has been no time-out interrupt.

- 4. A time-out interrupt is cleared and the timer is reset when the CPU reads a character from the receiver FIFO.

Transmitter interrupts occur as follows when the transmitter and transmitter FIFO interrupts are enabled (FCRO = 1, IER = 1).

- 1. When the transmitter FIFO is empty, the THR interrupt (IIR = 02) occurs. The interrupt is cleared as soon as the THR is written to or the IIR is read. One to sixteen characters can be written to the transmit FIFO when servicing this interrupt.

- 2. The transmitter FIFO empty indications are delayed one character time minus the last stop bit time whenever the following occurs:

THRE = 1 and there has not been a minimum of two bytes at the same time in transmitter FIFO, since the last THRE = 1. The first transmitter interrupt after changing FCR0 is immediate, however, assuming it is enabled.

Receiver FIFO trigger level and character time-out interrupts have the same priority as the received data available interrupt. The THRE interrupt has the same priority as the transmitter FIFO empty interrupt.

### FIFO polled mode operation

Clearing IER0, IER1, IER2, IER3, or all, with FCR0 = 1, puts the ACE into the FIFO polled mode. Receiver and transmitter are controlled separately. Therefore, either or both can be in the polled mode.

In the FIFO polled mode, there is no time-out condition indicated or trigger level reached. However, the receiver and transmitter FIFOs still have the capability of holding characters. The LSR must be read to determine the ACE status.

### interrupt enable register (IER)

The IER independently enables the four serial channel interrupt sources that activate the interrupt (INT0 or INT1) output. All interrupts are disabled by clearing IER0 – IER3. Interrupts are enabled by setting the appropriate bits of the IER. Disabling the interrupt system inhibits the IIR and the active (high) interrupt output. All other system functions operate in their normal manner, including the setting of the LSR and MSR. The contents of the IER are described in Table 3 and in the following bulleted list.

Bit 0: IER0, when set, enables the received data available interrupt and the time-out interrupts in the FIFO mode.

## interrupt enable register (IER) (continued)

- Bit 1: IER1, when set, enables the THRE interrupt.

- Bit 2: IER2, when set, enables the receiver line status interrupt.

- Bit 3: IER3, when set, enables the modem status interrupt.

- Bits 4 7: IER4 IER7 are always cleared.

### interrupt identification register (IIR)

In order to minimize software overhead during data character transfers, the serial channel prioritizes interrupts into four levels. The four levels of interrupt conditions are shown in the following bulleted list:

- Priority 1 Receiver line status (highest priority)

- Priority 2 Receiver data ready or receiver character time out

- Priority 3 Transmitter holding register empty

- Priority 4–Modem status (lowest priority)

Information indicating that a prioritized interrupt is pending and the type of interrupt is stored in the IIR. The IIR indicates the highest priority interrupt pending. The contents of the IIR are indicated in Table 5.

| FIFO<br>MODE<br>ONLY | IDEN  | TERRUF<br>ITIFICAT<br>EGISTE | ΓΙΟΝ  |                   | INTERRUPT SET AND RESET FUNCTIONS |                                                                                                                                                                                 |                                                             |  |  |

|----------------------|-------|------------------------------|-------|-------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| BIT 3                | BIT 2 | BIT 1                        | BIT 0 | PRIORITY<br>LEVEL | INTERRUPT TYPE                    | INTERRUPT SOURCE                                                                                                                                                                | INTERRUPT RESET<br>CONTROL                                  |  |  |

| 0                    | 0     | 0                            | 1     | -                 | None                              | None                                                                                                                                                                            | -                                                           |  |  |

| 0                    | 1     | 1                            | 0     | First             | Receiver line status              | OE, PE, FE, or BI                                                                                                                                                               | LSR read                                                    |  |  |

| 0                    | 1     | 0                            | 0     | Second            | Received data available           | Receiver data available or trigger level reached                                                                                                                                | RBR read until FIFO<br>drops below the<br>trigger level     |  |  |

| 1                    | 1     | 0                            | 0     | Second            | Character time-out<br>indication  | No characters have been removed<br>from or input to the receiver FIFO<br>during the last four character times and<br>there is at least one character in it<br>during this time. | RBR read                                                    |  |  |

| 0                    | 0     | 1                            | 0     | Third             | THRE                              | THRE                                                                                                                                                                            | IIR read if THRE is<br>the interrupt source<br>or THR write |  |  |

| 0                    | 0     | 0                            | 0     | Fourth            | Modem status                      | CTS, DSR, RI, or DCD                                                                                                                                                            | MSR read                                                    |  |  |

#### **Table 5. Interrupt Control Functions**

- Bit 0: IIR0 indicates whether an interrupt is pending. When IIR0 is cleared, an interrupt is pending.

- Bits 1 and 2: IIR1 and IIR2 identify the highest priority interrupt pending as indicated in Table 5.

- Bit 3: IIR3 is always cleared when in the TL16C450 mode. This bit is set along with bit 2 when in the FIFO mode and a trigger change level interrupt is pending.

- Bits 4 and 5: IIR4 and IIR5 are always cleared.

- Bits 6 and 7: IIR6 and IIR7 are set when FCR0=1.

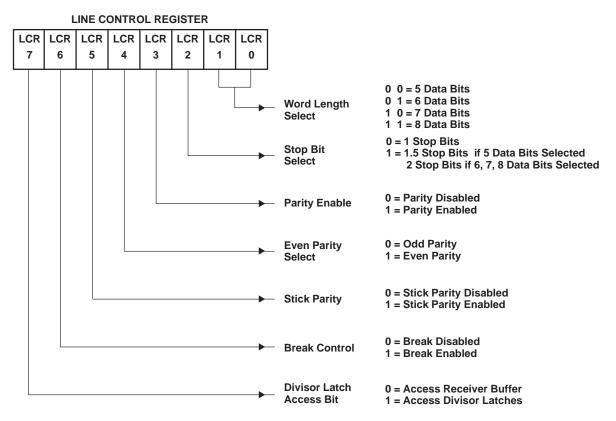

## line control register (LCR)

The format of the data character is controlled by the LCR. The LCR may be read. Its contents are described in the following bulleted list and shown in Figure 17.

- Bits 0 and 1: LCR0 and LCR1 are the word length select bits. The number of bits in each serial character is programmed as shown in Figure 17.

- Bit 2: LCR2 is the stop bit select bit. LCR2 specifies the number of stop bits in each transmitted character as shown in Figure 17. The receiver always checks for one stop bit.

- Bit 3: LCR3 is the parity enable bit 3. When LCR3 is high, a parity bit between the last data word bit and stop bit is generated and checked.

- Bit 4: LCR4 is the even parity select bit 4. When enabled, setting this bit selects even parity.

- Bit 5: LCR5 is the stick parity bit 5. When parity is enabled (LCR3=1), LCR5=1 causes the transmission and reception of a parity bit to be in the opposite state from the value of LCR4. This forces parity to a known state and allows the receiver to check the parity bit in a known state.

- Bit 6: LCR6 is the break control bit 6. When LCR6 is set, the serial output (SOUT1 and SOUT0) is forced to the spacing state (low). The break control bit acts only on the serial output and does not affect the transmitter logic. When the following sequence is used, no invalid characters are transmitted because of the break: