# STLC5412 2B1Q U INTERFACE DEVICE ENHANCED WITH DECT MODE

**PRELIMINARY DATA**

### **GENERAL FEATURES**

- SINGLE CHIP 2B1Q LINE CODE TRANSCEIVER

- SUITABLE FOR ISDN, PAIR GAIN AND DECT APPLICATIONS

- MEETS OR EXCEEDS ETSI EUROPEAN STANDARD

- SINGLE 5V SUPPLY

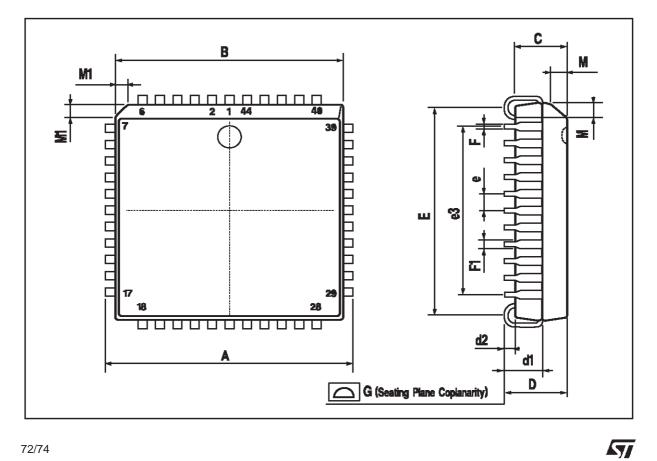

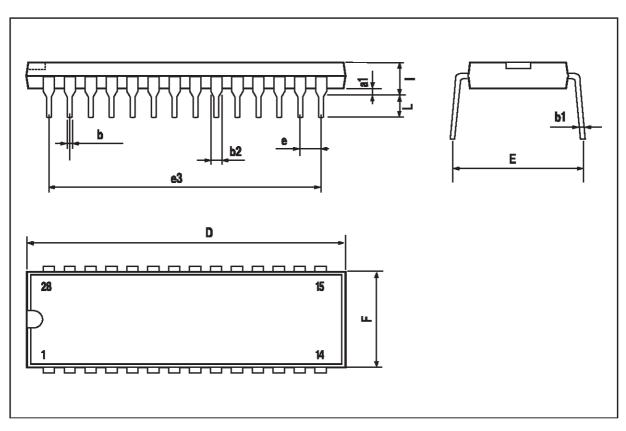

- DIP28 AND PLCC44 PACKAGE

- HCMOS3A SGS-THOMSON ADVANCED 1.2µm DOUBLE-METAL CMOS PROCESS

- ROUND TRIP DELAY MEASUREMENT

- EXTENDED TEMPERATURE RANGE (-40°C TO +70°C)

#### TRANSMISSION FEATURES

- 160 KBIT/S FULL DUPLEX TRANSCEIVER

- 2B1Q LINE CODING WITH SCRAMBLER/DE-SCRAMBLER

- SUPPORTS BRIDGE TAPS, SPLICES AND MIXED GAUGES

- >70DB ADAPTIVE ECHO-CANCELLATION

- ON CHIP HYBRID CIRCUIT

- DECISION FEEDBACK EQUALIZATION

- ON CHIP ANALOG VCO SYSTEM

- DIRECT CONNECTION TO SMALL LINE TRANSFORMER

#### SYSTEM FEATURES

- ACTIVATION/DEACTIVATION CONTROLLER

- ON CHIP CRC CALCULATION AND VERIFI-CATION INCLUDING TWO PROGRAMMA-BLE BLOCK ERROR COUNTERS

- EOC CHANNEL AND OVERHEAD-BITS TRANSMISSION WITH AUTOMATIC MES-SAGE CHECKING

- GCI AND μW/DSI MODULE INTERFACES COMPATIBLE

- DIGITAL LOOPBACKS

- COMPLETE (2B+D) ANALOG LOOPBACK IN LT

- ELASTIC DATA BUFFERS AND BACKPLANE CLOCK DE-JITTERIZER

- AUTOMODE NT1 AND REPEATER

- "U ACTIVATION ONLY" IN NT1

February 1999

- IDENTIFICATION CODE AS PER GCI STANDARD

- DECT FRAME SYNCHRONIZATION

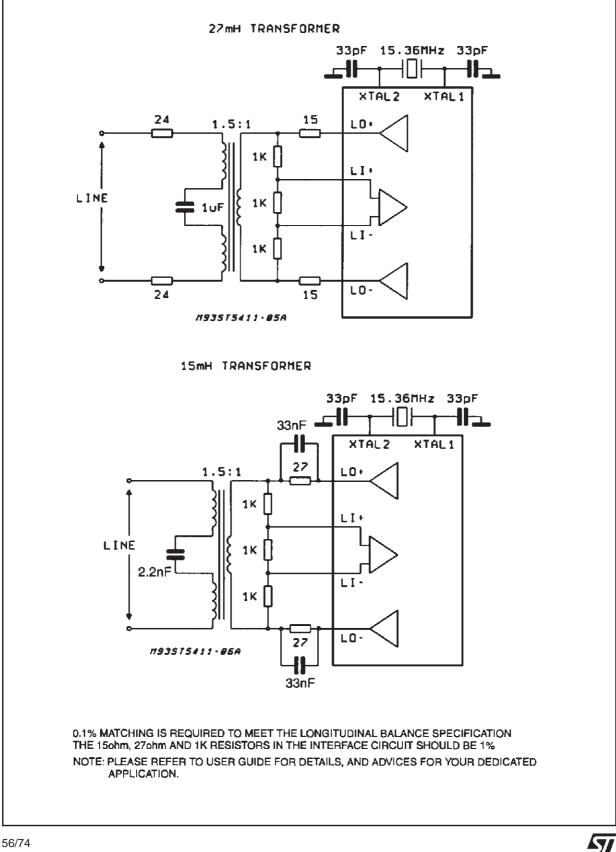

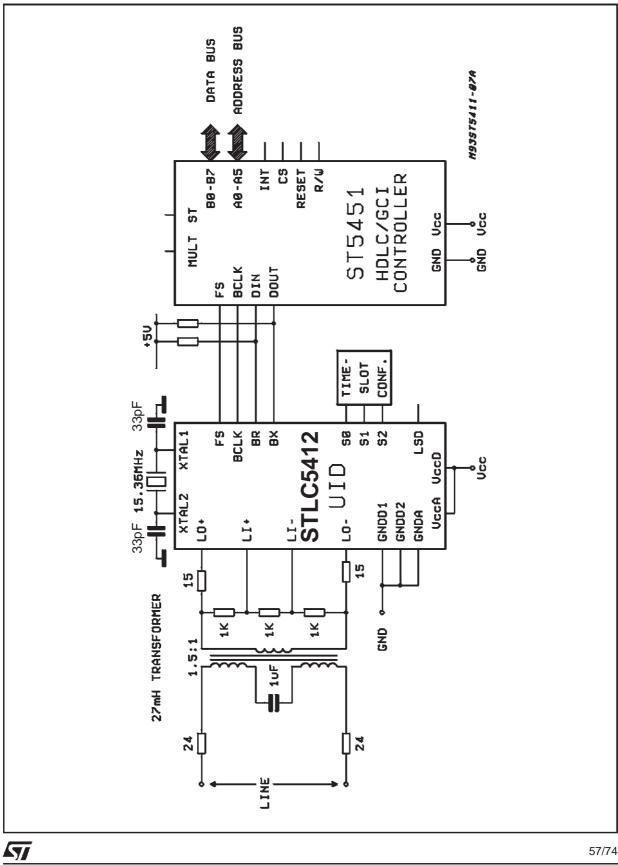

- EASILY INTERFACEABLE WITH ST5451 (HDLC & GCI CONTROLLER), STLC5464 / STLC5465 AND ANY OTHER GCI, IDL or TDM COMPATIBLE DEVICES

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

# STLC5412

### INDEX

| DISTINCTIVE CHARACTERISTICS Page                                                                                                                                          | 1                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| GENERAL DESCRIPTION                                                                                                                                                       | 5                                      |

|                                                                                                                                                                           | 6                                      |

| FUNCTIONAL DESCRIPTION                                                                                                                                                    | 14                                     |

| $\mu W/DSI mode$                                                                                                                                                          | 14<br>14<br>14                         |

| ······································                                                                                                                                    | 14<br>14                               |

|                                                                                                                                                                           | 15<br>18                               |

| Physical links                                                                                                                                                            | 18<br>18<br>22<br>23                   |

| Transmit section<br>Receive section<br>Elastic buffers                                                                                                                    | 23<br>24<br>24<br>25<br>25             |

| Maintenance functions                                                                                                                                                     | 26                                     |

| EOC<br>M4 channel<br>Spare M5 and M6 bits<br>CRC calculation checking                                                                                                     | 26<br>27<br>27<br>27<br>27<br>27<br>27 |

| General purpose I/Os.                                                                                                                                                     | 34<br>34<br>35                         |

| Turning on and off the device                                                                                                                                             | 35                                     |

| Line signal detection                                                                                                                                                     | 35<br>35<br>35<br>36<br>36<br>36       |

| Activation deactivation sequencing.<br>Case of restricted activation.<br>Reset of activation / deactivation state machine.<br>Hardware reset.<br>Quiet mode.<br>Automode. | 36<br>36<br>36                         |

|                                                                                                                                                                           | 37<br>41                               |

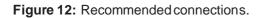

| Line interface circuit                                                                                                                                                    | 55<br>55                               |

| APPENDIX A: STATE MATRIX                                                                                                                                                  | 60                                     |

| APPENDIX B: ELECTRICAL PARAMETERS                                                                                                                                         | 62                                     |

| 2/74                                                                                                                                                                      | 57                                     |

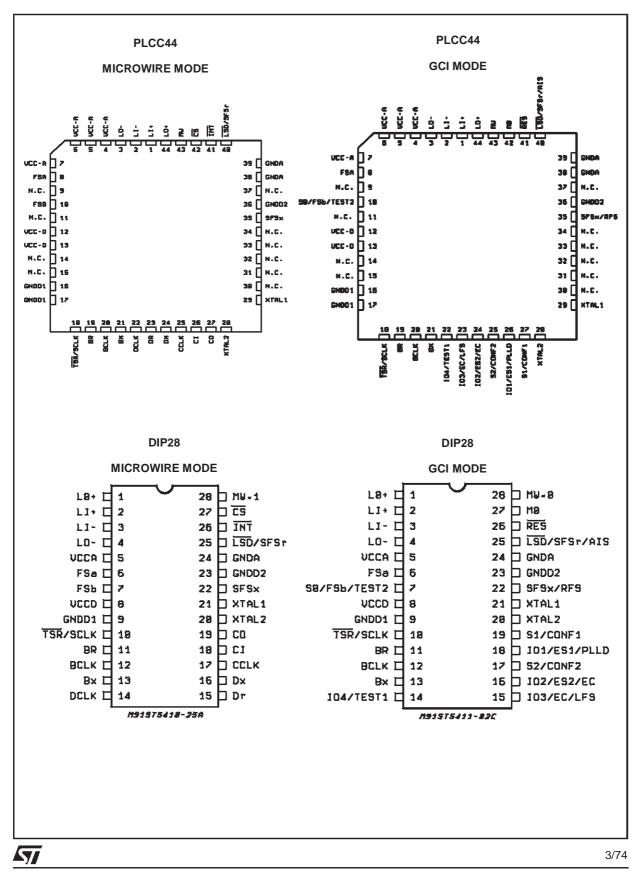

#### **PIN CONNECTIONS** (Top view)

# **STLC5412**

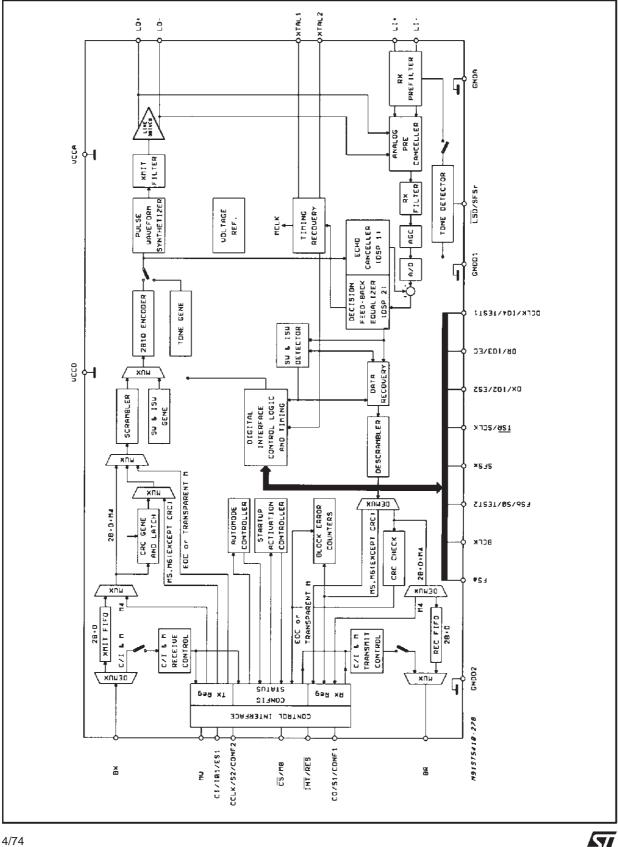

Figure 1: Block Diagram.

#### **GENERAL DESCRIPTION**

STLC5412 is a complete monolithic transceiver for ISDN Basic access data transmission on twisted pair subscriber loops typical of public switched telephone networks. The device is fully compatible with ETSI ETRO80 and CSE (C32-11) French specifications.

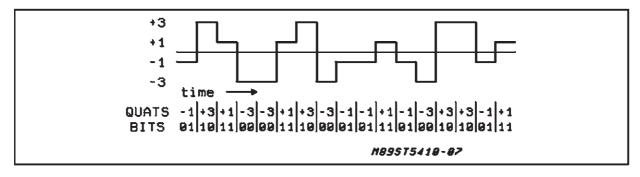

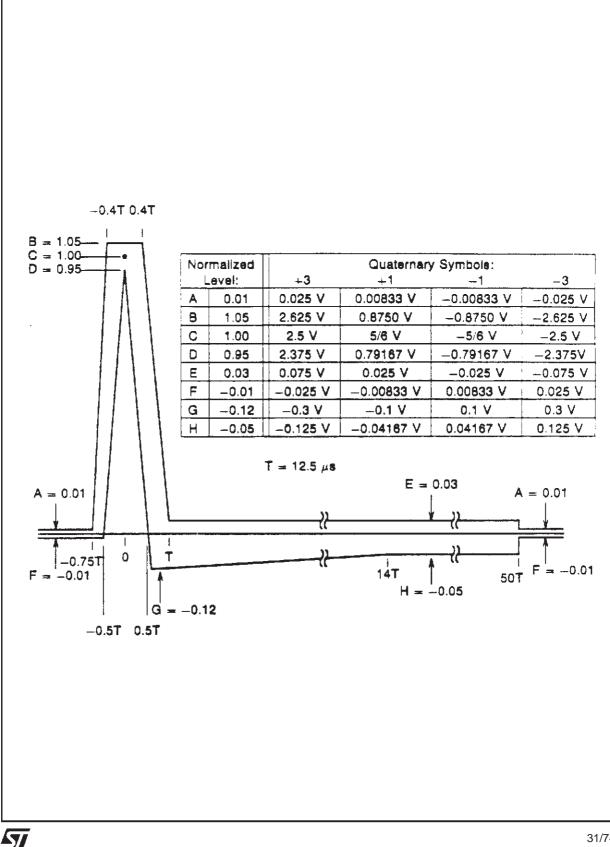

The equivalent of 160 kbit/s full-duplex transmission on a single twisted pair is provided, according to the formats defined in the a.m. spec. Frames include two B channels, each of 64 kbit/s, one D channel of 16 kbit/s plus an additional 4 kbit/s M channel for loop maintenance and other user functions. 12 kbit/s bandwidth is reserved for framing. 2B1Q Line coding is used, where pairs of bits are coded into one of 4 quantum levels. This technique results in a low frequency spectrum (160 kbit/s turn into 80 kbaud), thereby reducing both line attenuation and crosstalk and achieving long range with low Bit Error Rates.

STLC5412 is designed to operate with Bit Error Rate near-end Crosstalk (NEXT) as specified in european ETSI recommendation.

To meet these very demanding specifications, the device includes two Digital Signal Processors, one configured as an adaptive Echo-Canceller to cancel the near end echoes resulting from the transmit/receive hybrid interface, the other as an adaptive line equalizer. A Digital Phase-Locked Loop (DPLL) timing recovery circuit is also included that provides in NT modes a 15.36 MHz synchronized clock to the system. Scrambling and descrambling are performed as specified in the specifications.

On the system side, STLC5412 can be linked to two bus configuration simply by pin MW bias.

**MICROWIRE**( $\mu$ W/DSI) mode (MWpin = 5V): 144 kbit/s 2B+D basic access data is transferred on a multiplex Digital System Interface with 4 different interface formats (see fig. 2 and 3) providing maximum flexibility with a limited pin count (BCLK, Bx, Br, FSa, FSb). Three pre-defined 2B+D formats plus an internal time slot assigner allows direct connection of the UID to the most common multiplexed digital interfaces (TDM/IDL). Bit and Frame Synchronisation signals are inputs or outputs depending on the configuration selected. Data buffers allow any phase between the line and the digital interface. That permits building of slave-slave configurations e.g. in NT12 trunkcards.

It is possible to separate the D from the B chan-

nels and to transfer it on a separate digital interface (Dx, Dr) using the same bit and frame clocks as for the B channels or in a continuous mode using an internally generated 16 kHz bit clock output (DCLK).

All the Control, Status and Interrupt registers are handled via a control channel on a separate serial interface MICROWIRE compatible (CI, CO, CS, CCLK, INT) supported by a number of microcontroller including the MCU families from SGS-THOMSON

**GCI** mode (MWpin = 0V). Control/maintenance channels are multiplexed with 2B+D basic access data in a GCI compatible interface format (see fig. 4a) requiring only 4 pins (BCLK, Bx, Br, FSa). On chip GCI channel assignement allows to multiplex on the same bus up to 8 GCI channels, each supporting data and controls of one device. Bit and Frame Synchronisation signals can be inputs or ouputs depending on the configuration selected. Data buffers, again, allow to have any phase between the line interface and the digital interface.

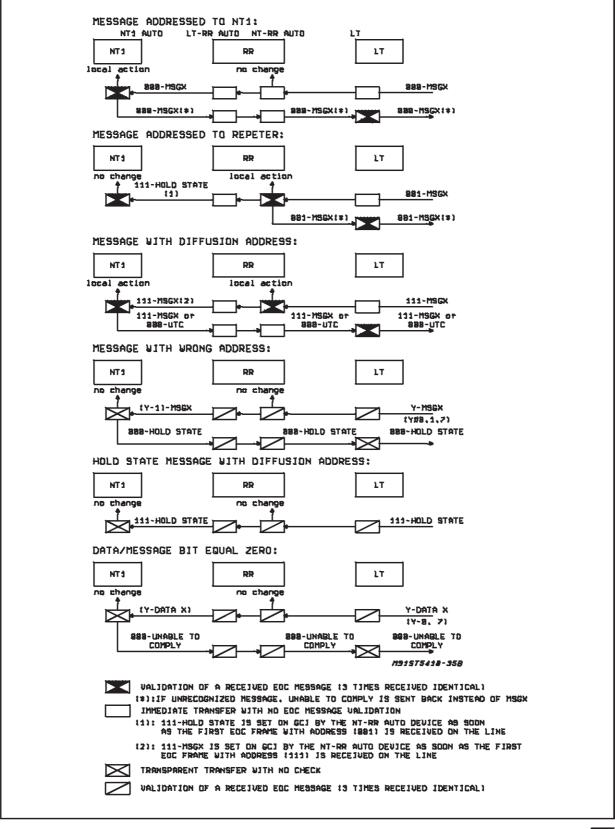

Through the M channel and its protocol allowing to check both direction exchanges, internal registers can be configured, the EOC channel and the Overhead-bits can be monitored. Associated to the M channel, there are A and E channels for enabling the exchanged messages and to check the flow control. The C/I channel allows the primitive exchanges following the standard protocol.

In both mode ( $\mu$ W and GCI) CRC is calculated and checked in both directions internally.

In LT mode, the transmit superframe can be synchronized by an external signal (SFSx) or be self running. In NT mode, the SFSx is always output synchronized by the transmit superframe.

Line side or Digital Interface side loopbacks can be selected for each B1, B2 or D channel independently without restriction in transparent or in non-transparent mode. A transparent complete analog loopback allowing the test of the transmission path is also selectable.

Activation and deactivation procedures, which are automatically processed by UID, require only the exchange of simple commands as Activation Request, Deactivation Request, Activation Indication. Cold and Warm start up procedures are operated automatically without any special instruction.

Four programmable I/Os are provided in GCI for external device control.

<u>[</u>]

### **PIN FUNCTIONS** (no Specific Microwire / GCI Mode) Note: all pin number are referred to Plastic DIP28 package.

| Pin         | Name                | In/Out       | Description                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-------------|---------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

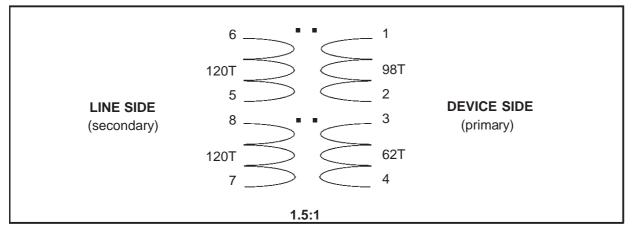

| 1, 4        | LO+, LO-            | Out, Out     | Transmit 2B1Q signal differential outputs to the line transformer. When used with an appropriate 1:1.5 step-up transformer and the proper line interface circuit the line signal conforms to the output specifications in ANSI standard with a nominal pulse amplitude of 2.5 Volts.                                                                                           |  |  |

| 2, 3        | LI+, LI-            | ln, In       | Receive 2B1Q signal differential inputs from the line transformer.                                                                                                                                                                                                                                                                                                             |  |  |

| 5, 8        | VCCA, VCCD          | In, In       | Positive power supply input for the analog and digital sections, which must be +5 Volts +/-5% and must be directly connected together.                                                                                                                                                                                                                                         |  |  |

| 24, 9<br>23 | GNDA,GNDD1<br>GNDD2 | ln, ln<br>In | Negative power supply pins, which must be connected together close to the device.<br>All digital and analog signals are referred to these pins, which are normally at the system Ground.                                                                                                                                                                                       |  |  |

| 10          | TSR                 | Out          | (LT configuration only)<br>This pin is an open drain output normally in the high impedance state which<br>pulls low when B1 and B2 time-slots are active. It can be used to enable the<br>Tristate control of a backplane line-driver.                                                                                                                                         |  |  |

|             | SCLK                | Out          | (NT configuration only)<br>15.36 MHz clock output which is frequency locked to the received line<br>signal active as soon as UID is powered up except in NT1 Auto<br>configuration (active only if S line activation is requested)                                                                                                                                             |  |  |

| 20          | XTAL2               | Out          | The output of the crystal oscillator, which should be connected to one end of the crystal, if used. Otherwise, this pin must be left not connected.                                                                                                                                                                                                                            |  |  |

| 21          | XTAL1               | In           | The master clock input, which requires either a parallel resonance crystal to be tied between this pin and XTAL2, or a logic level clock input from a stable source. This clock does not need to be synchronized to the digital interface clocks (FSa, BCLK).Crystal specifications: 15.36 MHz +/-50ppm parallel resonant; Rs $\leq$ 20 ohms; load with 33pF to GND each side. |  |  |

| 28          | MW                  | In           | MICROWIRE selection: When set high, MICROWIRE control interface is selected. When set low, GCI interface is selected.                                                                                                                                                                                                                                                          |  |  |

# PIN FUNCTIONS (specific Micro Wire mode)

| Pin | Name | In/Out | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | FSa  | In Out | Input or Output depending of the CMS bit in CR1 register, FSa is a 8 KHz clock which indicates the start of the frame on Bx when FSa is input, or Bx and Br when FSa is output.<br>Input or Output, the location of FSa relative to the frame on Bx or Bx and Br depends of DDM bit in CR1 register, also the selected format.                                                                                                         |

| 7   | FSb  | In Out | Input or Output depending of the CMS bit in CR1 register, FSb is a 8 KHz clock which indicates the start of the frame on Br when it is an input. When it is an output, FSb is a 8 KHz pulse conforming with the selected format and always indicating the second 64Kbit/sec channel of the frame on Br. Input or Output, the location of FSb relative to the frame on Br depends of DDM bit in CR1 register, also the selected format. |

| 11  | Br   | Out    | 2B+D datas tristate output. Datas received from the line are shifted out on<br>the rising edge (at the BCLK frequency or the half BCLK frequency if format<br>4 is selected) during the assigned time slot. Br is in high impedance state<br>outside the assigned time slot and during the assigned time slot of the<br>channel if it is disabled.<br>When D channel port is enabled, only B1 B2 are on Br.                            |

### **PIN FUNCTIONS** (specific Micro Wire mode)

| Pin | Name | In/Out | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | BCLK | In Out | Bit clock input or output depending of the CMS bit in CMR register. When BCLK is<br>an input, its frequency may be any multiple of 8 KHz from 256 KHz to 4096 KHz in<br>formats 1, 2, 3; 512 KHz to 6176 KHz in format 4. When BCLK is an output, its<br>frequency is 256 KHz, 512 KHz, 1536 KHz, 2048 KHz or 2560 KHz depending of<br>the selection in CR1 register. In this case, BCLK is locked to the recovered clock<br>received from the line. Input or Output BCLK is synchronous with FSa/FSb. Datas<br>are shifted in and out (on Bx and Br) at the BCLK frequency in formats 1, 2, 3. In<br>format 4 datas are shifted out at half the BCLK frequency. |

| 13  | Bx   | In     | 2B+D input. Basic access data to transmit to the line is shifted in on the falling edges (at the BCLK frequency or the half BCLK frequency if format 4 is selected) during the assigned time-slots. When D channel port is enabled, only B1 & B2 sampled on Bx.                                                                                                                                                                                                                                                                                                                                                                                                  |

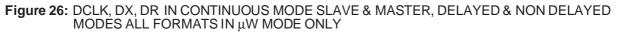

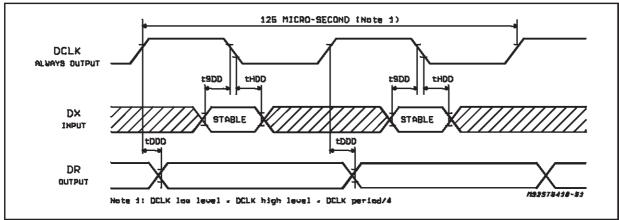

| 14  | DCLK | Out    | D channel clock output when the D channel port is enabled in continuous mode. Datas are shifted in and out (on Dx and Dr) at 16 KHz on the falling and rising edges of DCLK respectively. In master mode, DCLK is synchronous with BCLK.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15  | Dr   | Out    | D channel data output when the D channel port is enabled. D channel data is shifted out from the UID on this pin in 2 selectable modes: in TDM mode data is shifted out at the BCLK frequency (or half BCLK frequency in format 4) on the ridsing edges when the assigned time slot is active. In continuous mode data is shifted in at the DCLK frequency on the rising edge continuously.                                                                                                                                                                                                                                                                      |

| 16  | Dx   | In     | D channel data input when the D channel port is enabled. D channel data is shifted in from the UID on this pin in 2 selectable modes: in TDM mode data is shifted in at the BCLK frequency (or half BCLK frequency in format 4) on the falling edges when the assigned time slot is active. In continuous mode data is shifted in at the DCLK frequency on the falling edge continuously.                                                                                                                                                                                                                                                                        |

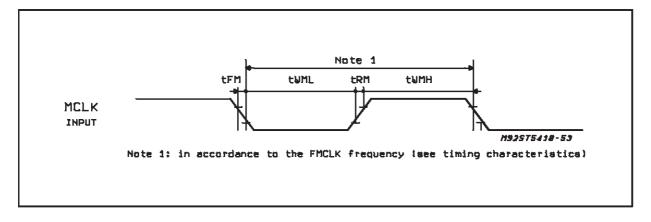

| 17  | CCLK | In     | Clock input for the MICROWIRE control channel: data is shifted in and out on CI and CO pins with CCLK frequency following 2 modes. For each mode the CCLK polarity is indifferent. CCLK may be asynchronous with all the others UID clocks.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18  | CI   | In     | MICROWIRE control channel serial input: Two bytes data is shifted in the UID on this pin on the rising or the falling edge of CCLK depending of the working mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19  | со   | Out    | MICROWIRE control channel serial output: two bytes data is shifted out the UID on this pin on the rising or the falling edge of CCLK depending of the working mode. When not enabled by CS low, CO is high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

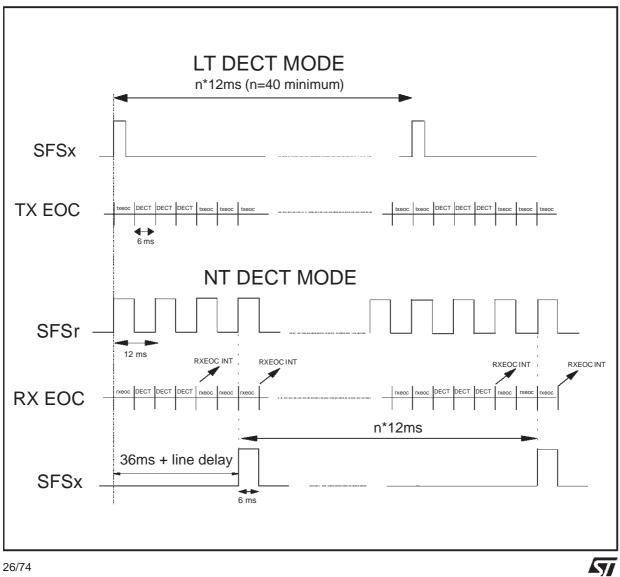

| 22  | SFSx | In Out | Tx Super frame synchronization. The rising edge of SFSx indicates the beginning of the transmit superframe on the line. In NT mode SFSx is always an output. In LT mode SFSx is an input or an output depending of the SFS bit in CR2 register. When SFSx is input, it must be synchronous of FSa. In DECT mode this pin is always an input in LT configuration and is used to evaluate the round trip delay, in NT configuration is an output used to resynchronise the DECT frame counter.(refer to page 25)                                                                                                                                                   |

| 25  | SFSr | Out    | Rx Super frame synchronization. The rising edge of SFSr indicates the beginning of the received superframe on the line. UID provides this output only when ESFR bit in CR4 register is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | LSD  | Out    | Line Signal Detect output (default configuration): This pin is an open drain<br>output which is normally in the high impedance state but pulls low when the<br>device previously in the power down state receives a wake-up by Tone from<br>the line. This signal is intended to be used to wake-up a micro-controller<br>from a low power idle mode. The LSD output goes back in the high<br>impedance state when the device is powered up.                                                                                                                                                                                                                     |

| 26  | INT  | Out    | Interrupt output: Latched open-drain output signal which is normally high impedance and goes low to request a read cycle. Pending interrupt data is shifted out from CO at the following read-write cycle. Several pending interrupts may be queued internally and may provide several interrupt requests. INT is freed upon receiving of CS low and can go low again when CS is freed.                                                                                                                                                                                                                                                                          |

| 27  | CS   | In     | Chip Select input: When this pin is pulled low, data can be shifted in and out from the UID through CI & CO pins. When high, this pin inhibits the MICROWIRE interface. For normal read or write operation, CS has to be pulled low for 16 CCLK periods.                                                                                                                                                                                                                                                                                                                                                                                                         |

### PIN FUNCTIONS (specific GCI mode)

| Pin | Name  | In/Out  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 6   | FSa   | In Out  | Input or Output depending of the configuration. FSa is a 8 KHz clock which indicates the start of the frame on Bx and Br.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 7   | FSb   | Out     | In NT/TE non auto-mode configuration, FSb is a 8 KHz pulse always indicating the second 64Kbit/sec channel of the frame on Br.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|     | SO    | In      | When MO = 0 (LT/NT12 configuration): S0 associated with S1 and S2 selects a GCI channel number on Bx/Br.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     | TEST2 | In      | Input pin to select a transmission test in all auto mode configurations.<br>TEST2 is associated with TEST1.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 11  | Br    | Out     | 2B+D and GCI control channel open drain output. Data is shifted out (at the half BCLK frequency) on the first rising edge of BCLK during the assigned channels slot. Br is in high impedance state outside the assigned time slot and during the assigned time slot of a channel if it is disabled.                                                                                                                                                                                |  |  |  |

| 12  | BCLK  | In Out  | Bit clock input or output depending of the configuration. When BCLK is an input, its frequency may be any multiple of 16 KHz from 512 KHz to 6176 KHz When BCLK is an output, its frequency is 512 KHz in NT1 auto and NTRR auto configurations, 1536 KHz in NT/TE configuration; In this case, BCLK is locked to the recovered clock received from the line. Input or Output BCLK is synchronous with FSa. Data are shifted in and out (on Bx and Br) at half the BCLK frequency. |  |  |  |

| 13  | Bx    | In      | 2B+D and GCI control channel input. Data is sampled by the UID on the second falling edge of BCLK within the period of the bit, during the assign channels time slot.                                                                                                                                                                                                                                                                                                              |  |  |  |

| 14  | IO4   | In Out  | General purpose programmable I/O configured by CR5 register in all non auto mode configurations.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     | TEST1 | In      | Input pin to select a transmission test in all auto mode configurations.<br>TEST1 is associated with TEST2.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 15  | IO3   | In Out  | General purpose programmable I/O configured by CR5 register in all non auto mode configurations.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     | EC    | Out     | External control output pin in NT1 auto configuration. Normaly high, this pin is pulled low when an eoc message "operate 2B+D loopback" is recognized from the line.                                                                                                                                                                                                                                                                                                               |  |  |  |

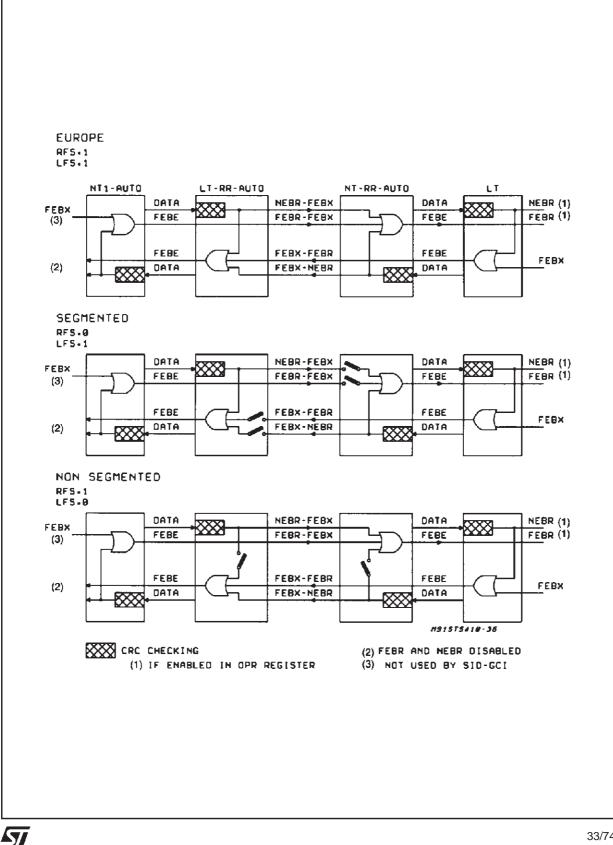

|     | LFS   | In      | Local febe select:<br>When tied to 1 the febe is locally looped back. See figure 10.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 16  | IO2   | In, Out | General purpose programmable I/O configured by CR5 register in all non auto mode configurations.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     | EC    | Out     | External control output pin in LTRR auto configuration. Normaly high, this pin is pulled low when an ARL command is received by the UID.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     | ES2   | In      | External status input pin. In NT1 auto and NTRR auto configurations, this status is sent on the line through the ps2 bit.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 17  | S2    | In      | When MO = 0 (LT/NT12 configuration): S2 associated with S0 and S1 selects a GCI channel number on Bx/Br.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     | CONF2 | In      | When MO = 1: Configuration input pin. Is used associated with CONF1 to select configuration NT/TE (non auto), NT1 auto, LTRR auto and NTRR auto.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 18  | IO1   | In Out  | General purpose programmable I/O configured by CR5 register in all non auto mode configurations.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     | ES1   | In      | External status input pin. In NT1 auto and NTRR auto configurations, this status is sent on the line through the ps1 bit.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|     | PLLD  | In      | PLL1 can be disabled in LTRR configuration with this pin.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 19  | S1    | In      | When MO = 0 (LT/NT12 configuration): S1 associated with S0 and S2 selects a GCI channel number on Bx/Br.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     | CONF1 | In      | When MO = 1: Configuration input pin. Is used associated with CONF2 to select configuration NT/TE (non auto), NT1 auto, LTRR auto and NTRR auto.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

# PIN FUNCTIONS (specific GCI mode)

| Pin | Nama | In/Out | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Name | In/Out | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 22  | RFS  | In     | Remote febe select:<br>When tied to 0 the remote febe is not transferred. When tied to 1 febe is<br>transparently reported. See figure 10.                                                                                                                                                                                                                                                                                                          |

|     | SFSx | In Out | Tx Super frame synchronization. In LT mode this pin is an input giving the Tx<br>Super Frame Synchronization if $SFS = 0$ in CR2. It becomes an output if $SFS = 1$ with ISW free running on the line. In NT mode this pin is always an output<br>giving the Tx Super Frame position. If DECT mode is selected (DECT = 1 in<br>CR7) this pin provide the DECT synchronization pulse at each validated<br>reception of the DECT eoc message.         |

| 25  | AIS  | In     | Analog interface select for all auto mode configurations                                                                                                                                                                                                                                                                                                                                                                                            |

|     | SFSr | Out    | Rx Super frame synchronization. The rising edge of SFSr indicates the beginning of the received superframe on the line. UID provides this output only when ESFR bit in CR4 register is to 1 and LT/NT12 or NT/TE configuration is done.                                                                                                                                                                                                             |

|     | LSD  | Out    | Line Signal Detect output (default configuration): This pin is an open drain<br>output which is normally in the high impedance state but pulls low when the<br>device previously in the power down state receives a wake-up by Tone from<br>the line. This signal is intended to <u>be</u> used to wake-up a micro-controller<br>from a low power idle mode. The LSD output goes back in the high<br>impedance state when the device is powered up. |

| 26  | RES  | In     | Reset input pin with internal pull-up resistor. When pulled low, all registers of the UID are reset to their default values. UID is configured according to configuration inputs bias excluding MW input which must be maintained at the 0 volt. minimum recommended pulse length is 200µs.                                                                                                                                                         |

| 27  | MO   | In     | Configuration input pin. When pulled low, GCI channel assigner is selected (channel number defined by inputs S0, S1, S2). When pulled high, UID is configured by pins CONF1 and CONF2.                                                                                                                                                                                                                                                              |

# MULTIPLE FUNCTION PIN DESCRIPTION

Pin 6: FSa

|             | Function    | In/Out         |                |     |     |

|-------------|-------------|----------------|----------------|-----|-----|

| M/M/(nin) 1 |             | CMS(cr1) = 1   |                | FSa | Out |

| MW(pin) = 1 |             | CMS(cr1) = 0   |                | FSa | In  |

| MW(pin) = 0 | MO(pin) = 1 | CONF2(pin) = 1 |                | FSa | Out |

|             |             | CONF2(pin) = 0 | CONF1(pin) = 1 | FSa | In  |

|             |             | CON 2(pin) = 0 | CONF1(pin) = 0 | FSa | Out |

|             | MO(pin) = 0 |                |                | FSa | In  |

Pin 7: S0/FSb/TEST2

|             | Function     | In/Out         |                |       |     |

|-------------|--------------|----------------|----------------|-------|-----|

| MW(pin) = 1 | CMS(cr1) = 1 |                | FSb            | Out   |     |

| (pin) = 1   |              | CMS(cr1) = 0   |                | FSb   | In  |

| MW(pin) = 0 | MO(pin) = 1  | CONF2(pin) = 1 | CONF1(pin) = 1 | TEST2 | In  |

|             |              |                | CONF1(pin) = 0 | FSb   | Out |

|             |              | CONF2(pin) = 0 |                | TEST2 | In  |

|             | MO(pin) = 0  |                |                | S0    | In  |

# Pin 10: TSR/SCLK/TCLK

|             | Function    | In/Out         |                |      |        |

|-------------|-------------|----------------|----------------|------|--------|

| MW(pin) = 1 |             | NTS(cr2) = 1   |                | SCLK | Out    |

| ww(pin) = 1 |             | NTS(cr2) = 0   |                | TSR  | Out OD |

|             | MO(pin) = 1 | CONF2(pin) = 1 |                | SCLK | Out    |

|             |             | CONF2(pin) = 0 | CONF1(pin) = 1 | TSR  | Out OD |

| MW(pin) = 0 |             |                | CONF1(pin) = 0 | SCLK | Out    |

|             | MO(pin) = 0 | NTS(cr2) = 1   |                | SCLK | Out    |

|             | (pill) = 0  | NTS(cr2) = 0   |                | TSR  | Out OD |

# Pin 12: BCLK

| Function or In/Out conditions |             |                |                |      | In/Out |

|-------------------------------|-------------|----------------|----------------|------|--------|

| MW(pin) = 1                   |             | CMS(cr1) = 1   |                | BCLK | Out    |

| WW(pin) = 1                   |             | CMS(cr1) = 0   |                | BCLK | In     |

| MW(pin) = 0                   | MO(pin) = 1 | CONF2(pin) = 1 |                | BCLK | Out    |

|                               |             | CONF2(pin) = 0 | CONF1(pin) = 1 | BCLK | In     |

|                               |             |                | CONF1(pin) = 0 | BCLK | Out    |

|                               | MO(pin) = 0 |                |                | BCLK | In     |

Pin 14: DCLK/IO4/TEST1 with pull up resistor

| Function or In/Out conditions |              |                |                |              |          | In/Out   |

|-------------------------------|--------------|----------------|----------------|--------------|----------|----------|

|                               |              | DEN(cr2) = 1   | DMO(cr2) = 1   |              | DCLK     | Out      |

| MW(pin) = 1                   |              |                | DMO(cr2) = 0   |              | reserved | reserved |

|                               |              | DEN(cr2) = 0   |                |              | reserved | reserved |

|                               | MO(pin) = 1  | CONF2(pin) = 1 | CONF1(pin) = 1 |              | TEST1    | In       |

|                               |              |                | CONF1(pin) = 0 | IO4(cr5) = 1 | 14       | In       |

| MW(pin) = 0                   |              |                |                | IO4(cr5) = 0 | O4       | Out      |

|                               |              | CONF2(pin) = 0 |                |              | TEST1    | In       |

|                               | MO(pin) = 0  |                |                | IO4(cr5) = 1 | 14       | In       |

|                               | WO(pill) = 0 |                |                | IO4(cr5) = 0 | O4       | Out      |

# Pin 15: Dr/IO3/EC/LFS with pull up resistor

|             | Function or In/Out conditions |                |                |              |          |          |

|-------------|-------------------------------|----------------|----------------|--------------|----------|----------|

| MW(pin) = 1 |                               | DEN(cr2) = 1   |                |              | Dr       | Out      |

| WW(pin) = 1 |                               | DEN(cr2) = 0   |                |              | reserved | reserved |

|             |                               |                | CONF1(pin) = 1 |              | EC       | Out      |

|             | MO(pin) = 1                   | CONF2(pin) = 1 | CONF1(pin) = 0 | IO3(cr5) = 1 | 13       | In       |

| MW(pin) = 0 |                               |                |                | IO3(cr5) = 0 | O3       | Out      |

|             |                               | CONF2(pin) = 0 |                |              | LFS      | In       |

|             | MO(pin) = 0                   |                |                | IO3(cr5) = 1 | 13       | In       |

|             | WO(pin) = 0                   |                |                | IO3(cr5) = 0 | O3       | Out      |

### Pin 16: Dx/IO2/EC/ES2 with pull up resistor

|              | Function or In/Out conditions |                                  |                |              |          |          |

|--------------|-------------------------------|----------------------------------|----------------|--------------|----------|----------|

| MW(pin) = 1  |                               | DEN(cr2) = 1                     |                |              | Dx       | In       |

| WW (pin) = 1 |                               | DEN(cr2) = 0                     |                |              | reserved | reserved |

|              | MO(pin) = 1                   |                                  | CONF1(pin) = 1 |              | ES2      | In       |

|              |                               | CONF2(pin) = 1<br>CONF2(pin) = 0 | CONF1(pin) = 0 | IO2(cr5) = 1 | 12       | In       |

|              |                               |                                  |                | IO2(cr5) = 0 | O2       | Out      |

| MW(pin) = 0  |                               |                                  | CONF1(pin) = 1 |              | EC       | Out      |

|              |                               | CONT 2(pin) = 0                  | CONF1(pin) = 0 |              | ES2      | In       |

|              | MO(pin) = 0                   |                                  |                | IO2(cr5) = 1 | 12       | In       |

|              | WO(pill) = 0                  |                                  |                | IO2(cr5) = 0 | O2       | Out      |

Pin 17: CCLK/S2/CONF2

|             | Function or In/Out conditions |  |  | Function | In/Out |    |

|-------------|-------------------------------|--|--|----------|--------|----|

| MW(pin) = 1 |                               |  |  |          | CCLK   | In |

| MW(pin) = 0 | MO(pin) = 1                   |  |  |          | CONF2  | In |

| (pin) = 0   | MO(pin) = 0                   |  |  |          | S2     | In |

### Pin 18: CI/IO1/ES1/PLLD with pull up resistor

|             | Function or In/Out conditions |                                 |                |              |      |     |

|-------------|-------------------------------|---------------------------------|----------------|--------------|------|-----|

| MW(pin) = 1 |                               |                                 |                |              | CI   | In  |

|             |                               | CONF2(pin) = 1 $CONF2(pin) = 0$ | CONF1(pin) = 1 |              | ES1  | In  |

|             |                               |                                 | CONF1(pin) = 0 | IO1(cr5) = 1 | l1   | In  |

| MW(pin) = 0 | MO(pin) = 1                   |                                 |                | IO1(cr5) = 0 | O1   | Out |

| WW(pin) = 0 |                               |                                 | CONF1(pin) = 1 |              | PLLD | In  |

|             |                               |                                 | CONF1(pin) = 0 |              | ES1  | In  |

|             | MO(pin) = 0                   |                                 |                | IO1(cr5) = 1 | l1   | In  |

|             | WO(pin) = 0                   |                                 |                | IO1(cr5) = 0 | O1   | Out |

### Pin 19: CO/S1/CONF1

|             | Function or In/Out conditions |  |  | Function | In/Out |     |

|-------------|-------------------------------|--|--|----------|--------|-----|

| MW(pin) = 1 |                               |  |  |          | CO     | Out |

| MW(pin) = 0 | MO(pin) = 1                   |  |  |          | CONF1  | In  |

| WW(pin) = 0 | MO(pin) = 0                   |  |  |          | S2     | In  |

Pin 22: SFSx/RFS with pull up resistor

|             | Funct       | ion or In/Out cond                           | litions      | Function | In/Out |

|-------------|-------------|----------------------------------------------|--------------|----------|--------|

|             |             | NTS(cr2) = 1                                 |              | SFSx     | Out    |

| MW(pin) = 1 |             | NTS(cr2) = 0                                 | SFS(cr2) = 1 | SFSx     | Out    |

|             |             | NTS(CI2) = 0                                 | SFS(cr2) = 0 | SFSx     | In     |

|             | MO(pin) = 1 | CONF2(pin) = 1                               |              | SFSx     | Out    |

|             |             | CONF2(pin) = 0                               |              | RFS      | In     |

| MW(pin) = 0 |             | NTS(cr2) = 1                                 |              | SFSx     | Out    |

|             | MO(pin) = 0 | NTS(cr2) = 0                                 | SFS(cr2) = 1 | SFSx     | Out    |

|             |             | $\operatorname{NIS}(\operatorname{CIZ}) = 0$ | SFS(cr2) = 0 | SFSx     | In     |

# Pin 25: LSD/SFSr/AIS

|             | Function or In/Out conditions |                |                |               |      | In/Out |

|-------------|-------------------------------|----------------|----------------|---------------|------|--------|

| MW(pin) = 1 |                               |                |                | ESFR(cr4) = 1 | SFSr | Out OD |

| (pin) = 1   |                               |                |                | ESFR(cr4) = 0 | LSD  | Out OD |

|             | MW(pin) = 0                   |                | CONF1(pin) = 1 |               | AIS  | In     |

|             |                               | CONF2(pin) = 1 | CONF1(pin) = 0 | ESFR(cr4) = 1 | SFSr | Out OD |

| MW(pin) = 0 |                               |                |                | ESFR(cr4) = 0 | LSD  | Out OD |

|             |                               | CONF2(pin) = 0 |                |               | AIS  | In     |

|             |                               |                |                | ESFR(cr4) = 1 | SFSr | Out OD |

| MO(pin) = 0 |                               |                |                | ESFR(cr4) = 0 | LSD  | Out OD |

# Pin 26: INT/RES with pull up resistor

|             | Function or In/Out conditions |  |  | Function | In/Out |        |

|-------------|-------------------------------|--|--|----------|--------|--------|

| MW(pin) = 1 |                               |  |  |          | INT    | Out OD |

| MW(pin) = 0 |                               |  |  |          | RES    | In     |

### Pin 27: CS/MO

|             | Function or In/Out conditions |  |  | Function | In/Out |    |

|-------------|-------------------------------|--|--|----------|--------|----|

| MW(pin) = 1 |                               |  |  |          | CS     | In |

| MW(pin) = 0 |                               |  |  |          | MO     | In |

Notes: Out OD = Open Drain Output

### STLC5412

### FUNCTIONAL DESCRIPTION

#### **Digital Interfaces**

STLC5412 provides a choice between two types of digital interface for both control data and (2 B+D) basic access data.

These are:

a) General Circuit Interface: GCI.

b) Microwire/Digital System Interface: µW/DSI

The device will automatically switch to one of them by sensing the MW input pin at the Power up.

#### μW/DSI MODE

#### **Microwire control interface**

The MICROWIRE interface is enabled when pin MW equal one. Internal registers can be written or read through that control interface. It is constituted of 5 pins:

| CI:           | data input        |

|---------------|-------------------|

| CO:           | data output       |

| <u>CC</u> LK: | data clock input  |

| <u>CS:</u>    | Chip Select input |

| INT:          | Interruptoutput   |

Transmission of data onto CI & CO is enabled when CS input is low.

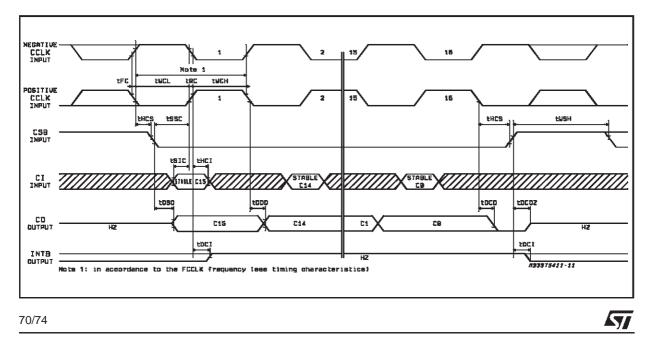

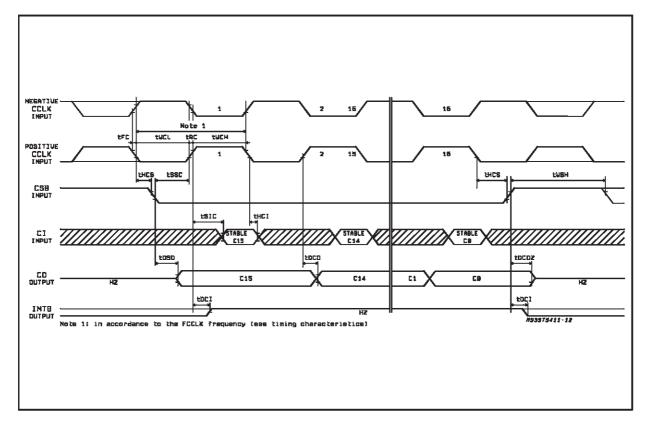

A Write cycle or a Read cycle is always constituted of two bytes. CCLK must be pulsed 16 times while  $\overline{CS}$  is low.

Transmission of data onto CI & CO is enabled following 2 modes.

- MODE A: the first CCLK edge after CS falling edge (and fifteen others odd CCLK edges) are used to shift in the CI data, the even edges being used to shift out the CO data.

- MODE B: the CCLK first edge after CS falling edge (and the fifteen others odd CCLK edges) are used to shift out the CO data, the even edges being used to shift in the CI data.

For each mode the first CCLK edge after  $\overline{CS}$  falling edge can be positive or negative: the UID automaticaly detects the CCLK polarity.

Mode A is the default value. To select the mode B, write MWPS register.

You can write in the UID on CI while the UID send back a register content to the microprocessor. If the UID has no message to send, it forces the CO output to all zero's.

If the UID is to be read (status change has occured in the UID or a read-back cycle has been requested by the controller), it pulls the INT output low until CS is provided. INT high to low transition is not allowed when CS is low (the UID waits for CS high if a pending interrupt occurs while  $\overline{CS}$  is low).

When  $\overline{CS}$  is high, the CO pin is in the high impedance state.

### Write cycle

The format to write a 8 bits message into the UID is:

| A7 | A6 | A5 | A4    | A3   | A2 | A1 | A0 |

|----|----|----|-------|------|----|----|----|

|    |    |    | 1st l | ovte |    |    |    |

| D7 | D6 | D5 | D4  | D3   | D2 | D1 | D0 |

|----|----|----|-----|------|----|----|----|

|    |    |    | 2nd | byte |    |    |    |

| A7-A1: | Register Address          |

|--------|---------------------------|

| A0:    | Write/Read back Indicator |

| D7-D0: | Register Content          |

After the first byte is shifted in, Register address is decoded. A0 set low indicates a write cycle: the content of the following received byte has to be loaded into the addressed register.

A0 set high indicates a read-back cycle request and the byte following is not significant. The UID will respond to the request with an interrupt cycle. It is then possible for the microprocessor to receive the required register content after several other pending interrupts.

To write a 12bits message, the difference is:

limited address field: A7 - A4 extended data field (D11 - D8): A3 - A0.

The Write/Read back indicator doesn't apply; to read and write a 12 bits register two addresses are necessary.

### **Read cycle**

When UID has a register content to send to the microprocessor, it pulls low the  $\overline{\text{INT}}$  output to request CS and CCLK signals. Note that the data to send can be the content of a Register previously requested by the microprocessor by means of a read-back request.

The format of the 8 bits message sent by the UID is:

| A7       | A6 | A5 | A4 | A3 | A2 | A1 | A0 |  |  |

|----------|----|----|----|----|----|----|----|--|--|

| 1st byte |    |    |    |    |    |    |    |  |  |

| D7       | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

|----------|----|----|----|----|----|----|----|--|--|--|

| 2nd byte |    |    |    |    |    |    |    |  |  |  |

A7-A1: **Register Address**

- A0: forced to 1 if read back

- forced to 0 if spontaneous

- D7-D0: Register Content

To read a 12 bits message, the difference is: limited address field: A7 - A4 extended data field (D11 - D8): A3 - A0. The Write/Read back indicator doesn't exit.

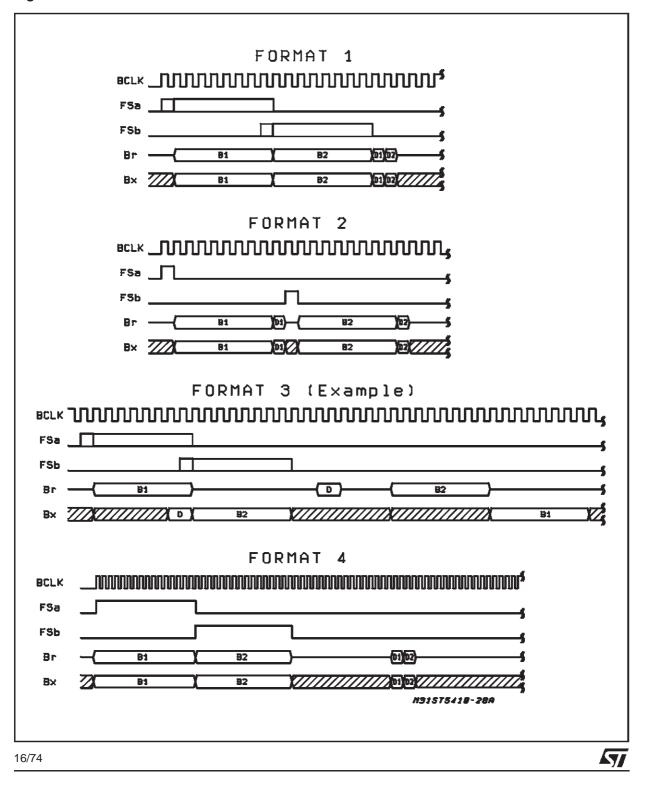

### DIGITAL SYSTEM INTERFACE

Two B channels, each at 64 kbit/s and one D channel at 16 kbit/s form the Basic access data. Basic access data is transferred on the Digital System Interface with several different formats selectable by means of the configuration register CR1.

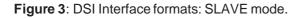

The DSI is basically constituted of 5 wires (see fig.2 and 3):

BCLK bit clock

- Bx data input to transmit to the line

- Br data output received from the line

- FSa Transmit Frame sync

- FSb Receive Frame sync

It is possible to separate the D channel from the B channels and to transfer it on a separate Digital Interface constituted of 2 pins:

- Dx D channel data input

- Dr D channel data ouput

The TDM (Time Division Multiplex) mode uses the same bit and frame clocks as for the B channels. The continuous mode uses an internally generated 16 kHz bit clock output:

DCLK D channel clock output

For all formats when D channel port is enabled "continuous mode" is possible. When the D channel port is enabled in TDM mode, D bits are assigned according to the related format on Dx and Dr.

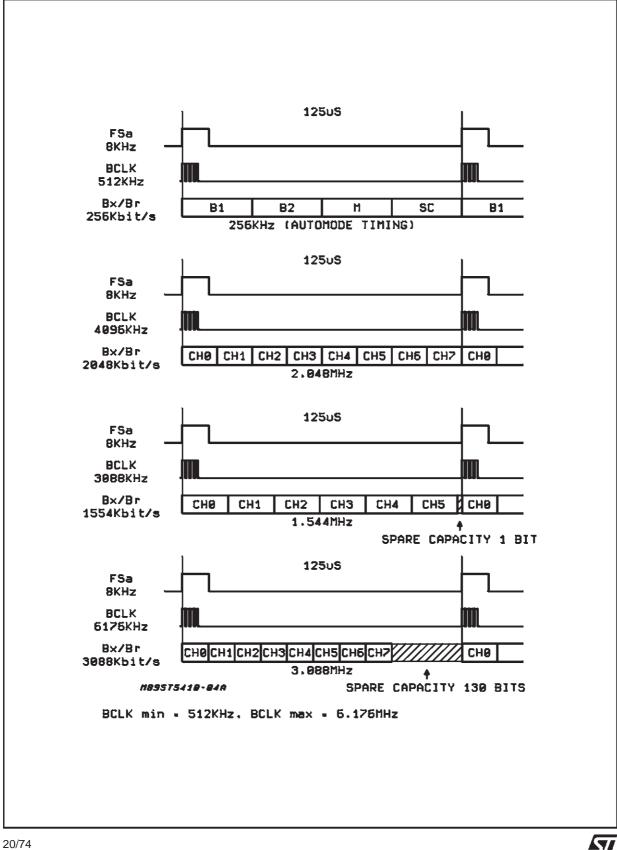

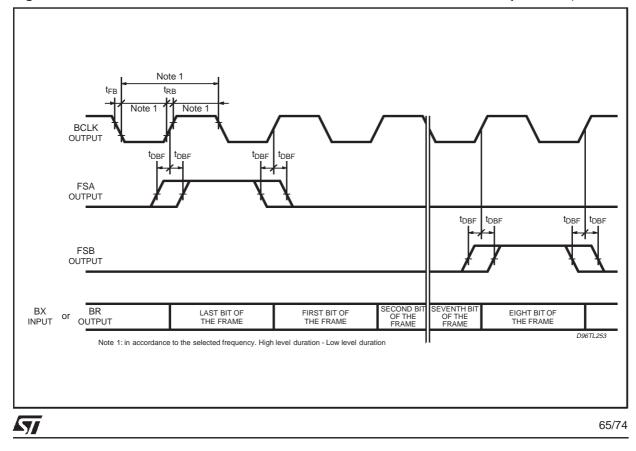

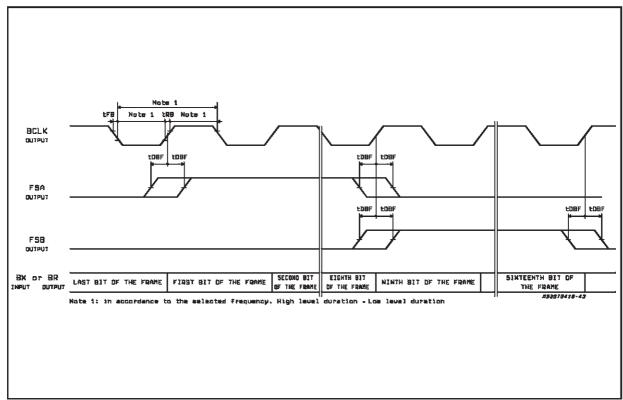

STLC5412 provides a choice of four multiplexed formats for the B and D channels data as shown in fig.2 and 3.

**Format 1:** the 2B+D data transfer is assigned to the first 18 bits of the frame on Br and Bx I/0 pins. Channels are assigned as follows: B1(8 bits), B2(8 bits), D(2 bits), with the remaining bits ignored until the next Frame sync pulse.

**Format 2:** the 2B+D data transfer is assigned to the first 19 bits of the frame on Br and Bx I/O pins. Channels are assigned as follows: B1(8 bits), D(1 bit), 1 bit ignored, B2(8 bits), D(1 bit), with the remaining bits ignored until the next frame sync pulse.

**Format 3:** B1 and B2 Channels can be independently assigned to any 8 bits wide time slot among 64 (or less) on the Bx and Br pins. The transmit and receive directions are also independent. When TDM mode is selected, the D channel can be assigned to any 2 bits wide time slot among 256 on the Bx and Br pins or on the

Dx and Dr pins (D port disabled or enabled in TDM mode respectively).

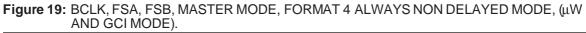

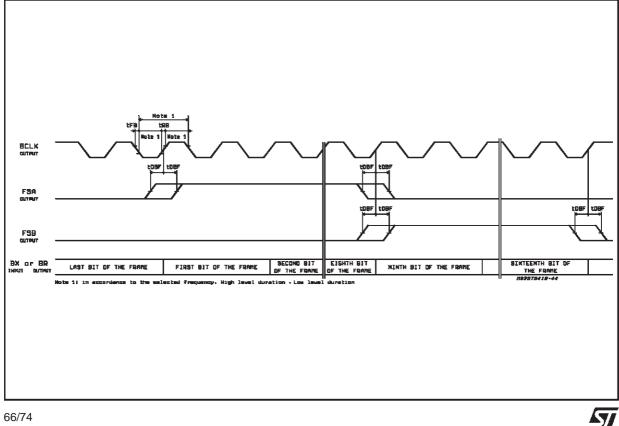

**Format 4:** is a GCI like format excluding Monitor channel and C/I channel. The 2B+D data transfer is assigned to the first 26 bits of the frame on Br and Bx I/O pins. Channels are assigned as follows. B1(8 bits) B2(8 bits), 8 bits ignored, D(2 bits), with remaining bits ignored up to the next frame sync pulse.

When the Digital Interface clocks are selected as inputs, FSa must be a 8 kHz clock input which indicates the start of the frame on the data input pin Bx. When the Digital Interface clocks are selected as outputs, FSa is an 8 kHz output pulse conforming to the selected format which indicates the frame beginning for both Tx and Rx directions.

When the Digital Interface clocks are selected as inputs, FSb is a 8 kHz clock input which defines the start of the frame on the data ouput pin Br. When the Digital Interface clocks are selected as outputs, FSb is a 8 kHz output pulse indicating the second 64kbit/s slot.

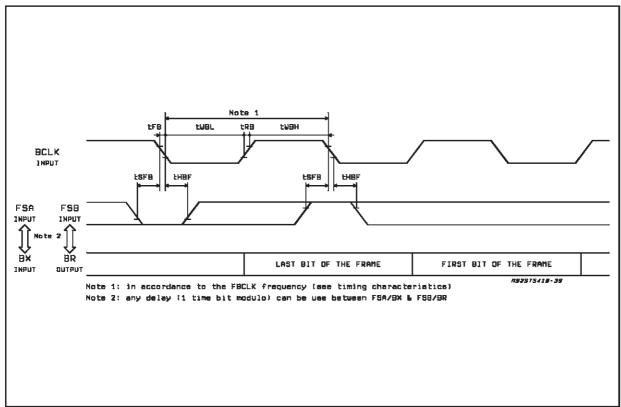

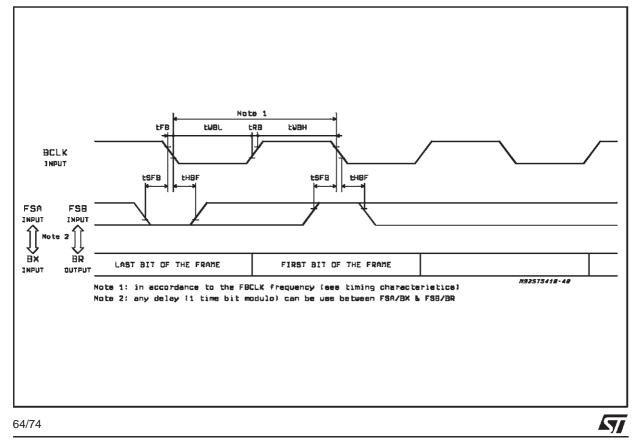

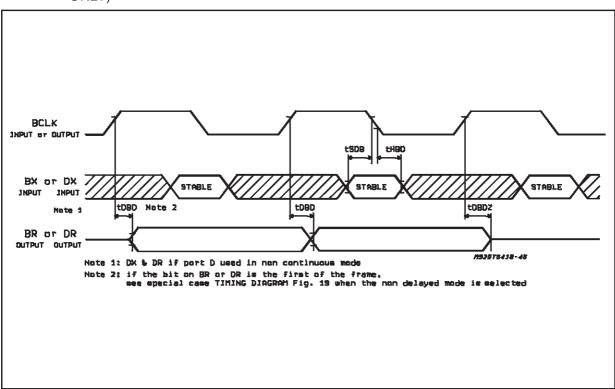

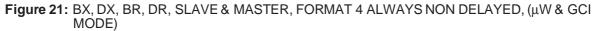

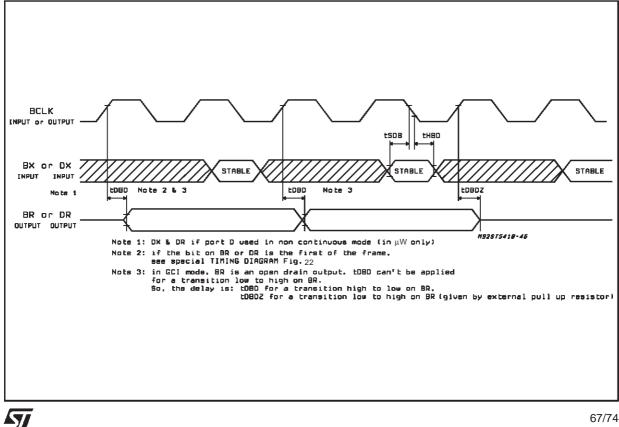

Two phase-relations between the rising edge of FSa/FSb and the first (or second for FSb as output) slot of the frame can be selected depending on format selected: Delayed timing mode or non Delayed timing mode.

Non delayed data mode is similar to long frame timing on the COMBOI/II series of devices: The first bit of the frame begins nominally coincident with the rising edge of FSa/b. When output, FSa is coincident with the first 8 bits wide time-slot while FSb is coincident with the second 8 bits wide time-slot. Non delayed mode is not available in format 2.

Delayed timing mode, which is similar to short frame sync timing on COMBO I/II, in which the FSa/b input must be set high at least a half cycle of BCLK earlier the frame beginning. When output, FSa 1bit wide pulse indicates the first 8 bits wide time-slot while FSb indicates the second. Delayed mode is not available in format 4.

2B+D basic access data to transmit to the line can be shifted in at the BCLK frequency on the falling edges during the assigned time-slots. When D channel port is enabled, only B1 & B2 data is shifted in during the assigned time slots. In format 4, data is shifted in at half the BCLK frequency on the receive falling edges.

2B+ D basic access data received from the line can be shifted out from the Br output at the BCLK frequency on the rising edges during the assigned time-slots. Elsewhere, Br is in the high impedance state. When the D channel port is enabled, only B1 & B2 data is shifted out from Br. In Format 4, data is shifted out at half the BCLK frequency on the transmit rising edges; there is 1.5 period delay between the rising transmit edge and the receive falling edge of BCLK.

Bit Clock BCLK determines the data shift rate on the Digital Interface. Depending on mode selected, BCLK is an input which may be any multiple of 8 kHz from 256 kHz to 6176 kHz or an output at a frequency depending on the format and the frequency selected. Possible frequencies are: 256 KHz, 512 KHz, 1536 KHz,

Figure 2: DSI Interface formats: MASTER mode.

2048 KHz, 2560 KHz.

In format 4 the use of 256kHz is forbidden.

BCLK is synchronous with FSa/b frame sync signal. When output, BCLK is phased locked to the recovered clock received from the line.

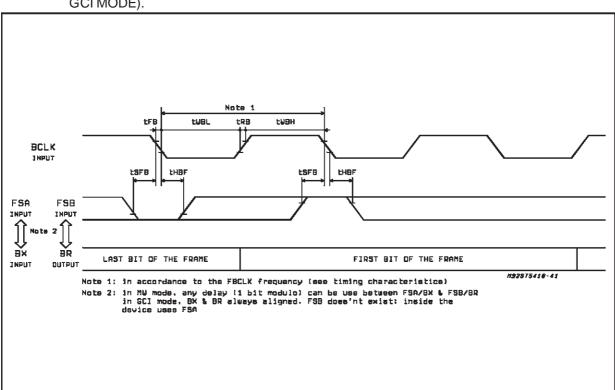

### GCI MODE

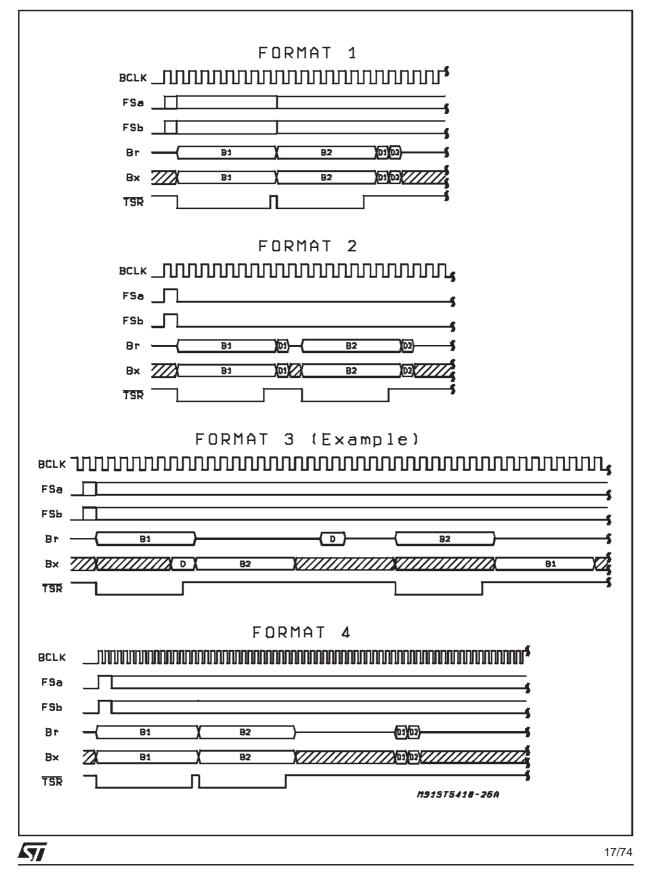

The GCI is a standard interface for the interconnection of dedicated ISDN components in the different equipments of the subscriber loop :

In a Terminal, GCI interlinks the STLC5412, the ISDN layer 2 (LAPD) controller and the voice/data processing components as an audio-processor or a Terminal Adaptor module.

In NT1-2, PABX subscriber line card, or central office line card (LT), GCI interlinks the UID, the ISDN Layer 2 (LAPD) controllers and eventually the backplane where the channels are multiplexed.

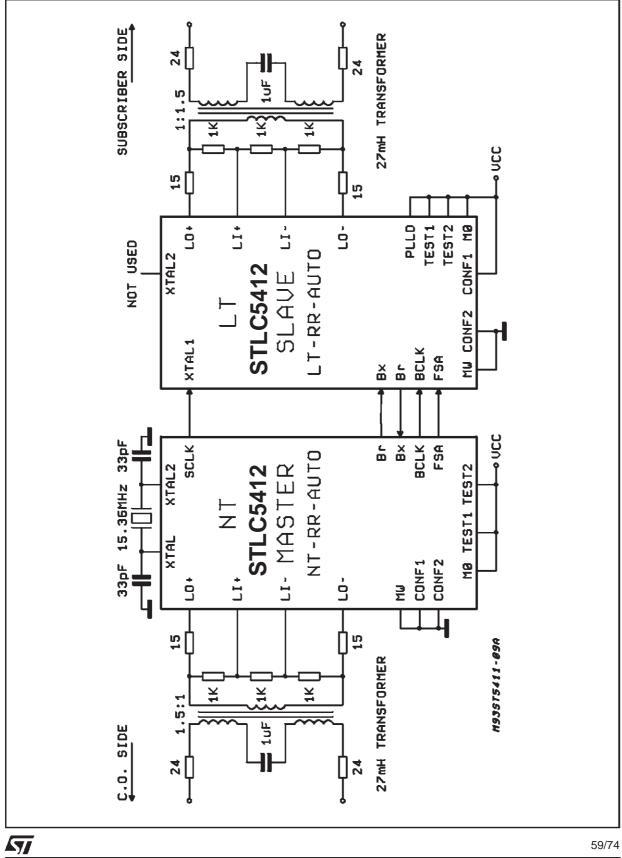

In NT1, GCI interlinks SID-GCI and STLC5412, via automode (NT1-auto). In Regenerators, GCI links both STLC5412 UID in automode (NT-RR-auto, LT-RR-auto). (See Fig. 4a)

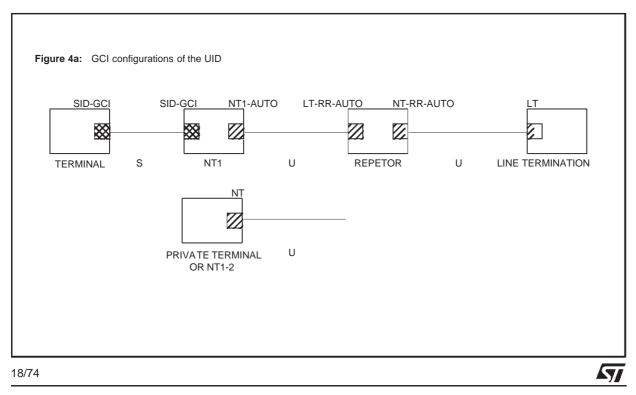

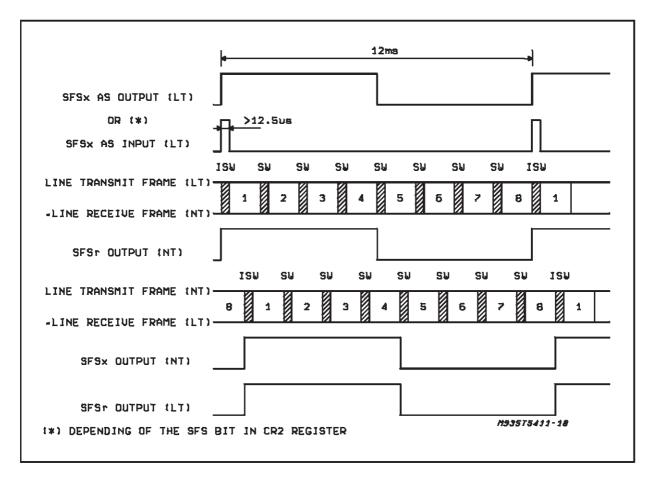

#### **Frame Structure**

2B+D data and control interface is transferred in a time-division multiplexed mode based on 8 kHz frame structure and assigned to four octets per frame and direction.(see fig.4b).

The 64 kbit/s channels B1 and B2 are conveyed in the first two octets; the third octet (M: Monitor) is used for transferring most of the control and status registers; the fourth octet (SC: Signalling & Control) contains the two D channel bits, the four C/I (command/Indicate) bits controlling the activation/deactivation procedures, and the E & A bits which support the handling of the Monitor channel.

Figure 4a: GCI configurations of the UID.

These four octets per frame serving one ISDN subscribers line form a GCI Channel. One GCI channel calls for a bit rate of 256 kbit/s.

In NT1-2s or subscriber Line Cards up to 8 GCI channels may be carried in a frame of a GCI multiplex. The bit rate of a GCI multiplex may be from 256 kbit/s and up to 3088 kbit/s. Adjacent 4-octet slots from the frame start are numbered 0 to 7. The GCI channel takes the number of the slot it occupies. Spare bits in the frame beyond 256 bits from the frame start will be ignored by GCI compatible devices but may be used for other purposes if required (see Fig.4c). GCI channel number is selected by biasing pins S0,S1,S2.

#### **Physical Links**

Four physical links are used in the GCI. Transmitted data to the line: Bx

Received data from the line: Br Data clock: BCLK Frame Synchronization clock: FSa

GCI is always synchronized by frame and data clocks derived by any master clock source.

A device used in NT mode can deliver clock sources able to synchronize GCI, either directly, or via a local Clock Generator synchronized on the line by means of the SCLK 15.36 MHz output clock. Frame clock and data clock could be independent of the internal devices clocks. Logical one on the Br output is the high impedance state while logical zero is low voltage. For E and A bits, active state is voltage Low while inactive state is high impedance state.

Figure 4b: GCI interface format.

### **STLC5412**

Figure 4c: GCI multiplex examples, (slave mode).

Data is transmitted in both directions at half the data clock rate. The information is clocked by the transmitter on the front edge of the data clock and can be accepted by the receiver after 1 to 1.5 period of the data clock.

The data clock (BCLK) is a square wave signal at twice the data transmission frequency on Bx and Br with a 1 to 1 duty cycle. The frequency can be choosen from 512 to 6176 kHz with 16 kHz modularity. Data transmission rate depends only on the data clock rate.

The Frame Clock FSa is a 8 kHz signal for synchronization of data transmission. The front edge of this signal gives the time reference of the first bit in the first GCI input and output channel, and reset the slot counter at the start of each frame.

When some GCI channels are not selected on devices connected to the same GCI link, these time slots are free for alternative uses.

GCI configuration selection is done by biasing of input pins MW, M0, CONF1, CONF2 according to Table 1.

| Pin Nu | umber | Pin name      |             |       | Configuration |            |            |

|--------|-------|---------------|-------------|-------|---------------|------------|------------|

| PLCC44 | DIP28 |               | LT/NT12 (1) | NT/TE | NT1-AUTO      | LT-RR-AUTO | NT-RR-AUTO |

| 43     | 28    | MW            | 0           | 0     | 0             | 0          | 0          |

| 42     | 27    | MO            | 0           | 1     | 1             | 1          | 1          |

| 27     | 19    | S1/CONF1      | S1          | 0     | 1             | 1          | 0          |

| 25     | 17    | S2/CONF2      | S2          | 1     | 1             | 0          | 0          |

| 10     | 7     | S0/FSb/TEST2  | S0          | FSb   | TEST2         | TEST2      | TEST2      |

| 26     | 18    | IO1/ES1 (2)   | IO1         | IO1   | ES1           | PLDD       | ES1        |

| 24     | 16    | IO2/ES2 (2)   | IO2         | IO2   | ES2           | EC         | ES2        |

| 23     | 15    | IO3/EC (2)    | IO3         | IO3   | EC            | LFS        | LFS        |

| 22     | 14    | IO4/TEST1 (2) | IO4         | IO4   | TEST1         | TEST1      | TEST1      |

| 35     | 22    | SFSx/RFS (2)  | SFSx        | SFSx  | SFSx          | RFS        | RFS        |

Table 1: GCI Configuration selection.

(1) Differentation between LT and NT configuration done by bit NTS in CR2 register; GCI in slave mode. When NT1-AUTO or NT-RR-AUTO configuration is selected, BCLK bit clock frequency of 512 kHz is automatically selected

When NT configuration is selected, BCLK bit clock frequency of 1536 kHz is automatically selected. (2) Connected to Vcc through internal pull-up resistors.

#### **Monitor channel**

The Monitor channel is used to write and read all STLC5412 internal registers. Protocol on the Monitor channel allows a bidirectional transfer of bytes between UID and a control unit with acknowledgement at each received byte. Bytes are transmitted on the Br output and received on the Bx input in the Monitor channel time slot.

A write or read cycle is always constituted of two bytes.(see fig. 5). It is possible to operate several write or read cycles within a single monitor message.

Note: Special format is used for EOC channel.

### Write cycle

The format to write a message into the UID is:

| A7       | A6 | A5 | A4 | A3 | A2 | A1 | A0 |  |  |

|----------|----|----|----|----|----|----|----|--|--|

| 1st byte |    |    |    |    |    |    |    |  |  |

| D7       | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

|----------|----|----|----|----|----|----|----|--|--|

| 2nd byte |    |    |    |    |    |    |    |  |  |

- A7-A1: Register Address

- A0: Write/Read back Indicator D7-D0: Register Content

After the first byte is shifted in, Register address is decoded. A0 set low indicates a write cycle: the content of the following received byte has to be loaded into the addressed register.

A0 set high indicates a read-back cycle request. The second byte content is not significative. STLC5412 will respond to the request by sending back a message with the register content associated with its own address. It is then possible for the microprocessor to receive the required register content after several other pending messages. To avoid any loss of data, it is recommended to operate only one read-back request at a time.

Note: Special format is used for EOC channel.

#### **Read cycle**

When UID has a register content to send to the controller, it send it on the monitor channel directly. Note that the data to send can be the content of a Register previously requested by the controller by means of a read-back request.

The format of the message sent by the UID is:

| A7       | A6 | A5 | A4 | A3 | A2 | A1 | A0 |  |  |  |

|----------|----|----|----|----|----|----|----|--|--|--|

| 1st byte |    |    |    |    |    |    |    |  |  |  |

| D7       | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| 2nd byte |    |    |    |    |    |    |    |  |  |  |

| A0:    | forced to 0 if spontaneous      |

|--------|---------------------------------|

|        | interrupt, forced to 1 if read- |

|        | back                            |

| D7-D0: | Register Content                |

### **Exchange Protocol**

STLC5412 validates a received byte if it is detected two consecutive times identical. (see fig. 5) The exchange protocol is identical for both directions. The sender uses the E bit to indicate that it is sending a Monitor byte while the receiver uses A bit to acknowledge the received byte. When no message is transferred, E bit and A bit are forced to inactive state.

A transmission is started by the sender (Transmit section of the Monitor channel protocol handler) by putting the E bit from inactive to active state and by sending the first byte on Monitor channel in the same frame. Transmission of a message is allowed only if A bit sent from the receiver has been set inactive for at least two consecutive frames. When the receiver is ready, it validates the incoming byte when received identical in two consecutive frames. Then, the receiver set A bit from the inactive to the active state (preacknowledgement) and maintain active at least in the following frame (acknowledgement).

If validation is not possible (two last bytes received are not identical) the receiver aborts the message by setting the A bit active for only a single frame. The second byte can be transmitted by the sender putting the E bit from the active to the inactive state and sending the second byte on the Monitor channel in the same frame. The E bit is set inactive for only one frame. If it remains inactive more than one frame, it is an end of message. The second byte may be transmitted only after receiving of the pre-acknowledgement of the previous byte . Each byte has to be transmitted at least in two consecutive frames.

The receiver validates the current received byte as for the first one and then set the A bit in the next two frames first from the active state to the inactive state (pre-acknowledgement) and back to the active (acknowledgement). If the receiver cannot validates the received current byte (two bytes received not identical)it pre-acknowledges normally but let the A bit in the inactive state in the next frame which indicates an abort request . If a message sent by the UID is aborted, the UID will send again the complete message until receiving of an acknowledgement . A message received by the UID can be acknowledged or aborted with flow Control.

The most significant bit (MSB) of Monitor byte is sent first on the Monitor channel. E & A bits are active low and inactive state on Br is 5 V. When no byte is transmitted, Monitor channel time slot

on Br is in the high impedance state.

A 24 ms timer is implemented in the UID. This timer (when enabled) starts each time the sender starts a byte sending and waits for a pre acknowledgement.

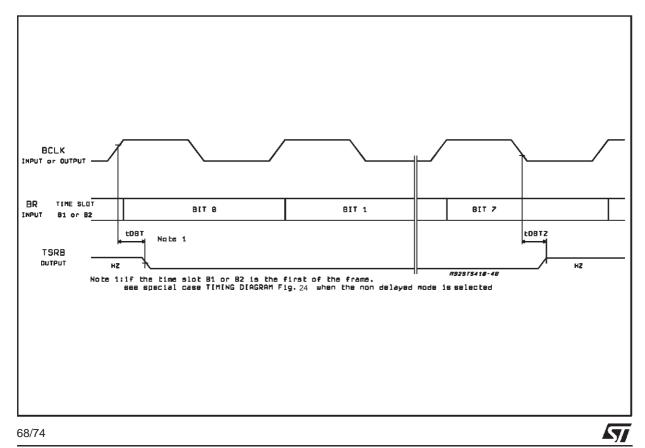

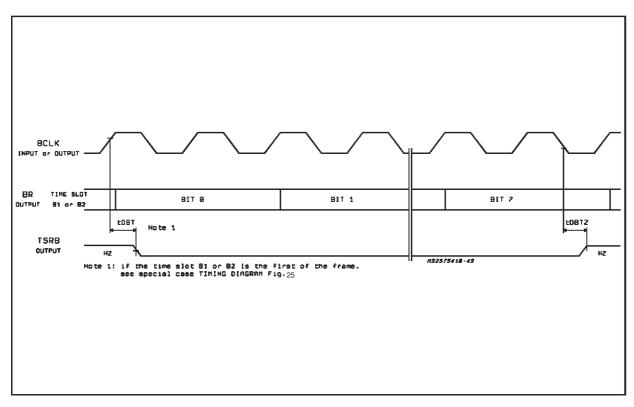

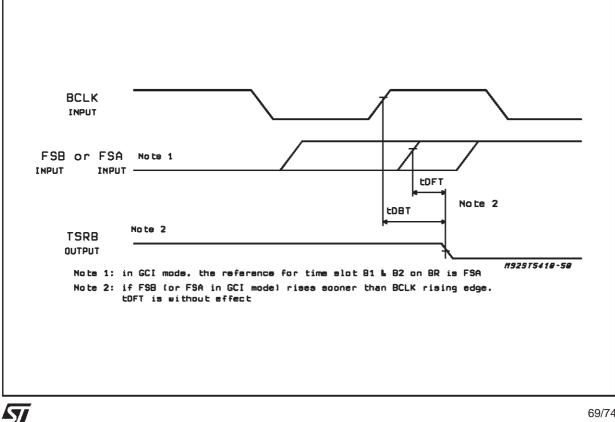

#### C/I channel