## NVRAM CONTROLLER for up to TWO LPSRAM

- CONVERT LOW POWER SRAMs into NVRAMs

- PRECISION POWER MONITORING and POWER SWITCHING CIRCUITRY

- AUTOMATIC WRITE-PROTECTION when V<sub>CC</sub> is OUT-OF-TOLERANCE

- CHOICE of SUPPLY VOLTAGES and POWER-FAIL DESELECT VOLTAGES:

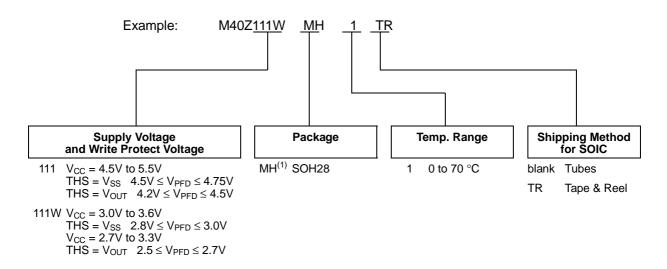

- $\begin{array}{ll} \ \mbox{M40Z111:} \\ \mbox{Vcc} = 4.5\mbox{V to } 5.5\mbox{V} \\ \mbox{THS} = \mbox{Vss} \ \ 4.5\mbox{V} \leq \mbox{V}_{\mbox{PFD}} \leq 4.75\mbox{V} \\ \mbox{THS} = \mbox{V}_{\mbox{OUT}} \ \ 4.2\mbox{V} \leq \mbox{V}_{\mbox{PFD}} \leq 4.5\mbox{V} \end{array}$

- $\begin{array}{lll} & \text{M40Z111W:} \\ & \text{V}_{\text{CC}} = 3.0 \text{V to } 3.6 \text{V} \\ & \text{THS} = \text{V}_{\text{SS}} & 2.8 \text{V} \leq \text{V}_{\text{PFD}} \leq 3.0 \text{V} \\ & \text{V}_{\text{CC}} = 2.7 \text{V to } 3.3 \text{V} \\ & \text{THS} = \text{V}_{\text{OUT}} & 2.5 \leq \text{V}_{\text{PFD}} \leq 2.7 \text{V} \end{array}$

- LESS THAN 15ns CHIP ENABLE ACCESS PROPAGATION DELAY (for 5.0V device)

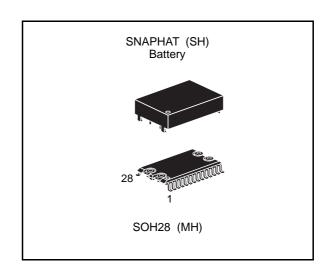

- PACKAGING INCLUDES a 28-LEAD SOIC and SNAPHAT® TOP (to be Ordered Separately)

- SOIC PACKAGE PROVIDES DIRECT CONNECTION for a SNAPHAT TOP which CONTAINS the BATTERY

#### **DESCRIPTION**

The M40Z111/111W NVRAM Controller is a self-contained device which converts a standard low-power SRAM into a non-volatile memory.

A precision voltage reference and comparator monitors the  $V_{\text{CC}}$  input for an out-of-tolerance condition.

**Table 1. Signal Names**

| THS              | Threshold Select Input         |

|------------------|--------------------------------|

| Ē                | Chip Enable Input              |

| Econ             | Conditioned Chip Enable Output |

| V <sub>OUT</sub> | Supply Voltage Output          |

| V <sub>CC</sub>  | Supply Voltage                 |

| V <sub>SS</sub>  | Ground                         |

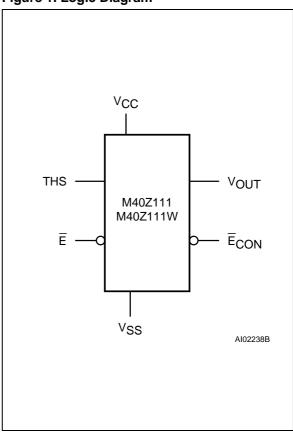

Figure 1. Logic Diagram

February 1999 1/12

Table 2. Absolute Maximum Ratings (1)

| Symbol               | Parameter                                              | Value                        | Unit |

|----------------------|--------------------------------------------------------|------------------------------|------|

| T <sub>A</sub>       | Ambient Operating Temperature                          | 0 to 70                      | °C   |

| T <sub>STG</sub>     | Storage Temperature (V <sub>CC</sub> Off) SNAPHAT SOIC | -40 to 85<br>-55 to 125      | °C   |

| T <sub>SLD</sub> (2) | Lead Solder Temperature for 10 seconds                 | 260                          | °C   |

| V <sub>IO</sub>      | Input or Output Voltages                               | -0.3 to V <sub>CC</sub> +0.3 | V    |

| V <sub>CC</sub>      | Supply Voltage                                         | –0.3 to 7                    | V    |

| lo                   | Output Current                                         | 20                           | mA   |

| P <sub>D</sub>       | Power Dissipation                                      | 1                            | W    |

Notes: 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to the absolute maximum rating conditions for extended periods of time may affect reliability.

CAUTION: Negative undershoots below -0.3 volts are not allowed on any pin while in the Battery Back-up mode.

CAUTION: Do NOT wave solder SOIC to avoid damaging SNAPHAT sockets.

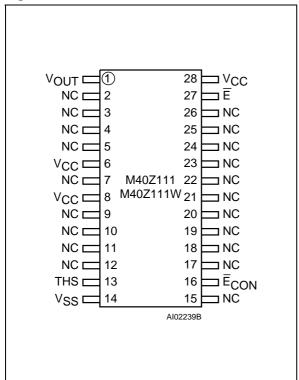

**Figure 2. SOIC Pin Connections**

Warning: NC = Not Connected.

### **DESCRIPTION** (cont'd)

When an invalid  $V_{\underline{CC}}$  condition occurs, the conditioned chip enable ( $\overline{E}_{CON}$ ) output is forced inactive to write-protect the stored data in the SRAM.

During a power failure, the SRAM is switched from the  $V_{CC}$  pin to the lithium cell within the SNAPHAT to provide the energy required for data retention. On a subsequent power-up, the SRAM remains write protected until a valid power condition returns.

The 28 pin 330mil SOIC provides sockets with gold plated contacts at both ends for direct connection to a separate SNAPHAT housing containing the battery. The unique design allows the SNAPHAT battery package to be mounted on top of the SOIC package after the completion of the surface mount process. Insertion of the SNAPHAT housing after reflow prevents potential battery damage due to the high temperatures required for device surfacemounting. The SNAPHAT housing is keyed to prevent reverse insertion. The SOIC and battery packages are shipped separately in plastic antistatic tubes or in Tape & Reel form. For the 28 lead SOIC, the battery package (i.e. SNAPHAT) part number is "M4Z28-BR00SH1" or "M4Z32-BR00SH1" (See Table 7).

### **OPERATION**

The M40Z111/111W, as shown in Figure 4, can control up to two standard low-power SRAMs. These SRAMs must be configured to have the chip enable input disable all other input signals. Most slow, low-power SRAMs are configured like this, however many fast SRAMs are not. During normal operating conditions, the conditioned chip enable ( $\overline{E}_{CON}$ ) output pin follows the chip enable ( $\overline{E}$ ) input pin with timing shown in Table 6. An internal switch connects  $V_{CC}$  to  $V_{OUT}$ . This switch has a voltage drop of less than 0.3V ( $I_{OUT1}$ ).

<sup>2.</sup> Soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

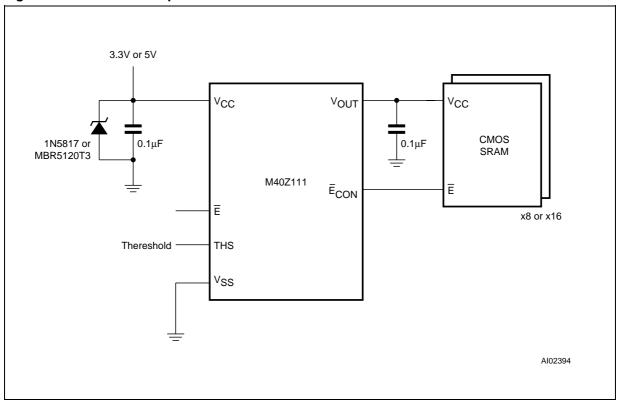

Figure 3. Hardware Hookup

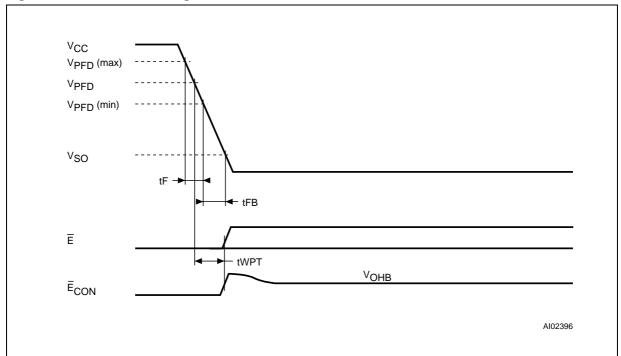

When  $V_{CC}$  degrades during a power failure, $\overline{E}_{CON}$  is forced inactive independent of  $\overline{E}$ . In this situation, the SRAM is unconditionally write protected as  $V_{CC}$  falls below an out-of-tolerance threshold ( $V_{PFD}$ ). The power fail detection value associated with  $V_{PFD}$  is selected by the THS pin and is shown in Table 5. (Note: THS pin must be connected to either  $V_{SS}$  or  $V_{OUT}$ ). If chip enable access is in progress during a power fail detection, that memory cycle continues to completion before the memory is write protected. If the memory cycle is not terminated within time  $t_{WP}$ ,  $\overline{E}_{CON}$  is unconditionally driven high, write protecting the SRAM.

A power failure during a write cycle may corrupt data at the currently addressed location, but does not jeopardize the rest of the SRAM's contents. At voltages below V<sub>PFD</sub> (min), the user can be assured the memory will be write protected provided the V<sub>CC</sub> fall time exceeds t<sub>F</sub>.

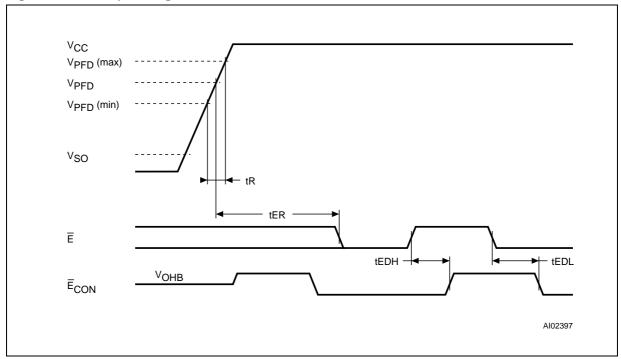

As  $V_{CC}$  continues to degrade, the internal switch disconnects  $V_{CC}$  and connects the internal battery to  $V_{OUT}$ . This occurs at the switchover voltage ( $V_{SO}$ ). Below the  $V_{SO}$ , the battery provides a voltage  $V_{OHB}$  to the SRAM and can supply current  $I_{OUT2}$  (see Table 5). When  $V_{CC}$  rises above  $V_{SO}$ ,  $V_{OUT}$  is switched back to the supply voltage. Output

E<sub>CON</sub> is held inactive for t<sub>ER</sub> (200ms maximum) after the power supply has reached V<sub>PFD</sub>, independent of the E input, to allow for processor stabilization (see Figure 6).

### **DATA RETENTION LIFETIME CALCULATION**

Most low power SRAMs on the market today can be used with the M40Z111/111W NVRAM Controller. There are, however some criteria which should be used in making the final choice of which SRAM to use. The SRAM must be designed in a way where the chip enable input disables all other inputs to the SRAM. This allows inputs to the M40Z111/111W and SRAMs to be Don't Care once V<sub>CC</sub> falls below V<sub>PFD</sub> (min). The SRAM should also guarantee data retention down to V<sub>CC</sub> =2.0V. The chip enable access time must be sufficient to meet the system needs with the chip enable propagation delays included. If the SRAM includes a second chip enable pin ( $\overline{\text{E2}}$ ), this pin should be tied to  $V_{\text{OUT}}$ . If data retention lifetime is a critical parameter for the system, it is important to review the data retention current specifications for the particular SRAMs being evaluated. Most SRAMs specify a data retention current at 3.0V.

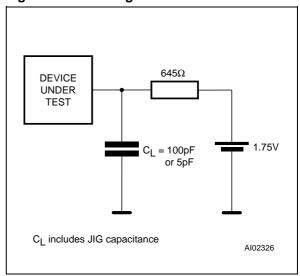

**Table 3. AC Measurement Condition**

| Input Rise and Fall Times             | ≤ 5ns   |

|---------------------------------------|---------|

| Input Pulse Voltages                  | 0 to 3V |

| Input and Output Timing Ref. Voltages | 1.5V    |

Note that Output Hi-Z is defined as the point where data is no longer driven.

Manufacturers generally specify a typical condition for room temperature along with a worst case condition (generally at elevated temperatures). The system level requirements will determine the choice of which value to use. The data retention current value of the SRAMs can then be added to the I<sub>CCDR</sub> value of the M40Z111/111W to determine the total current requirements for data retention.

The available battery capacity for the SNAPHAT of your choice can then be divided by this current to determine the amount of data retention available (see Table 7). For more information on Battery Storage Life refer to the Application Note AN1012.

#### VCC NOISE AND NEGATIVE-GOING TRAN-SIENTS

lcc transients, including those produced by output switching, can produce voltage fluctuations, resulting in spikes on the  $V_{\rm CC}$  bus. These transients can be reduced if capacitors are used to store energy, which stabilizes the  $V_{\rm CC}$  bus. The energy stored in the bypass capacitors will be released as low going spikes are generated or energy will be absorbed when overshoots occur.

Figure 4. AC Testing Load Circuit

A ceramic bypass capacitor value of  $0.1\mu F$  (as shown in Figure 4) is recommended in order to provide the needed filtering. In addition to transients that are caused by normal SRAM operation, power cycling can generate negative voltage spikes on  $V_{CC}$  that drive it to values below  $V_{SS}$  by as much as one volt. These negative spikes can cause data corruption in the SRAM while in battery backup mode. To protect from these voltage spikes, ST recommends connecting a schottky diode from  $V_{CC}$  to  $V_{SS}$  (cathode connected to  $V_{CC}$ , anode to  $V_{SS}$ ).

Table 4. Capacitance  $^{(1)}$  (T<sub>A</sub> = 25°C; f = 1MHz)

| Symbol               | Parameter Test Condition |                       | Min | Max | Unit |

|----------------------|--------------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub>      | Input Capacitance        | $V_{IN} = 0V$         |     | 8   | pF   |

| C <sub>OUT</sub> (2) | Output Capacitance       | V <sub>OUT</sub> = 0V |     | 10  | pF   |

Note: 1. Sampled only, not 100% tested.

2. Outputs deselected.

Table 5A. DC Characteristics for M40Z111 ( $T_A = 0$  to  $70^{\circ}$ C;  $V_{CC} = 4.5V$  to 5.5V)

| Symbol                         | Parameter                                  | Test Condition                          | Min             | Тур  | Max                   | Unit |

|--------------------------------|--------------------------------------------|-----------------------------------------|-----------------|------|-----------------------|------|

| I <sub>LI</sub> <sup>(1)</sup> | Input Leakage Current                      | $0V \le V_{IN} \le V_{CC}$              |                 |      | ±1                    | μА   |

| I <sub>LO</sub> <sup>(1)</sup> | Output Leakage Current                     | $0V \leq V_{OUT} \leq V_{CC}$           |                 |      | ±1                    | μΑ   |

| I <sub>CC</sub>                | Supply Current                             | Outputs open                            |                 | 3    | 6                     | mA   |

| V <sub>IL</sub>                | Input Low Voltage                          |                                         | -0.3            |      | 0.8                   | V    |

| V <sub>IH</sub>                | Input High Voltage                         |                                         | 2.2             |      | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>                | Output Low Voltage                         | I <sub>OL</sub> = 4.0mA                 |                 |      | 0.4                   | V    |

| V <sub>OH</sub>                | Output High Voltage                        | I <sub>OH</sub> = -2.0mA                | 2.4             |      |                       | V    |

| V <sub>OHB</sub>               | V <sub>OH</sub> Battery Back-up            | $I_{OUT2} = 1.0 \mu A$                  | 2.0             | 2.9  | 3.6                   | V    |

| I <sub>OUT1</sub>              | V <sub>OUT</sub> Current (Active)          | V <sub>OUT</sub> > V <sub>CC</sub> -0.3 |                 |      | 160                   | mA   |

| 10011                          | V <sub>001</sub> Guilent (Nouve)           | V <sub>OUT</sub> > V <sub>CC</sub> -0.2 |                 |      | 100                   | mA   |

| I <sub>OUT2</sub>              | V <sub>OUT</sub> Current (Battery Back-up) | $V_{OUT} > V_{BAT} - 0.3$               |                 | 100  |                       | μΑ   |

| ICCDR                          | Data Retention Mode Current                |                                         |                 |      | 150                   | nA   |

| THS                            | Threshold Select Voltage                   |                                         | V <sub>SS</sub> |      | V <sub>OUT</sub>      | V    |

| $V_{PFD}$                      | Power-fail Deselect Voltage (THS = 0)      |                                         | 4.5             | 4.6  | 4.75                  | V    |

| * PFD                          | Power-fail Deselect Voltage (THS = 1)      |                                         | 4.2             | 4.35 | 4.5                   | V    |

| V <sub>SO</sub>                | Battery Back-up Switchover Voltage         |                                         |                 | 3.0  |                       | V    |

Note: 1. Outputs deselected.

Table 5B. DC Characteristics for M40Z111W ( $T_A = 0$  to  $70^{\circ}$ C;  $V_{CC} = 3V$  to 3.6V or 2.7V to 3.3V)

| Symbol                         | Parameter                                  | Test Condition                | Min             | Тур | Max                   | Unit |

|--------------------------------|--------------------------------------------|-------------------------------|-----------------|-----|-----------------------|------|

| I <sub>LI</sub> <sup>(1)</sup> | Input Leakage Current                      | $0V \le V_{IN} \le V_{CC}$    |                 |     | ±1                    | μА   |

| I <sub>LO</sub> <sup>(1)</sup> | Output Leakage Current                     | $0V \leq V_{OUT} \leq V_{CC}$ |                 |     | ±1                    | μА   |

| I <sub>CC</sub>                | Supply Current                             | Outputs open                  |                 | 2   | 4                     | mA   |

| V <sub>IL</sub>                | Input Low Voltage                          |                               | -0.3            |     | 0.8                   | V    |

| V <sub>IH</sub>                | Input High Voltage                         |                               | 2.0             |     | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>                | Output Low Voltage                         | $I_{OL} = 4.0 \text{mA}$      |                 |     | 0.4                   | V    |

| Vон                            | Output High Voltage                        | $I_{OH} = -2.0$ mA            | 2.4             |     |                       | V    |

| V <sub>OHB</sub>               | V <sub>OH</sub> Battery Back-up            | $I_{OUT2} = 1.0 \mu A$        | 2.0             | 2.9 | 3.6                   | V    |

| I <sub>OUT1</sub>              | V <sub>OUT</sub> Current (Active)          | $V_{OUT} > V_{CC} - 0.3$      |                 |     | 100                   | mA   |

| 10011                          | Voor Garrette (Nouve)                      | $V_{OUT} > V_{CC} - 0.2$      |                 |     | 65                    | mA   |

| I <sub>OUT2</sub>              | V <sub>OUT</sub> Current (Battery Back-up) | $V_{OUT} > V_{BAT} - 0.3$     |                 | 100 |                       | μА   |

| I <sub>CCDR</sub>              | Data Retention Mode Current                |                               |                 |     | 150                   | nA   |

| THS                            | Threshold Select Voltage                   |                               | V <sub>SS</sub> |     | V <sub>OUT</sub>      | V    |

| $V_{PFD}$                      | Power-fail Deselect Voltage (THS = 0)      |                               | 2.8             | 2.9 | 3.0                   | V    |

| * PFD                          | Power-fail Deselect Voltage (THS = 1)      |                               | 2.5             | 2.6 | 2.7                   | V    |

| V <sub>SO</sub>                | Battery Back-up Switchover Voltage         |                               |                 | 2.5 |                       | ٧    |

Note: 1. Outputs deselected.

Table 6. Power Down/Up AC Characteristics ( $T_A = 0 \text{ to } 70^{\circ}\text{C}$ )

| Symbol                                         | Parameter                                                                  | Min      | Max | Unit |    |  |

|------------------------------------------------|----------------------------------------------------------------------------|----------|-----|------|----|--|

| t <sub>F</sub> <sup>(1)</sup>                  | V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> Fall Time |          | 300 |      | μs |  |

| t <sub>FB</sub> (2)                            | V <sub>PFD</sub> (min) to V <sub>SO</sub> V <sub>CC</sub> Fall Time        |          | 10  |      | μs |  |

| t <sub>R</sub>                                 | V <sub>PFD</sub> (min) to V <sub>PFD</sub> (max) V <sub>CC</sub> Rise Time |          | 10  |      | μs |  |

| t <sub>EDL</sub>                               | t <sub>EDL</sub> Chip Enable Propagation Delay                             | M40Z111  |     | 15   | ns |  |

| EDL                                            | Only Enable Flopagation Belay                                              | M40Z111W |     | 20   | ns |  |

| tenu                                           | Chip Enable Propagation Delay                                              | M40Z111  |     | 10   | ns |  |

| t <sub>EDH</sub> Chip Enable Propagation Delay | Only Enable Flopagation Belay                                              | M40Z111W |     | 20   | ns |  |

| t <sub>ER</sub>                                | Chip Enable Recovery                                                       |          | 40  | 200  | ms |  |

| 4                                              | Write Protect Time                                                         | M40Z111  | 40  | 150  | μs |  |

| twp                                            | Write Protect Time M40Z111W                                                |          | 40  | 250  | μs |  |

Notes: 1. V<sub>PFD</sub> (max) to V<sub>PFD</sub> (min) fall time of less than t<sub>F</sub> may result in deselection/write protection not occurring until 200 μs after V<sub>CC</sub> passes V<sub>PFD</sub> (min).

2. V<sub>PFD</sub> (min) to V<sub>SO</sub> fall time of less than t<sub>FB</sub> may cause corruption of RAM data.

Figure 5. Power Down Timing

Figure 6. Power Up Timing

Table 7. Battery Table

| Part Number   | Description                      | Package |

|---------------|----------------------------------|---------|

| M4Z28-BR00SH1 | Lithium Battery (50mAh) SNAPHAT  | SH      |

| M4Z32-BR00SH1 | Lithium Battery (130mAh) SNAPHAT | SH      |

### **ORDERING INFORMATION SCHEME**

Note: 1. The SOIC package (SOH28) requires the battery package (SNAPHAT) which is ordered separately under the part number "M4ZxxBR00SH1" in plastic tube or "M4Zxx-BR00SH1TR" in Tape & Reel form.

Caution: Do not place the SNAPHAT battery package "M4Zxx-BR00SH1" in conductive foam since will drain the lithium button-cell battery.

For a list of available options (Package, etc...) or for further information on any aspect of this device, please contact the STMicroelectronics Sales Office nearest to you.

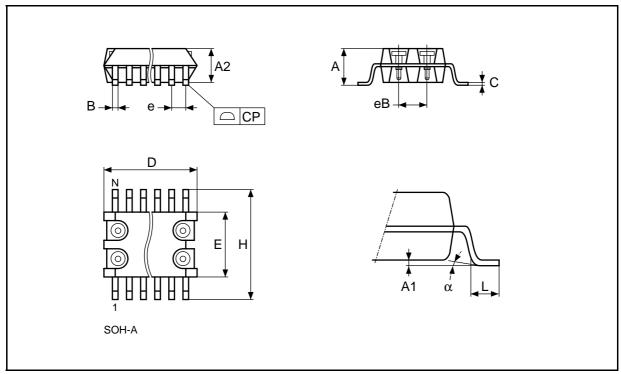

## SOH28 - 28 lead Plastic Small Outline, battery SNAPHAT

| Symb |      | mm    |       |       | inches |       |

|------|------|-------|-------|-------|--------|-------|

| Symb | Тур  | Min   | Max   | Тур   | Min    | Max   |

| А    |      |       | 3.05  |       |        | 0.120 |

| A1   |      | 0.05  | 0.36  |       | 0.002  | 0.014 |

| A2   |      | 2.34  | 2.69  |       | 0.092  | 0.106 |

| В    |      | 0.36  | 0.51  |       | 0.014  | 0.020 |

| С    |      | 0.15  | 0.32  |       | 0.006  | 0.012 |

| D    |      | 17.71 | 18.49 |       | 0.697  | 0.728 |

| Е    |      | 8.23  | 8.89  |       | 0.324  | 0.350 |

| е    | 1.27 | _     | _     | 0.050 | _      | _     |

| eB   |      | 3.20  | 3.61  |       | 0.126  | 0.142 |

| Н    |      | 11.51 | 12.70 |       | 0.453  | 0.500 |

| L    |      | 0.41  | 1.27  |       | 0.016  | 0.050 |

| α    |      | 0°    | 8°    |       | 0°     | 8°    |

| N    |      | 28    |       | 28    |        |       |

| СР   |      |       | 0.10  |       |        | 0.004 |

Drawing is not to scale.

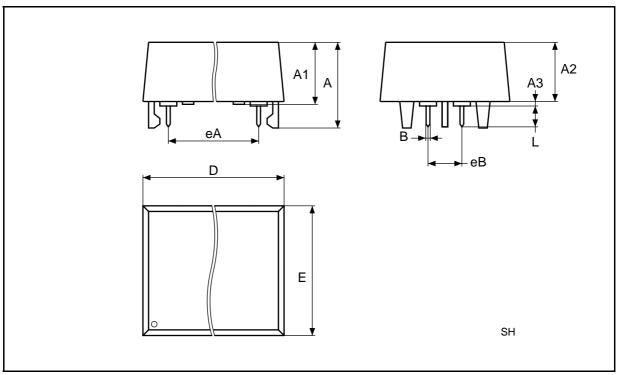

# SH - SNAPHAT Housing for 28 lead Plastic Small Outline

| Symb   | mm  |       |       | inches |       |       |

|--------|-----|-------|-------|--------|-------|-------|

| Gyilib | Тур | Min   | Max   | Тур    | Min   | Max   |

| Α      |     |       | 9.78  |        |       | 0.385 |

| A1     |     | 6.73  | 7.24  |        | 0.265 | 0.285 |

| A2     |     | 6.48  | 6.99  |        | 0.255 | 0.275 |

| A3     |     |       | 0.38  |        |       | 0.015 |

| В      |     | 0.46  | 0.56  |        | 0.018 | 0.022 |

| D      |     | 21.21 | 21.84 |        | 0.835 | 0.860 |

| Е      |     | 14.22 | 14.99 |        | 0.560 | 0.590 |

| eA     |     | 15.55 | 15.95 |        | 0.612 | 0.628 |

| eB     |     | 3.20  | 3.61  |        | 0.126 | 0.142 |

| L      |     | 2.03  | 2.29  |        | 0.080 | 0.090 |

Drawing is not to scale.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 1999 STMicroelectronics - All Rights Reserved

® SNAPHAT is a registered trademark of STMicroelectronics

All other names are the property of their respective owners

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com