# Analog LCD Display Engine for XGA and SXGA Resolutions

TARGET SPECIFICATION

### **Feature Overview**

- Programmable Context Sensitive<sup>™</sup> Scaling

- High-quality Up-scaling and Down-scaling

- Integrated 9-bit ADC/PLL

- IQSync<sup>™</sup> AutoSetup

- Integrated programmable Timing Controller

- Integrated Pattern Generator

- Perfect Picture<sup>™</sup> Technology

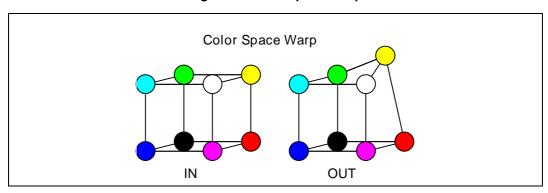

- sRGB 3D Color Warp

- Integrated OSD

- Advanced EMI reduction features

- Framelock operation with Safety Mode<sup>™</sup>

- Serial I<sup>2</sup>C interface

- Low power 0.18 µm process technology

## **General Description**

ADE3700 devices are a family of highly-integrated display engine ICs, enabling the most advanced, flexible, and cost-effective system-on-chip solutions for analog-only input LCD display applications.

The ADE3700 covers the full range of XGA and SXGA analog-only applications including Smart Panel designs.

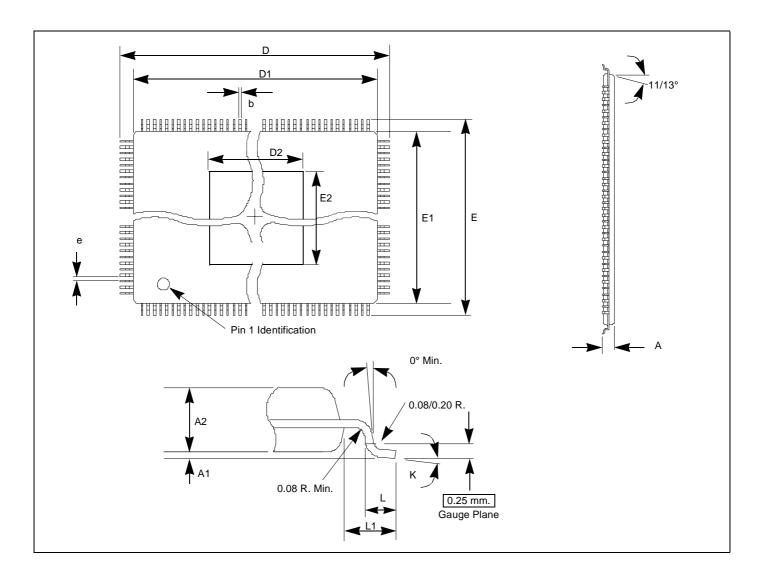

The ADE3700 family is pin-to-pin compatible and comes in a low-cost, 128-pin LQFP package.

ADE3700 devices use the same software platform and are backward-compatible with the previous generation of ADE3xxx Scaling Engines.

#### LCD Scaler Product Selector

| Product   | Pookogo  | Output Format Su | Input Interface Support |        |     |     |

|-----------|----------|------------------|-------------------------|--------|-----|-----|

| Product   | Package  | Resolution       | TCON                    | Analog | DVI | YUV |

| ADE3700X  | 128 LQFP | Up to XGA 75 Hz  |                         | Yes    |     |     |

| ADE3700XT | 128 LQFP | Up to XGA 75 Hz  | Yes                     | Yes    |     |     |

| ADE3700SX | 128 LQFP | Up to SXGA 75 Hz |                         | Yes    |     |     |

October 2003 1/89

#### Third Generation Context Sensitive™ Scaler

- Sharper text with Edge Enhancement

- RAM based coefficients for unique customization

- 5:1 Upscale and 2:1 Downscale

- Independent X Y axis zoom and shrink

## **Analog RGB input**

- 140 MHz 9-bit ADC

- Ultra low jitter digital Line Lock PLL

- Composite Sync and Sync on Green support

### IQsync™ AutoSetup

- AutoSetup configures phase, clock, level, and position

- Supports continuous calibration for reduced user intervention

- Automatically detects activity on input

- Compatible with all standard VESA and GTF modes

### Perfect Picture™ Technology

- Programmable 3D Color Warp

- Digital brightness, contrast, hue, and saturation gamma controls for all inputs

- Simple white point control

- Compatible with sRGB standard

- Video & Picture windowing

- Supports up to 7 different windows

- Independent window controls for contrast brightness, saturation, hue and gamma

#### Perfect Color™ Technology

- True color dithering for 12- and 18-bit panels

- Temporal and spatial dithering

- 30-bit programmable gamma table

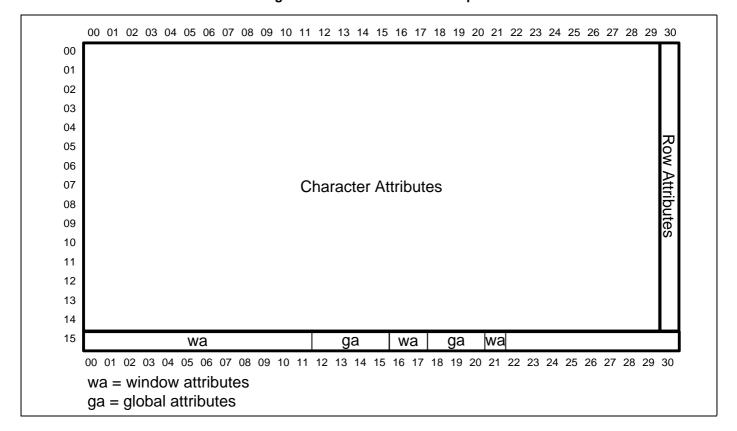

#### **OSD Engine**

- 256 RAM based 12x18 characters

- 1- and 4-bit per pixel color characters

- Bordering, shadowing, transparency, fade-in, and fade-out effects

- Supports font rotation

- Up to 4 sub windows

- 32-entry TrueColor LUT

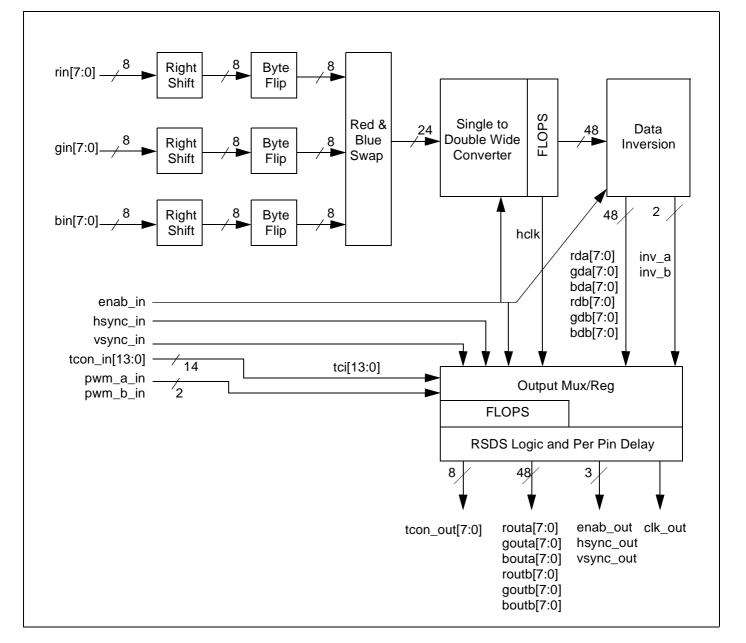

### **Programmable Timing Controller (TCON)**

- Highly programmable support for XGA SmartPanels

- Dual-function LVCMOS and RSDS outputs

- Supports 18-, 24-, 36-, and 48-bit RSDS outputs

- Advanced Flicker Detection and Reduction

- 12 programmable timing signals for row/ column control

- Wide range of drivers & TCON compatibility

- Simulation tools for easy programming

- Supports complex polarity generation for IPS panels

#### **Advanced EMI Reduction Features**

- Flexible data inversion / transition minimization, single, dual, and separate

- Per pin delay, 0 to 6ns in 0.4ns increments

- Adaptive Slew Rate control outputs

- Differential clock

- Spread spectrum -programmable digital FM modulation of the output clock with no external components

#### **Output Format**

- Supports resolutions up to SXGA @ 75Hz

- Supports 6- or 8-bit Panels

- Supports double or single pixel wide formats

# **Table of Contents**

| Chapter 1 | General Information                                                                                                                                                                                        | 5        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1       | Pin Descriptions                                                                                                                                                                                           | 7        |

| Chapter 2 | Functional Description                                                                                                                                                                                     |          |

| 2.1       | Global Control                                                                                                                                                                                             | 11       |

| 2.2       | FM Frequency Synthesizer                                                                                                                                                                                   | 16       |

| 2.3       | Analog-to-Digital Converter (ADC)                                                                                                                                                                          | 17       |

| 2.4       | Line Lock PLL                                                                                                                                                                                              | 18       |

| 2.5       | Sync Retiming (SRT)                                                                                                                                                                                        | 23       |

| 2.6       | Sync Measurement                                                                                                                                                                                           | 25       |

| 2.7       | Sync Multiplexer (SMUX)                                                                                                                                                                                    | 33       |

| 2.8       | Data Multiplexer                                                                                                                                                                                           | 37       |

| 2.9       | Data Measurement (DMEAS)  2.9.1 Edge Intensity  2.9.2 Pixel Sum  2.9.3 Minimum/Maximum Pixel  2.9.4 Pixel Cumulative Distribution (PCD)  2.9.5 Horizontal Position  2.9.6 Vertical Position  2.9.7 DE Size |          |

| 2.10      | LCD Scaler                                                                                                                                                                                                 | 42       |

| 2.11      | Output Sequencer  2.11.1 Frame Synchronization  2.11.2 Timing Unit  2.11.3 Signal Generation                                                                                                               | 45<br>45 |

| 2.12      | Timing Controller (TCON)                                                                                                                                                                                   | 48       |

| 2.13      | Pattern Generator  2.13.1 Screen Split  2.13.2 Pattern Engine  2.13.3 Borders                                                                                                                              | 54<br>55 |

| 2.14      | sRGB                                                                                                                                                                                                       | 60       |

| 2.15      | On-Screen Display (OSD)                                                                                                                                                                                    |          |

| 2.16      | Flicker                                                                                                                                                                                                    | 68       |

| 2.17      | Gamma                                                                                                                                                                                       | .70                  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| 2.18      | APC                                                                                                                                                                                         | .71                  |  |  |  |  |

| 2.19      | Output Multiplexer  2.19.1 Sub Block Function  2.19.2 RSDS  2.19.3 Per Pin Delay                                                                                                            | . 73<br>. 76         |  |  |  |  |

| 2.20      | Pulse Width Modulation (PWM)                                                                                                                                                                | .80                  |  |  |  |  |

| 2.21      | DFT Block                                                                                                                                                                                   | .81                  |  |  |  |  |

| 2.22      | I <sup>2</sup> C RAM Addresses                                                                                                                                                              | .83                  |  |  |  |  |

| Chapter 3 | Electrical Specifications                                                                                                                                                                   | 84                   |  |  |  |  |

| 3.1       | Absolute Maximum Ratings                                                                                                                                                                    | .84                  |  |  |  |  |

| 3.2       | Power Consumption Matrices                                                                                                                                                                  | .84                  |  |  |  |  |

| 3.3       | Nominal Operating Conditions85                                                                                                                                                              |                      |  |  |  |  |

| 3.4       | Preliminary Thermal Data                                                                                                                                                                    | .85                  |  |  |  |  |

| 3.5       | Preliminary DC Specifications  3.5.1 LVTTL 5 Volt Tolerant Inputs With Hysteresis  3.5.2 LVTTL 5 Volt Tolerant Inputs  3.5.3 LVTTL 5 Volt Tolerant I/O With Hysteresis  3.5.4 LVTTL Outputs | . 85<br>. 85<br>. 86 |  |  |  |  |

| 3.6       | Preliminary AC Specifications                                                                                                                                                               | .86                  |  |  |  |  |

| Chapter 4 | Package Mechanical Data                                                                                                                                                                     | 87                   |  |  |  |  |

| Chapter 5 | Revision History                                                                                                                                                                            | 88                   |  |  |  |  |

# 1 General Information

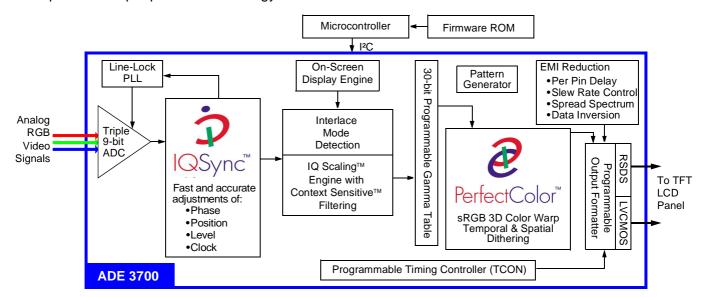

The ADE3700 family of devices is capable of implementing all of the advanced features of today's LCD monitor products. For maximum flexibility, an external microcontroller (MCU) is used for controlling the ADE3700 and other monitor functions.

---- DATA Timing Controller **CTRL DMEAS** Output Format Analog LCD Port Color Management Scaler GAMMA LUT OSE **SMEAS SCLK** Frequency Pattern Synthesizer Generator FM LLKPLL **INCLK SCLK** DOTCLK Freq. Synthesizer

Figure 1: ADE3700 Block Diagram

The ADE3700 architecture unburdens the MCU from all data-intensive pixel manipulations, providing an optimal blend of features and code customizing without incurring the cost of a 16-bit processor or memory. The key interactions between the monitor MCU and the ADE3700 can be broken down into the features shown in the table below.

**Blocks Used Feature Description of ADE3700 Operation Pages GLBL** Power-up / When power is first applied, the ADE3700 is asynchronously reset from a pin. 11 Initialize The MCU typically programs the ADE3700 with a number of default values **SMEAS** 25 and sets up the ADE3700 to identify activity on any of the input pins. All pre-LLK 18 configured values and RAMs, such as DVI settings, line-lock PLL settings, ADC 17 OSD characters, LCD timing values (output sequencer), scale kernels, OSD 62 gamma curves, sRGB color warp, APC dithering, output pin configuration **SCALER** 42 (OMUX), etc. can be pre-loaded into the ADE3700. The typical end state is GAMMA 70 that the ADE3700 is initialized into a low power mode, ready to turn active **SRGB** 60 once the power button is pressed. **OUTSEQ** 45 **TCON** 48 APC 71 **OMUX** 72 **Activity Detect** When the monitor has been powered on, the inputs can be monitored for **SMEAS** 25 active video sources. Based on the activity monitors, the MCU chooses an input or power down state.

Table 1: ADE3700 Features (Sheet 1 of 2)

Table 1: ADE3700 Features (Sheet 2 of 2)

| Feature                          | Description of ADE3700 Operation                                                                                                                                                                                                                                                                                                                                                         | Blocks Used                        | Pages                      |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------|--|--|

| Sync / Timing<br>Measurement     | Once an input source is selected, all available information on frequencies and line/pixel counts is measured for the selected source and made available to the MCU.                                                                                                                                                                                                                      | SMEAS                              | 25                         |  |  |

| Mode Set                         | GLBL<br>LLK<br>SRT<br>DMUX<br>SMUX<br>SCALER                                                                                                                                                                                                                                                                                                                                             | 11<br>18<br>23<br>37<br>32<br>42   |                            |  |  |

| Autotune                         | When the MCU calls for an autotune, the MCU sets up an iterative loop to search for the best phase, gain, offset, etc. At each step of the loop, the MCU kicks off a test in which the ADE3700 which performs extensive statistical analysis of the incoming data stream. The results of the analysis are made available to the MCU which is responsible for the optimization algorithm. | DMEAS<br>LLK<br>ADC<br>SMUX<br>SRT | 47<br>18<br>17<br>32<br>23 |  |  |

| Digital Contrast /<br>Brightness | In response to user OSD control, the MCU can program single 8-bit registers that set brightness and contrast for each color channel independently.                                                                                                                                                                                                                                       | SRGB                               | 60                         |  |  |

| White Point<br>Control           | In response to user OSD control, the MCU can program three 8-bit registers that set the white point for the output.                                                                                                                                                                                                                                                                      | SRGB                               | 60                         |  |  |

| GAMMA<br>Adjustment              | The MCU can program the gamma RAMs to implement 10-bit accurate color transformations.                                                                                                                                                                                                                                                                                                   | GAMMA                              | 70                         |  |  |

| sRGB Control                     | The SRGB block allows simple, intuitive color control with just a few registers.                                                                                                                                                                                                                                                                                                         | SRGB                               | 60                         |  |  |

| Pattern<br>Generation            | For production testing, the ADE3700 can be programmed by the MCU to output a wide set of test patterns.                                                                                                                                                                                                                                                                                  | PGEN                               | 54                         |  |  |

| Flicker Reduction                | For Smart Panel applications, the MCU can set up the flicker detection block to report any correlation with the polarity inversion signal. The MCU can then change the polarity inversion to a non-correlating pattern to eliminate flicker.                                                                                                                                             | FLICKER<br>TCON                    | 68<br>48                   |  |  |

| Backlight Control                | Backlight Control  The ADE3700 provides two PWM outputs for direct control of the power components in a typical backlight. The MCU sets up the registers and enables the function.                                                                                                                                                                                                       |                                    |                            |  |  |

| Low Power State                  | To enter a low power state, the MCU can gate of most of the clocks and put the analog blocks into a low power standby state.                                                                                                                                                                                                                                                             | GLBL                               | 11                         |  |  |

ADE3700 Pin Descriptions

# 1.1 Pin Descriptions

Table 2: Pinout (Sheet 1 of 4)

| LQFP128 | Name      | Туре           | Description                            |  |

|---------|-----------|----------------|----------------------------------------|--|

| 32      | XVDD18    | Power          | Crystal Oscillator 1.8V VDD            |  |

| 31      | XTAL_OUT  | Output         | Crystal Oscillator output              |  |

| 30      | XTAL_IN   | Input          | Crystal Oscillator input               |  |

| 29      | XGND      | Power          | Crystal Oscillator Ground              |  |

| 19      | XCLK_EN   | Input          | Crystal clock output enable            |  |

| 18      | XCLK      | Output         | Crystal clock buffered output          |  |

| 34      | VSYNC     | Input          | Vertical Sync Input                    |  |

| 21      | TSTCLK    | Input          | Connect to Digital Ground              |  |

| 65      | TST_SCAN  | Input          | Connect to Digital Ground              |  |

| 8       | TCON7     | Output         | TCON Output 7                          |  |

| 9       | TCON6/OVS | Output         | TCON Output 6/Output Vertical Sync     |  |

| 10      | TCON5/OHS | Output         | TCON Output 5/Output Horizontal Sync   |  |

| 11      | TCON4/ODE | Output         | TCON Output 4/Output Data Enable       |  |

| 12      | TCON3     | Input/Output   | TCON Output 3                          |  |

| 13      | TCON2     | Input/Output   | TCON Output 2                          |  |

| 14      | TCON1     | Input/Output   | TCON Output 1                          |  |

| 15      | TCON0     | Input/Output   | TCON Output 0                          |  |

| 17      | SDA       | Open Drain I/O | I2C Data                               |  |

| 16      | SCL       | Input          | I2C Clock                              |  |

| 20      | RESETN    | Input          | Reset input, Active Low                |  |

| 54      | REFR      | Passive        | 1% 15.0 kOhm resistor to Analog Ground |  |

| 55      | REFMR     | Passive        | Connect to Analog Ground               |  |

| 48      | REFMG     | Passive        | Connect to Analog Ground               |  |

| 41      | REFMB     | Passive        | Connect to Analog Ground               |  |

| 47      | REFG      | Passive        | 1% 15.0 kOhm resistor to Analog Ground |  |

| 58      | REFCR     | Passive        | 100nF capacitor to Analog Ground       |  |

| 51      | REFCG     | Passive        | 100nF capacitor to Analog Ground       |  |

| 44      | REFCB     | Passive        | 100nF capacitor to Analog Ground       |  |

| 40      | REFB      | Passive        | 1% 15.0 kOhm resistor to Analog Ground |  |

| 26      | PVDD18    | Power          | PLL 1.8V VDD                           |  |

| 28      | PVDD18    | Power          | PLL 1.8V VDD                           |  |

| 25      | PGND      | Power          | PLL Ground                             |  |

| 27      | PGND      | Power          | PLL Ground                             |  |

| 105     | AVS       | Output         | Alternate Vertical Sync                |  |

| 126     | ORB7      | Input/Output   | Output Port B: Red Data 7              |  |

| 127     | ORB6      | Input/Output   | Output Port B: Red Data 6              |  |

Pin Descriptions ADE3700

Table 2: Pinout (Sheet 2 of 4)

| LQFP128 | Name | Туре         | Description                 |  |

|---------|------|--------------|-----------------------------|--|

| 128     | ORB5 | Input/Output | Output Port B: Red Data 5   |  |

| 1       | ORB4 | Input/Output | Output Port B: Red Data 4   |  |

| 2       | ORB3 | Input/Output | Output Port B: Red Data 3   |  |

| 3       | ORB2 | Input/Output | Output Port B: Red Data 2   |  |

| 4       | ORB1 | Input/Output | Output Port B: Red Data 1   |  |

| 5       | ORB0 | Input/Output | Output Port B: Red Data 0   |  |

| 86      | ORA7 | Output       | Output Port A: Red Data 7   |  |

| 87      | ORA6 | Output       | Output Port A: Red Data 6   |  |

| 88      | ORA5 | Output       | Output Port A: Red Data 5   |  |

| 89      | ORA4 | Output       | Output Port A: Red Data 4   |  |

| 90      | ORA3 | Output       | Output Port A: Red Data 3   |  |

| 95      | ORA2 | Output       | Output Port A: Red Data 2   |  |

| 96      | ORA1 | Output       | Output Port A: Red Data 1   |  |

| 97      | ORA0 | Output       | Output Port A: Red Data 0   |  |

| 103     | AHS  | Output       | Alternate Horizontal Sync   |  |

| 112     | OGB7 | Input/Output | Output Port B: Green Data 7 |  |

| 113     | OGB6 | Input/Output | Output Port B: Green Data 6 |  |

| 114     | OGB5 | Input/Output | Output Port B: Green Data 5 |  |

| 115     | OGB4 | Input/Output | Output Port B: Green Data 4 |  |

| 120     | OGB3 | Input/Output | Output Port B: Green Data 3 |  |

| 121     | OGB2 | Input/Output | Output Port B: Green Data 2 |  |

| 122     | OGB1 | Input/Output | Output Port B: Green Data 1 |  |

| 123     | OGB0 | Input/Output | Output Port B: Green Data 0 |  |

| 74      | OGA7 | Output       | Output Port A: Green Data 7 |  |

| 75      | OGA6 | Output       | Output Port A: Green Data 6 |  |

| 76      | OGA5 | Output       | Output Port A: Green Data 5 |  |

| 77      | OGA4 | Output       | Output Port A: Green Data 4 |  |

| 78      | OGA3 | Output       | Output Port A: Green Data 3 |  |

| 79      | OGA2 | Output       | Output Port A: Green Data 2 |  |

| 82      | OGA1 | Output       | Output Port A: Green Data 1 |  |

| 83      | OGA0 | Output       | Output Port A: Green Data 0 |  |

| 102     | ADE  | Output       | Alternate Data Enable       |  |

| 104     | OCLK | Output       | Output Clock                |  |

| 98      | OBB7 | Input/Output | Output Port B: Blue Data 7  |  |

| 99      | OBB6 | Input/Output | Output Port B: Blue Data 6  |  |

| 100     | OBB5 | Input/Output | Output Port B: Blue Data 5  |  |

| 101     | OBB4 | Input/Output | Output Port B: Blue Data 4  |  |

ADE3700 Pin Descriptions

Table 2: Pinout (Sheet 3 of 4)

| LQFP128 | Name   | Туре         | Description                            |

|---------|--------|--------------|----------------------------------------|

| 108     | OBB3   | Input/Output | Output Port B: Blue Data 3             |

| 109     | OBB2   | Input/Output | Output Port B: Blue Data 2             |

| 110     | OBB1   | Input/Output | Output Port B: Blue Data 1             |

| 111     | OBB0   | Input/Output | Output Port B: Blue Data 0             |

| 66      | OBA7   | Output       | Output Port A: Blue Data 7             |

| 67      | OBA6   | Output       | Output Port A: Blue Data 6             |

| 68      | OBA5   | Output       | Output Port A: Blue Data 5             |

| 69      | OBA4   | Output       | Output Port A: Blue Data 4             |

| 70      | OBA3   | Output       | Output Port A: Blue Data 3             |

| 71      | OBA2   | Output       | Output Port A: Blue Data 2             |

| 72      | OBA1   | Output       | Output Port A: Blue Data 1             |

| 73      | OBA0   | Output       | Output Port A: Blue Data 0             |

| 56      | INR    | Input        | Analog Video Port: Red Channel input   |

| 49      | ING    | Input        | Analog Video Port: Green Channel input |

| 42      | INB    | Input        | Analog Video Port: Blue Channel input  |

| 35      | HSYNC  | Input        | Horizontal (or Composite) Sync Input   |

| 7       | DVDD33 | Power        | Digital 3.3V VDD                       |

| 64      | DVDD33 | Power        | Digital 3.3V VDD                       |

| 80      | DVDD33 | Power        | Digital 3.3V VDD                       |

| 91      | DVDD33 | Power        | Digital 3.3V VDD                       |

| 106     | DVDD33 | Power        | Digital 3.3V VDD                       |

| 119     | DVDD33 | Power        | Digital 3.3V VDD                       |

| 23      | DVDD18 | Power        | Digital 1.8V VDD                       |

| 62      | DVDD18 | Power        | Digital 1.8V VDD                       |

| 84      | DVDD18 | Power        | Digital 1.8V VDD                       |

| 93      | DVDD18 | Power        | Digital 1.8V VDD                       |

| 117     | DVDD18 | Power        | Digital 1.8V VDD                       |

| 124     | DVDD18 | Power        | Digital 1.8V VDD                       |

| 6       | DGND   | Power        | Digital Ground                         |

| 22      | DGND   | Power        | Digital Ground                         |

| 24      | DGND   | Power        | Digital Ground                         |

| 63      | DGND   | Power        | Digital Ground                         |

| 81      | DGND   | Power        | Digital Ground                         |

| 85      | DGND   | Power        | Digital Ground                         |

| 92      | DGND   | Power        | Digital Ground                         |

| 94      | DGND   | Power        | Digital Ground                         |

| 107     | DGND   | Power        | Digital Ground                         |

Pin Descriptions ADE3700

Table 2: Pinout (Sheet 4 of 4)

| LQFP128 | Name    | Туре  | Description                              |

|---------|---------|-------|------------------------------------------|

| 116     | DGND    | Power | Digital Ground                           |

| 118     | DGND    | Power | Digital Ground                           |

| 125     | DGND    | Power | Digital Ground                           |

| 33      | CSYNC   | Input | Composite Sync Input - for Sync On Green |

| 36      | AVDD33  | Power | Analog 3.3V VDD                          |

| 43      | AVDD33  | Power | Analog 3.3V VDD                          |

| 50      | AVDD33  | Power | Analog 3.3V VDD                          |

| 57      | AVDD33  | Power | Analog 3.3V VDD                          |

| 46      | AVDD18  | Power | Analog 1.8V VDD                          |

| 53      | AVDD18  | Power | Analog 1.8V VDD                          |

| 60      | AVDD18  | Power | Analog 1.8V VDD                          |

| 37      | AGND    | Power | Analog Ground                            |

| 39      | AGND    | Power | Analog Ground                            |

| 45      | AGND    | Power | Analog Ground                            |

| 52      | AGND    | Power | Analog Ground                            |

| 59      | AGND    | Power | Analog Ground                            |

| 61      | AGND    | Power | Analog Ground                            |

| 38      | ADVDD18 | Power | 1.8V VDD                                 |

ADE3700 Global Control

# **2 Functional Description**

### 2.1 Global Control

The global control block is responsible for:

- selecting clock sources

- power control

- I<sup>2</sup>C control

- SCLK frequency synthesizer control

- block by block synchronous reset generation

The global control block runs on the XCLK clock domain which is required to be active for programming. The clock domains of all other blocks are set in the Global Control Block. For I<sup>2</sup>C access, the requested block must be driven with a valid clock frequency greater than 10 MHz. Clock domains are shown in Figure 2.

Figure 2: Global Control Block Diagram

To program the SCLK frequency synthesizer to a desired frequency (f<sub>OUT</sub>, in MHz), the following equations apply.

Table 3: SCLK Frequency Synthesizer Programmable Values (Sheet 1 of 2)

| Frequency Range                                                          | SDIV |

|--------------------------------------------------------------------------|------|

| $f_{OUT}$ < 8 x $f_{XCLK}$ AND $f_{OUT} \ge 4$ x $f_{XCLK}$              | 0    |

| $f_{OUT} < 4 \times f_{XCLK} \text{ AND } f_{OUT} \ge 2 \times f_{XCLK}$ | 1    |

Global Control ADE3700

Table 3: SCLK Frequency Synthesizer Programmable Values (Sheet 2 of 2)

| Frequency Range                                                                       | SDIV |

|---------------------------------------------------------------------------------------|------|

| f <sub>OUT</sub> < 2 x f <sub>XCLK</sub> AND f <sub>OUT</sub> ≥ f <sub>XCLK</sub>     | 2    |

| $f_{OUT} < f_{XCLK} \text{ AND } f_{OUT} \ge f_{XCLK} / 2$                            | 3    |

| $f_{OUT} < f_{XCLK}/2 \text{ AND } f_{OUT} \ge f_{XCLK} / 4$                          | 4    |

| $f_{OUT} < f_{XCLK}/4 \text{ AND } f_{OUT} \ge f_{XCLK} / 8$                          | 5    |

| f <sub>OUT</sub> < f <sub>XCLK</sub> /8 AND f <sub>OUT</sub> ≥ f <sub>XCLK</sub> / 16 | 6    |

| $f_{OUT} < f_{XCLK}/16 \text{ AND } f_{OUT} \ge f_{XCLK} / 32$                        | 7    |

$$\begin{split} & \text{MD} = \text{INT}(f_{\text{XCLK}} \text{ x } (2^{(6 + \text{NDIV} - \text{SDIV})}) \, / \, f_{\text{OUT}}) \\ & \text{PE} = \text{INT}((2^{15}) \text{ x } (\text{MD} + 1 - f_{\text{XCLK}} \text{ x } (2^{(6 + \text{NDIV} - \text{SDIV})}) \, / \, f_{\text{OUT}})) \end{split}$$

where  $f_{XCLK}$  is the external crystal frequency in MHz (typically 27). The maximum SCLK frequency generated by this block is  $f_{XTAL} \times 2^{(2+NDIV)}$ .

For the lowest power operation, all clock sources should be set to the "zero" setting and the analog power disables should be set. In this condition, only the crystal clock domain (XCLK) is running and blocks in INCLK or DOTCLK domains may not be accessible through the I<sup>2</sup>C interface.

The following modules can have their clocks disabled to reduce power consumption when the chip is in steady-state mode: FLK, OSD, PGEN, DFT, and DMEAS. Also, the clock to the TCON can be disabled for non-Smart Panel applications. Note that the OSD module has a special power bypass bit that must be enabled when the OSD clock is disabled.

Also, the clock to all I<sup>2</sup>C registers associated with modules in the INCLK and DOTCLK domains can be disabled after the chip is configured to reduce power in steady-state mode. Note that during chip configuration, all I<sup>2</sup>C clocks must be enabled.

An asynchronous clock enable override signal must be disabled to allow control of individual module clock signals.

ADE3700 Global Control

Table 4: Global Registers (Sheet 1 of 4)

| Register Name      | Addr.  | mode | Bits  | Default | Description                                                                                                                                                                                                                              |

|--------------------|--------|------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GLBL_NULL_ADDR     | 0x0000 | Read | [7:0] |         | Chip Revision ID                                                                                                                                                                                                                         |

| GLBL_CLK_SRC_SEL_0 | 0x0001 |      | [7]   | 0x0     | Reserved                                                                                                                                                                                                                                 |

|                    |        | R/W  | [6:4] | 0x5     | DOTCLK source  0x0: TESTCLK pin 0x1: SCLK freq synth 0x2: FM freq synth (normal) 0x3: INCLK source 0x4: CLKIN pin 0x5: crystal clock 0x6: 0 0x7: Reserved                                                                                |

|                    |        | R/W  | [3:0] | OxA     | INCLK source  0x0: TESTCLK pin 0x1: nc 0x2: ADC clock red 0x3: ADC clock green 0x4: ADC clock blue 0x5: SCLK freq synth 0x6: nc 0x7: LLK PLL (ADC Input) 0x8: CLKIN pin 0x9: FM freq synth 0xA: crystal clock 0xB: 0 0xC - 0xF: Reserved |

| GLBL_CLK_SRC_SEL_2 | 0x0002 |      | [7]   | 0x0     | Reserved                                                                                                                                                                                                                                 |

|                    |        | R/W  | [6:4] | 0x4     | LLK CTRL CLK source  0x0: TESTCLK pin 0x1: SCLK freq synth 0x2: LLKPLL control clock (normal) 0x3: CLKIN pin 0x4: crystal clock 0x5: 0 0x6 - 0x7: Reserved                                                                               |

|                    |        |      | [3]   |         | Reserved                                                                                                                                                                                                                                 |

|                    |        | R/W  | [2:0] | 0x4     | LLK ZERO CLK source  0x0: TESTCLK pin 0x1: SCLK freq synth 0x2: LLKPLL zero clock (normal) 0x3: CLKIN pin 0x4: crystal clock 0x5: 0 0x6 - 0x7: Reserved                                                                                  |

Global Control ADE3700

Table 4: Global Registers (Sheet 2 of 4)

| Register Name        | Addr.  | mode | Bits  | Default | Description                                                                                                                                              |

|----------------------|--------|------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| GLBL_CLK_INV         | 0x0003 |      | [7:5] | 0x0     | Reserved                                                                                                                                                 |

|                      |        | R/W  | [4]   | 0x0     | Invert LLPLL control clock                                                                                                                               |

|                      |        | R/W  | [3]   | 0x0     | Invert LLPLL zero clock                                                                                                                                  |

|                      |        | R/W  | [2]   | 0x0     | Invert ADC sample clock                                                                                                                                  |

|                      |        | R/W  | [1]   | 0x0     | Invert DOT clock                                                                                                                                         |

|                      |        | R/W  | [0]   | 0x0     | Invert input clock                                                                                                                                       |

| GLBL_CLK_ENABLE_0    | 0x0004 |      | [7:1] | 0x0     | Reserved                                                                                                                                                 |

|                      |        | R/W  | [0]   | 0x1     | Clock enable async override                                                                                                                              |

| GLBL_ANA_PWR         | 0x0005 |      | [7:5] | 0x0     | Reserved                                                                                                                                                 |

|                      |        | R/W  | [4]   | 0x1     | Blue ADC power down                                                                                                                                      |

|                      |        | R/W  | [3]   | 0x1     | Green ADC power down                                                                                                                                     |

|                      |        | R/W  | [2]   | 0x1     | Red ADC power down                                                                                                                                       |

|                      |        |      | [1:0] | 0x0     | Reserved                                                                                                                                                 |

| GLBL_XK_SRST         | 0x0006 |      | [7:3] | 0x0     | Reserved                                                                                                                                                 |

|                      |        | R/W  | [2]   | 0x0     | SMEAS block reset, synchronous to XCLK                                                                                                                   |

|                      |        | R/W  | [1]   | 0x0     | SRT block reset, synchronous to XCLK                                                                                                                     |

|                      |        | R/W  | [0]   | 0x0     | Frame Sync block reset, synchronous to XCLK                                                                                                              |

| GLBL_I2C_CTRL        | 0x0007 |      | [7:3] | 0x0     | Reserved                                                                                                                                                 |

|                      |        | R/W  | [2]   | 0x0     | Disable I2C auto increment                                                                                                                               |

|                      |        | R/W  | [1]   | 0x0     | SDA PMOS enable                                                                                                                                          |

|                      |        | R/W  | [0]   | 0x0     | bypass I2C filter                                                                                                                                        |

| GLBL_XTAL_CTRL       | 0x0008 |      | [7:1] | 0x0     | Reserved                                                                                                                                                 |

|                      |        | R/W  | [0]   | 0x1     | crystal oscillator enable                                                                                                                                |

| GLBL_SCLK_SYNTH_CTRL | 0x0009 |      | [7:5] | 0x0     | Reserved                                                                                                                                                 |

|                      |        | R/W  | [4:3] | 0x0     | XTAL frequency multiplier NDIV  0x0: f <sub>XCLK</sub> = 54MHz  0x1: f <sub>XCLK</sub> = 27MHz (normal)  0x2: f <sub>XCLK</sub> = 13.5MHz  0x3: Reserved |

|                      |        | R/W  | [2]   | 0x0     | SCLK frequency synthesizer EXT_PLL (normal operation = 0)                                                                                                |

|                      |        | R/W  | [1]   | 0x0     | SCLK frequency synthesizer PLL_SEL (normal operation = 1)                                                                                                |

|                      |        | R/W  | [0]   | 0x1     | SCLK freq synth control disable (normal operation = 0)                                                                                                   |

ADE3700 Global Control

Table 4: Global Registers (Sheet 3 of 4)

| Register Name      | Addr.  | mode | Bits  | Default | Description                                                                                                                                                    |

|--------------------|--------|------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GLBL_SCLK_MD_SD    | 0x000A | R/W  | [7:3] | 0x0     | SCLK frequency synthesizer MD, range is [16,31]                                                                                                                |

|                    |        | R/W  | [2:0] | 0x0     | SCLK frequency synthesizer SDIV, range is [0,7]                                                                                                                |

| GLBL_SCLK_PE_L     | 0x000B | R/W  | [7:0] | 0x0     | SCLK frequency synthesizer PE, range is [0, 32767]                                                                                                             |

| GLBL_SCLK_PE_H     | 0x000C | R/W  | [7:0] |         |                                                                                                                                                                |

| GLBL_TST_CTRL      | 0x000D |      | [7:1] | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [0]   | 0x0     | functional test mode enable                                                                                                                                    |

| GLBL_COMP_PAD_CTRL | 0x000E |      | [7:2] | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [1]   | 0x0     | Compensation pad TQ (test mode)                                                                                                                                |

|                    |        | R/W  | [0]   | 0x1     | Compensation pad EN (enable)                                                                                                                                   |

| GLBL_SCLK_CTRL     | 0x0010 |      | [7:5] | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [4]   | 0x0     | invert SCLK                                                                                                                                                    |

|                    |        |      | [3]   | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [2:0] | 0x0     | SCLK source select  0x0: TESTCLK pin 0x1: SCLK freq synth 0x2: FM freq synth (normal) 0x3: INCLK source 0x4: CLKIN pin 0x5: crystal clock 0x6: 0 0x7: Reserved |

| GLBL_BPAD_EN       | 0x0011 | R/W  | [3:0] | 0x0     | For each bit n (0 to 3) in the LS nibble, 0: TCON[n] pin is TCON output 1: TCON[n] pin is input for testing                                                    |

|                    |        | R/W  | [4]   | 0x0     | Port B input mode enable (production test only)                                                                                                                |

| GLBL_IK_SRST       | 0x0020 | R/W  | [7]   | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [6]   | 0x0     | DFT block reset synchronous to INCLK                                                                                                                           |

|                    |        | R/W  | [5]   | 0x0     | ADC block reset synchronous to INCLK                                                                                                                           |

|                    |        | R/W  | [4]   | 0x0     | SCALER block reset synchronous to INCLK                                                                                                                        |

|                    |        | R/W  | [3]   | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [2]   | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [1]   | 0x0     | DMEAS block reset synchronous to INCLK                                                                                                                         |

|                    |        | R/W  | [0]   | 0x0     | SMUX block reset synchronous to INCLK                                                                                                                          |

| GLBL_SHADOW_EN     | 0x0021 |      | [7:1] | 0x0     | Reserved                                                                                                                                                       |

|                    |        | R/W  | [0]   | 0x0     | Shadow registers sync on frame boundary                                                                                                                        |

Table 4: Global Registers (Sheet 4 of 4)

| Register Name         | Addr.  | mode | Bits  | Default | Description                             |

|-----------------------|--------|------|-------|---------|-----------------------------------------|

| GLBL_INCLK_GATE_CTRL  | 0x0022 |      | [7:3] | 0x0     | Reserved                                |

|                       |        | R/W  | [2]   | 0x1     | Enable DFT clock                        |

|                       |        | R/W  | [1]   | 0x1     | Enable DMEAS clock                      |

|                       |        | R/W  | [0]   | 0x1     | Enable INCLK to I2C registers           |

| GLBL_DK_SRST          | 0x0040 |      | [7]   | 0x0     | Reserved                                |

|                       |        | R/W  | [6]   | 0x0     | PGEN block reset synchronous to DOTCLK  |

|                       |        | R/W  | [5]   | 0x0     | OMUX block reset synchronous to DOTCLK  |

|                       |        | R/W  | [4]   | 0x0     | APC block reset synchronous to DOTCLK   |

|                       |        | R/W  | [3]   | 0x0     | OSD block reset synchronous to DOTCLK   |

|                       |        | R/W  | [2]   | 0x0     | GAMMA block reset synchronous to DOTCLK |

|                       |        | R/W  | [1]   | 0x0     | OSQ block reset synchronous to DOTCLK   |

|                       |        | R/W  | [0]   | 0x0     | SCALE block reset synchronous to DOTCLK |

| GLBL_OSD_POWER_CTRL   | 0x0041 |      | [7:1] | 0x0     | Reserved                                |

|                       |        | R/W  | [0]   | 0x0     | OSD bypass (when clock disabled)        |

| GLBL_DOTCLK_GATE_CTRL | 0x0042 |      | [7:5] | 0x0     | Reserved                                |

|                       |        | R/W  | [4]   | 0x1     | Enable FLK clock                        |

|                       |        | R/W  | [3]   | 0x1     | Enable TCON clock                       |

|                       |        | R/W  | [2]   | 0x1     | Enable OSD clock                        |

|                       |        | R/W  | [1]   | 0x1     | Enable PGEN clock                       |

|                       |        | R/W  | [0]   | 0x1     | Enable DOTCLK to I2C registers          |

# 2.2 FM Frequency Synthesizer

The FM Frequency Synthesizer can create a clock up to eight times the crystal input clock using a digital frequency synthesizer. The modulation period and amplitude are directly controlled by I2C registers. The I2C interface runs in the LLK\_CTRL clock domain, which must be active for access.

The relationship of the output frequency ( $f_{OUT}$ ) to the 32-bit phase\_rate value and the crystal frequency ( $f_{XCLK}$ ) is:

$$f_{OUT} = f_{XCLK} * 2^{27+NDIV} / phase_rate$$

where f<sub>OUT</sub> and f<sub>XCLK</sub> are in MHz.

The maximum output frequency of the FM frequency synthesizer is  $f_{XTAL} \times 2^{(2+NDIV)}$ .

Note that native duty cycle of the FM frequency synthesizer is not 50/50, so it is recommended to either enable the divide-by-two in the fm synthesizer block for frequencies up to  $f_{XCLK}$  x  $2^{(1+NDIV)}$  (typically 108 MHz) or set the output mux to a double wide output mode for pixel clocks above  $f_{XCLK}$  x  $2^{(1+NDIV)}$ . This will ensure a 50% duty clock on the output.

| Register Name   | Addr   | Mode | Bits  | Default | Description                       |

|-----------------|--------|------|-------|---------|-----------------------------------|

| FM_FS_CTRL      | 0x0830 |      | [7:4] |         | Reserved                          |

|                 |        | R/W  | [3]   | 0x0     | Clear the FM synthesizer          |

|                 |        | R/W  | [2]   | 0x0     | Clear the fs accumulator          |

|                 |        | R/W  | [1]   | 0x0     | Activate the frequency modulation |

|                 |        | R/W  | [0]   | 0x0     | Divide the output by 2            |

| FM_FS_PR_0      | 0x0831 | R/W  | [7:0] | 8000000 | Phase Rate                        |

| FM_FS_PR_1      | 0x0832 | R/W  | [7:0] |         |                                   |

| FM_FS_PR_2      | 0x0833 | R/W  | [7:0] |         |                                   |

| FM_FS_PR_3      | 0x0834 | R/W  | [7:0] |         |                                   |

| FM_FS_AMPLITUDE | 0x0835 | R/W  | [7:0] | 0x0     | LSB = 72 ps                       |

| FM_FS_PERIODX64 | 0x0836 | R/W  | [7:0] | 0x80    | LSB = 1.185 us                    |

| FM_FS_PULSE_EXT | 0x0837 | R/W  | [7]   | 0x0     | Enable                            |

|                 |        |      | [6:3] |         | Reserved                          |

|                 |        | R/W  | [2:0] | 0x0     | Value                             |

**Table 5: FM Frequency Synthesizer Registers**

# 2.3 Analog-to-Digital Converter (ADC)

The analog port consists of three 9-bit RGB ADCs with preamp, gain/offset adjustment and digital filtering. The I2C interface for the ADC block is in the INCLK clock domain which must be active for programming.

The relationship of input voltage, gain and offset register settings to output code is approximately as follows:

output\_code\_8b =  $457 \times 0$ ffset  $/ 2^8 + 181 \times 0$ gain x input\_mV  $/ 2^{16} - 125 \times 0$ gain x offset  $/ 2^{16} - 219$

Addr. Mode **Bits** Default **Description** Register ADC\_DITHER 0x0324 [7] Reserved R/W [6] 0x0 Dither horizontally R/W 0x0 [5] Dither vertically R/W [4] 0x0 Dither temporally R/W [3] 0x0 Force dither high R/W [2] 0x0 Enable dither 0x0 [1:0] Reserved ADC\_OFFSET\_R 0x0326 R/W 0x0 Offset Control, Red Channel [7:0] ADC\_OFFSET\_G 0x0328 R/W [7:0] 0x0 Offset Control, Green Channel

Table 6: ADC Registers (Sheet 1 of 2)

Line Lock PLL ADE3700

| Register     | Addr.  | Mode | Bits  | Default | Description                  |

|--------------|--------|------|-------|---------|------------------------------|

| ADC_OFFSET_B | 0x0329 | R/W  | [7:0] | 0x0     | Offset Control, Blue Channel |

| ADC_GAIN_R   | 0x032A | R/W  | [7:0] | 0x0     | Gain Control, Red Channel    |

| ADC_GAIN_G   | 0x032B | R/W  | [7:0] | 0x0     | Gain Control, Green Channel  |

| ADC_GAIN_B   | 0x032C | R/W  | [7:0] | 0x0     | Gain Control, Blue Channel   |

Table 6: ADC Registers (Sheet 2 of 2)

### 2.4 Line Lock PLL

The Line Lock PLL recovers a sample clock from an incoming has source. The response characteristics of the line lock PLL can be adjusted for optimum response time and jitter filtering. The phase of the sample clock can be digitally adjusted in steps of 289 ps (with a 27-MHz crystal). The I2C interface of the line lock PLL is in the LLK\_CTRL clock domain which must be active for programming.

The PLL filter has three ranges with independent filter parameters. When the phase detector error stays below a programmable threshold for a programmable number of input lines, the PLL filter coefficients are changed. Any phase detector error above the programmed threshold will return the filter to the appropriate level in one line. The operation is shown in Figure 3.

Error <= SLOW\_TOL for more than SLOW\_LINE\_NB of lines

Fast

Slow

Error <= LOCK\_TOL for more than LOCK\_LINE\_NB

of lines

Fast

Error > SLOW\_TOL

Error > LOCK\_TOL

Error > LOCK\_TOL

Figure 3: Line Lock PLL

The digital loop filter is controlled by three parameters: MFACTOR, A and B. M\_FACTOR is the desired number of clocks per input line. The A and B parameters control the response of the 2nd order digital filter. A and B are composed of a linear and exponential component designated by the L and E suffix, respectively. The relationship of these numbers to the classic 2nd order damping and natural frequency are as follows:

Damping = AL x  $2^{(AE-12)}$  x SQRT(5 x M\_FACTOR / (BL x  $2^{BE}$ )) Natural Frequency = SQRT(M\_FACTOR x 5 x BL x  $2^{(BE-34)}$ ) ADE3700 Line Lock PLL

Table 7: Line Lock PLL Registers (Sheet 1 of 4)

| Register Name              | Addr   | Mode | Bits  | Default | Description                                                                                               |

|----------------------------|--------|------|-------|---------|-----------------------------------------------------------------------------------------------------------|

| LLK_PLL_CLEAR              | 0x0800 |      | [7:6] |         | Reserved                                                                                                  |

|                            |        | R/W  | [5]   | 0x0     | master reset                                                                                              |

|                            |        | R/W  | [4]   | 0x0     | reset the PLL synthetic sync                                                                              |

|                            |        | R/W  | [3]   | 0x0     | reset PLL offset                                                                                          |

|                            |        | R/W  | [2]   | 0x0     | reset PLL accumulator                                                                                     |

|                            |        | R/W  | [1]   | 0x0     | reset the low pass filter                                                                                 |

|                            |        | R/W  | [0]   | 0x0     | reset the PLL phase error                                                                                 |

| LLK_PLL_CTRL               | 0x0801 | R/W  | [7]   |         | Reserved                                                                                                  |

|                            |        | R/W  | [6]   | 0x0     | zero clock delay enable                                                                                   |

|                            |        | R/W  | [5]   | 0x0     | 0: normal 1: diagnostic mode PLL uses only fine error                                                     |

|                            |        | R/W  | [4]   | 0x0     | 0: normal 1: diagnostic coarse error is multiplied by 2                                                   |

|                            |        | R/W  | [3]   | 0x0     | input hsync edge selection 0: rising edge 1: falling edge                                                 |

|                            |        | R/W  | [2]   | 0x0     | sync on green input selection 0: composite sync (HSYNC pin) 1: sync on green (CSYNC pin)                  |

|                            |        | R/W  | [1]   | 0x0     | 0: normal<br>1: divide PLL clock by 2                                                                     |

|                            |        | R/W  | [0]   | 0x0     | 0: normal<br>1: free-running mode                                                                         |

| LLK_PLL_MFACTOR_L          | 0x0802 | R/W  | [7:0] | 0x0280  | number of clocks in a line                                                                                |

| LLK_PLL_MFACTOR_H          | 0x0803 | R/W  | [7:0] |         |                                                                                                           |

| LLK_PLL_HPERIOD_L          | 0x0804 | R/W  | [7:0] | 0x0040  | pulse width of synthetic hsync                                                                            |

| LLK_PLL_HPERIOD_H          | 0x0805 | R/W  | [7:0] |         |                                                                                                           |

| LLK_PLL_PHASE_RATE_INIT_0  | 0x0806 | R/W  | [7:0] | 0x0     | initial phase rate                                                                                        |

| LLK_PLL_PHASE_RATE_INIT_1  | 0x0807 | R/W  | [7:0] |         | fout = fxtal * 2 <sup>27+NDIV</sup> / phase_rate                                                          |

| LLK_PLL_PHASE_RATE_INIT_2  | 0x0808 | R/W  | [7:0] |         |                                                                                                           |

| LLK_PLL_PHASE_RATE_INIT_3  | 0x0809 | R/W  | [7:0] |         |                                                                                                           |

| LLK_PLL_PHASE_RATE_INIT_WR | 0x080A | R/W  | [7:1] |         | Reserved                                                                                                  |

|                            |        |      | [0]   |         | When written to 1, the pll phase rate is initialized with the initial phase rate register. Self clearing. |

Line Lock PLL ADE3700

Table 7: Line Lock PLL Registers (Sheet 2 of 4)

| Register Name           | Addr   | Mode | Bits  | Default | Description                                                                                                                                             |

|-------------------------|--------|------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| LLK_PLL_TC_AEF          | 0x080B |      | [7:4] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [3:0] | 0xA     | Fast Time Constant A Exponent                                                                                                                           |

| LLK_PLL_TC_BEF          | 0x080C |      | [7:4] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [3:0] | 0xA     | Fast Time Constant B Exponent                                                                                                                           |

| LLK_PLL_TC_ALF          | 0x080D |      | [7:6] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [5:0] | 0x20    | Fast Time Constant A Linear                                                                                                                             |

| LLK_PLL_TC_BLF          | 0x080E |      | [7:6] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [5:0] | 0x20    | Fast Time Constant B Linear                                                                                                                             |

| LLK_PLL_TC_AES          | 0x080F |      | [7:4] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [3:0] | 0x6     | Slow Time Constant A Exponent                                                                                                                           |

| LLK_PLL_TC_BES          | 0x0810 |      | [7:4] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [3:0] | 0x6     | Slow Time Constant B Exponent                                                                                                                           |

| LLK_PLL_TC_ALS          | 0x0811 |      | [7:6] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [5:0] | 0x20    | Slow Time Constant A Linear                                                                                                                             |

| LLK_PLL_TC_BLS          | 0x0812 |      | [7:6] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [5:0] | 0x20    | Slow Time Constant B Linear                                                                                                                             |

| LLK_PLL_TC_AEK          | 0x0813 |      | [7:4] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [3:0] | 0x6     | Lock Time Constant A Exponent                                                                                                                           |

| LLK_PLL_TC_BEK          | 0x0814 |      | [7:4] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [3:0] | 0x6     | Lock Time Constant B Exponent                                                                                                                           |

| LLK_PLL_TC_ALK          | 0x0815 |      | [7:6] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [5:0] | 0x20    | Lock Time Constant A Linear                                                                                                                             |

| LLK_PLL_TC_BLK          | 0x0816 |      | [7:6] |         | Reserved                                                                                                                                                |

|                         |        | R/W  | [5:0] | 0x20    | Lock Time Constant B Linear                                                                                                                             |

| LLK_PLL_TC_SLOW_TOL     | 0x0817 | R/W  | [7:0] | 0x80    | More than slow_line_nb lines with a phase error less than the slow_tol will set the slow status bit, and the pll will work with the slow time constant. |

|                         |        |      |       |         | One or more lines with a phase error more than slow_tol will reset the slow status bit, and the pll will work with the fast time constant.              |

|                         |        |      |       |         | LSB of slow tol is approx. 200ps.                                                                                                                       |

| LLK_PLL_TC_SLOW_LINE_NB | 0x0818 | R/W  | [7:0] | 0x10    |                                                                                                                                                         |

ADE3700 Line Lock PLL

Table 7: Line Lock PLL Registers (Sheet 3 of 4)

| Register Name                  | Addr   | Mode | Bits  | Default | Description                                                                                                                                             |

|--------------------------------|--------|------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| LLK_PLL_LOCK_TOL               | 0x0819 | R/W  | [7:0] | 0x20    | More than lock_line_nb lines with a phase error less than the lock_tol will set the lock status bit, and the pll will work with the lock time constant. |

|                                |        |      |       |         | One or more lines with a phase error more than lock_tol will reset the lock status bit, and the pll will work with the slow time constant.              |

|                                |        |      |       |         | LSB of lock tol is approx. 200ps.                                                                                                                       |

| LLK_PLL_LOCK_LINE_NB           | 0x081A | R/W  | [7:0] | 0x30    |                                                                                                                                                         |

| LLK_PLL_PH_OFFSET              | 0x081B | R/W  | [7:0] | 0x0     | Phase adjustment.                                                                                                                                       |

|                                |        |      |       |         | The maximum phase offset value is equal to phase_rate[31:21] or 0x40, whichever is higher.                                                              |

| LLK_PLL_PH_OFFSET_EN           | 0x081C | R/W  | [7]   | 0x0     | phase enable                                                                                                                                            |

|                                |        |      | [6]   |         | skip pulse                                                                                                                                              |

|                                |        |      | [5]   |         | skip pulse at every rising edge of hsync                                                                                                                |

|                                |        |      | [4:0] |         | Reserved                                                                                                                                                |

| LLK_PLL_PULSE_HIGH_EXT         | 0x081D | R/W  | [7]   | 0x0     | 0: no pulse extend<br>1: extend pulse (normal)                                                                                                          |

|                                |        |      | [6:3] |         | Reserved                                                                                                                                                |

|                                |        | R/W  | [2:0] | 0x0     | pulse extend amount                                                                                                                                     |

|                                |        |      |       |         | 0x0: minimum<br>0x7: maximum (normal)                                                                                                                   |

| LLK_PLL_STAT_LINES_L           | 0x081E | R/W  | [7:0] | 0x10    | Number of lines to statistically analyze.                                                                                                               |

| LLK_PLL_STAT_LINES_H           | 0x081F | R/W  | [7:0] |         |                                                                                                                                                         |

| LLK_PLL_STAT_ERROR_INC_LO<br>W | 0x0820 |      | [7:0] |         | Reserved                                                                                                                                                |

| LLK_PLL_FINE_ERROR_WAIT        | 0x0821 |      | [7:4] |         | Reserved                                                                                                                                                |

|                                |        | R/W  | [3:0] | 0x0     | Wait this number of CTRL_CLK cycles before updating the PLL.                                                                                            |

| LLK_PLL_STAT_ON_VSYNC          | 0x0822 |      | [7:2] |         | Reserved                                                                                                                                                |

|                                |        | R/W  | [1]   | 0x0     | PLL statistic synchronize on falling edge of vsync                                                                                                      |

|                                |        | R/W  | [0]   | 0x0     | PLL statistic synchronize on rising edge of vsync                                                                                                       |

| LLK_PLL_MFACTOR_SHADOW_L       | 0x0823 | R/W  | [7:0] | 0x80    | Number of clocks in a line.                                                                                                                             |

| LLK_PLL_MFACTOR_SHADOW_U       | 0x0824 | R/W  | [7:0] | 0x02    | Registers 0x0803 and 0x0802 are transferred to those registers according to update_on_venab_fe.                                                         |

Line Lock PLL ADE3700

Table 7: Line Lock PLL Registers (Sheet 4 of 4)

| Register Name            | Addr   | Mode | Bits  | Default | Description                                                                   |

|--------------------------|--------|------|-------|---------|-------------------------------------------------------------------------------|

| LLK_PLL_UPDATE           | 0x0840 | R    | [7]   |         | In free-running mode, toggles when status is updated.                         |

|                          |        |      |       |         | In one-shot mode, this bit is set when status is ready.                       |

|                          |        |      | [6:2] |         | Reserved                                                                      |

|                          |        | R/W  | [1]   | 0x0     | 0: free-running mode<br>1: one-shot mode                                      |

|                          |        | R/W  | [0]   | 0x0     | update enable                                                                 |

| LLK_PLL_STATUS           | 0x0841 |      | [7:4] |         | Reserved                                                                      |

|                          |        | R    | [3]   |         | Ilk overflow                                                                  |

|                          |        | R    | [2]   |         | coarse error = 0                                                              |