# SiI100/SiI101 Datasheet

Silicon Image, Inc.

Version 1.1 June 1998

SiI/DS-0001-B

#### **Copyright Notice**

This manual is copyrighted by Silicon Image, Inc. Do not reproduce, transform to any other format, or send/transmit any part of this documentation without the express written permission of Silicon Image, Inc.

#### **Trademark Acknowledgment**

$\mathsf{PanelLink}^{\scriptscriptstyle\mathsf{TM}}$  and  $\mathsf{TMDS}^{\scriptscriptstyle\mathsf{TM}}$  are trademarks of Silicon Image, Inc.

VESA® a registered trademark of Video Electronics Standards Association.

All other trademarks are the property of their respective holders.

#### **Disclaimer**

This document is provided for technical information for the user. Silicon Image, Inc. reserves the right to modify the information in this document as necessary. The customer should make sure that it has the most recent data sheet version. Silicon Image, Inc. holds no responsibility for any errors that may appear in this document. Customers should take appropriate action to ensure their use of the products does not infringe upon any patents. Silicon Image, Inc. respects valid patent rights of third parties and does not infringe upon or assist others to infringe upon such rights.

# **Revision History**

| Revision | Date | Comment                             |

|----------|------|-------------------------------------|

| 1.0      | 8/97 | Version 1.0 of SiI100/101 Datasheet |

| 1.1      | 6/98 | Version 1.1 of SiI100/101 Datasheet |

(This page left intentionally blank)

# **Table of Contents**

| Revision History                               |    |

|------------------------------------------------|----|

| Table of Contents                              | 5  |

| List of Figures                                | 6  |

| List of Tables                                 | 7  |

| 1. Feature Review                              | 8  |

| 2. Product Summary                             | 9  |

| 3. Order Information                           | 10 |

| 4. PanelLinkTechnology Overview                | 11 |

| 5. SiI100 Overview                             | 12 |

| 5.1 Data Input                                 | 13 |

| 6. SiI101 Overview                             | 14 |

| 6.1 Output Modes                               | 16 |

| 6.1.1 One Pixel Per Clock Mode                 | 16 |

| 6.1.2 Two Pixels Per Clock Mode                | 16 |

| 6.2 Data Mapping (TFT) - VESA@ompatible        | 17 |

| 6.2.1 One Pixel Per Clock Data Mapping         |    |

| 6.2.2 Two Pixels Per Clock Data Mapping        |    |

| 6.3 Output Clock Modes for 24-bit DSTN         |    |

| 6.4 Data Mapping (DSTN) - VESA@ompatible       |    |

| 7. TMDS <sup>TM</sup> Interconnect Layer       | 22 |

| 7.1 Voltage Swing Control (EXT_SWING)          |    |

| 7.2 Termination Control (EXT_RES)              |    |

| 8. PLL Synchronization                         |    |

| 9. SiI100 Pin Description                      |    |

| 9.1 SiI100 Pin Diagram                         |    |

| 9.2 SiI100 Pins Grouped by Functionality       |    |

| 9.2.1 SiI100 Input Pin Description.            |    |

| 9.2.2 SiI100 Test Output Pin Description       |    |

| 9.2.3 SiI100 Synchronization Pin Description   |    |

| 9.2.4 SiI100 Configuration Pin Description     |    |

| 9.2.5 SiI100 Analog Data Pin Description       |    |

| 9.2.6 SiI100 Power and Ground Pin Description  |    |

| 9.3 SiI100 Pins Listed Numerically             |    |

| 10. SiI101 Pin Description                     |    |

| 10.1 SiI101 Pin Diagram.                       |    |

| 10.2 SiI101 Pins Grouped by Functionality      |    |

| 10.2.1 SiI101 Data Output Pin Description      |    |

| 10.2.2 SiI101 Test Output Pin Description      |    |

| 10.2.3 SiI101 Synchronization Pin Description  |    |

| 10.2.4 SiI101 Analog Data Pin Description      |    |

| 10.2.5 SiI101 Configuration Pin Description    |    |

| 10.2.6 SiI101 Power and Ground Pin Description |    |

| 10.3 SiI101 Pins Listed Numerically            |    |

| 11. Electrical Specifications                  |    |

| 11.1 Absolute Conditions.                      |    |

| 11.2 DC Specifications                         |    |

| 11.3 AC Specifications                         |    |

| 11.4 Timing Diagrams                           |    |

| 11.4.1 SiI100 Input Timing                     |    |

| 11.4.2 SiI100 Input Timing                     |    |

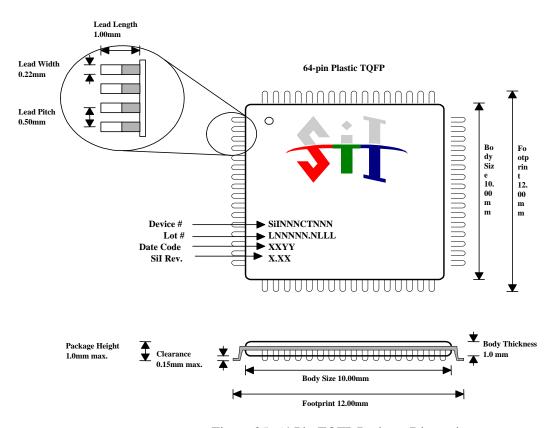

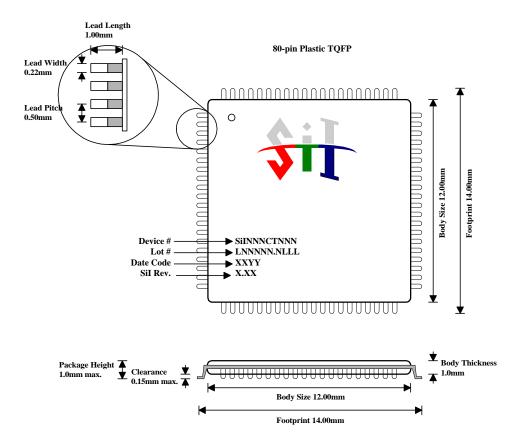

| 12. Package Dimensions                         |    |

| 12.1 SiI100 Package Dimensions.                |    |

| 12.2 SiI101 Package Dimensions.                |    |

| 12.2 DITIVI I acrage Dimensions                |    |

# **List of Figures**

| Figure 1. PanelLink®lock Diagram                                    | 11 |

|---------------------------------------------------------------------|----|

| Figure 2. SiI100 Functional Block Diagram                           |    |

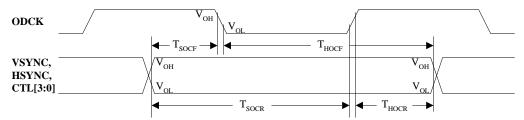

| Figure 3. Horizontal Input Timing                                   |    |

| Figure 4. Vertical Input Timing                                     |    |

| Figure 5. SiI101 Functional Block Diagram                           |    |

| Figure 6. One Pixel/Clock Timing with OCK_INV = Low                 | 16 |

| Figure 7. Two Pixels/Clock Timing with OCK_INV = Low                | 16 |

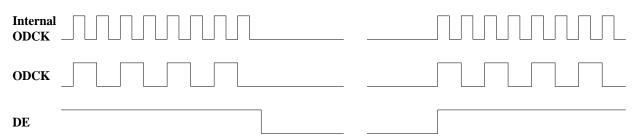

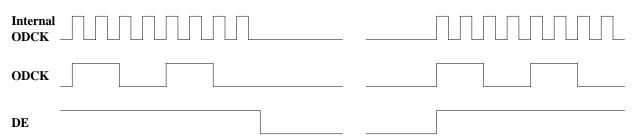

| Figure 8. ODCK Timing with DF0 High, PIXS Low, and OCK_INV Low      | 19 |

| Figure 9. ODCK Timing with DF0 High, PIXS High, and OCK_INV Low     | 19 |

| Figure 10. ODCK Timing with DF0 High, PIXS High, and OCK_INV High   |    |

| Figure 11. Differential Signaling Circuit                           | 22 |

| Figure 12. Single-Ended Low Voltage Differential Signal Adjustment  | 22 |

| Figure 13. How to send PLL_SYNC over CTL0                           | 24 |

| Figure 14. SiI100 Pin Diagram                                       | 25 |

| Figure 15. SiI101 Pin Diagram                                       | 31 |

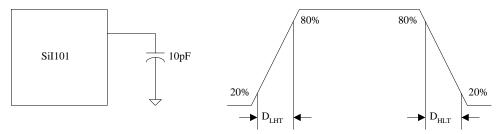

| Figure 16. Receiver Digital Output Transition Times                 | 41 |

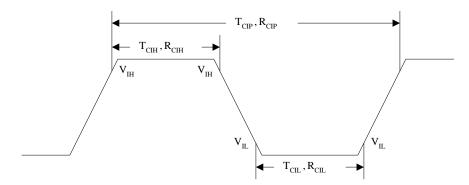

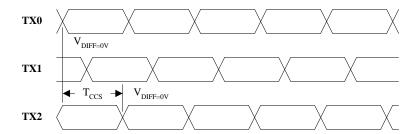

| Figure 17. Transmitter/Receiver Clock Cycle/High/Low Times          |    |

| Figure 18. Channel-to-Channel Skew Timing                           | 41 |

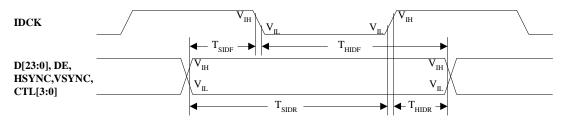

| Figure 19. Input Data Setup/Hold Times to IDCK of SiI100            |    |

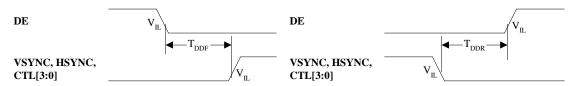

| Figure 20. VSYNC, HSYNC, and CTL[3:0] Delay Times from DE of SiI100 | 42 |

| Figure 21. DE High/Low Times of SiI100                              |    |

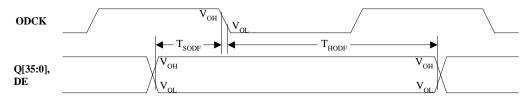

| Figure 22. Output Data Setup/Hold Times to ODCK of SiI101           | 43 |

| Figure 23. Output Control Setup/Hold Times to ODCK of SiI101        | 43 |

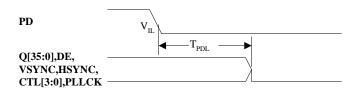

| Figure 24. Output Signals Disabled Timing from PD Active of SiI101  |    |

| Figure 25. 64 Pin TQFP Package Dimensions                           |    |

| Figure 26, 80 Pin TOFP Package Dimensions                           | 45 |

# **List of Tables**

| Table 1. Output Clock Configuration by Typical Application       | 15 |

|------------------------------------------------------------------|----|

| Table 2. One Pixel/Clock Mode Data Mapping from SiI100 to SiI101 |    |

| Table 3. Two Pixels/Clock Output Data Mapping                    | 18 |

| Table 4. DSTN Data Mapping                                       | 20 |

| Table 5. Absolute Conditions                                     | 38 |

| Table 6. Normal Operating Conditions                             | 38 |

| Table 7. DC Digital I/O Specifications (SiI100 and SiI101)       | 38 |

| Table 8. SiI100 Transmitter DC Specifications                    | 39 |

| Table 9. SiI101 Receiver DC Specifications                       | 39 |

| Table 10. SiI100 AC Specifications                               | 40 |

| Table 11. SiI101 AC Specifications                               | 40 |

#### 1. Feature Review

## • VESA Standards Compliant\*

- VESA®&D

- VESA®PDI-2

#### • Full-Color, High-Resolution Display Support

- Supports up to true color panels (24-bit/pixel, 16.7M color) in 1 pixel per clock mode.

- Supports up to 18-bit/pixel panels in 2 pixels per clock mode (36-bit interface).

- Supports VGA to XGA resolutions for TFT and VGA to SXGA resolutions for DSTN panels.

#### • High Integration, Simple Interface

- Only 3 data channels needed (Red, Green, Blue).

- One clock channel.

#### • Flexible Panel Interface

- Single or dual pixel out: supports up to 24-bit interface (one pixel per clock mode) or 36-bit interface (two 18-bit pixels per clock cycle).

- Up to 3 control signals (in addition to Horizontal Sync, Vertical Sync, and Display Enable signals) for supporting customized features.

- Parallel data can be latched on the positive or the negative edge.

- Variety of output clocking options for 24 bit DSTN support.

### Cable Distance Support and Fiber Optics Ready

- Adjustable TMDS<sup>TM</sup> low-voltage swing signaling for long distance support.

- DC-balanced signals for direct coupling to fiberoptics ready modules.

#### High Bandwidth and Reduced EMI

- Wide operating frequency range: 25MHz to 68MHz.

- Three TMDS<sup>TM</sup> data channels capable of transferring up to 680Mbps per channel.

- TMDS<sup>TM</sup> reduces high-speed data edges, lowering EMI across the cable.

- Adjustable internal termination impedance enables optimal impedance matching crucial for high-speed signaling.

#### Skew Tolerant for Reliable Transmission

- High-speed data oversampling to minimize effects of signal skew and jitter.

- Phase, byte, and multi-channel synchronization.

- Only the frequency information of received clock is used, eliminating effect of clock-to-data skew.

- Inter-pair skew tolerance up to 1 input clock cycle.

#### • High Jitter Tolerant

- Jitter tolerant PLL design

- PLL synchronization of both transmitter and receiver PLL clocks for improved jitter tolerance.

#### Low Power

- 3.3V core operation with 5V tolerant I/O.

- Low-power CMOS technology.

- Power-down mode.

#### Low Pin-Count Packages

- 64-pin TQFP SiI100.

- 80-pin TQFP SiI101.

<sup>\*</sup> As of August 1997, VESA®PDI-2 standard is in the process of completion. VESA®&D is a standard.

## 2. Product Summary

#### Introduction

The SiI100 and SiI101 are high-speed digital video/graphics interconnect devices capable of supporting VGA to XGA resolutions for TFT panels and VGA to SXGA resolutions for DSTN LCD panels. These devices are based on Silicon Image's PanelLink<sup>TM</sup>Technology that currently enables reliable, scaleable, high-speed data transmission over the same interface, from VGA to SXGA resolutions (and up to HDTV resolution in the future). The PanelLink<sup>TM</sup>transmitter incorporates an advanced coding scheme to enable TMDS<sup>TM</sup> signaling for reduced EMI across copper cables and DC-balancing for data transmission over fiber optics. In addition, the advanced coding scheme enables robust clock recovery at the receiver to achieve high-skew tolerance for driving longer cable lengths. maximize data recovery accuracy, the receiver triple oversamples and makes use of a data recovery algorithm to select the most reliable data sampling points.

#### **Skew Tolerant Reliable Transmission**

Valid data is sent over the three data channels during active display time, while synchronization data and embedded control signals are sent over the three data channels during blank time. After each line and frame are sent, the receiver will automatically force phase, byte, and inter-channel synchronization. Because the receiver PLL uses only the frequency information (and not the phase information) from the received clock signal, the receiver is immune to clock-to-data skew and extremely tolerant to data-to-data skew. This provides a robust transmission system for driving long cables.

### **Design Flexibility**

PanelLink<sup>™</sup> Technology enables notebook and FPD monitor designers to use one motherboard and one panel interface design to support resolutions from VGA (640x480) all the way up to XGA (1024x768) with true color support (16.7 million colors) for TFT panels, and up to SXGA (1280x1024) for DSTN panels. In addition, panel manufacturers will benefit from PanelLink<sup>™</sup>Pechnology by having the choice of one pixel per clock or two pixels per clock on the output data pins of the SiI101 receiver. Also, three control lines are available for supporting additional differentiating features that may exist on the panel side. (Future SiI products will maintain the same interface for forward compatibility).

#### Reduced EMI

PanelLink<sup>TM</sup> Technology helps manage EMI from both a *fundamental* and *advanced* perspective.

### Fundamental approach (common practice):

The *Fundamental* approach for lowering EMI is to send data using low voltage differential swing (LVDS) signaling.

#### **Advanced approach (unique to PanelLink**<sup>TM</sup>):

PanelLink<sup>TM</sup> Technology builds on LVDS and further codes the data to reduce the number of high frequency signal edges of each transmitted data byte by 22% on average, which is the basis of TMDS<sup>TM</sup>. And, PanelLink<sup>TM</sup> Technology provides on-chip termination resistors at the receiver to optimize the interconnect system impedance, helping reduce EMI signal reflection on the cable.

#### **Reduced Power**

PanelLink™ Technology reduces power consumption by using 3.3V low-power CMOS technology. Because the transmitter and receiver are designed in industry standard CMOS technology, they can be integrated into video/panel controllers, further reducing power and EMI.

### **Fiber Optics Support**

The coding scheme permits DC-balancing for AC coupling, enabling separate power supplies for the transmitter and receiver, with good isolation.

#### **High Jitter Tolerance**

PanelLink<sup>™</sup> Technology has a leading edge jitter tolerant PLL design. In addition, PanelLink<sup>™</sup> employs PLL synchronization, which forces both the transmitter and receiver PLL's to respond similarly to an input jitter, thus improving jitter tolerance.

# 3. Order Information

|   |                                       | Part Number | Order Information |

|---|---------------------------------------|-------------|-------------------|

| • | Production Version of the Transmitter | SiI100      | SiI100CT64V351    |

| • | Production Version of the Receiver    | SiI101      | SiI101CT80V360    |

For more information, please contact:

• Silicon Image web-site: www.siimage.com

Silicon Image main phone number: 888-PanelLink (within US and Canada)

+1-408-873-3111 (outside of US and Canada)

# 4. PanelLink<sup>TM</sup> Technology Overview

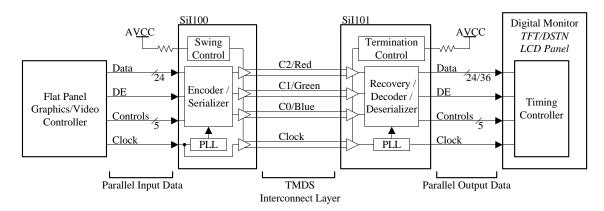

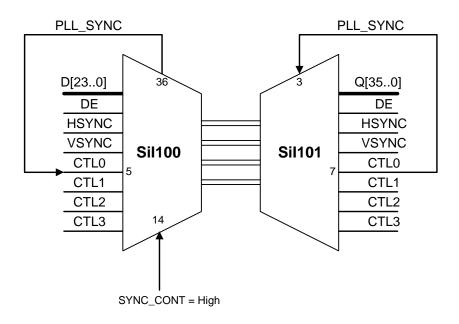

Figure 1. PanelLink<sup>TM</sup> Block Diagram

The SiI100 and SiI101 are high speed digital video interconnect devices for sending video data to digital displays, such as TFT or DSTN Liquid Crystal Displays (LCD). A block diagram of the transmission system is shown in Figure 1.

The transmitter (SiI100) receives parallel digital video data from a host graphics controller. Through the use of an internal PLL, the SiI100 encodes and serializes the parallel input data. The serialized data is then transmitted to the SiI101 receiver chip over the Transition Minimized Differential Signaling (TMDS<sup>TM</sup>) interconnect layer.

The TMDS™ interconnect layer consists of three high speed data channels, C2, C1 and C0 (red, green and blue, respectively) and one low speed clock channel. These signals are sent over four low voltage differential channels, the amplitude of which is set by the swing control circuit of the SiI100. The high speed data channels have a bandwidth equal to ten times the SiI100 input clock frequency, while the differential clock channel has the same frequency as the input clock. For example, if the input clock is 65 MHz, the output channels are 650 Mbps (megabits per second) and the differential clock channel is 65 MHz. These signals may be sent over a variety of physical medium, such as flex or twisted pair cables. In particular, the encoding of the serial channels is DC balanced, which is required in order for the channels to be capacitive coupled to fiber optic links or systems with independent ground potentials.

The SiI101 receives the serial data and clock from the SiI100. The differential signals are terminated by voltage controlled resistors internal to the SiI101. The value of the resistors is set by the termination control circuit. The differential clock is used only as a <u>frequency reference</u> to an internal PLL in the SiI101. The output of this PLL circuit is used to three times oversample the serial data channels. The oversampling and encoding enable the data recovery circuits to:

- 1. Determine the correct sampling point of each data channel <u>individually</u>. That is, the correct sampling point of each high speed channel is found independently from those of the other two data channels.

- 2. Determine the frame boundaries on each serial channel <u>individually</u>. The frame boundaries (also referred to as byte boundaries) are the locations within a serial data stream where the data for one byte ends and the data for then next byte begins.

- 3. Re-synchronize the three data channels to a single PLL generated clock. This re-synchronization corrects for inter-channel time skews up to one input clock cycle.

The synchronized data is then decoded back to the original parallel data. The SiI101 provides options to output the data at one 24 bit pixel per clock at the normal clock frequency, or in two 18 bit pixels per clock at half the clock frequency.

#### 5. SiI100 Overview

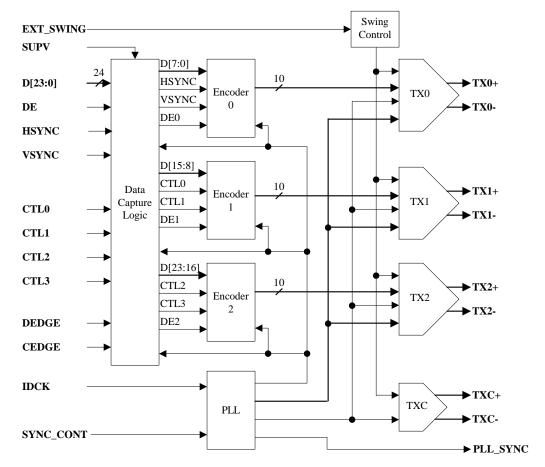

Figure 2. SiI100 Functional Block Diagram

Four major blocks of the SiI100 will be discussed below: Data Capture Logic, Encoders, Data and Clock Transmitters, and Swing Control.

#### **Data Capture Logic**

The data capture logic captures 24-bit RGB data (D[23:0]), 6 control signals (HSYNC, VSYNC, and CTL[3:0]), and data enable (DE) from the Graphics controller. Data and control signals can be latched on the rising or falling edge of IDCK depending on the state of the DEDGE and CEDGE configuration inputs respectively.

#### **Encoders**

Each encoder receives 8-bit data, 2 control signals, and a DE signal from the Data Capture Logic. When DE is HIGH (active display time), 8-bit data is converted to 10-bit coded data. The encoding guarantees DC-balanced and transition-minimized serial streams over the data channels during the active data period. When DE is LOW (blank time), 2-bit control signals are embedded into 10-bit synchronization control characters. The special characters enable the receiver to synchronize during every blank time (see the description of the SiI101 for a more complete description of what happens during synchronization).

### Data and Clock Transmitters (TX[2:0], TXC)

The three data transmitters convert the 10-bit coded data into a serial data stream. The maximum data rate of the data channels is ten times the input clock frequency. For example, for a 65 MHz input clock, the serial data channels transmit 650 Mbps. The input clock is converted directly to a pair of low voltage differential signals and sent to the receiver. Therefore, the transmitted clock has the same frequency as the input clock.

### **Swing Control**

The amplitude of the differential voltage swing is adjustable through the EXT\_SWING pin of the SiI100. A series resistor placed between AVCC and EXT\_SWING controls the swing amplitude. The larger the voltage swing, the better the signal to noise level, but the higher the power consumption of the cable driving circuit. The following settings are recommended for these common applications:

$R_{EXT~SWING} = 680~\Omega$  for short cable lengths, such as for computer laptops.

$R_{EXT~SWING} = 400~\Omega$  for long cable lengths, such as for desktop monitors.

#### 5.1 Data Input

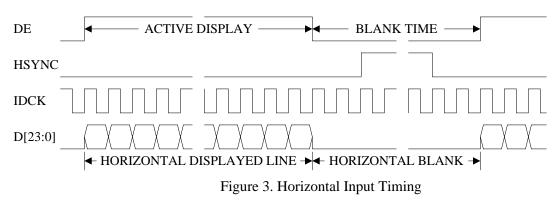

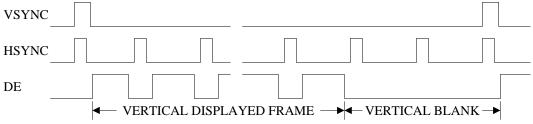

The following vertical and horizontal timing diagrams demonstrate the relationship between the data, control and clock signals input to the SiI100's parallel interface.

Figure 4. Vertical Input Timing

In the above figures, DE, HSYNC, and VSYNC signals are shown with positive polarity. DE <u>must</u> always have positive polarity, whereas HSYNC, VSYNC and the other control signals (CTL[3:0]) can have either positive or negative polarity. Since the encoding scheme is based on DE, this signal is always required. Because the state of the control signals, other than DE, are coded during the blanking time, the control signals must only transition during the blanking time. Any transitions of these control signals during the active data period will be ignored by the transmission link.

Input data D[23:0] and Data Enable (DE) are normally generated on the rising edge of IDCK by the graphics controller, since most panels latch data on the falling edge of the shift clock. For the SiI100, D[23:0] and DE can be latched on the rising or the falling edge of IDCK depending upon the setting of DEDGE and CEDGE, respectively.

#### 6. SiI101 Overview

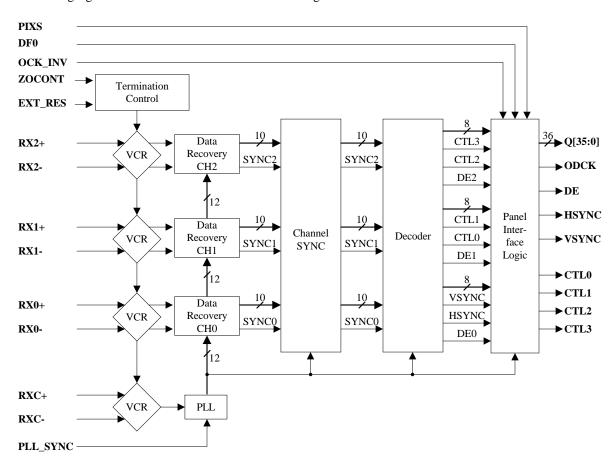

The following figure shows the SiI101 functional block diagram:

Figure 5. SiI101 Functional Block Diagram

Five major blocks of the SiI101 will be discussed below: Termination Control, Data Recovery, Channel Synchronization, Decoder, and the Panel Interface Logic.

#### **Termination Control**

All differential input channels are terminated by a VCR (Voltage Controlled Resistor), which is controlled by an adjustable impedance matching circuit. The VCR removes signal reflection on each line caused by an impedance mismatch between the cable and the inputs to the SiI101 sampling circuitry. The value of the termination is set by the value of a single resistor placed between the EXT\_RES pin of the SiI101 and the AVCC supply. The value of this resistor should be set to ten times the single-ended characteristic impedance of the transmission media. In most cases, the characteristic impedance is 50  $\Omega$ , so the external resistor should be set to 500  $\Omega$ . The ZOCONT configuration pin can be used to account for characteristic impedance of greater than or equal to 50  $\Omega$  (ZOCONT set low) and characteristic impedance of less than or equal to than 50  $\Omega$  (ZOCONT set high). For most cases, Silicon Image recommends setting ZOCONT high.

#### **Data Recovery**

The Data Recovery Block receives the high speed serial data from the transmitter. During horizontal or vertical blank time (when DE is LOW), one of four possible special characters are received. The data recovery block

differentiates the special characters from data characters by the number of transitions it detects. Each channel uses the PLL clock outputs to triple oversample the serial data. The phase tracking circuitry within the data recovery block, dynamically determines the best sampling point among the three sampling points. Also, the special codes enable the frame boundaries to be identified. Each 10 bit frame, during the active data period, is comprised of an encoded data byte (9 bits) and 1 coded bit for DC balancing. The phase and frame information, determined during the blanking time, is locked in and used for data recovery during the active data period. This information remains locked in until the next blanking period at which point it is reevaluated. The data recovery block treats each channel individually, meaning that the phase and byte information are generated for each channel. This enables the data channels to be skewed relative to each other with no adverse effect. The Data Recovery Block further converts the serial data streams to 10-bit parallel output streams from the frame boundary information.

#### **Channel Synchronization**

In the Channel Synchronization Block, the three data channels are re-synchronized to a single clock. The synchronization block aligns the channels up to a worse case skew of one input clock cycle (15ns at 65MHz).

#### **Decoder**

The Decoder Block receives 10-bit data and Sync signals from the Channel Synchronization Block, and then decodes the data to 8-bit RGB data, 2-bit control signals and a DE (Data Enable) signal.

#### **Panel Interface Logic**

The Panel Interface Logic is used to output the parallel data and control signals. The SiI101 data output is configurable for two output modes by the PIXS pin. When PIXS is LOW, the data output is one pixel per clock (24-bits per pixel, synchronized to the ODCK clock output). When PIXS is HIGH, the data output is in two pixels per clock mode (two 18 bits pixels, synchronized to a half frequency ODCK). The next two sections show the timing of these data output modes and the data mapping to use for these modes.

The SiI101 is also configurable for normal ODCK output or inverted ODCK output set by the OCK\_INV configuration pin. The configuration pin DF0 selects whether the output clock is blanked (low) during the DE low period or whether the output clock is free running. Many passive DSTN panels make use of the blanked clock output mode. Additional options for dividing the output clock frequency are available in 24-bit DSTN mode (DF0 high), which are described in Section 6.3. The following table summarizes the clock output modes as a function of DF0, PIXS, and OCK\_INV.

| DF0 | PIX | OCK_INV | PANEL           | ODCK (frequency/data latch edge/mode) |

|-----|-----|---------|-----------------|---------------------------------------|

| 0   | 0   | 0       | TFT/16-bit DSTN | divide by 1 / negative / free running |

| 0   | 0   | 1       | TFT/16-bit DSTN | divide by 1 / positive / free running |

| 0   | 1   | 0       | TFT             | divide by 2 / negative / free running |

| 0   | 1   | 1       | TFT             | divide by 2 /positive / free running  |

| 1   | 0   | 0       | 24-bit DSTN     | divide by 1 / negative / blanked low  |

| 1   | 0   | 1       | NONE            | divide by 1 / negative / blanked high |

| 1   | 1   | 0       | 24-bit DSTN     | divide by 2 / negative / blanked low  |

| 1   | 1   | 1       | 24-bit DSTN     | divide by 4 / negative / blanked low  |

Table 1. Output Clock Configuration by Typical Application

### **6.1 Output Modes**

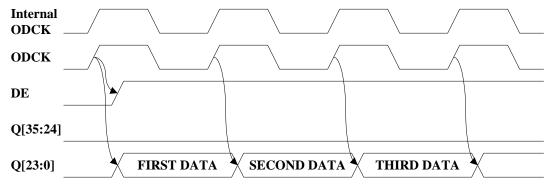

#### 6.1.1 One Pixel Per Clock Mode

When the PIXS configuration input is low, the output data format is 24-bit per ODCK on the data output pins Q[23:0]. The timing relationship between the ODCK, DE and the output data, when PIXS and OCK\_INV pins are low, is shown in the following timing diagram. When OCK\_INV is high the output clock is inverted from the clock shown in the figure below.

Figure 6. One Pixel/Clock Timing with OCK\_INV = Low

#### 6.1.2 Two Pixels Per Clock Mode

When the PIXS pin is high and the OCK\_INV pin is low, two pixels per clock are generated and ODCK is run at half frequency. In this mode, the output data format is 36-bit per ODCK and 18-bits per pixel. In this configuration, the two least significant bits for each byte of output data is discarded (not used). The first pixel data is output on Q[17:0] pins and the second pixel data is output on Q[35:18] pins as shown below. When OCK\_INV is high the output clock is inverted from the clock shown in the figure below.

Figure 7. Two Pixels/Clock Timing with OCK\_INV = Low

## 6.2 Data Mapping (TFT) - VESA® Compatible

## 6.2.1 One Pixel Per Clock Data Mapping

The following table shows the output data mapping in one pixel per clock mode for the connections from the SiI100 to the SiI101. Note that the three data channels (CH0, CH1 and CH2) are mapped to blue, green and red data respectively.

|         |          | SiI100    |          | SiI101              |          |          |  |  |  |

|---------|----------|-----------|----------|---------------------|----------|----------|--|--|--|

|         | 1        | Pixel/Clo | ck       | 1 Pixel/Clock       |          |          |  |  |  |

|         | 12bpp    | 18bpp     | 24bpp    | 4bpp 12bpp 18bpp 24 |          |          |  |  |  |

| СНО     | D[7:4]   | D[7:2]    | D[7:0]   | Q[7:4]              | Q[7:2]   | Q[7:0]   |  |  |  |

| (BLUE)  | HSYNC    | HSYNC     | HSYNC    | HSYNC               | HSYNC    | HSYNC    |  |  |  |

|         | VSYNC    | VSYNC     | VSYNC    | VSYNC               | VSYNC    | VSYNC    |  |  |  |

| CH1     | D[15:12] | D[15:10]  | D[15:8]  | Q[15:12]            | Q[15:10] | Q[15:8]  |  |  |  |

| (GREEN) | CTL0     | CTL0      | CTL0     | CTL0                | CTL0     | CTL0     |  |  |  |

|         | CTL1     | CTL1      | CTL1     | CTL1                | CTL1     | CTL1     |  |  |  |

| CH2     | D[23:20] | D[23:18]  | D[23:16] | Q[23:20]            | Q[23:18] | Q[23:16] |  |  |  |

| (RED)   | CTL2     | CTL2      | CTL2     | CTL2                | CTL2     | CTL2     |  |  |  |

|         | CTL3     | CTL3      | CTL3     | CTL3                | CTL3     | CTL3     |  |  |  |

Table 2. One Pixel/Clock Mode Data Mapping from SiI100 to SiI101

Note: For 18/12-bit mode, the LCD Graphics Controller interfaces to the SiI100 exactly the same as in the 24-bit mode; however, 6/4 bits per channel (color) are transmitted instead of 8. It is recommended that unused data bits be tied low.

Note: As can be seen from the above table, the data mapping for less than 24-bit per pixel interfaces are MSB justified.

## 6.2.2 Two Pixels Per Clock Data Mapping

The following table shows the output data mapping for two pixels per clock from the SiI100 to the SiI101. Pixel N to Pixel N+3, represent four consecutive input pixels to the SiI100. Pixels M and M+1 represent two consecutive parallel outputs of the SiI101, in two pixels per clock mode.

|             | Si       | I100     | Si            | I101     |  |  |  |

|-------------|----------|----------|---------------|----------|--|--|--|

|             | 1 Pix    | el/Clock | 2 Pixel/Clock |          |  |  |  |

|             | 12bpp    | 18bpp    | 12bpp         | 18bpp    |  |  |  |

| (Pixel N)   | IDO      | CK[N]    | ODO           | CK[M]    |  |  |  |

| CH0 (blue)  | D[7:4]   | D[7:2]   | Q[5:2]        | Q[5:0]   |  |  |  |

| CH1 (green) | D[15:12] | D[15:10] | Q[11:8]       | Q[11:6]  |  |  |  |

| CH2 (red)   | D[23:20] | D[23:18] | Q[17:14]      | Q[17:12] |  |  |  |

|             |          |          |               |          |  |  |  |

| (Pixel N+1) | IDC      | K[N+1]   | ODO           | CK[M]    |  |  |  |

| CH0 (blue)  | D[7:4]   | D[7:2]   | Q[23:20]      | Q[23:18] |  |  |  |

| CH1 (green) | D[15:12] | D[15:10] | Q[29:26]      | Q[29:24] |  |  |  |

| CH2 (red)   | D[23:20] | D[23:18] | Q[35:32]      | Q[35:30] |  |  |  |

|             |          |          |               |          |  |  |  |

| (Pixel N+2) | IDC      | K[N+2]   | ODC           | K[M+1]   |  |  |  |

| CH0 (blue)  | D[7:4]   | D[7:2]   | Q[5:2]        | Q[5:0]   |  |  |  |

| CH1 (green) | D[15:12] | D[15:10] | Q[11:8]       | Q[11:6]  |  |  |  |

| CH2 (red)   | D[23:20] | D[23:18] | Q[17:14]      | Q[17:12] |  |  |  |

|             |          |          |               |          |  |  |  |

| (Pixel N+3) | IDC      | K[N+3]   | ODC           | K[M+1]   |  |  |  |

| CH0 (blue)  | D[7:4]   | D[7:2]   | Q[23:20]      | Q[23:18] |  |  |  |

| CH1 (green) | D[15:12] | D[15:10] | Q[29:26]      | Q[29:24] |  |  |  |

| CH2 (red)   | D[23:20] | D[23:18] | Q[35:32]      | Q[35:30] |  |  |  |

Table 3. Two Pixels/Clock Output Data Mapping

Note: In 36-bit mode, the frequency of IDCK of the SiI100 is 2x that of ODCK of the SiI101. The 2 LSBs of 8-bit decoded data will be ignored to generate 18 (3x6) bit pixels. As shown in the mapping diagram, even numbered pixels (Pixel 0, 2, 4, ....) are received via Q[17:0], and odd numbered pixels (Pixel 1, 3, 5, ...) are received via Q[35:18].

Note: As can be seen from the above table, the data mapping for less than 18-bit per pixel interfaces are MSB justified.

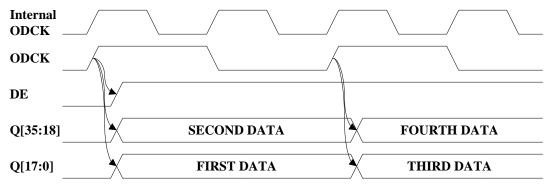

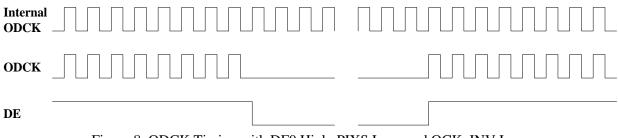

## 6.3 Output Clock Modes for 24-bit DSTN

The following timing diagrams show the clock output timing for the DF0 = 1 modes. These modes are most useful for 24-bit Color DSTN panel support. The internal clock depicted in each figure has the same frequency as the input clock IDCK (i.e. one pixel per clock frequency), and is shown for comparison to the output clock timing.

Figure 8. ODCK Timing with DF0 High, PIXS Low, and OCK\_INV Low

Figure 9. ODCK Timing with DF0 High, PIXS High, and OCK\_INV Low

Figure 10. ODCK Timing with DF0 High, PIXS High, and OCK\_INV High

## 6.4 Data Mapping (DSTN) - VESA® Compatible

| Input Data Pin | 24-bit                      | 16-bit    | 24-bit | 16-bit                                       |           |

|----------------|-----------------------------|-----------|--------|----------------------------------------------|-----------|

|                |                             |           | Pin    |                                              |           |

| D0             | UR0                         | UR0       | Q0     | UR0                                          | UR0       |

| D1             | UG0                         | UG0       | Q1     | UG0                                          | UG0       |

| D2             | UB0                         | UB0       | Q2     | UB0                                          | UB0       |

| D3             | LR0                         | UR1       | Q3     | LR0                                          | UR1       |

| D4             | LG0                         | LR0       | Q4     | LG0                                          | LR0       |

| D5             | LB0                         | LG0       | Q5     | LB0                                          | LG0       |

| D6             | UR1                         | LB0       | Q6     | UR1                                          | LB0       |

| D7             | UG1                         | LR1       | Q7     | UG1                                          | LR1       |

| D8             | UB1                         | UG1       | Q8     | UB1                                          | UG1       |

| D9             | LR1                         | UB1       | Q9     | LR1                                          | UB1       |

| D10            | LG1                         | UR2       | Q10    | LG1                                          | UR2       |

| D11            | LB1                         | UG2       | Q11    | LB1                                          | UG2       |

| D12            | UR2                         | LG1       | Q12    | UR2                                          | LG1       |

| D13            | UG2                         | LB1       | Q13    | UG2                                          | LB1       |

| D14            | UB2                         | LR2       | Q14    | UB2                                          | LR2       |

| D15            | LR2                         | LG2       | Q15    | LR2                                          | LG2       |

| D16            | LG2                         | Shift CLK | Q16    | LG2                                          | Shift CLK |

| D17            | LB2                         |           | Q17    | LB2                                          |           |

| D18            | UR3                         |           | Q18    | UR3                                          |           |

| D19            | UG3                         |           | Q19    | UG3                                          |           |

| D20            | UB3                         |           | Q20    | UB3                                          |           |

| D21            | LR3                         |           | Q21    | LR3                                          |           |

| D22            | LG3                         |           | Q22    | LG3                                          |           |

| D23            | LB3                         |           | Q23    | LB3                                          |           |

| IDCK           | Pixel CLK<br>or Pixel CLK/2 | Pixel CLK | ODCK   | Pixel CLK/4<br>or Pixel CLK/2<br>(Shift CLK) | Pixel CLK |

| VSYNC          | FLM                         | FLM       | VSYNC  | FLM                                          | FLM       |

| HSYNC          | LP                          | LP        | HSYNC  | LP                                           | LP        |

| DE             | DE                          | DE        | DE     | DE                                           | DE        |

|           | 24-bit            | 16-bit            |

|-----------|-------------------|-------------------|

| CHANNEL 0 | D[7:0]/Q[7:0]     | D[7:0]/Q[7:0]     |

|           | HSYNC, VSYNC      | HSYNC, VSYNC      |

| CHANNEL 1 | D[15:8]/Q[15:8]   | D[15:8]/Q[15:80]  |

|           | PLL_SYNC, CTL1    | PLL_SYNC, CTL1    |

| CHANNEL 2 | D[23:16]/Q[23:16] | D[23:16]/Q[23:16] |

|           | CTL2, CTL3        | CTL2, CTL3        |

Table 4. DSTN Data Mapping

#### Note:

The clock input to IDCK must be free running. For 16-bit DSTN support, the SiI101 must be in 1 pixel/clock mode (PIXS=0) and DF0 must be set low. This enables the panel shift clock to be sent over the unused data pin Q16, as shown above. For 24-bit DSTN support, the SiI101 must be in 24-bit DSTN mode (DF0=1). In this mode the panel shift clock is recreated on the ODCK output by programming PIXS and OCK\_INV (see Table 1). The panel shift clock (ODCK) can be divided by either 2 or 4 depending on IDCK frequency.

(This page left intentionally blank)

## 7. TMDS<sup>TM</sup> Interconnect Layer

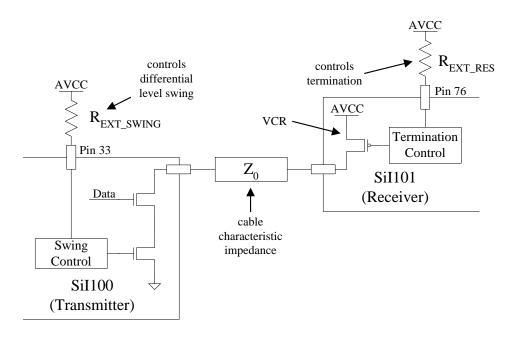

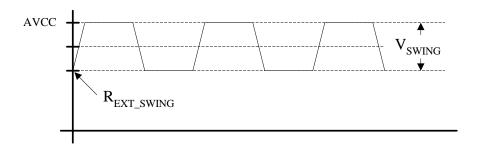

The TMDS<sup>TM</sup> Interconnect Layer refers to the electrical and physical connection between the transmitter and receiver. Typically, the physical media for this layer is a twisted pair or flex cable. PanelLink<sup>TM</sup> technology uses current mode to electrically drive the cable of the TMDS<sup>TM</sup> Interconnect Layer. In the following figure, the cable driving circuit between the transmitter and receiver is shown. The signal voltage is developed by pulling down the cable potential through the pull down devices at the transmitter side. The receiver contains the pull-up device which is a voltage controlled resistor that provides termination to AVCC. The actual signal voltage will therefore pull-down from AVCC (nominally 3.3V) as shown in Figure 12.

Figure 11. Differential Signaling Circuit

Figure 12. Single-Ended Low Voltage Differential Signal Adjustment

### 7.1 Voltage Swing Control (EXT\_SWING)

The amplitude of the differential voltage swing is adjustable through the EXT\_SWING pin of the SiI100. A series resistor placed between AVCC and EXT\_SWING controls the swing amplitude. The functional relationship between the resistor value and the voltage swing is approximately given by:

```

V_{SWING} = 0.5V \text{ x } (500\Omega/R_{EXT\_SWING}) \text{ where } V_{SWING} = Single-ended differential voltage swing.}

R_{EXT\_SWING} = External \text{ resistor on } EXT\_SWING \text{ pin.}

```

The larger the voltage swing, the better the signal to noise ratio, but the higher the power consumption of the cable driving circuit. The following settings are recommended for these common applications:

$R_{EXT\_SWING} = 680~\Omega$  for short cable lengths, such as for computer laptops.  $R_{EXT\_SWING} = 400~\Omega$  for long cable lengths, such as for desktop monitors.

### 7.2 Termination Control (EXT\_RES)

The value of the termination is set by the value of a single resistor placed between the EXT\_RES pin of the SiI101 and the AVCC supply. The value of this resistor should be set to ten times the single-ended characteristic impedance of the transmission media. In most cases, the characteristic impedance is 50  $\Omega$ , so the external resistor should be set to 500  $\Omega$ . The ZOCONT configuration pin can be used to account for characteristic impedance of greater than or equal to 50  $\Omega$  (ZOCONT set low) and characteristic impedance of less than or equal to than 50  $\Omega$  (ZOCONT set high). In most cases, ZOCONT high is recommended.

## 8. PLL Synchronization

PanelLink<sup>TM</sup> technology uses a PLL synchronization feature to make the link more robust to IDCK clock jitter and supply noise. PLL synchronization ensures that the transmitter and receiver PLLs respond to clock jitter and system noise with the same phase. This synchronization is accomplished by generating a sync signal (PLL\_SYNC) based on the VSYNC control input to the SiI100, PLL\_SYNC is independent of the polarity or the VSYNC input. The PLL\_SYNC signal needs to be sent from the SiI100 to the SiI101 for the synchronization to be enabled. While this signal can be routed directly from the transmitter to the receiver, Silicon Image strongly recommends that the PLL\_SYNC signal be sent over the auxiliary control line CTL0. In this way, no extra interconnect lines are required and delays due to the transmission distance will be automatically compensated. Silicon Image has reserved CTL0 for this purpose. To be compatible with future PanelLink<sup>TM</sup> products and VESA®&D, PLL\_SYNC must be sent over CTL0. The following figure shows how to send PLL\_SYNC over the CTL0 control line.

Figure 13. How to send PLL\_SYNC over CTL0

# 9. SiI100 Pin Description

# 9.1 SiI100 Pin Diagram

The SiI100 is available in a 64-pin 10mm x 10mm TQFP package.

|           | VCC              | AGND   | TX2+ | TX2- | AVCC | TX1+ | TX1- | AGND | TX0+ | TX0- | AVCC | TXC+ | TXC- | AGND | PVCC | PGND |     |        |     |

|-----------|------------------|--------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|--------|-----|

|           |                  | $\Box$ |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |        |     |

| EXT_SWING | ☐33 <sup>2</sup> | 31     | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 16   | G   | ND     |     |

| SUPV      | <u> </u>         |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 15   | P   | LLCK   |     |

| PD        | <u></u> 35       |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 14   | S   | YNC_CO | ONT |

| PLL_SYNC  | <u> </u>         |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 13   | R   | SVD    |     |

| D23       | <u></u> 37       |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 12   | II  | OCK    |     |

| D22       | <u></u> 38       |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 11   | C   | EDGE   |     |

| VCC       | 39               |        |      |      |      |      |      | C:1  | [10  | n    |      |      |      |      |      | 10   | _ v | CC     |     |

| D21       | <u> </u>         |        |      |      |      |      | 64   |      | n T( |      |      |      |      |      |      | 9    | D   | EDGE   |     |

| D20       | <u> </u>         |        |      |      |      |      |      |      | Viev |      |      |      |      |      |      | 8    | C   | TL3    |     |

| D19       | <u>42</u>        |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 7    | C   | TL2    |     |

| D18       | <u>43</u>        |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 6    | C   | TL1    |     |

| D17       | <u>44</u>        |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 5    | C   | TL0    |     |

| GND       | <u>45</u>        |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 4    | G   | ND     |     |

| D16       | <u> </u>         |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 3    | _ v | SYNC   |     |

| D15       | 47               |        |      |      |      |      |      |      |      |      |      |      |      |      |      | 2    | H   | SYNC   |     |

| D14       | 486              | 50     | 51   | 52   | 53   | 54   | 55   | 99   | 57   | 58   | 59   | 09   | 61   | 62   | 63   | Q 1  |     | E      |     |

|           | 4                |        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |        |     |

|           | D13              | D12    | D11  | D10  | IVCC | D9   | D8   | D7   | D6   | D5   | 74   | D3   | D2   | D1   | D0   | GND  |     |        |     |

Figure 14. SiI100 Pin Diagram

# 9.2 SiI100 Pins Grouped by Functionality

# 9.2.1 SiI100 Input Pin Description

| Pin Name | Pin# | Type | Description                                                                           |

|----------|------|------|---------------------------------------------------------------------------------------|

| D23      | 37   | In   | Input Data[23:0].                                                                     |

| D22      | 38   | In   | Input data is synchronized with input data clock (IDCK).                              |

| D21      | 40   | In   |                                                                                       |

| D20      | 41   | In   | Refer to Signal Mapping Section 6.2 for description of data coordination between      |

| D19      | 42   | In   | data in for SiI100 and data out for SiI101.                                           |

| D18      | 43   | In   |                                                                                       |

| D17      | 44   | In   |                                                                                       |

| D16      | 46   | In   |                                                                                       |

| D15      | 47   | In   |                                                                                       |

| D14      | 48   | In   |                                                                                       |

| D13      | 49   | In   |                                                                                       |

| D12      | 50   | In   |                                                                                       |

| D11      | 51   | In   |                                                                                       |

| D10      | 52   | In   |                                                                                       |

| D9       | 54   | In   |                                                                                       |

| D8       | 55   | In   |                                                                                       |

| D7       | 56   | In   |                                                                                       |

| D6       | 57   | In   |                                                                                       |

| D5       | 58   | In   |                                                                                       |

| D4       | 59   | In   |                                                                                       |

| D3       | 60   | In   |                                                                                       |

| D2       | 61   | In   |                                                                                       |

| D1       | 62   | In   |                                                                                       |

| D0       | 63   | In   |                                                                                       |

| IDCK     | 12   | In   | Input Data Clock. Input data can be valid either on the falling or on the rising edge |

|          |      |      | of IDCK as selected by DEDGE pin.                                                     |

| DE       | 1    | In   | Input Data Enable. This signal qualifies the active data period. DE is always         |

|          |      |      | required by the SiI100 and must be high during active display time and low during     |

|          |      |      | blank time.                                                                           |

| HSYNC    | 2    | In   | Horizontal Sync input control signal.                                                 |

| VSYNC    | 3    | In   | Vertical Sync input control signal.                                                   |

| CTL0     | 5    | In   | Reserved control signal, which should be connected to PLL_SYNC (pin 36).              |

| CTL1     | 6    | In   | General input control signal 1.                                                       |

| CTL2     | 7    | In   | General input control signal 2.                                                       |

| CTL3     | 8    | In   | General input control signal 3.                                                       |

# 9.2.2 SiI100 Test Output Pin Description

| Pin Name | Pin# | Type | Description                                                                                                                                                                                                                                                        |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLLCK    | 15   | Out  | Internal PLL Clock Output. The operating frequency is 2.5 times that of IDCK. This signal is for test purposes only, and should be left unconnected. To probe this signal output, a 500 $\Omega$ pull down resistor must be connected between this pin and ground. |

# 9.2.3 SiI100 Synchronization Pin Description

| Pin Name | Pin# | Type | Description                                                                     |

|----------|------|------|---------------------------------------------------------------------------------|

| PLL_SYNC | 36   | Out  | PLL Synchronization. Generated every VSYNC to force synchronization of both     |

|          |      |      | transmitter and receiver PLL clocks. This pin must be connected to pin 5 (CTL0) |

|          |      |      | to enable the PLL synchronization feature.                                      |

# 9.2.4 SiI100 Configuration Pin Description

| Pin Name  | Pin# | Type | Description                                                                         |

|-----------|------|------|-------------------------------------------------------------------------------------|

| DEDGE     | 9    | In   | Data Latching Edge. A low level indicates that input data (D[23:0]) will be         |

|           |      |      | latched on the falling edge of IDCK while a high level (3.3V) indicates that input  |

|           |      |      | data will be latched on the rising edge of IDCK.                                    |

| CEDGE     | 11   | In   | Control Latching Edge. Controls latching edge of control signals DE, HSYNC,         |

|           |      |      | VSYNC, and CTL[3:0]. A low level indicates that input data enable and control       |

|           |      |      | signals will be latched on the falling edge of IDCK, while a high level (3.3V)      |

|           |      |      | indicates that input data enable and control signals will be latched on rising edge |

|           |      |      | of IDCK.                                                                            |

| RSVD      | 13   | In   | This signal must be tied high (3.3V) for normal operation.                          |

|           |      |      |                                                                                     |

| SYNC_CONT | 14   | In   | PLL Synchronization Control. This signal should be tied high (3.3V) when            |

|           |      |      | PLL_SYNC is sent over CTL0, see Figure 13.                                          |

| SUPV      | 34   | In   | Input Threshold Voltage Control. A high level (3.3V) indicates that input signal    |

|           |      |      | voltage level is 5V and a low level indicates that input signal voltage level is    |

|           |      |      | 3.3V. Should match IVCC voltage.                                                    |

| PD        | 35   | In   | Power Down (active low). A high level (3.3V) indicates normal operation and a       |

|           |      |      | low level indicates power down mode. During power down mode, all data and           |

|           |      |      | control inputs are disabled and most internal logic is powered down.                |

# 9.2.5 SiI100 Analog Data Pin Description

| Pin Name | Pin# | Type   | Description                                                                          |

|----------|------|--------|--------------------------------------------------------------------------------------|

| TX0+     | 24   | Analog | Low Voltage Differential Signal output data pairs.                                   |

| TX0-     | 23   | Analog |                                                                                      |

| TX1+     | 27   | Analog |                                                                                      |

| TX1-     | 26   | Analog |                                                                                      |

| TX2+     | 30   | Analog |                                                                                      |

| TX2-     | 29   | Analog |                                                                                      |

| TXC+     | 21   | Analog | Low Voltage Differential Signal output clock pair.                                   |

| TXC-     | 20   | Analog |                                                                                      |

| EXT_     | 33   | Analog | Voltage Swing Adjust. A resistor should tie this pin to AVCC. The amplitude of       |

| SWING    |      |        | the voltage swing is determined by this resistance. For remote display applications, |

| ī        |      |        | $400~\Omega$ is recommended. For laptop computers, $680~\Omega$ is recommended.      |

# 9.2.6 SiI100 Power and Ground Pin Description

| Pin Name | Pin# | Type   | Description                                                                           |

|----------|------|--------|---------------------------------------------------------------------------------------|

| VCC      | 10   | Power  | Core VCC. These VCC pins supply power to the core digital logic and must be set       |

| VCC      | 32   | Power  | to 3.3V.                                                                              |

| VCC      | 39   | Power  |                                                                                       |

| IVCC     | 53   | Power  | Input VCC. This VCC pin supplies power for the input pin protection devices.          |

|          |      |        | This pin must be set to 5V if input signals are at 5V and can be set to 3.3V if input |

|          |      |        | signals are at 3.3V. SUPV should be set accordingly.                                  |

| GND      | 4    | Ground | Digital GND.                                                                          |

| GND      | 16   | Ground |                                                                                       |

| GND      | 45   | Ground |                                                                                       |

| GND      | 64   | Ground |                                                                                       |

|          |      |        |                                                                                       |

| AVCC     | 22   | Power  | Analog VCC, must be set to 3.3V.                                                      |

| AVCC     | 28   | Power  |                                                                                       |

| AGND     | 19   | Ground | Analog GND.                                                                           |

| AGND     | 25   | Ground |                                                                                       |

| AGND     | 31   | Ground |                                                                                       |

|          |      |        |                                                                                       |

| PVCC     | 18   | Power  | PLL Analog VCC, must be set to 3.3V.                                                  |

| PGND     | 17   | Ground | PLL Analog GND.                                                                       |

# 9.3 SiI100 Pins Listed Numerically

| Pin# | Pin Name | Type   | Description                                                                              |

|------|----------|--------|------------------------------------------------------------------------------------------|

| 1    | DE       | In     | Input Data Enable. This signal qualifies the active data period. DE is always            |

|      |          |        | required by the SiI100 and must be high during active display time and low during        |

|      |          |        | blank time.                                                                              |

| 2    | HSYNC    | In     | Horizontal Sync input control signal.                                                    |

| 3    | VSYNC    | In     | Vertical Sync input control signal.                                                      |

| 4    | GND      | Ground | Digital GND.                                                                             |

| 5    | CTL0     | In     | Reserved control signal, which should be connected to PLL_SYNC (pin 36).                 |

| 6    | CTL1     | In     | General input control signal 1.                                                          |

| 7    | CTL2     | In     | General input control signal 2.                                                          |

| 8    | CTL3     | In     | General input control signal 3.                                                          |

| 9    | DEDGE    | In     | Data Latching Edge. A low level indicates that input data (D[23:0]) will be latched      |

|      |          |        | on the falling edge of IDCK while a high level (3.3V) indicates that input data will be  |

|      |          |        | latched on the rising edge of IDCK.                                                      |

| 10   | VCC      | Power  | Core VCC. This VCC pin supplies power to the core digital logic and must be set to       |

|      |          |        | 3.3V.                                                                                    |

| 11   | CEDGE    | In     | Control Latching Edge. Controls latching edge of control signals DE, HSYNC,              |

|      |          |        | VSYNC, and CTL[3:0]. A low level indicates that input data enable and control            |

|      |          |        | signals will be latched on the falling edge of IDCK, while a high level (3.3V)           |

|      |          |        | indicates that input data enable and control signals will be latched on rising edge of   |

|      |          |        | IDCK.                                                                                    |

| 12   | IDCK     | In     | Input Data Clock. Input data can be valid either on falling or on rising edge of IDCK    |

|      |          |        | as selected by DEDGE pin.                                                                |

| 13   | RSVD     | In     | This signal must be tied high (3.3V) for normal operation.                               |

|      |          |        |                                                                                          |

| 14   | SYNC_    | In     | PLL Synchronization Control. This signal should be tied high (3.3V) when                 |

|      | CONT     |        | PLL_SYNC is sent over CTL0, see Figure 13.                                               |

| 15   | PLLCK    | Out    | Internal PLL Clock Output. The operating frequency is 2.5 times that of IDCK. This       |

|      |          |        | signal is for test purposes only, and should be left unconnected. To probe this signal   |

|      |          |        | output, a 500 $\Omega$ pull down resistor must be connected between this pin and ground. |

| 16   | GND      | Ground | Digital GND.                                                                             |

| 17   | PGND     | Ground | PLL Analog GND.                                                                          |

| 18   | PVCC     | Power  | PLL Analog VCC, must be set to 3.3V.                                                     |

| 19   | AGND     | Ground | Analog GND.                                                                              |

| 20   | TXC-     | Analog | Low voltage Differential Signal output clock pair.                                       |

| 21   | TXC+     | Analog |                                                                                          |

| 22   | AVCC     | Power  | Analog VCC must be set to 3.3V.                                                          |

| 23   | TX0-     | Analog | Low Voltage Differential Signal output data pairs.                                       |

| 24   | TX0+     | Analog |                                                                                          |

| 25   | AGND     | Ground | Analog GND.                                                                              |

| 26   | TX1-     | Analog | Low Voltage Differential Signal output data pairs.                                       |

| 27   | TX1+     | Analog |                                                                                          |

SiI100 Numerical Pin Description (cont'd)

| SiI100 | SiI100 Numerical Pin Description (cont'd) |        |                                                                                                                                                                                                                                                     |  |  |

|--------|-------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin#   | Pin Name                                  | Type   | Description                                                                                                                                                                                                                                         |  |  |

| 28     | AVCC                                      | Power  | Analog VCC must be set to 3.3V.                                                                                                                                                                                                                     |  |  |

| 29     | TX2-                                      | Analog | Low Voltage Differential Signal output data pairs.                                                                                                                                                                                                  |  |  |

| 30     | TX2+                                      | Analog |                                                                                                                                                                                                                                                     |  |  |

| 31     | AGND                                      | Ground | Analog GND.                                                                                                                                                                                                                                         |  |  |

| 32     | VCC                                       | Power  | Core VCC. This VCC pin supplies power to the core digital logic and must be set to 3.3V.                                                                                                                                                            |  |  |

| 33     | EXT_<br>SWING                             | Analog | Voltage Swing Adjust. A resistor should tie this pin to AVCC. The amplitude of the voltage swing is determined by this resistance. For remote display applications, $400 \Omega$ is recommended. For laptop computers, $680 \Omega$ is recommended. |  |  |

| 34     | SUPV                                      | In     | Input Threshold Voltage Control. A high level (3.3V) indicates that input signal voltage level is 5V and a low level indicates that input signal voltage level is 3.3V. Should match IVCC voltage.                                                  |  |  |

| 35     | PD                                        | In     | Power Down (active low). A high level (3.3V) indicates normal operation and a low level indicates power down mode. During power down mode, all data and control inputs are disabled and most internal logic is powered down.                        |  |  |

| 36     | PLL_<br>SYNC                              | Out    | PLL Synchronization. Generated every VSYNC to force synchronization of both transmitter and receiver PLL clocks. This pin must be connected to pin 5 (CTL0) to enable the PLL synchronization feature.                                              |  |  |

| 37     | D23                                       | In     | Input Data.                                                                                                                                                                                                                                         |  |  |

| 38     | D22                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 39     | VCC                                       | Power  | Core VCC. This VCC pin supplies power to the core digital logic and must be set to 3.3V.                                                                                                                                                            |  |  |

| 40     | D21                                       | In     | Input Data.                                                                                                                                                                                                                                         |  |  |

| 41     | D20                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 42     | D19                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 43     | D18                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 44     | D17                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 45     | GND                                       | Ground | Digital GND.                                                                                                                                                                                                                                        |  |  |

| 46     | D16                                       | In     | Input Data.                                                                                                                                                                                                                                         |  |  |

| 47     | D15                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 48     | D14                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 49     | D13                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 50     | D12                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 51     | D11                                       | In     |                                                                                                                                                                                                                                                     |  |  |

| 52     | D10                                       | In     | L. AVOC TIL' VCC d'anni l'anni Carta 'anni a' anni d'anni l'anni Til'                                                                                                                                                                               |  |  |

| 53     | IVCC                                      | Power  | Input VCC. This VCC pin supplies power for the input pin protection devices. This pin must be set to 5V if input signals are at 5V and can be set to 3.3V if input signals are at 3.3V. SUPV should be set accordingly.                             |  |  |

| 54     | D9                                        | In     | Input Data.                                                                                                                                                                                                                                         |  |  |

| 55     | D8                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 56     | D7                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 57     | D6                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 58     | D5                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 59     | D4                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 60     | D3                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 61     | D2                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 62     | D1                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 63     | D0                                        | In     |                                                                                                                                                                                                                                                     |  |  |

| 64     | 64                                        | Ground | Digital GND.                                                                                                                                                                                                                                        |  |  |

# 10. SiI101 Pin Description

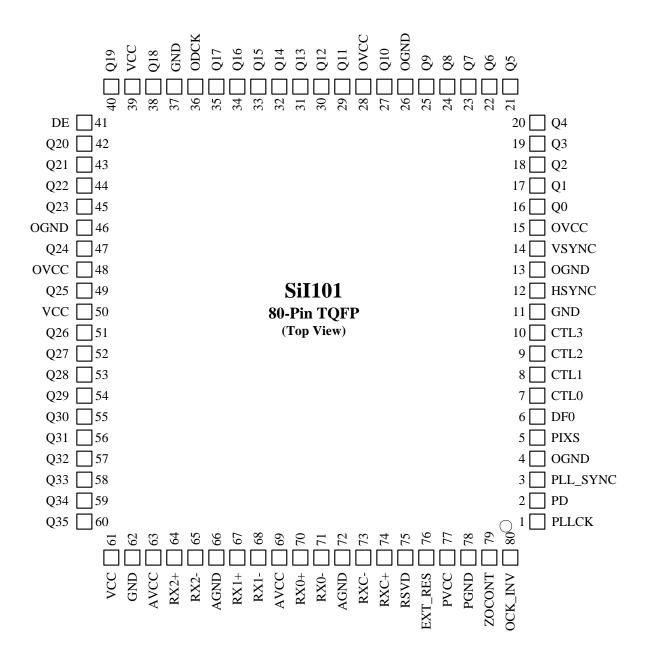

## 10.1 SiI101 Pin Diagram

The SiI101 is available in an 80-pin 12mm x 12mm TQFP package.

Figure 15. SiI101 Pin Diagram

# 10.2 SiI101 Pins Grouped by Functionality

# 10.2.1 SiI101 Data Output Pin Description

| Pin Name   | Pin# | Type | Description                                                                      |

|------------|------|------|----------------------------------------------------------------------------------|

| Q35        | 60   | Out  | Output Data [35:0].                                                              |

| Q34        | 59   | Out  | Output data is synchronized with output data clock (ODCK).                       |

| Q33        | 58   | Out  | When PIXS is low Q35-Q24 are low and Q23-Q0 output 24-bit/pixel data.            |

| Q32        | 57   | Out  | When PIXS is high Q17-Q0 output the even numbered pixels (pixel 0, 2, 4,, etc.)  |

| Q31        | 56   | Out  | and Q35-Q18 output the odd numbered pixels (pixel 1, 3, 5,, etc.).               |

| Q30        | 55   | Out  |                                                                                  |

| Q29        | 54   | Out  | Refer to Signal Mapping Section 6.2 for description of data coordination between |

| Q28        | 53   | Out  | data in for SiI100 and data out for SiI101.                                      |

| Q27        | 52   | Out  |                                                                                  |

| Q26        | 51   | Out  |                                                                                  |

| Q25        | 49   | Out  |                                                                                  |

| Q24        | 47   | Out  |                                                                                  |

| Q23        | 45   | Out  |                                                                                  |

| Q22        | 44   | Out  |                                                                                  |