# Single-chip 4-bit microcontroller for CD-DA BU34675

The BU34675 is a compact 4-bit, single-chip microcontroller that includes all the I / O required for CD system control. Circuits on the chip include a pulse width measurement counter (PWC), SIO, and an LCD controller / driver for a 28-segment display. The LCD segments can all be switched in software to CMOS output, and the extensive I / O allows many functions with a low pin count.

# Applications

Portable CD-DA, CD / radio / cassette players

### Features

- Low-voltage, high-speed operation (V<sub>DD</sub> = 2.3 to 5.5V at 4.4MHz).

- Pulse width measurement counter on chip (for remote control reception).

- 3) SIO provided for communication with the DSP.

- Seven-segment, four-common LCD controller / driver on chip.

- 5) All segments of the LCD controller / driver output can be switched to CMOS output using software.

# ● Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol          | Limits                     | Unit |

|-----------------------|-----------------|----------------------------|------|

| Power supply voltage  | V <sub>DD</sub> | <b>−</b> 0.3∼ <b>+</b> 7.0 | V    |

| Power dissipation     | Pd              | 500                        | mW   |

| Operating temperature | Topr            | <b>−25~+75</b>             | °    |

| Storage temperature   | Tstg            | <b>−55∼+125</b>            | ొ    |

### • Recommended operating conditions (Ta = 25°C)

| Parameter                                     | Symbol          | Min.               | Тур. | Max.                | Unit |

|-----------------------------------------------|-----------------|--------------------|------|---------------------|------|

| Power supply voltage                          | V <sub>DD</sub> | 2.3                | _    | 5.5                 | V    |

| Input high level voltage (without hysteresis) | ViH             | 0.7Vpb             | _    | VDD                 | V    |

| Input low level voltage (without hysteresis)  | VIL             | 0                  | _    | 0.3V <sub>DD</sub>  | V    |

| Input high level voltage (with hysteresis)    | Vins            | 0.7V <sub>DD</sub> | _    | VDD                 | V    |

| Input low level voltage (with hysteresis)     | Vils            | 0                  | _    | 0.25V <sub>DD</sub> | V    |

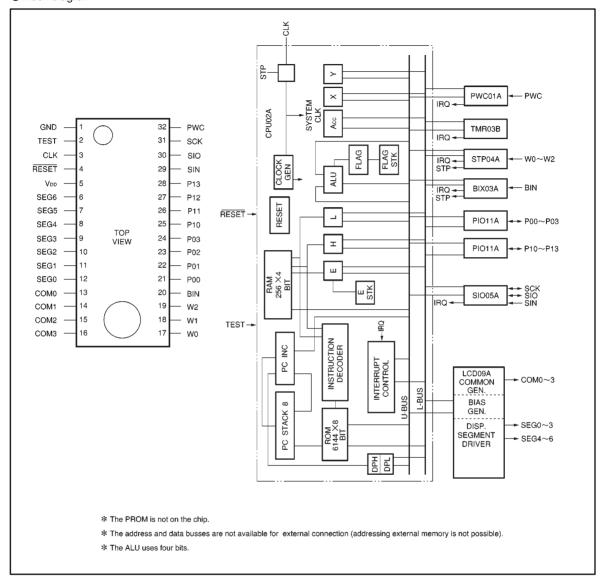

# Block diagram

# Pin descriptions

| Pin No.                          | Pin name           | 1/0 | Function                                                                                                                                                                                                                                                                           | Туре |  |  |

|----------------------------------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| 21~24<br>25~28<br>(PIO11A block) | P00~P03<br>P10~P13 | 1/0 | <ul> <li>4-bit input or output</li> <li>I/O bits can be set individually by program (output is N-ch open drain)</li> <li>Pull-up resistors can be switched on and off by program (setting possible for each bit)</li> <li>At reset, input turns off pull-up resistors*1</li> </ul> |      |  |  |

| 17~19<br>(STP04A block)          | W0~W2              | I   | General purpose 3-bit input With software, this can be used for STOP or HALT release input, or as interrupt request signal input (can be set for each bit) Pull-up resistors can be switched on and off by program (setting possible for each bit) At reset, pull-up resistors off | С    |  |  |

| 20<br>(BIX03A block)             | BIN                | ı   | General purpose 1-bit input With software this can be used for STOP or HALT release input, or as interrupt request signal input Pull-up resistors can be switched on and off by program At reset, pull-up resistors off                                                            | С    |  |  |

| 29                               | SIN                | 1   | 8-bit serial data input                                                                                                                                                                                                                                                            | Α    |  |  |

| 30                               | SIO                | 1/0 | 8-bit serial data I / O     I / O selectable by program                                                                                                                                                                                                                            | E    |  |  |

| 31<br>(SI005A block)             | SCK                | 1/0 | Clock I / O for serial data transmission/reception     Software can be used to select among three internal clocks and one external clock                                                                                                                                           | E    |  |  |

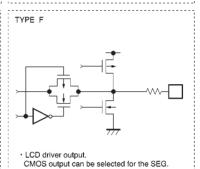

| 6~9<br>10~12                     | SEG6~3<br>SEG2~0   | 0   | Either LCD segment output and CMOS low current output can be selected by program (the upper three pins are for each segment, and the lower four pins are for setting all at once)     At reset, all revert to low-current CMOS output ("L" polarity is output)                     | F    |  |  |

| 13~16<br>(LCD09A block)          | COM0~<br>COM3      | 0   | LCD common output     COM3 is low-current CMOS output when 1/3 duty is selected                                                                                                                                                                                                    | F    |  |  |

| 32<br>(PWC01A block)             | PWC                | I   | Pulse input                                                                                                                                                                                                                                                                        | А    |  |  |

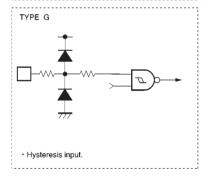

| 3                                | CLK                | 1   | External clock input                                                                                                                                                                                                                                                               | G    |  |  |

| 2                                | TEST               | ı   | Test input (the chip test pin has an internal pull-down resistor, and is to be left open normally)                                                                                                                                                                                 | В    |  |  |

| 4                                | RESET              | ı   | Reset input (set to "L" to reset the CPU)                                                                                                                                                                                                                                          | А    |  |  |

| 5                                | V <sub>DD</sub>    | _   | • Power supply                                                                                                                                                                                                                                                                     | _    |  |  |

| 1                                | GND                | _   | • Ground                                                                                                                                                                                                                                                                           | _    |  |  |

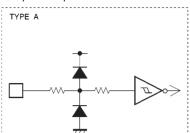

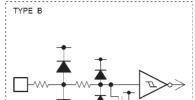

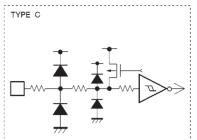

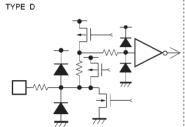

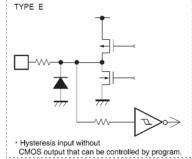

Format :Refer to the I / O circuit diagrams on the following page.

<sup>\*1</sup> The pins are in the high impedance state immediately after reset, so depending on the application, pin processing may be required.

# Input / output circuits

· Hysteresis input.

· Pull down resistor internal hysteresis input.

Hysteresis input that allows switching pull-up resistors on and off using a program.

Normal input/output that allows switching pull-up resistors on and off using a program and 6 has an N-ch open-drain output.

Optical disc ICs BU34675

●Electrical characteristics (unless otherwise noted, Ta = 25°C and V<sub>DD</sub> = 5V)

| Parameter                         | Symbol           | Pin                                                                         | Min. | Тур.           | Max. | Unit | Conditions                                                                                  |

|-----------------------------------|------------------|-----------------------------------------------------------------------------|------|----------------|------|------|---------------------------------------------------------------------------------------------|

| STOP circuit current              | IDDST            | _                                                                           | _    | _              | 1    | μΑ   | STOP mode                                                                                   |

| HALT circuit current              | Іррнт            | _                                                                           | _    | 700            | _    | μΑ   | HALT mode<br>fosc=4.4MHz                                                                    |

| Operation circuit current         | IDDOP            | _                                                                           | _    | 2              | _    | mA   | fosc=4.4MHz                                                                                 |

| Clock frequency                   | fosc             | CLK                                                                         | 2    | _              | 4.4  | MHz  | _                                                                                           |

| Input high level voltage 1        | V <sub>IH1</sub> | P00~P03, P10~P13                                                            | 3.5  | _              | _    | ٧    | When input                                                                                  |

| Input high level voltage 2        | V <sub>IH2</sub> | W0~W2, BIN, SIN,<br>SIO, SCK, PWC,<br>TEST, RESET                           | 3.75 | _              | _    | ٧    | Hysteresis input<br>When SIO and<br>SCK are input                                           |

| Input high level voltage 3        | VIH3             | CLK                                                                         | 3.9  | _              | _    | ٧    | _                                                                                           |

| Input low level voltage 1         | VIL1             | P00~P03, P10~P13                                                            | _    | _              | 1.5  | ٧    | When input                                                                                  |

| Input low level voltage 2         | VIL2             | W0~W2, BIN, SIN,<br>SIO, SCK, PWC,<br>TEST, RESET                           | _    | _              | 1.25 | ٧    | Hysteresis input<br>When SIO and<br>SCK are input                                           |

| Input low level voltage 3         | VIL3             | CLK                                                                         | _    | _              | 1.1  | ٧    | _                                                                                           |

| Input high level current 1        | liH1             | P00~P03, P10~P13,<br>W0~W2, BIN, SIN,<br>SIO, SCK, PWC,<br>RESET, CLK       | _    | _              | 1    | μΑ   | No pull-down resistor<br>Pxx, SIO, and<br>SCK are input<br>V <sub>IN</sub> =V <sub>DD</sub> |

| Input high level current 2        | I <sub>IH2</sub> | TEST                                                                        | 35   | 70             | 140  | μΑ   | Pull-down resistor<br>on chip<br>V <sub>IN</sub> =V <sub>DD</sub>                           |

| Input low level current 1         | lil.1            | P00~P03, P10~P13,<br>W0~W2, BIN, SIN,<br>SIO, SCK, PWC,<br>RESET, TEST, CLK | _    | _              | -1   | μA   | No pull-up resistor<br>Pxx, SIO, and<br>SCK are input<br>V <sub>IN</sub> =GND               |

| Input low level current 2         | lıL2             | P00~P03, P10~P13,<br>W0~W2, BIN                                             | -90  | -125<br>(40kΩ) | -160 | μΑ   | Pull-up resistor on chip V <sub>IN</sub> = GND                                              |

| Output high level voltage 1       | Vон1             | SIO, SCK                                                                    | 4.5  | _              | _    | v    | When SIO and SCK are output IOH=-500 μ A                                                    |

| Output high level voltage 2       | V <sub>OH2</sub> | SEG0~SEG6,<br>COM0~COM3                                                     | 4.5  | _              | _    | ٧    | Іон=-250 μ А                                                                                |

| Output low level voltage 1        | V <sub>OL1</sub> | P00~P03, P10~P13,<br>SIO, SCK                                               | _    | _              | 0.4  | V    | When Pxx, SIO and<br>SCK are output<br>loL=1.6mA                                            |

| Output low level voltage 2        | Vol2             | SEG0~SEG6,<br>COM0~COM3                                                     | _    | _              | 0.7  | ٧    | IoL=1.0mA                                                                                   |

| Output leak current               | lı.              | P00~P03, P10~P13                                                            | _    | _              | 1    | μΑ   | When Pxx is output high impedance                                                           |

| LCD 2 / 3 level<br>output voltage | V <sub>1</sub>   | COM0~COM3,<br>SEG0~SEG6                                                     | _    | 3.3            | _    | V    | _                                                                                           |

| LCD 1 / 3 level<br>output voltage | <b>V</b> 2       | COM0~COM3,<br>SEG0~SEG6                                                     | _    | 1.6            | _    | V    | _                                                                                           |

$<sup>\</sup>boldsymbol{*}$  One machine cycle requires 1 / 6 of the oscillator frequency.

●Electrical characteristics (unless otherwise noted, Ta = 25°C and V<sub>DD</sub> = 3V)

| Parameter                         | Symbol           | Pin                                                                         | Min. | Тур.           | Max.       | Unit | Conditions                                                                                  |  |

|-----------------------------------|------------------|-----------------------------------------------------------------------------|------|----------------|------------|------|---------------------------------------------------------------------------------------------|--|

| STOP circuit current              | Iddst            | _                                                                           |      |                | 1          | μΑ   | STOP mode                                                                                   |  |

| HALT circuit current              | IDDHT            | _                                                                           | _    | 200            | _          | μΑ   | HALT mode<br>fosc = 4.4MHz                                                                  |  |

| Operation circuit current         | IDDOP            | _                                                                           | _    | 0.7            | _          | mA   | fosc = 4.4MHz                                                                               |  |

| Clock frequency                   | fosc             | CLK                                                                         | 2    | _              | 4.4        | MHz  | _                                                                                           |  |

| Input high level voltage 1        | ViH1             | P00~P03, P10~P13                                                            | 2.1  | _              | _          | ٧    | When input                                                                                  |  |

| Input high level voltage 2        | V <sub>IH2</sub> | W0~W2, BIN, SIN,<br>SIO, SCK, PWC,<br>TEST, RESET                           | 2.25 | _              | _          | ٧    | Hysteresis input<br>When SIO and<br>SCK are input                                           |  |

| Input high level voltage 3        | VIH3             | CLK                                                                         | 2.4  | _              | _          | ٧    | _                                                                                           |  |

| Input low level voltage 1         | VIL1             | P00~P03, P10~P13                                                            | _    | _              | 0.9        | ٧    | When input                                                                                  |  |

| Input low level voltage 2         | V <sub>IL2</sub> | W0~W2, BIN, SIN,<br>SIO, S <u>CK, P</u> WC,<br>TEST, RESET                  | _    | _              | 0.75       | V    | Hysteresis input<br>When SIO and<br>SCK are input                                           |  |

| Input low level voltage 3         | V <sub>IL3</sub> | CLK                                                                         | _    | _              | 0.65       | ٧    | _                                                                                           |  |

| Input high level current 1        | Іінт             | P00~P03, P10~P13,<br>W0~W2, BIN, SIN,<br>SIO, SCK, PWC,<br>RESET, CLK       | _    | _              | 1          | μΑ   | No pull-down resistor<br>Pxx, SIO, and<br>SCK are input<br>V <sub>IN</sub> =V <sub>DD</sub> |  |

| Input high level current 2        | I <sub>IH2</sub> | TEST                                                                        | 10   | 20             | 35         | μΑ   | Pull-down resistor on chip V <sub>IN</sub> =V <sub>DD</sub>                                 |  |

| Input low level current 1         | lil1             | P00~P03, P10~P13,<br>W0~W2, BIN, SIN,<br>SIO, SCK, PWC,<br>RESET, TEST, CLK | _    | _              | <b>—</b> 1 | μA   | No pull-up resistor<br>Pxx, SIO, and<br>SCK are input<br>V <sub>IN</sub> =GND               |  |

| Input low level current 2         | lıl2             | P00~P03, P10~P13,<br>W0~W2, BIN                                             | -20  | -40<br>(125kΩ) | -60        | μΑ   | Pull-up resistor on chip<br>V <sub>IN</sub> =GND                                            |  |

| Output high level voltage 1       | Vон1             | SIO, SCK                                                                    | 2.5  | _              | _          | ٧    | When SIO and SCK are output IOH=-500 $\mu$ A                                                |  |

| Output high level voltage 2       | V <sub>OH2</sub> | SEG0~SEG6,<br>COM0~COM3                                                     | 2.5  | _              | _          | ٧    | Ioн=-250 μ A                                                                                |  |

| Output low level voltage 1        | V <sub>OL1</sub> | P00~P03, P10~P13,<br>SIO, SCK                                               | _    | _              | 0.6        | ٧    | When Pxx, SIO and SCK are output IoL=1.6mA                                                  |  |

| Output low level voltage 2        | V <sub>OL2</sub> | SEG0~SEG6,<br>COM0~COM3                                                     | _    | _              | 0.7        | V    | IoL=0.8mA                                                                                   |  |

| Output leak current               | lL               | P00~P03, P10~P13                                                            | _    | _              | 1          | μΑ   | When Pxx is output high impedance                                                           |  |

| LCD 2 / 3 level<br>output voltage | V <sub>1</sub>   | COM0~COM3,<br>SEG0~SEG6                                                     | _    | 2              | _          | v    | _                                                                                           |  |

| LCD 1 / 3 level<br>output voltage | V <sub>2</sub>   | COM0~COM3,<br>SEG0~SEG6                                                     | _    | 1              | -          | ٧    | _                                                                                           |  |

$<sup>\</sup>boldsymbol{*}$  One machine cycle requires 1 / 6 of the oscillator frequency.

Optical disc ICs BU34675

### Explanation of the hardware

(1) Operates of a single power supply ( $V_{DD} = 2.3$  to 5.5V).

(2) Memory size

ROM: 6144  $\times$  8 bits RAM: 256  $\times$  4 bits LCD display RAM : 7  $\times$  4 bits

(3) Instruction time (one cycle instruction)1.5μsec (at 4 MHz)

(4) Sub-routine nesting: ..... 8 levels

(5) Interrupts: 5

- (6) ROM data table function (6k data table region)

- (7) Two power save modes STOP / HALT

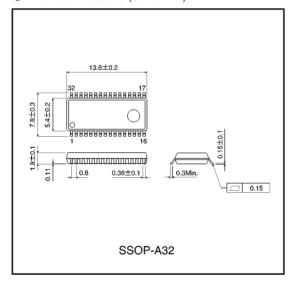

# External dimensions (Units: mm)

(8) On-chip 7-segment LCD driver that can drive a wide variety of display types

(9) LCD segment output can be switched to CMOS output by software.

The COM3 pin and upper three segments are one-bit units, and the lower four segments are all selected together. At reset, switches to CMOS low-current output port with low level polarity.

- (10) Remote control receiver circuit (pulse width measurement)

- (11) On-chip 8-bit timer counter

- (12) On-chip I / O system makes interfacing with external LSI easy (LSB first).

- (13) 8 I / O lines that can be pulled up by software

- (14) 4 input lines that can be pulled up by software