# CLD SERIES: CLOCK OSCILLATOR, LVDS, +3.3 VDC

DESCRIPTION: A crystal controlled, high frequency, highly stable oscillator, adhering to Low Voltage Differential Signaling (LVDS) Standards. The output can be Tri-stated to facilitate testing or combined multiple clocks. The device is contained in a sub-miniature, very low profile, leadless ceramic SMD package with 6 gold contact pads. This miniature oscillator is ideal for today's automated assembly environments.

### **APPLICATIONS AND FEATURES:**

- > Infiniband; 10GbE; Network Processors; SOHO Routing; Switches; WAN Interfaces

- > Common Frequencies: 106.25 MHz; 125 MHz; 150 MHz; 155.52 MHz; 156.25 MHz; 161.1328 MHz

- > +3.3 VDC LVDS

- > Frequency Range from 80 to 250 MHz

- Miniature Ceramic SMD Package Available on Tape and Reel

- > Lead Free

#### **■** ELECTRICAL PARAMETERS:

| PARAMETER                            | SYMBOL     | TEST CONDITIONS <sup>*1</sup>                      | VALUE                                    | UNIT       |

|--------------------------------------|------------|----------------------------------------------------|------------------------------------------|------------|

| Nominal Frequency                    | fo         |                                                    | 80.000 ~ 250.000                         | MHz        |

| Supply Voltage                       | Vcc        | +3.3 ±5%                                           |                                          | VDC        |

| Supply Current                       | ls         | 60.0 MAX                                           |                                          | mA         |

| Output Logic Type                    |            |                                                    | LVDS                                     |            |

| Load                                 |            | Connected between Out and Complementary Out        | 100                                      | Ω          |

| Output Voltage Levels                | Voh<br>Vol |                                                    | 1.43 TYP; 1.60 MAX<br>0.90 MIN; 1.10 TYP | VDC<br>VDC |

| Duty Cycle                           | DC         | Measured at 50% of Vcc                             | 40/60 to 60/40 or 45/55 to 55/45         | %          |

| Rise / Fall Time                     | tr / tf    | Measured at 20/80% and 80/20% Vcc Levels           | 1.0 TYP *2                               | ns         |

| Jitter                               | J          | RMS, Fj = 12 kHz20 MHz                             | 1 TYP                                    | ps         |

| Overall Frequency Stability          | Δf/fc      | Op. Temp., Aging, Load, Supply and Cal. Variations | ±25, ±50, or ±100 MAX <sup>3</sup>       | ppm        |

| Pin 1 Output Enabled Output Disabled | En<br>Dis  | High Voltage or No Connect<br>Ground               | 0.7•Vcc MIN<br>0.3•Vcc MAX               | VDC<br>VDC |

| Absolute voltage range               | Vcc(abs)   | Non-Destructive                                    | -0.5+7.0                                 | VDC        |

<sup>\*1</sup> Test Conditions Unless Stated Otherwise: Nominal Vcc, Nominal Load, +25 ±3°C

#### **■ ENVIRONMENTAL PARAMETERS:**

| PARAMETER                   | SYMBOL | TESTCONDITIONS*1 | VALUE                 | UNIT |

|-----------------------------|--------|------------------|-----------------------|------|

| Operating temperature range | Та     |                  | SEE PART NUMBER TABLE | °C   |

| Storage temperature range   | T(stg) |                  | -55+90                | °C   |

### **■ PART NUMBERING SYSTEM:**

| SERIES       | SYMMETRY           | TEMPERATURE<br>RANGE (°C) | FREQUENCY<br>STABILITY<br>(Overall) | FREQUENCY<br>(MHz) |

|--------------|--------------------|---------------------------|-------------------------------------|--------------------|

| CLD: Clock   | A: 40/60 to 60/40% | R: 0+50                   | I: ±25 ppm                          | 80.000250.000      |

| with LVDS    | T: 45/55 to 55/45% | S: 0+70                   | H: ±50 ppm                          |                    |

| Comp. Output |                    | U: -20+70                 | J: ±100 ppm                         |                    |

|              |                    | V: -40+85                 |                                     |                    |

#### **EXAMPLE: CLDPASH-155.520**

Clock Oscillator, 7x5mm Package,  $\pm 3.3$  VDC Supply Voltage, LVDS Output, Standard Symmetry,  $0...\pm 70^{\circ}$ C Operating Temperature Range,  $\pm 50$  ppm Total Frequency Stability, 155.520 MHz

<sup>\*2</sup> Frequency Dependent

<sup>\*3</sup> Not All Stabilities Available With All Temperature Ranges—Please Consult Factory For Availability

Please consult the factory for any custom requirements.

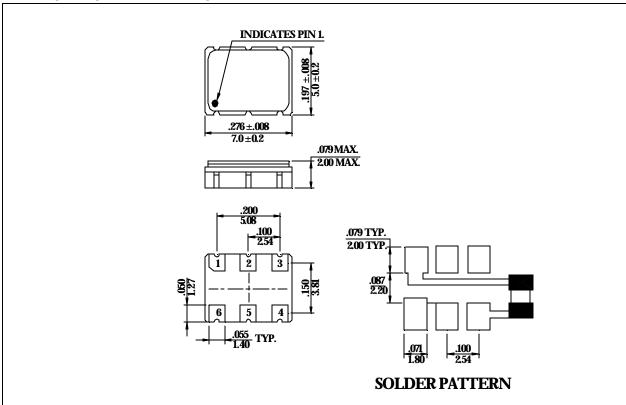

### **■ MECHANICAL PARAMETERS:**

# **OUTLINE TOLERANCE:**

±0.006" / 0.15mm

(Unless otherwise specified)

### PIN FUNCTIONS:

[1] ENABLE/ DISABLE

[2] NO CONNECT

[3] CASE GROUND

[4] OUTPUT

[5] COMP. OUTPUT

[6] SUPPLY VOLTAGE

## MARKING:

**CLDASH**

155.52

RAL D/C

# \*0.01mF external by-pass

filter is recommended as seen on solder pattern.