INTEGRATED CIRCUITS

Objective specification Supersedes data of 2002 Oct 16 2002 Oct 30

| CONTEN                                        | TS                                                                                                                                               | 17       | PACKAGE OUTLINE                                                                |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|

| 1                                             | FEATURES                                                                                                                                         | 18       | SOLDERING                                                                      |

| 2                                             | APPLICATIONS                                                                                                                                     | 18.1     | Introduction to soldering surface mount                                        |

| 3                                             | GENERAL DESCRIPTION                                                                                                                              | 18.2     | packages<br>Reflow soldering                                                   |

| 4                                             | QUICK REFERENCE DATA                                                                                                                             | 18.3     | Wave soldering                                                                 |

| 5                                             | ORDERING INFORMATION                                                                                                                             | 18.4     | Manual soldering                                                               |

| 6                                             | BLOCK DIAGRAM                                                                                                                                    | 18.5     | Suitability of surface mount IC packages for wave and reflow soldering methods |

| 7                                             | PINNING INFORMATION                                                                                                                              | 19       | DATA SHEET STATUS                                                              |

| 7.1<br>7.2<br>8                               | Pinning<br>Pin description<br>FUNCTIONAL DESCRIPTION                                                                                             | 20<br>21 | DEFINITIONS<br>DISCLAIMERS                                                     |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7 | RF receiver front-end and RF VCO<br>Channel filter and AGC<br>RF VCO<br>RF LO section<br>RF fractional-N synthesizer PLL<br>Clock PLL<br>Control |          |                                                                                |

| 9                                             | OPERATING MODES                                                                                                                                  |          |                                                                                |

| 9.1<br>9.2<br>9.3<br>9.4                      | Basic operating mode<br>AGC gain look-up table<br>RF PLL synthesizer<br>Clock PLL synthesizer                                                    |          |                                                                                |

| 10                                            | PROGRAMMING                                                                                                                                      |          |                                                                                |

| 10.1<br>10.2<br>10.3                          | Serial programming bus<br>Data format<br>Register contents                                                                                       |          |                                                                                |

| 11                                            | LIMITING VALUES                                                                                                                                  |          |                                                                                |

| 12                                            | THERMAL CHARACTERISTICS                                                                                                                          |          |                                                                                |

| 13                                            | DC CHARACTERISTICS                                                                                                                               |          |                                                                                |

| 14                                            | AC CHARACTERISTICS                                                                                                                               |          |                                                                                |

| 15                                            | SERIAL BUS TIMING CHARACTERISTICS                                                                                                                |          |                                                                                |

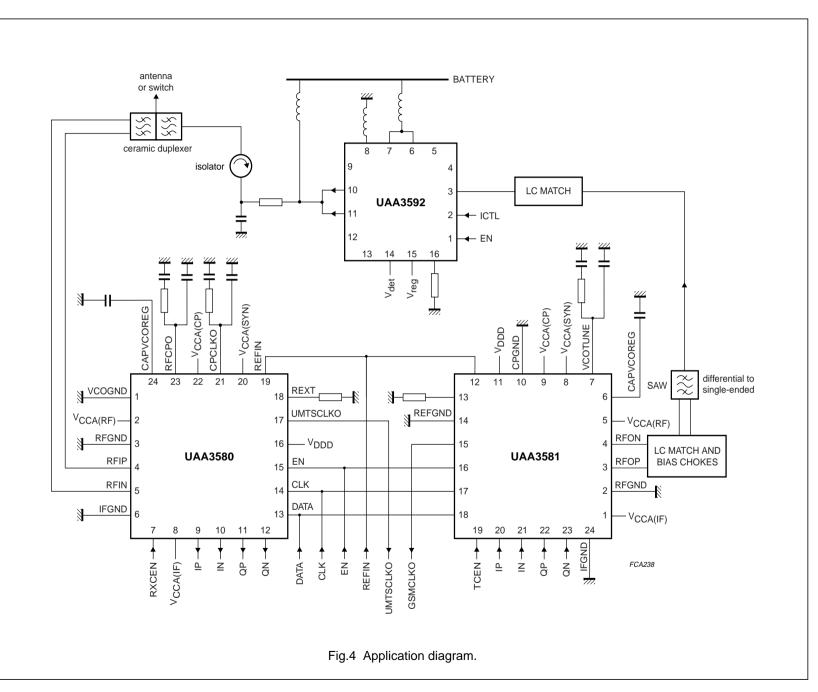

| 16                                            | APPLICATION INFORMATION                                                                                                                          |          |                                                                                |

## UAA3580

#### **1 FEATURES**

- Low noise wide dynamic range for zero IF receivers

- 79 dB gain control range; in steps of 1 dB

- Channel filters

- 96 dB voltage gain

- Fully integrated fractional-N synthesizer with AFC control capability

- Fully integrated RF VCO with integrated supply voltage regulator

- Fully differential design to minimize crosstalk

- Supply voltage from 2.4 to 3.3 V

- 3-wire serial interface bus

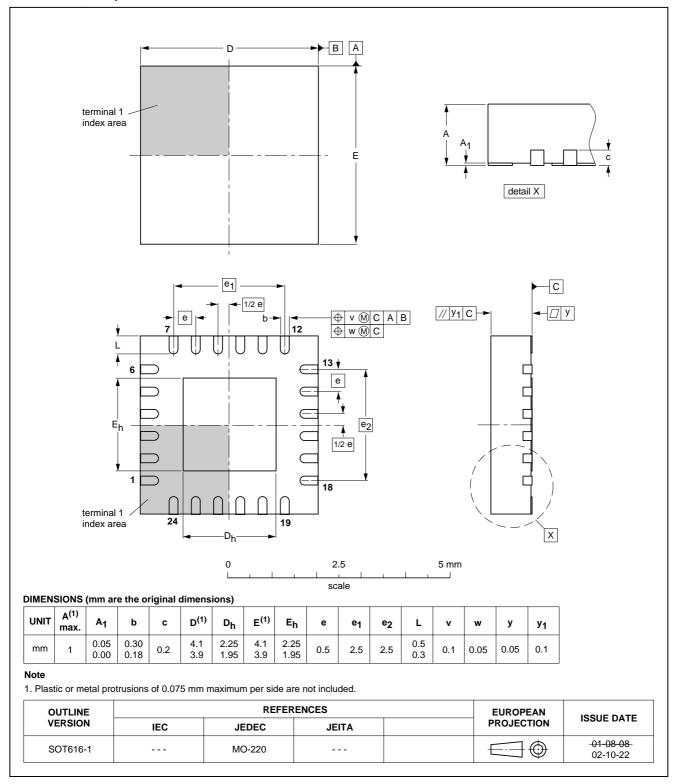

- HVQFN24 package.

#### 2 APPLICATIONS

- WCDM-FDD receiver for GSM hand-portable equipment

- Dual mode GSM/GPRS/EDGE/UMTS handset.

#### 4 QUICK REFERENCE DATA

#### **3 GENERAL DESCRIPTION**

The UAA3580 is a BiCMOS integrated circuit receiver intended for the Third Generation Partnership Project (3GPP) specification for the Universal Mobile Telecommunication System (UMTS).

The circuit is specially designed for the Frequency Division Duplex (FDD) mode of the Wide Code Division Multiple Access (WCDMA) that operates in the 2110 to 2170 MHz band.

The UAA3580 contains the whole analog receive chain from Radio Frequency (RF) Low Noise Amplifier (LNA) to baseband IQ outputs including a channel filter, a complete RF Phase-Locked Loop (PLL) with a fully integrated Voltage Controlled Oscillator (VCO), and a clock PLL that generates a programmable UMTS system clock from an external 26 MHz reference signal.

| SYMBOL           | PARAMETER              | MIN. | TYP. | MAX. | UNIT |

|------------------|------------------------|------|------|------|------|

| V <sub>CCA</sub> | analog supply voltage  | 2.6  | _    | 3.3  | V    |

| V <sub>DDD</sub> | digital supply voltage | 1.6  | _    | 2.8  | V    |

| T <sub>amb</sub> | ambient temperature    | -30  | _    | +70  | °C   |

#### **5 ORDERING INFORMATION**

| ТҮРЕ      |         | PACKAGE                                                                                                | VERSION  |  |  |  |  |  |

|-----------|---------|--------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| NUMBER    | NAME    | DESCRIPTION                                                                                            |          |  |  |  |  |  |

| UAA3580HN | HVQFN24 | plastic, heatsink very thin quad flat package; no leads 24 terminals; body $4 \times 4 \times 0.90$ mm | SOT616-1 |  |  |  |  |  |

UAA3580

# Wideband code division multiple access frequency division duplex zero IF receiver

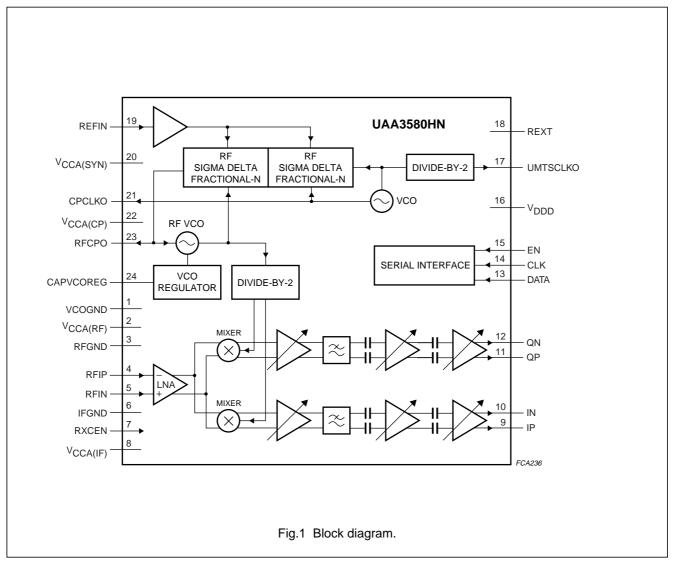

#### 6 BLOCK DIAGRAM

UAA3580

# Wideband code division multiple access frequency division duplex zero IF receiver

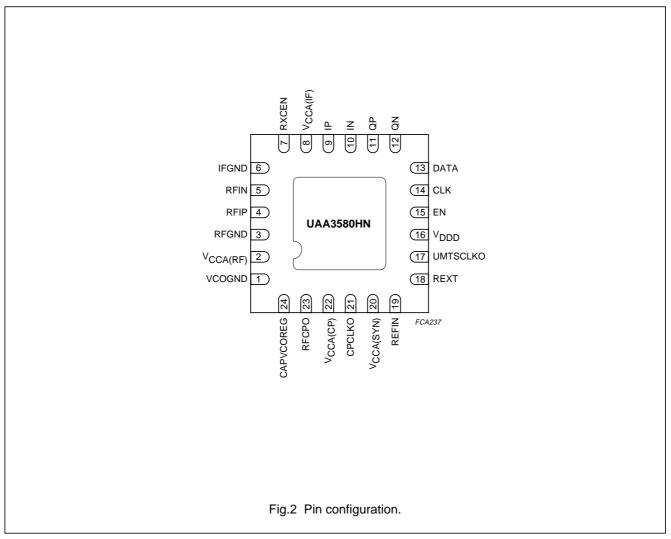

#### 7 PINNING INFORMATION

#### 7.1 Pinning

## UAA3580

#### 7.2 Pin description

#### Table 1 HVQFN24 package

| SYMBOL                | PIN     | DESCRIPTION                                                 |

|-----------------------|---------|-------------------------------------------------------------|

| VCOGND                | 1       | RF VCO ground                                               |

| V <sub>CCA(RF)</sub>  | 2       | analog supply voltage for the RF receiver                   |

| RFGND                 | 3       | RF receiver ground                                          |

| RFIP                  | 4       | RF positive input                                           |

| RFIN                  | 5       | RF negative input                                           |

| IFGND                 | 6       | IF section ground                                           |

| RXCEN                 | 7       | receiver chip enable input                                  |

| V <sub>CCA(IF)</sub>  | 8       | analog supply voltage for the IF section                    |

| IP                    | 9       | differential receive baseband positive in-phase output      |

| IN                    | 10      | differential receive baseband negative in-phase output      |

| QP                    | 11      | differential receive baseband positive in-quadrature output |

| QN                    | 12      | differential receive baseband negative in-quadrature output |

| DATA                  | 13      | serial bus data input                                       |

| CLK                   | 14      | serial bus clock input                                      |

| EN                    | 15      | serial bus enable input                                     |

| V <sub>DDD</sub>      | 16      | digital supply voltage                                      |

| UMTSCLKO              | 17      | UMTS system clock output                                    |

| REXT                  | 18      | external charge pump biasing resistor connection            |

| REFIN                 | 19      | reference clock input                                       |

| V <sub>CCA(SYN)</sub> | 20      | analog supply voltage for the synthesizer                   |

| CPCLKO                | 21      | charge pump clock output                                    |

| V <sub>CCA(CP)</sub>  | 22      | analog supply voltage for the charge pump section           |

| RFCPO                 | 23      | RF charge pump output                                       |

| CAPVCOREG             | 24      | decoupling capacitor for the VCO regulator                  |

|                       | die pad | ground                                                      |

#### 8 FUNCTIONAL DESCRIPTION

The receiver consists of an RF receiver front-end, an RF VCO, a channel filter, Automatic Gain Control (AGC), a RF fractional-N synthesizer PLL, a clock PLL, a Power-up reset circuit and a 3-wire serial programming bus.

#### 8.1 RF receiver front-end and RF VCO

The front-end receiver converts the aerial RF signal from WCMDA (2.11 to 2.17 GHz) band down to a Zero Intermediate Frequency (ZIF). The first stage is a differential low noise amplifier matched to 50  $\Omega$  using an external balun. The LNA is followed by an IQ down-mixer which consists of two mixers in parallel but driven by quadrature out-of-phase LO signals. The In phase (I) and Quadrature phase (Q) ZIF signals are then low-pass filtered, to provide protection from high frequency offset interference, and fed into the channel filter.

#### 8.2 Channel filter and AGC

The front-end zero IF I and Q outputs are applied to the integrated low-pass channel filter with a provision for  $4 \times 8$  dB gain steps in front of the filter. The filter is a self-calibrated fifth-order low-pass filter with a cut-off frequency around 2.4 MHz. Once filtered the zero IF I and Q outputs are further amplified with provision for  $47 \times 1$  dB steps and DC offset compensation. The zero IF output buffer provides close rail-to-rail output signal.

#### 8.3 RF VCO

The RF VCO is fully integrated and self-calibrated on manufacturing tolerances. It consists of 16 different frequency ranges that are selected internally, depending on the frequency programmation. It covers the necessary bandwidth of 4.22 to 4.34 GHz and is tuned via the RF charge pump and external loop filter. An internal supply voltage regulator using the pin CAPVCOREG as external decoupling capacitor supplies the RF VCO and minimizes parasitic coupling and pushing. The regulator and the RF VCO are turned on by the RXCEN signal.

#### 8.4 RF LO section

The RF LO section covering the 4.22 to 4.34 GHz band is driven by the internal RF VCO module. It includes the LO buffering for the RF PLL and a divide-by-two circuit to generate the quadrature LO signals to drive the RX IQ down-mixer.

#### 8.5 RF fractional-N synthesizer PLL

A high performance RF fractional-N synthesizer PLL is included on-chip which enables the frequency of the RF VCO to be synthesized. The frequency is set via the 3-wire serial programming bus.

The PLL is based on Sigma-Delta ( $\Sigma\Delta$ ) fractional-N synthesis that enables the required channel frequency, including Automatic Frequency Control (AFC) from a free running external 26 MHz GSM reference frequency, to be obtained. Very low close in-phase noise is achieved which allows a wider PLL loop bandwidth and a shorter settling time. The programmable main dividers are controlled by a second-order ( $\Sigma\Delta$ ) modulus controller. They divide the RF VCO signals down to frequencies of 26 MHz (in programmable 12 Hz steps). Their phase is then compared in a digital Phase/Frequency Detector (PFD) to the 26 MHz reference clock signal. The phase error information is fed back to the RF VCO via the charge pump circuit that 'sources' into or 'sinks' current from the loop filter capacitor, thus changing the VCO frequency so that the loop is finally brought into phase-lock.

The RF synthesizer division range enables an external reference frequency of 13 to 26 MHz to be used.

#### 8.6 Clock PLL

The clock PLL is based on SD fractional-N synthesis that allows the UMTS system clock, including AFC from a non-corrected external 26 MHz GSM reference frequency, to be obtained. The PLL comprises a fully integrated RC VCO. The PLL output is a low harmonic content waveform, the frequency of which can be programmed to 15.36, 30.72 or 61.44 MHz. The default value is 30.72 MHz.

#### 8.7 Control

The control of the chip is done via the 3-wire serial bus and pin RXCEN. At power-up the clock PLL section is automatically enabled, the other sections are enabled when the RXCEN signal is set HIGH (also via the 3-wire bus). The power-up signal is detected on pin  $V_{DDD}$  when the voltage rises. The  $V_{DDD}$  pin, if the supply voltage is maintained, enables the programming parameters to be retained in memory.

#### 9 OPERATING MODES

#### 9.1 Basic operating modes

The circuit can be powered up into different operating modes, depending on the control bits RXON and SYNON, via the 3-wire bus. This defines three main modes called IDLE, SYN and RX mode.

The voltage level applied to pin RXCEN must be set HIGH to enable the device. The VCO and the PLL sections are enabled in SYN mode. In the RX mode every section is enabled (receive part, VCO and PLL sections).

#### Table 2 Selection of operating mode

| MODE | SYNON | RXON |

|------|-------|------|

| IDLE | 0     | 0    |

| SYN  | 1     | 0    |

| RX   | 1     | 1    |

#### 9.2 AGC gain look-up table

The AGC gain is set via the AGC[8:0] bits; see Table 3.

| Table 3 | AGC gain look-up table |

|---------|------------------------|

|---------|------------------------|

| AGC8 | AGC7 | AGC6 | AGC5 | AGC4 | AGC3 | AGC2 | AGC1 | AGC0 | ATTENUATION FROM<br>MAXIMUM GAIN (dB) |

|------|------|------|------|------|------|------|------|------|---------------------------------------|

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0                                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1                                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 2                                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 3                                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 4                                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 5                                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 6                                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 7                                     |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 8                                     |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 9                                     |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 10                                    |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 11                                    |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 12                                    |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 13                                    |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 14                                    |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 15                                    |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 16                                    |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 17                                    |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 18                                    |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 19                                    |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 20                                    |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 21                                    |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 22                                    |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 23                                    |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 24                                    |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 25                                    |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 26                                    |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 27                                    |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 28                                    |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 29                                    |

| AGC8 | AGC7 | AGC6 | AGC5 | AGC4 | AGC3 | AGC2 | AGC1 | AGC0 | ATTENUATION FROM<br>MAXIMUM GAIN (dB) |

|------|------|------|------|------|------|------|------|------|---------------------------------------|

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 30                                    |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 31                                    |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 32                                    |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 33                                    |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 34                                    |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 35                                    |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 36                                    |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 37                                    |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 38                                    |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 39                                    |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 40                                    |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 41                                    |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 42                                    |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 43                                    |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 44                                    |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 45                                    |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 46                                    |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 47                                    |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 48                                    |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 49                                    |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 50                                    |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 51                                    |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 52                                    |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 53                                    |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 54                                    |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 55                                    |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 56                                    |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 57                                    |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 58                                    |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 59                                    |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 60                                    |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 61                                    |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 62                                    |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 63                                    |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 64                                    |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 65                                    |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 66                                    |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 67                                    |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 68                                    |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 69                                    |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 70                                    |

The AGC[8:0] code required to program the AGC attenuation (AGC<sub>att</sub>) can be calculated from the following formulas:

$$\begin{split} & AGC[8:0] = (511 - AGC_{att})_B \text{ if } 0 < AGC_{att} < 11 \\ & AGC[8:0] = (391 - AGC_{att})_B \text{ if } 12 < AGC_{att} < 19 \\ & AGC[8:0] = (271 - AGC_{att})_B \text{ if } 20 < AGC_{att} < 27 \\ & AGC[8:0] = (151 - AGC_{att})_B \text{ if } 28 < AGC_{att} < 35 \\ & AGC[8:0] = (95 - AGC_{att})_B \text{ if } 36 < AGC_{att} < 43 \\ & AGC[8:0] = (151 - AGC_{att})_B \text{ if } 44 < AGC_{att} < 51 \\ & AGC[8:0] = (95 - AGC_{att})_B \text{ if } 52 < AGC_{att} < 59 \\ & AGC[8:0] = (135 - AGC_{att})_B \text{ if } 60 < AGC_{att} < 67 \\ & AGC[8:0] = (79 - AGC_{att})_B \text{ if } 68 < AGC_{att} < 79 \end{split}$$

Where  $(X)_B$  is the binary code of the integer X.

#### 9.3 RF PLL synthesizer

The RF fractional-N synthesizer is set via the 3-wire bus with the FRAC and CH chains. CH sets the integer divider ratio and FRAC the fractional divider ratio. They both provide the LO frequency in accordance with the following equation:

$$\begin{split} f_{RFLO} \ &= \ f_{ref} \times \left( \frac{N_{RX}}{2} + K_{frac(RX)} \right) \\ \text{Where} \ K_{frac(RX)} \ &= \ \frac{1}{2^{22}} \times \left( K_{RX} + \frac{1}{2} \right) \end{split}$$

Where  $K_{RX}$  is the integer value of FRAC[21:0],  $N_{RX}$  is the integer value of CH[8:0] and  $f_{ref}$  is the external frequency reference applied to pin REFIN.

**Example**: to obtain a  $f_{RFLO}$  frequency of 2.14 GHz with an error less than  $\Delta f_{PLL} N_{RX}$  must be set to 164 and  $K_{frac(RX)}$  to 1290555 if the reference frequency is 26 MHz. It should be noted that some particular frequencies can be obtained in two ways;  $N_{RX} = x$  and  $K_{frac(RX)} = 0.25$  provides the same frequency as  $N_{RX} = x - 1$  and  $K_{frac(RX)} = 0.75$

#### 9.4 Clock PLL synthesizer

#### 9.4.1 AFC MODE

The clock PLL is based on the SD fractional-N synthesizer that allows to derive the UMTS system clock including AFC from a non-corrected external 26 MHz only GMS reference. The clock PLL frequency with the AFC correction word is given by the following equation:

$$f_{CLKPLL} = f_{ref} \times \left(\frac{9 + K_{AFC}}{2}\right)$$

Where  $K_{AFC} = \frac{231}{512} + \frac{AFC}{2^{21}}$

AFC represents the integer value of AFC[11:0] and  $f_{ref}$  is the external reference frequency applied to pin REFIN.

#### 9.4.2 CLOCK PLL MODES

The clock PLL synthesizer is controlled by bits CLKon and CLKoff. At power-up the clock PLL synthesizer is automatically on when pin RXCEN is set HIGH. The control, done with CLKon, will be reset at the rising edge of RXCEN. For application which do not require the UMTS clock system, the clock PLL can be powered-down with bit CLKoff set to logic 1.

#### Table 4 Clock mode

| RXCEN            | CLKon            | CLKoff | DESCRIPTION                             |

|------------------|------------------|--------|-----------------------------------------|

| 1                | 1                | 0      | CLKPLL synthesizer<br>enabled (default) |

| 0                | 1                | 0      | CLKPLL synthesizer<br>disabled; note 1  |

| 1                | 0                | 0      | CLKPLL synthesizer<br>disabled; note 2  |

| X <sup>(4)</sup> | X <sup>(4)</sup> | 1      | CLKPLL synthesizer<br>disabled; note 3  |

#### Notes

- 1. Hard power-down of the clock PLL done with RXCEN.

- 2. Power-down achieved via the 3-wire bus, reset by RXCEN.

- 3. Power-down achieved via the 3-wire bus, no effect by RXCEN in this mode. This mode will be reset if  $V_{DDD}$  is not maintained.

- 4. X = don't care.

#### 9.4.3 CLOCK PLL OUTPUT DIVIDER

The clock PLL output divider ratio is set in accordance with Table 5.

| Table 5 | Clock mode; note 1 |

|---------|--------------------|

|---------|--------------------|

| CLKoff | CLK1 | CLK0 | DESCRIPTION                        |

|--------|------|------|------------------------------------|

| 1      | Х    | Х    | UMTSCLKO output<br>disabled        |

| 0      | 0    | 0    | clock divider ratio set to default |

| 0      | 0    | 1    | clock divider ratio set to 2       |

| 0      | 1    | 0    | clock divider ratio set to 4       |

| 0      | 1    | 1    | clock divider ratio set to 8       |

#### Note

```

1. X = don't care.

```

#### 10 PROGRAMMING

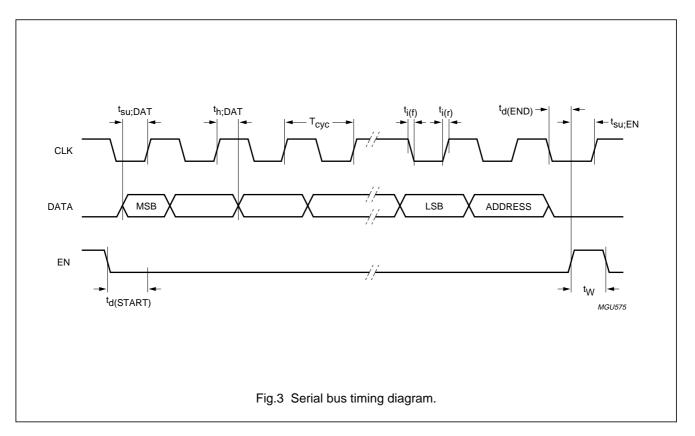

#### 10.1 Serial programming bus

A simple 3-wire unidirectional serial bus is used to program the circuit. The 3 lines are DATA, CLK and EN.

The data sent to the device is loaded in bursts framed by EN. Programming clock edges are ignored until EN goes active LOW. The programmed information is loaded into the addressed latch when EN goes HIGH (inactive). This is allowed when CLK is in either state without causing any consequences to the data register. Only the last 21 bits serially clocked into the device are retained within the programming register. Additional leading bits are ignored, and no check is made on the number of clock pulses.

The fully static CMOS design uses virtually no current when the bus is inactive. It can always capture new programming data even during Power-down of the synthesizer.

#### 10.2 Data format

Data is entered with the most significant bit first. The leading bits make up the data field, while the trailing four bits are an address field. The address bits are decoded on the rising edge of EN. This produces an internal load pulse to store the data in the address latch.

To ensure that data is correctly loaded on first power-up, EN should be held LOW and only taken HIGH after having programmed an appropriate register. To avoid erroneous divider ratios, the pulse is inhibited during the period when data is read by the frequency dividers. This condition is guaranteed by respecting a minimum EN pulse width after data transfer.

#### 10.3 Register contents

#### Table 6 Register bit allocation

| CONTROL BITS |                                                                                                        |       |       |          |        |                                                                                                                      |         |        |       |        |        | ADDRESS |           |         |           |       |   |   |   |   |

|--------------|--------------------------------------------------------------------------------------------------------|-------|-------|----------|--------|----------------------------------------------------------------------------------------------------------------------|---------|--------|-------|--------|--------|---------|-----------|---------|-----------|-------|---|---|---|---|

| 20           | 19                                                                                                     | 18    | 17    | 16       | 15     | 14         13         12         11         10         9         8         7         6         5         4         3 |         |        |       |        |        |         |           | 3       | 2         | 1     | 0 |   |   |   |

| for te       | for test purposes only; all bits must be set to zero for normal operation; this is a forbidden address |       |       |          |        |                                                                                                                      |         |        |       |        |        | 0       | 0         | 0       | 0         |       |   |   |   |   |

| for te       | est pu                                                                                                 | rpose | s onl | y; all b | oits m | ust be                                                                                                               | e set f | to zer | o for | norma  | al ope | ratior  | i; this i | s a for | bidden ad | dress | 0 | 0 | 0 | 1 |

|              |                                                                                                        |       |       |          |        |                                                                                                                      | FR      | AC[1   | 5:0]  |        |        |         |           |         |           | SYNON | 0 | 1 | 0 | 0 |

|              |                                                                                                        |       | C     | CH[8:0   | )]     |                                                                                                                      |         |        |       |        | FR[    | 21:16   | ]         |         | 1         | SYNON | 0 | 1 | 0 | 1 |

| 0            | 0                                                                                                      | 0     | 0     | 0        |        | AGC[8:0]                                                                                                             |         |        |       |        |        |         |           | 1       | 1         | RXON  | 0 | 1 | 1 | 0 |

| 0            | 0 AFC[11:0]                                                                                            |       |       |          |        |                                                                                                                      |         | CKO[   | 1:0]  | CLKoff | CLKon  | 0       | 1         | 1       | 1         |       |   |   |   |   |

#### Table 7 Description of symbols used in Table 6

| SYMBOL | BITS | DESCRIPTION                                   |

|--------|------|-----------------------------------------------|

| SYNON  | 1    | 3-wire bus                                    |

| RXON   | 1    | 3-wire bus                                    |

| AGC    | 9    | automatic gain control                        |

| СН     | 6    | integer division ratio for the RF PLL         |

| FRAC   | 22   | fractional division ratio for the RF PLL      |

| AFC    | 12   | automatic frequency control for the clock PLL |

| CLKoff | 1    | clock PLL disabled                            |

| СКО    | 2    | integer division ratio for the clock PLL      |

## UAA3580

#### Table 8 Register preset condition

|    | CONTROL |    |    |    |    |    |    | ADD | RESS |    |   |   |   |   |   |   |   |   |   |   |

|----|---------|----|----|----|----|----|----|-----|------|----|---|---|---|---|---|---|---|---|---|---|

| 20 | 19      | 18 | 17 | 16 | 15 | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0  | 0       | 0  | 0  | 0  | 1  | 1  | 1  | 1   | 1    | 1  | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| 0  | 1       | 0  | 0  | 1  | 0  | 1  | 0  | 0   | 1    | 1  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

#### **11 LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL           | PARAMETER               | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|------------------|-------------------------|------------|------|------|------|------|

| V <sub>DDD</sub> | digital supply voltage  |            | -0.3 | -    | +2.8 | V    |

| V <sub>CCA</sub> | analog supply voltage   |            | -0.3 | _    | +3.3 | V    |

| P <sub>tot</sub> | total power dissipation |            | _    | _    | 300  | mW   |

| T <sub>amb</sub> | ambient temperature     |            | -30  | _    | +80  | °C   |

| T <sub>stg</sub> | storage temperature     |            | -40  | -    | +150 | °C   |

#### **12 THERMAL CHARACTERISTICS**

| SYMBOL               | PARAMETER                                   | CONDITIONS                                                      | VALUE | UNIT |

|----------------------|---------------------------------------------|-----------------------------------------------------------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air; on a 4 layer PCB and with soldered exposed die pad | 36    | K/W  |

## UAA3580

#### 13 DC CHARACTERISTICS

$V_{CCA}$  = 2.6 V;  $V_{CCA(CP)}$  = 2.6 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL                   | PARAMETER                                    | CONDITIONS                                                                   | MIN. | TYP. | MAX. |    |

|--------------------------|----------------------------------------------|------------------------------------------------------------------------------|------|------|------|----|

| Supplies                 | -                                            |                                                                              |      |      |      | •  |

| V <sub>CCA</sub>         | analog supply voltage                        | on pins $V_{CCA(RF)}$ , $V_{CCA(IF)}$ , $V_{CCA(CP)}$ and $V_{CCA(SYN)}$     | 2.6  | 2.8  | 3.3  | V  |

| V <sub>DDD</sub>         | digital supply voltage                       |                                                                              | 1.6  | 1.8  | 2.8  | V  |

| I <sub>CCA(tot)</sub>    | total analog supply current                  | receive mode; note 1                                                         | _    | 52   | 63   | mA |

|                          |                                              | receive mode; note 2                                                         | _    | 45   | 54   | mA |

|                          |                                              | synthesizer mode; note 3                                                     | _    | 25   | 30   | mA |

|                          |                                              | standby mode; note 4                                                         | -    | 12   | 15   | mA |

|                          |                                              | sleep mode; note 5                                                           | -    | 10   | 50   | μA |

| I <sub>CCA(RF)</sub>     | analog supply current for the RF VCO section |                                                                              | -    | 19   | -    | mA |

| I <sub>CCA(IF)</sub>     | analog supply current for the RX section     |                                                                              | -    | 16   | -    | mA |

| I <sub>CCA(SYN)</sub>    | analog supply current for the synthesizer    |                                                                              | -    | 15   | -    | mA |

| I <sub>CCA(CP)</sub>     | analog supply current for the charge pump    |                                                                              | -    | 0.9  | -    | mA |

| I <sub>DDD</sub>         | digital supply current                       |                                                                              | -    | 1.1  | -    | mA |

| Baseband IQ              | section; pins IN, IP, QP and QN              |                                                                              |      |      |      |    |

| V <sub>O(IQ)(CM)</sub>   | IQ common mode output voltage                | $0.5(V_{IN} + V_{IP}) \text{ or}$<br>$0.5(V_{QP} + V_{QN}); \text{ note } 6$ | 1.15 | 1.25 | 1.35 | V  |

| RF VCO secti             | on; pin CAPVCOREG                            | ·                                                                            | L.   |      |      | •  |

| V <sub>O(CAPVCOREG</sub> | ) output voltage                             |                                                                              | -    | 2    | -    | V  |

| CLKPLL sect              | ion; pin UMTSCLKO                            | ·                                                                            | L    | •    |      | •  |

| V <sub>O(UMTSCLKO)</sub> | output voltage                               |                                                                              | -    | 0.8  | -    | V  |

| Reference vo             | Itage; pin REXT                              |                                                                              |      | •    |      | •  |

| V <sub>REXT</sub>        | reference voltage for the charge pump        | $R_{ext} = 1.8 \ k\Omega$                                                    | -    | 360  | -    | mV |

| Control section          | on; pins DATA, CLK, EN and RXON              |                                                                              |      |      | -    |    |

| V <sub>IH</sub>          | HIGH-level input voltage                     |                                                                              | 0.9  | -    | -    | V  |

| V <sub>IL</sub>          | LOW-level input voltage                      |                                                                              | _    | -    | 0.3  | V  |

#### Notes

- 1. Receive mode: All circuits are active.

- 2. Receive mode: All circuits are active with the clock PLL off (CLKoff = 1).

- 3. Synthesizer mode: RF PLL and clock PLL are active.

- 4. Standby mode: Clock PLL is active.

- 5. Sleep mode: RXCEN set LOW, DATA, CLK and EN are in high-impedance.

- 6. Receive mode: DC voltage supplied from the IC.

## UAA3580

#### 14 AC CHARACTERISTICS

$V_{CCA}$  = 2.6 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL                    | PARAMETER                                        | CONDITIONS                                                                                                                                   | MIN. | TYP. | MAX. | UNIT   |

|---------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| RF receiver in            | nputs; pins RFIN and RFIP                        |                                                                                                                                              | •    | •    |      |        |

| f <sub>i(RF)</sub>        | RF input frequency                               |                                                                                                                                              | 2.11 | -    | 2.17 | GHz    |

| R <sub>i</sub>            | input resistance                                 |                                                                                                                                              | _    | 170  | _    | Ω      |

| Ci                        | input capacitance                                |                                                                                                                                              | _    | 1    | _    | pF     |

| S <sub>11</sub>           | input power matching                             | with external balun                                                                                                                          | _    | -10  | -    | dB     |

| F                         | noise figure                                     | in receive mode with maximum gain                                                                                                            | -    | 3.2  | 4    | dB     |

| CP <sub>1</sub>           | 1 dB compression point                           | in receive mode with maximum gain                                                                                                            | -23  | -20  | -    | dBm    |

| IP <sub>3</sub>           | input referred 3rd-order<br>intercept point      | in receive mode with<br>maximum gain;<br>interference 20 MHz<br>away from channel<br>bandwidth                                               | -18  | -15  | -    | dBm    |

| IP <sub>2</sub>           | input referred 2nd-order<br>intercept point      | in receive mode with<br>maximum gain;<br>interferers 190 MHz away<br>from channel bandwidth                                                  | 37   | 42   | -    | dBm    |

| φ <sub>n</sub>            | phase noise                                      | at 15 MHz offset                                                                                                                             | _    | -    | -135 | dBc/Hz |

| Baseband IQ               | section; pins IP, IN, QP and QI                  | N                                                                                                                                            |      | •    | ·    | ·      |

| G <sub>v(max)</sub>       | maximum voltage gain                             |                                                                                                                                              | 92   | 96   | 100  | dB     |

| G <sub>v(min)</sub>       | minimum voltage gain                             |                                                                                                                                              | 12   | 17   | 22   | dB     |

| AGC <sub>tot</sub>        | total AGC range                                  |                                                                                                                                              | _    | 79   | -    | dB     |

| G <sub>step(AGC)</sub>    | AGC gain step                                    |                                                                                                                                              | _    | 1    | _    | dB     |

| AGC <sub>tot(lin)</sub>   | total AGC linearity                              |                                                                                                                                              | -0.5 | -    | +0.5 | dB     |

| $\Delta G_{v(IQ)}$        | voltage gain mismatch between the I and Q paths  |                                                                                                                                              | -    | -    | 0.5  | dB     |

| $\Delta \Phi$             | quadrature phase error between the I and Q paths | peak error                                                                                                                                   | -    | -    | 5    | deg    |

| V <sub>o(max)</sub>       | maximum output voltage per pin                   | $ \begin{array}{l} R_{L(diff)} = 10 \; k\Omega; \\ THD < 3\% \end{array} $                                                                   | 0.75 | -    | -    | V      |

| I <sub>o(max)</sub>       | maximum output current per<br>pin                | $\label{eq:volume} \begin{array}{l} V_{o(p-p)} = 1.75 \text{ V at 1 MHz}; \\ R_{L(diff)} = 10  k\Omega; \\ C_{L(diff)} = 20  pF \end{array}$ | 650  | -    | -    | μΑ     |

| V <sub>offset(diff)</sub> | differential output offset voltage               |                                                                                                                                              | -20  | -    | +20  | mV     |

| HP <sub>-3dB</sub>        | -3 dB high-pass corner<br>frequency              | 2nd-order high-pass<br>frequency                                                                                                             | 10   | 15   | 20   | kHz    |

| LP <sub>-3dB</sub>        | -3 dB low-pass corner<br>frequency               | 5th-order low-pass frequency                                                                                                                 | 2.25 | 2.4  | 2.55 | MHz    |

| $\Delta d_{(g)}$          | group delay variation                            | 100 kHz < f <sub>o</sub> < 2 MHz                                                                                                             | -    | 260  | _    | ns     |

|                                                                                                                                                                                                                                                                                        | PARAMETER                                                                                                                                                                                                                                                                                                                                                | CONDITIONS                                                                                                                                                                                                                            | MIN.                                                            | TYP.                                                      | MAX.                                                                                   | UNIT                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| α <sub>LPF</sub>                                                                                                                                                                                                                                                                       | LPF attenuation                                                                                                                                                                                                                                                                                                                                          | f <sub>i</sub> = 5 MHz                                                                                                                                                                                                                | 39                                                              | 42                                                        | _                                                                                      | dB                                                                       |

|                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                          | f <sub>i</sub> = 10 MHz                                                                                                                                                                                                               | 72                                                              | 75                                                        | -                                                                                      | dB                                                                       |

|                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                          | f <sub>i</sub> = 15 to 60 MHz                                                                                                                                                                                                         | 91                                                              | 94                                                        | _                                                                                      | dB                                                                       |

| RF synthesiz                                                                                                                                                                                                                                                                           | er; pin RFCPO                                                                                                                                                                                                                                                                                                                                            | l                                                                                                                                                                                                                                     |                                                                 |                                                           |                                                                                        | -1                                                                       |

| f <sub>RFLO</sub>                                                                                                                                                                                                                                                                      | synthesizer frequency                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                       | 2.11                                                            | _                                                         | 2.17                                                                                   | GHz                                                                      |

| f <sub>comp(RF)</sub>                                                                                                                                                                                                                                                                  | RF comparison frequency                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                       | _                                                               | 26                                                        | _                                                                                      | MHz                                                                      |

| Δf <sub>PLL</sub>                                                                                                                                                                                                                                                                      | frequency resolution                                                                                                                                                                                                                                                                                                                                     | f <sub>comp</sub> = 13 to 26 MHz                                                                                                                                                                                                      | 0.05                                                            | _                                                         | _                                                                                      | ppm                                                                      |

|                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                          | f <sub>comp</sub> = 26 MHz                                                                                                                                                                                                            | -                                                               | -                                                         | 6.2                                                                                    | Hz                                                                       |

| $\Phi_{\sf n}$                                                                                                                                                                                                                                                                         | close-in-phase noise                                                                                                                                                                                                                                                                                                                                     | at 2 kHz offset                                                                                                                                                                                                                       | -                                                               | -85                                                       | -80                                                                                    | dBc/Hz                                                                   |

| l <sub>sink</sub>                                                                                                                                                                                                                                                                      | sink current                                                                                                                                                                                                                                                                                                                                             | R <sub>ext</sub> = 1.8 kΩ; THD = 1%                                                                                                                                                                                                   | 170                                                             | 200                                                       | 230                                                                                    | μA                                                                       |

| I <sub>source</sub>                                                                                                                                                                                                                                                                    | source current                                                                                                                                                                                                                                                                                                                                           | R <sub>ext</sub> = 1.8 kΩ; THD = 1%                                                                                                                                                                                                   | 170                                                             | 200                                                       | 230                                                                                    | μA                                                                       |

| V <sub>o(CP)</sub>                                                                                                                                                                                                                                                                     | charge pump output voltage                                                                                                                                                                                                                                                                                                                               | charge pump current<br>within specified range                                                                                                                                                                                         | 0.4                                                             | -                                                         | V <sub>CCA</sub> - 0.4                                                                 | V                                                                        |

| KΦ                                                                                                                                                                                                                                                                                     | PFD gain                                                                                                                                                                                                                                                                                                                                                 | R <sub>ext</sub> = 1.8 kΩ; THD = 1%                                                                                                                                                                                                   | 27                                                              | 32                                                        | 37                                                                                     | μA/rad                                                                   |

| I <sub>leak(CP)</sub>                                                                                                                                                                                                                                                                  | charge pump leakage current in off state                                                                                                                                                                                                                                                                                                                 | over full charge pump<br>voltage range                                                                                                                                                                                                | -1                                                              | _                                                         | +1                                                                                     | μA                                                                       |

| Ν                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                       |                                                                 |                                                           |                                                                                        |                                                                          |

|                                                                                                                                                                                                                                                                                        | integer divider ratio                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                       | 130                                                             | -                                                         | 507                                                                                    |                                                                          |

| K <sub>frac</sub>                                                                                                                                                                                                                                                                      | fractional divider ratio                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                       | 0.25                                                            | -                                                         | 0.75                                                                                   |                                                                          |

| K <sub>frac</sub>                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                       |                                                                 | -<br> -                                                   | _                                                                                      |                                                                          |

| K <sub>frac</sub><br>Integrated RF                                                                                                                                                                                                                                                     | fractional divider ratio                                                                                                                                                                                                                                                                                                                                 | $V_{RFCPO} = 0$ to 3.3 V                                                                                                                                                                                                              |                                                                 | -<br>-                                                    | _                                                                                      | GHz                                                                      |

| K <sub>frac</sub><br>Integrated RF<br>f <sub>RF</sub><br>G <sub>VCO</sub>                                                                                                                                                                                                              | fractional divider ratio                                                                                                                                                                                                                                                                                                                                 | V <sub>RFCPO</sub> = 0 to 3.3 V<br>V <sub>RFCPO</sub> = 1.3 V                                                                                                                                                                         | 0.25                                                            |                                                           | 0.75                                                                                   | -                                                                        |

| K <sub>frac</sub><br>Integrated RF<br>f <sub>RF</sub><br>G <sub>VCO</sub>                                                                                                                                                                                                              | fractional divider ratio VCO; pin RFCPO RF frequency                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                       | 0.25<br>4.22                                                    | _                                                         | 0.75<br>4.34                                                                           | -                                                                        |

| K <sub>frac</sub><br>Integrated RF<br>f <sub>RF</sub><br>G <sub>VCO</sub>                                                                                                                                                                                                              | fractional divider ratio         VCO; pin RFCPO         RF frequency         VCO gain                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                       | 0.25<br>4.22<br>50                                              | _                                                         | 0.75<br>4.34<br>90                                                                     | MHz/V<br>V                                                               |

| K <sub>frac</sub><br>Integrated RF<br>f <sub>RF</sub><br>G <sub>VCO</sub><br>V <sub>tune</sub>                                                                                                                                                                                         | fractional divider ratio         VCO; pin RFCPO         RF frequency         VCO gain         tuning voltage                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                       | 0.25<br>4.22<br>50<br>0.4                                       | -<br>70<br>-                                              | 0.75<br>4.34<br>90<br>V <sub>CCA</sub> - 0.4                                           | MHz/V<br>V                                                               |