# SMART HotPlug<sup>™</sup> IC/Inrush Limiter/Circuit Breaker

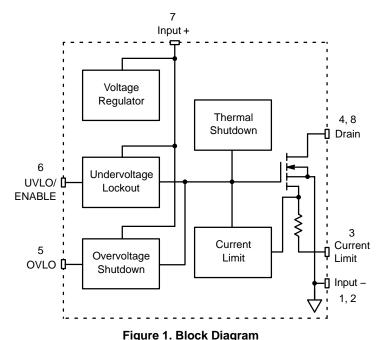

The SMART HotPlug Integrated Circuit combines the control function and power FET into a single IC that saves design time and reduces the number of components required for a complete hot swap application. It is designed to allow safe insertion and removal of electronic equipment to -48 V backplanes. This chip features simplicity of use combined with an integrated solution.

The SMART HotPlug includes user selectable undervoltage and overvoltage lockout levels. It also has adjustable current limiting that can be reduced from the maximum level with a single resistor. Operation at the maximum current level requires no extra external components. An internal temperature shutdown circuit greatly increases the reliability of this device.

#### **Features**

- Integrated Power Device

- 100 V Operation

- Thermal Limit Protection

- Adjustable Current Limit

- No External Current Shunt Required

- Undervoltage and Overvoltage Lockouts

- 6.5 A Continuous Operation

- UIS Rated

#### **Typical Applications**

- VoIP (Voice over Internet Protocol) Servers

- -48 V Telecom Systems

- +24 V Wireless Base Station Power

- Central Office Switching

- Electronic Circuit Breaker

# ON Semiconductor®

http://onsemi.com

#### MARKING DIAGRAM

S-PAK EX SUFFIX CASE 553AA

= 1 for Thermal Latch or

2 for Thermal Auto-retry

A = Assembly Location

Y = Year

WW = Work Week

#### **ORDERING INFORMATION**

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| NIS5101E1T1 | S-PAK<br>Latch Off  | 2000 Units/Reel       |

| NIS5101E2T1 | S-PAK<br>Auto-Retry | 2000 Units/Reel       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### PIN FUNCTION DESCRIPTION

| Pin  | Symbol        | Description                                                                                                                                                                                                     |

|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2 | Input –       | Negative input voltage to the device. This is used as the internal reference for the IC.                                                                                                                        |

| 3    | Current Limit | This pin is shorted to the Input – pin for maximum current limit setting. If a reduced current limit level is desired, a series resistor is added between this pin and the Input – pin.                         |

| 4, 8 | Drain         | Drain of power FET, which is also the switching node for the load.                                                                                                                                              |

| 5    | OVLO          | The overvoltage shutdown point is programmed by a resistor from this pin to the Input + supply.                                                                                                                 |

| 6    | UVLO/ENABLE   | A resistor from Input + to the UVLO pin adjusts the voltage at which the device will turn on. An open drain device can be connected to this pin, which will inhibit operation, when in its low impedance state. |

| 7    | Input +       | Positive input voltage to the device.                                                                                                                                                                           |

#### **MAXIMUM RATINGS**

| Rating                                                                                                | Symbol                     | Value                      | Unit |

|-------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|------|

| Input Voltage, Operating (Input + to Input –) Transient (1 second) Steady–State                       | V <sub>in</sub>            | -0.3 to 110<br>-0.3 to 100 | V    |

| Drain Voltage, Operating (Drain to Input –) Transient (1 second) Steady–State                         | V <sub>DD</sub>            | -0.3 to 110<br>-0.3 to 100 | V    |

| Drain Current, Continuous (T <sub>A</sub> = 25°C, 2.0 in <sup>2</sup> Cu, double–sided board, 1 oz.)  | I <sub>Davg</sub>          | 6.5                        | А    |

| Operating Temperature Range                                                                           | Tj                         | -40 to 145                 | °C   |

| Non–Operating Temperature Range                                                                       | Tj                         | -55 to 175                 | °C   |

| Lead Temperature, Soldering (10 Seconds)                                                              | T <sub>L</sub>             | 260                        | °C   |

| Drain Current, Peak (Internally Limited)                                                              | I <sub>pk</sub>            | 20                         | А    |

| Thermal Resistance, Junction–to–Air 0.5 in <sup>2</sup> copper 1.0 in <sup>2</sup> copper             | $R_{	heta JA}$             | 75<br>43                   | °C/W |

| Power Dissipation @ T <sub>A</sub> = 25°C<br>0.5 in <sup>2</sup> copper<br>1.0 in <sup>2</sup> copper | P <sub>max</sub>           | 1.4<br>2.4                 | W    |

| ESD Immunity for Device Handling (All Pins)                                                           | HBM<br>JESD22-A114-B       | 2.0                        | kV   |

| ESD Immunity Board Level (Note 1)                                                                     | IEC 61000-4-2<br>(Level 3) | 6.0                        | kV   |

| Lightning, Surge (8 x 20 μsec) (Note 1)                                                               | IEC 61000-4-5              | 2.0                        | kV   |

|                                                                                                       | (Level 3)                  | 48                         | А    |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

1. Applied between Input + and Input – pins only, and using an external 68 V bi–directional TVS device (P6SMB68AT3) connected across these

# **ELECTRICAL CHARACTERISTICS** ( $T_j = 25^{\circ}C$ unless otherwise noted.)

| Characteristic                                                                                               | Symbol              | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------|---------------------|------|-----|------|------|

| POWER FET                                                                                                    | •                   | •    | •   | •    | •    |

| Charging Time (Turn-On to Rated Max Current)                                                                 | t <sub>chg</sub>    | _    | 5.0 | _    | ms   |

| ON Resistance                                                                                                | R <sub>DSon</sub>   | _    | 43  | 50   | mΩ   |

| Zero Gate Voltage Drain Current $(V_{DS} = 100 V_{dc}, V_{GS} = 0 V_{dc})$                                   | I <sub>DSS</sub>    | -    | 10  | -    | μА   |

| Sense Voltage Tolerance (V <sub>input</sub> = 48 V, RextI <sub>LIMIT</sub> = 20 Ω)                           | V <sub>Sense</sub>  | -    | 3.0 | -    | %    |

| Output Capacitance (V <sub>DS</sub> = 48 V <sub>dc</sub> , V <sub>GS</sub> = 0 V <sub>dc</sub> , f = 10 kHz) | -                   | -    | 326 | -    | pF   |

| THERMAL LIMIT                                                                                                |                     |      |     |      | •    |

| Shutdown Junction Temperature (Note 4)                                                                       | T <sub>SD</sub>     | 125  | 135 | 145  | °C   |

| Hysteresis (Note 4)                                                                                          | T <sub>hyst</sub>   | 35   | 40  | 45   | °C   |

| OVER/UNDERVOLTAGE                                                                                            | •                   |      |     | •    | •    |

| Turn–On Voltage (Rext <sub>UVLO</sub> = ∞)                                                                   | V <sub>on</sub>     | 41.5 | 46  | 50.5 | V    |

| Hysteresis (Rext <sub>UVLO</sub> = ∞)                                                                        | V <sub>hyst</sub>   | 6.3  | 8.0 | 9.7  | V    |

| Turn–On Voltage (Rext <sub>UVLO</sub> = 270 kΩ)                                                              | V <sub>on</sub>     | 29   | 33  | 37   | V    |

| Hysteresis (Rext <sub>UVLO</sub> = 270 kΩ)                                                                   | V <sub>hyst</sub>   | 3.5  | 5.0 | 6.5  | V    |

| Zener Voltage (UVLO Pin Voltage at Turn-On)                                                                  | V <sub>Z</sub>      | 14.3 | 16  | 17.5 | V    |

| OVLO Threshold (Input + Increasing, Rext <sub>OVLO</sub> = ∞)                                                | V <sub>OV</sub>     | 100  | -   | -    | V    |

| OVLO Threshold (Input + Increasing, Rext <sub>OVLO</sub> = 300 k $\Omega$ )                                  | V <sub>OV</sub>     | 65   | 74  | 83   | V    |

| OVLO Hysteresis (Input + Decreasing, Rext <sub>OVLO</sub> = 300 kΩ)                                          | V <sub>OVhyst</sub> | 3.0  | 4.7 | 6.4  | V    |

| CURRENT LIMIT                                                                                                |                     |      |     |      | •    |

| Short Circuit Current Limit (RextI <sub>LIMIT</sub> = 20 Ω) (Note 5)                                         | I <sub>LIM1</sub>   | 3.5  | 4.2 | 5.0  | Α    |

| Overload Current Limit (Rextl <sub>LIMIT</sub> = 20 Ω) (Notes 4 and 5)                                       | I <sub>LIM2</sub>   | 5.4  | 6.0 | 6.6  | Α    |

| TOTAL DEVICE                                                                                                 | •                   | •    |     | •    | •    |

| Bias Current (Operational) (V <sub>input</sub> = 48 V, R <sub>UVLO</sub> = ∞)                                | I <sub>Bias</sub>   | _    | 1.4 | _    | mA   |

| Bias Current (Non–Operational) (V <sub>input</sub> = 30 V, R <sub>UVLO</sub> = ∞)                            | I <sub>Bias</sub>   | _    | 800 | -    | μΑ   |

| Minimum Operating Voltage ( $R_{UVLO} = 30 \text{ k}\Omega$ )                                                | Vin <sub>min</sub>  | _    | 18  | -    | V    |

| 1                                                                                                            | L                   |      | ·   |      |      |

Pulse Test: Pulse width 300 μs, duty cycle 2%.

Switching characteristics are independent of operating junction temperatures.

Verified by design.

Please refer to explanation about the device's current limit operation in short circuit and overload conditions.

#### TYPICAL PERFORMANCE CURVES

(T<sub>A</sub> = 25°C unless otherwise noted)

45 Turn-On -40°C Turn-On 25°C 40 Turn-On 120°C UVLO TRIP POINT (V) 35 30 25 20 Turn-Off 25°C Turn-Off 120°C 15 10 100 1000 UVLO\_ $R_{ext}$  (k $\Omega$ )

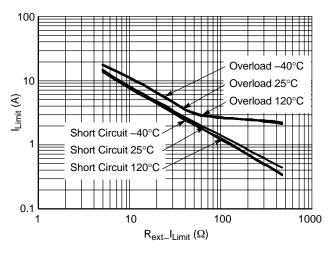

Figure 2. Current Limit Adjustment

(For Main/Mirror MOSFET Current Ratio explanation, see page 11)

Figure 3. UVLO Adjustment

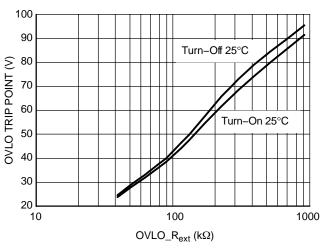

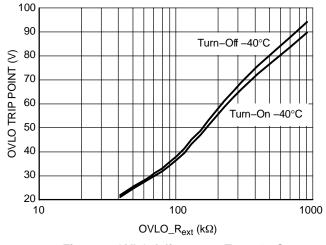

Figure 4. OVLO Adjustment,  $T_J = 25^{\circ}C$

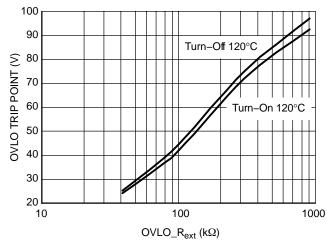

Figure 5. OVLO Adjustment,  $T_J = 120^{\circ}C$

Figure 6. OVLO Adjustment,  $T_J = -40^{\circ}C$

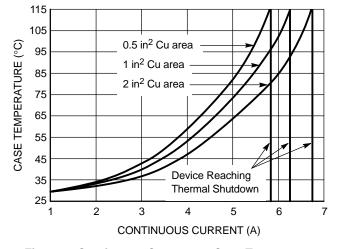

Figure 7. Continuous Current vs. Case Temperature (Test performed on a double sided copper board, 1 oz)

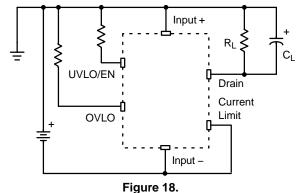

# **TYPICAL APPLICATION CIRCUIT & OPERATION WAVEFORMS**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

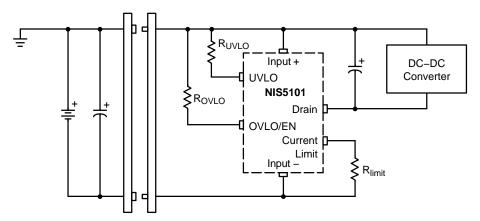

Figure 8. Typical Application

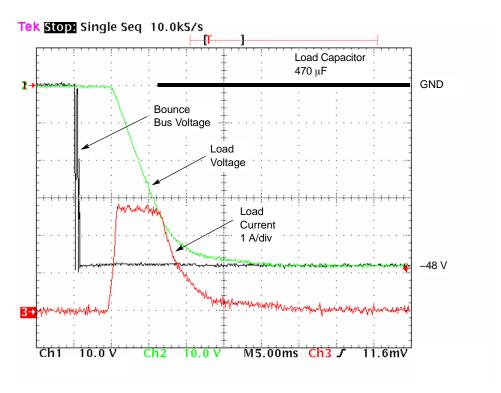

Figure 9. Turn On Waveforms for 470  $\mu F$  Load Capacitor

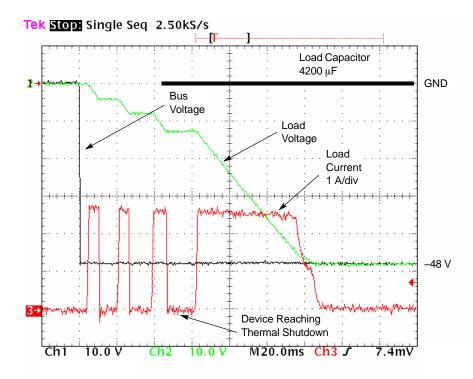

Figure 10. Typical Operation Waveforms of the Auto-Retry Device

Figure 11. Typical Operation Waveforms of the Latch Off Device

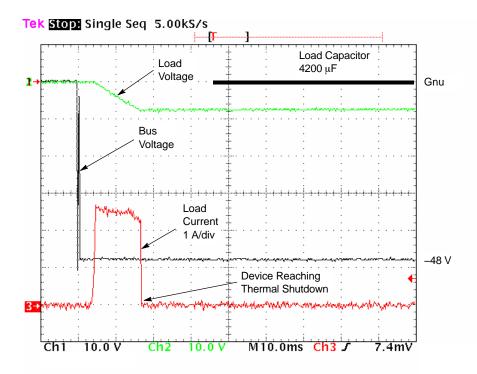

# ADDITIONAL APPLICATION CIRCUITS FOR DIFFERENT FUNCTIONS

Figure 14. Increased Delay Time Circuit

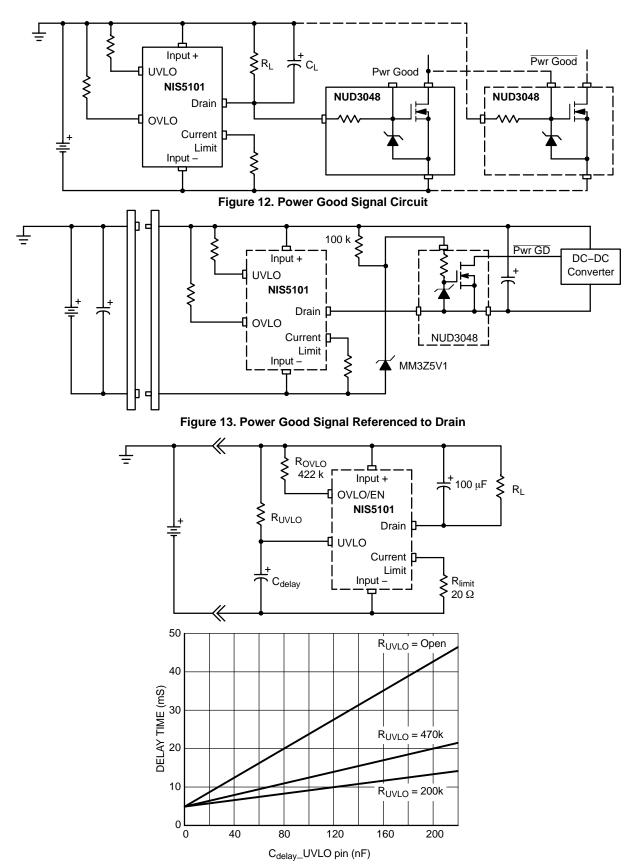

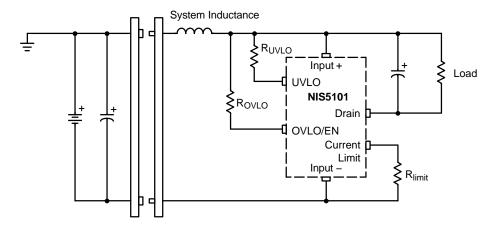

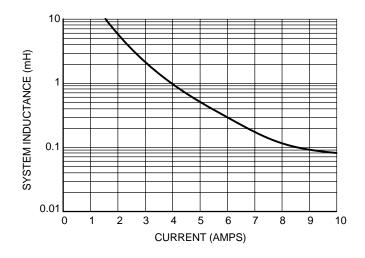

# TYPICAL DEVICE PERFORMANCE FOR DIFFERENT SYSTEM INDUCTANCE VALUES

Figure 15. System Inductance Test Circuit

Figure 16. Total System Inductance vs. Current

#### **OPERATION DESCRIPTION**

#### Turn-on

The SMART HotPlug monitors the input voltage by sensing the voltage across the Input + to Input – pins. When the UVLO voltage has been reached, the internal circuitry slowly charges the gate of the internal SENSEFET<sup>TM</sup>. There will be a slight delay of several milliseconds before the SENSEFET begins conduction. This may be increased by adding a capacitor to the UVLO pin. For a discussion of this, see application note AND8115/D.

The SENSEFET will increase the load current with a controlled di/dt until the current limit level has been reached. At this point the SENSEFET will enter a constant current mode of operation until the load capacitor has been fully charged. If the thermal limit threshold is reached before the capacitor reaches its final charge level, the device will shut down until the die temperature reaches 95°C and then restart, if it is the auto—retry device. The thermal latching version must not be allowed to reach the thermal shutdown level at turn—on as this will cause it to latch in an off state.

During the capacitor charging period, the dv/dt of the capacitor is:

$$dv/dt = \frac{ILIMIT}{CLOAD}$$

#### **Faults**

Once the load capacitance is charged, the SENSEFET will become fully enhanced as long as the current does not reach the current limit threshold, or is shut—down due to an overvoltage, undervoltage or thermal fault. Both the UVLO and OVLO circuits incorporate hysteresis to assure clean turn—on and turn—offs with no chatter. The thermal latching circuit will require the input power to be recycled to resume operation after a fault. The current limit is always active, so any transient or overload will always be limited.

# **Circuit Description**

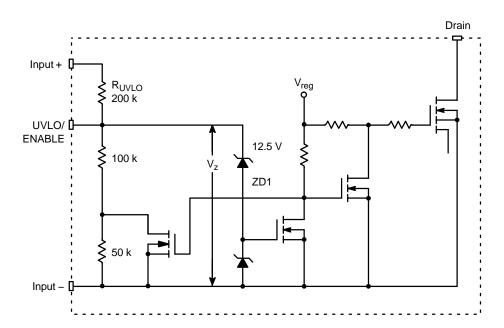

Undervoltage Lockout: The UVLO circuit holds the chip off when the input voltage is less than the turn—on limit. It includes internal hysteresis to assure clean on/off switching. An internal divider sets the turn—on voltage level at 46 V. This voltage can be reduced by adding an external resistor from the UVLO pin to the Input + pin. The equivalent circuit is shown in Figure 17.

Figure 17. Undervoltage Lockout Circuit

The theoretical equation for the UVLO turn-on voltage is:

$$R_{UVLO} (k\Omega) = \frac{215 \text{ V}_{in} - 2970}{46.8 - \text{V}_{in}}$$

where  $R_{UVLO}$  is in  $k\Omega$ .

Where  $V_{in}$  is the desired turn-on voltage, and  $R_{UVLO}$  is the programming resistance from the UVLO pin to the Input + pin.

The UVLO trip point voltage calculated through the theoretical formula may show small variations with respect to Figure 3, therefore it is recommended to use the formulas gotten from the UVLO characterization, which are shown below:

$$\begin{split} R_{UVLO}\left(k\Omega\right) &= e^{\left[(y+4.4706)\,/\,6.4484\right]}; \ for \ T_J = 25^{\circ}C \\ R_{UVLO}\left(k\Omega\right) &= e^{\left[(y+4.6185)\,/\,6.8525\right]}; \ for \ T_J = 120^{\circ}C \\ R_{UVLO}\left(k\Omega\right) &= e^{\left[(y+5.7642)\,/\,6.7234\right]}; \ for \ T_J = -40^{\circ}C \\ where \ "y" \ is \ the \ desired \ UVLO \ value. \end{split}$$

To reduce nuisance tripping due to transients and noise spikes, a capacitor may be added from the UVLO pin to the Input – pin. This will create a low pass filter with a cutoff frequency of f. The required capacitance on this pin is:

$$C = \frac{1}{2\pi \cdot f \left[150 \ k + \left(\frac{R_{UVLO} \cdot 200 \ k}{R_{UVLO} + 200 \ k}\right)\right]}$$

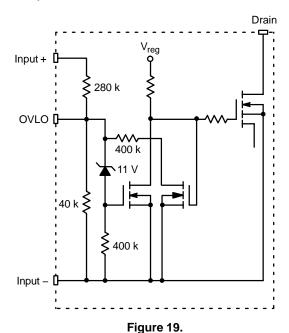

Overvoltage Lockout: The overvoltage shutdown circuit is an optional protection feature that can be disabled by simply grounding the OVLO pin.

This circuit contains an internal Zener diode/resistor combination in series with the gate of a FET. When the input + to input - voltage reaches a level sufficient to apply the required gate voltage to the FET, operation of the SMART HotPlug will be inhibited. There is a hysteresis circuit built in that will eliminate on/off bursts due to noise on the input.

The equation for the OVLO trip point is:

$$R_{OVLO} (k\Omega) = \frac{290 \text{ V}_{in} - 3200}{113.7 - \text{V}_{in}}$$

Where  $R_{OVLO}$  is the overvoltage programming resistor from the OVLO pin to Input +, and  $V_{in}$  is the desired trip point for the overvoltage shutdown to occur.

The OVLO trip point voltage calculated through the theoretical formula may show small variations with respect to Figures 4, 5 and 6, therefore it is recommended to use the formulas gotten from the OVLO characterization, which are shown below:

$$\begin{split} R_{OVLO} \left( k\Omega \right) &= e^{\left[ (y+69.6) \, / \, 24.82 \right]}; \text{ for } T_J = 25^{\circ} C \\ R_{OVLO} \left( k\Omega \right) &= e^{\left[ (y+60.56) \, / \, 23.27 \right]}; \text{ for } T_J = 120^{\circ} C \\ R_{OVLO} \left( k\Omega \right) &= e^{\left[ (y+66.47) \, / \, 23.52 \right]}; \text{ for } T_J = -40^{\circ} C \end{split}$$

where "y" is the desired OVLO value.

Similar to the undervoltage lockout circuit, the noise sensitivity of this circuit can be reduced by adding a capacitor from the OVLO pin to Input –. The capacitor required for the desired pole frequency is:

$$C_{OVLO} = \frac{(1 + 31.3 \cdot 10^{-6} \cdot R_{OVLO})}{2\pi f \cdot R_{OVLO}}$$

Temperature Limit: The temperature limit circuit senses the temperature of the Power FET and removes the gate drive if the maximum level is exceeded. There is a nominal hysteresis of 40°C for this circuit. After a thermal shutdown, the device will automatically restart when the temperature drops to a safe level as determined by the hysteresis.

Current Limit: The SMART HotPlug uses a SENSEFET to measure the Drain Current. The behavior of the SENSEFET in a short circuit condition varies from that in an overload because there is sufficient voltage across the drain to source terminals for the sense current to follow the ratio of the sense cells to main FET cells. This is not the case when the device is fully enhanced, since there are only a few millivolts from drain to source. In this condition, the sense voltage follows a different set of equations.

An overload condition is one in which the FET is fully enhanced and operating at it's minimum  $R_{DSon}$ . A short circuit condition occurs when either the load has shorted or upon turn on, as the load capacitor to the hot swap device initially looks like a short circuit.

A single resistor will determine both the short circuit and overload current. For example, a 110  $\Omega$  resistor would result in a 1 A current limit when charging the capacitance at turn on, but once the FET is fully enhanced, it would allow the load to operate at a current up to 2.5 A. Once the 2.5 A limit is reached, any further reduction in load impedance will result in a short circuit condition and the current will be reduced to 1 amp.

As with all SMART HotPlug devices, the current limit will never shut down the limiter. Only the thermal limit will stop the flow of current to the load. Once the current is stopped due to the thermal limit, it will remain off until input power is recycled for the latching version, or it will continuously retry to start again if it is the auto—retry version.

The  $I_{Limit}$  graph shown in Figure 2 was generated from the data of the  $I_{Limit}$  characterization, the formulas for each of the curves and temperatures are shown below:

$$R_{ILimit}(\Omega) = (56.55 / y)^{1.20}$$

; for  $T_J = 25C$

$$R_{ILimit}(\Omega) = (52.91 / y)^{1.22}$$

; for  $T_J = 120^{\circ}C$

$$R_{IL,imit}(\Omega) = (44.80 / y)^{1.33}$$

; for  $T_J = -40^{\circ}C$

where "y" is the desired ILimit value.

*Main/Mirror MOSFET Current Ratio*. The ratio varies with current and sense resistance. The key parameter that

it is important to know is that the current sense reference voltage of the device is 50 mV. Knowing this information, it is possible to use Figure 2 on the datasheet for the current limit to calculate the ratio for any condition.

For "normal" operating condition, the overload curve would apply. If a 100  $\Omega$  for the  $I_{Limit}$  resistor is used, the sense current would be 50 mV/ 100  $\Omega$  at the current limit level, which results in 500  $\mu$ A. The drain current is 2.7 A under this condition, so the ratio is 5400:1.

Same analysis can be made for "short circuit" conditions, the only difference is that the short circuit curve of Figure 2 is used to do the ratio calculations instead.

There is a 5  $\Omega$  resistor in series with the sense cells. This has a tolerance of about 10% and should be taken into account when making the above calculations.

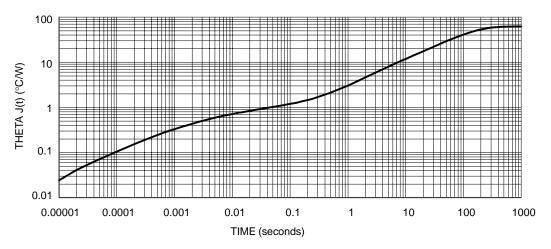

Turn-onSurge: During the turn-on event, there is a large amount of energy dissipated due to the linear operation of the power device. The energy rating is the amount of energy that the device can absorb before the thermal limit circuit will shut the unit down. This is very important specially for the latch off device as it determines the maximum load capacitance that the device can charge before the thermal limit shuts the device down. The calculation of this is not very simple as it depends on several factors such as the input voltage  $(V_{in})$ , load capacitance  $(C_L)$ , current limit settings  $(I_{Limit})$  and device's thermal transient response. Figure 20 shows the device's thermal transient response for minimum pad.

Figure 20. Thermal Transient Response

The device junction temperature  $(T_j)$  for turn-on surge conditions can be calculated by knowing the thermal transient resistance of a given pulse duration.

$$\begin{split} T_j &= T_A + [P_D \; x \; R_{\theta J(t)}], \text{ and} \\ R_{\theta J(t)} &= (T_i - T_A)/P_D \end{split}$$

where:

T<sub>i</sub> is the device junction temperature

TA is the ambient temperature

P<sub>D</sub> is the power dissipation of the device

$R_{\theta J(t)}$  is the value from Figure 20

In order to obtain the thermal transient resistance value  $R_{\theta J(t)}$ , it is necessary to calculate the charging time of a given load capacitance ( $C_L$ ), the following equation is used for these purposes:

$$i = C dV/dt$$

; then,

$t = (C_L/I_{Limit}) \times V_{in}$

where:

C<sub>L</sub> is the total load capacitance

I<sub>Limit</sub> is the current limit value

Vin is the input voltage

By calculating the charging time, the thermal transient resistance is then given by Figure 20. And finally the device junction temperature  $(T_j)$  for turn—on surge conditions is calculated. If the calculated  $T_j$  does not exceed 135°C, then the thermal limit circuit is most likely to not shut the unit down.

To better illustrate this theoretical methodology, an example is explained:

For the following conditions,

$$T_A = 25^{\circ}C$$

$$V_{in} = 48 \text{ V}$$

$$I_{Limit} = 2.0 A$$

What is the maximum load capacitance that the NIS5101 device can charge before the thermal limit circuit shuts the unit down?

If:

$$R_{\theta J(t)} = (T_i - T_A)/P_D$$

$$R_{\theta J(t)} = (135^{\circ}C - 25^{\circ}C)/(48 \text{ V x } 2.0 \text{ A})$$

$$R_{\theta J(t)} = 1.1$$

From Figure 20:

$R_{\theta J(t)} = 1.1$  corresponds to 80 msec

Then:

$$t = (C_L/I_{Limit}) \ x \ V_{in}$$

$$C_L = (t \times I_{Limit})/V_{in}$$

$$C_L = (0.080 \text{ x } 2)/48$$

$$C_{L} = 3,330 \mu f$$

It is important to notice that this theoretical methodology is intended to be used only for first approximation purposes.

Enable: The UVLO pin serves a double function. In addition to the UVLO function, it can also be used to disable the chip when it is pulled to the input– rail, with an open drain type of device. The open drain device must be able to sink the current from the internal  $100 \text{ k}\Omega$  resistor in parallel with the external adjustment resistor, at the highest input voltage required.

The turn on voltage at the UVLO pin is approximately 15 V, so any device that can sink the required amount of current should have a saturation voltage well below this requirement. The maximum sinking current can be calculated by the following equation:

$$I_{enable(max)} = V_{in(max)} \frac{100 \text{ k} + RUVLO}{100 \text{ k} \cdot RUVLO}$$

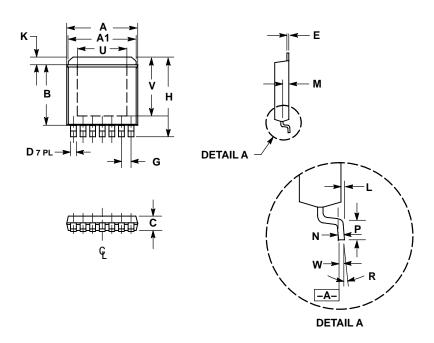

# **PACKAGE DIMENSIONS**

#### S-PAK-7 **EX SUFFIX** CASE 553AA-01 **ISSUE O**

- NOTES:

1. DIMENSIONS AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. PACKAGE OUTLINE EXCLUSIVE OF MOLD FLASH AND METAL BURR.

4. PACKAGE OUTLINE INCLUSIVE OF PLATING THICKNESS.

5. FOOT LENGTH MEASURED AT INTERCEPT POINT BETWEEN DATUM A AND LEAD SURFACE.

|     | INCHES    |           | MILLIMETERS |       |  |

|-----|-----------|-----------|-------------|-------|--|

| DIM | MIN       | MAX       | MIN         | MAX   |  |

| Α   | 0.365     | 0.375     | 9.27        | 9.52  |  |

| A1  | 0.350     | 0.360     | 8.89        | 9.14  |  |

| В   | 0.310     | 0.320     | 7.87        | 8.13  |  |

| С   | 0.070     | 0.080     | 1.78        | 2.03  |  |

| D   | 0.025     | 0.031     | 0.63        | 0.79  |  |

| E   | 0.010     | 0.010 BSC |             | BSC   |  |

| G   | 0.050     | 0.050 BSC |             | BSC   |  |

| н   | 0.410     | 0.420     | 10.41       | 10.67 |  |

| K   | 0.030     | 0.050     | 0.76        | 1.27  |  |

| L   | 0.001     | 0.005     | 0.03        | 0.13  |  |

| М   | 0.035     | 0.045     | 0.89        | 1.14  |  |

| N   | 0.010 BSC |           | 0.25 BSC    |       |  |

| Р   | 0.031     | 0.041     | 0.79        | 1.04  |  |

| R   | 0 °       | 6°        | 0 °         | 6°    |  |

| U   | 0.256 BCS |           | 6.50 BSC    |       |  |

| ٧   | 0.316 BSC |           | 8.03 BSC    |       |  |

| w   | 0.010 BSC |           | 0.25 BSC    |       |  |

The product described herein (NIS5101), may be covered by U.S. patents. Other patents may be pending, including ON Semiconductor disclosures ONS00448 and ONS00458.

SENSEFET and SMART HotPlug are trademarks of Semiconductor Components Industries, LLC.

ON Semiconductor and was are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082-1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Japan: ON Semiconductor, Japan Customer Focus Center Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81-3-5773-3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.