# LM5080

# **Modular Current Sharing Controller**

# **General Description**

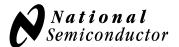

The LM5080 is a simple and cost effective load share controller that provides all functions required to balance the currents delivered from multiple power converters operated in parallel. The LM5080 implements an average program (AP) method of active load share control which adjusts the output voltage of individual power stages either up or down to deliver nearly equal currents to a common load. The average program method improves stability and reduces the output voltage tolerance when compared to other common load sharing methods. The LM5080 supports two common applications for load share controllers: external control in which the load share circuit balances currents between separate power modules (bricks), and internal control where the load share circuit is integrated into the voltage regulation loop of each power converter module or circuit.

#### **Features**

- Average program current share method

- Single-wire star link current share bus

- No precision external resistors necessary

- 3V to 15V bias voltage range

- Adaptable for high or low side current sensing

- Flexible architecture allows 4 modes of operation:

Negative remote sense adjustment

Positive remote sense adjustment

Trim or reference adjustment

Feedback divider adjustment

# **Packages**

- MSOP-8

- RoHS compliant Pb free available

# **LM5080 Typical Application**

Remote Sense Adjust Mode

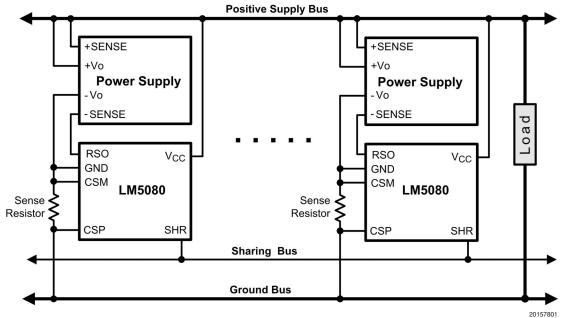

# **Connection Diagram**

8-Lead MSOP See NS Package Number MUA08A

# **Ordering Information**

| Order Number | Description | NSC Package Drawing | Supplied As                 |

|--------------|-------------|---------------------|-----------------------------|

| LM5080MM     | MSOP-8      | MUA08A              | 1000 Units on Tape and Reel |

| LM5080MMX    | MSOP-8      | MUA08A              | 3500 Units on Tape and Reel |

# **Pin Descriptions**

| Pin | Name | Description                                                                                                                                                                                  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SHR  | Current Share Bus. The SHR pins of each LM5080 device are connected together.                                                                                                                |

| 2   | CSM  | Current Sense Amplifier Minus Input.                                                                                                                                                         |

| 3   | TRO  | Transconductance Output. One of two outputs of the current sense transconductance amplifier.                                                                                                 |

| 4   | GND  | Ground. Connect to negative terminal of the LM5080 bias supply.                                                                                                                              |

| 5   | RSO  | Remote Sense Output. Capable of driving the low impedance remote sense pin of a power converter.                                                                                             |

| 6   | VCC  | Bias Supply. VCC can be connected to the output of the power converter that the LM5080 controls if greater than 3V, or it can be connected to another bias source for lower voltage systems. |

| 7   | CSO  | Current Sense Output. One of two outputs of the current sense transconductance amplifier.                                                                                                    |

| 8   | CSP  | Current Sense Amplifier Positive Input.                                                                                                                                                      |

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{\rm CC}$  to GND -0.3V to 15V RSO to GND (Note 2) -0.3V to 5V

All other pins to GND ESD Rating (Note 3)

Human Body Model 2kV

Storage Temperature -55°C to +150°C Junction Temperature 150°C

# **Operating Ratings** (Note 1)

VCC to GND 3V to 14 V Operating Junction Temperature  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

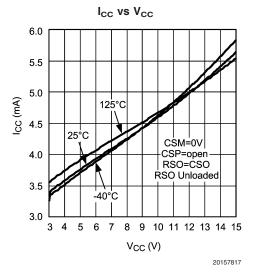

**Electrical Characteristics** Limits in standard type are for  $T_J = 25^{\circ}C$  only; limits in **boldface type** apply over the junction temperature range of  $-40^{\circ}C$  to  $+125^{\circ}C$  and are provided for reference only. Unless otherwise specified, the following conditions apply: CSM = 0, VCC = 5V, RSO unloaded.

-0.3V to 5V

| ICC                   |                                      |                                   |      |        |      |      |

|-----------------------|--------------------------------------|-----------------------------------|------|--------|------|------|

| ICC                   | VCC Quiescent Current                | RSO shorted to CSO                |      | 3.7    | 5.5  | mA   |

|                       |                                      | CSP = 50 mV                       |      |        |      |      |

|                       |                                      | CTRO = 10nF                       |      |        |      |      |

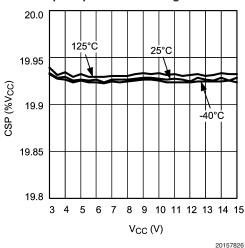

|                       | CSP Input open circuit voltage ratio | Specified as a percentage of VCC  | 19   | 20     | 21   | %    |

|                       | CSP mode threshold ratio- Rising     | Specified as a percentage of VCC  | 8.5  | 10.5   | 12.5 | %    |

|                       | CSP mode threshold ratio - Falling   | Specified as a percentage of VCC  | 7.0  | 9.5    | 11   | %    |

| Current Share         | Amplifier                            |                                   | •    |        |      |      |

| VIO                   | Input Offset Voltage (RSO-CSP)       | RSO shorted to CSO                | -2.5 | 0      | 2.5  | mV   |

|                       |                                      | CSP = 50 mV                       | -3.5 |        | 3.5  |      |

|                       |                                      | CTRO = 10nF                       |      |        |      |      |

|                       |                                      | RSO shorted to CSO                | -1   | 0      | 1    | mV   |

|                       |                                      | CSP = 600 mV                      | -2   |        | 2    |      |

|                       |                                      | CTRO = 10nF, VCC = 3V             |      |        |      |      |

| CSM <sub>MAX</sub>    | Input Common Mode Voltage            | CSP - CSM = 50 mV                 |      | VCC-2V |      | V    |

|                       | Range                                | RSO shorted to CSO                |      |        |      |      |

| CSM <sub>MIN</sub>    |                                      | CSO-CSP < 1 mV                    |      | 0      |      | V    |

| IVIIIV                |                                      | CTRO = 10 nF                      |      |        |      |      |

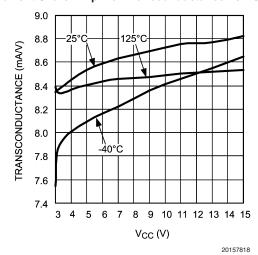

| $GM_{TRO}$            | Current Share Amplifier              | GM <sub>TRO</sub> = ΔITRO / ΔVSHR |      | 8.7    |      | mA/V |

|                       | Transconductance                     | CTRO = 10 nF                      |      |        |      |      |

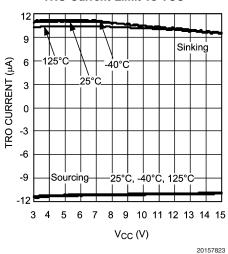

| I <sub>TRO_SRC</sub>  | TRO sourcing current limit           | TRO = 500 mV                      | 9    | 11     | 14   | μA   |

|                       |                                      | CSO open, CSP = 1.1V              |      |        |      |      |

| I <sub>TRO_SINK</sub> | TRO sinking current limit            | TRO = 500 mV                      | 8.2  | 11     | 13.5 | μA   |

|                       |                                      | CSO open, CSP=0.9V                |      |        |      |      |

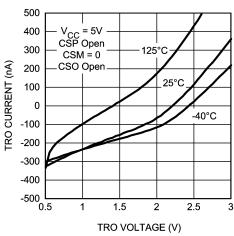

| I <sub>TRO_OS</sub>   | TRO offset current                   | TRO = 750 mV                      | -1   | 0      | 1    | μΑ   |

|                       |                                      | CSP, CSO Open Circuit             |      |        |      |      |

| $V_{TRO\_MIN}$        | TRO Output Range                     | CSP, CSO, SHA open circuit        |      | 450    |      | mV   |

| V <sub>TRO_MAX</sub>  |                                      | ITRO_OS < 500 nA                  |      | 2.75   |      | V    |

| RSO Buffer            |                                      |                                   |      |        |      |      |

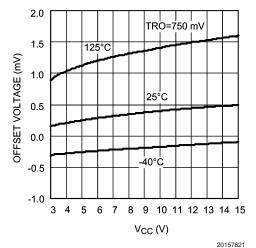

| VIO <sub>RSO</sub>    | RSO Buffer Input offset Voltage      | Offset = TRO-RSO, TR0 = 750 mV    | -4   | 0      | 4    | mV   |

| noo                   | , and the second second              | CSO, CSP open circuit             |      |        |      |      |

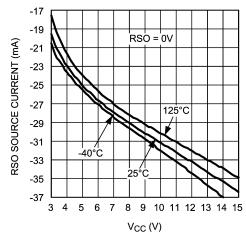

| I <sub>LIMSRC</sub>   | RSO source current limit             | ·                                 | 18   | 26     | 35   | mA   |

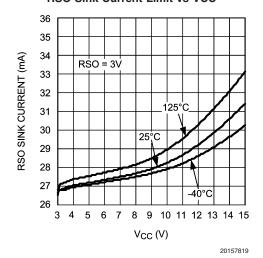

| I <sub>LIMSNK</sub>   | RSO sink current limit               |                                   | 18   | 26     | 35   | mA   |

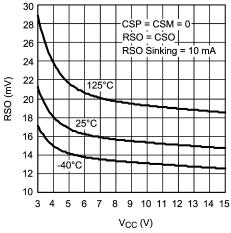

| VOL <sub>RSO</sub>    | RSO output low voltage               | CSP = 0V, Sinking 10 mA           | 1    | 12     | 28   | mV   |

|                       | -                                    | , ,                               | 1    | 1      |      |      |

| Thermal Resist        | tance                                |                                   |      |        |      |      |

**Electrical Characteristics** Limits in standard type are for  $T_J = 25^{\circ}\text{C}$  only; limits in **boldface type** apply over the junction temperature range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and are provided for reference only. Unless otherwise specified, the following conditions apply: CSM = 0, VCC = 5V, RSO unloaded. (Continued)

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but does not guarantee specific perfromance limits. For guaranteed specifications and test conditions see the Electrical Characteristics.

Note 2: Maximum recommended operating voltage not to exceed VCC - 2V or 5V, whichever is lower.

**Note 3:** The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

# **Typical Performance Characteristics**

# RSO Sink Current Limit vs VCC

#### **Current Share Amplifier Transconductance vs VCC**

#### **RSO Source Current Limit vs VCC**

20157820

# **Typical Performance Characteristics** (Continued)

#### **RSO Buffer Input Offset Voltage vs VCC**

**RSO VOL vs VCC**

#### 20157822

#### **TRO Current Limit vs VCC**

### TRO Offset Current vs TRO Voltage

20157824

#### CSP Input Open Circuit Voltage vs VCC

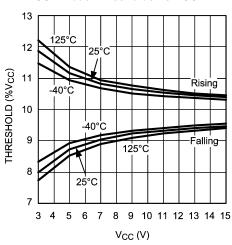

#### **CSP Mode Thresholds vs VCC**

20157827

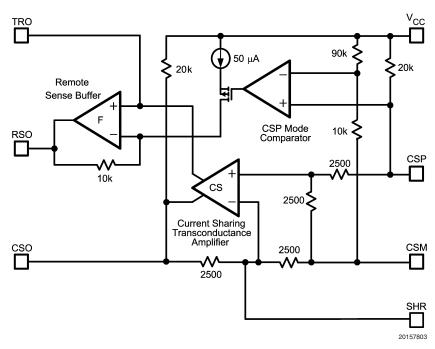

# **Block Diagram**

# **Operating Description**

Identical regulators connected in parallel will theoretically share the total load current equally. However, slight mismatches in the reference voltage or feedback dividers of each regulator can cause significant imbalances in the load current sharing. The LM5080 senses the load current of each regulator with an external sense resistor and makes adjustments to the regulator's output voltage to achieve nearly equal current sharing. There are four possible implementations for the LM5080:

Reference Adjust Mode achieves current sharing by adjusting the regulator reference voltage by applying an error current from the TRO transconductance amplifier to the trim or adjust pin of the regulator.

Remote Sense Positive Mode achieves current sharing by adjusting the positive remote sense pin of the power converter with current supplied by the RSO buffer amplifier output.

Remote Sense Negative Mode achieves current sharing by adjusting the negative remote sense pin of the power converter with current supplied by the RSO buffer amplifier output.

Feedback Adjust Mode achieves current sharing by adjusting the regulator feedback voltage by applying an error current from the TRO transconductance amplifier to the feedback resistor divider.

In each mode, the LM5080 combines the regulator's load current information with the total load information on the share (SHR) bus to create an error current on the TRO output which is proportional to the load current mismatch. In the reference adjust or feedback adjust modes of operation, the output of the current share amplifier (CSA) is fed directly into the regulator reference or feedback divider. The RSO buffer can optionally be used to boost the transconductance of the CSA if needed. In the remote sense adjust modes, the RSO and CSO pins are tied together which reconfigures the CSA as a voltage error amplifier where the RSO buffer drives the remote sense pins of the regulator directly.

# **Current Share Amplifier**

The current share amplifier is a low input offset transconductance amplifier with inputs CSP and CSM and dual outputs, TRO and CSO. The two outputs are identical except TRO is current limited to approximately  $\pm 10~\mu A$  in order to limit the maximum correction of the regulator reference in the trim adjust and feedback adjust modes. The outputs can operate down to 450 mV without saturating which allows the TRO output to adjust reference voltages as low as 500 mV. A capacitor from TRO to ground (CTRO) is used for frequency compensation of the current share loop.

In the two remote sense adjust modes, the current share amplifier is configured as a unity gain differential voltage amplifier by tying RSO to CSO. A capacitor from TRO to ground (CTRO) is used for frequency compensation of the amplifier and the current share loop.

#### **RSO Buffer**

The RSO buffer is a low-offset unity-gain operational amplifier that has different uses, depending on the mode of operation. In the remote sense adjust modes, the RSO pin is externally tied to the CSO pin to create a differential voltage amplifier that can drive the  $10\Omega$  input impedance of the remote sense pin of typical power converter modules. The RSO buffer can source or sink 10mA at an output voltage as

low as 20mV above ground. With RSO load resistors of  $10\Omega$ , the buffer can drive up to 10nF without causing amplifier instability. For RSO loads > 1 k $\Omega$ , max load capacitance on this node is 500pF for stable operation. In the trim adjust and feedback adjust modes, the RSO buffer can be configured with external resistors to boost the CSA transconductance which increases the current share loop gain.

## **CSP Mode Comparator**

The LM5080 monitors CSP & CSM with the CSP mode comparator and applies a 500 mV input offset on the RSO buffer amplifier if CSP-CSM is less than 10% of VCC (which indicates a remote sense application mode). This offset allows the RSO output to swing within 10 mV of ground without saturating the TRO output which drives the RSO buffer. In the trim adjust and feedback adjust modes, the CSP pin is left open. In this configuration CSP is internally biased such that CSP - CSM = 0.2 x VCC resulting in the removal of the 500mV RSO buffer offset.

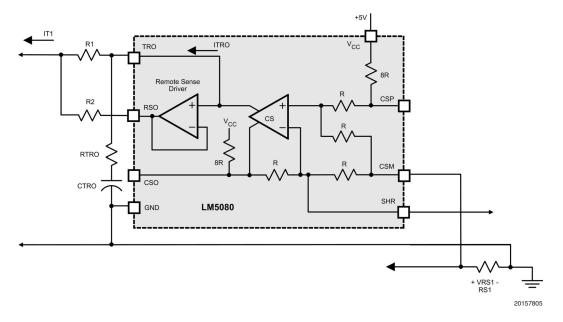

# Reference Adjustment Operation Mode

The reference adjust or trim adjust mode configuration is shown in Figure 1. Typically only the current share amplifier is used, however the RSO buffer can be optionally configured for boosting the transconductance to increase the current share loop gain (Figure 2). CSP is left open and CSM is connected to a low side current sense resistor. The TRO output is connected to the TRIM pin of the power converter to inject a correction that adjusts the voltage regulator.

To understand the control loop, assume for a moment the SHR pin is disconnected from the share bus. Since both inputs to the current share amplifier are equal, the TRO output current (IT) is zero and independent of the sense resistor voltage (VRS). Hence the voltage regulation loop of each converter is unaffected by the LM5080 when the SHR bus is open. When the SHR pins are connected in a 2 supply system, the transfer function between the sense resistor voltages (VRS1 & VRS2) and the current injected into each power converter TRIM pin (IT1 & IT2) are as follows:

IT1 = 0.9 x gm x (VRS1 - VRS2)

IT2 = 0.9 x gm x (VRS2 - VRS1)

where gm = current share amplifier transconductance (8.7mA/V).

As long as the current sharing is equal (VRS1=VRS2), the correction to the references (IT1 & IT2) will remain unchanged. However, any difference between VRS1 and VRS2 will drive the TRIM pin currents in opposite polarities. As a result the power converter output voltages will be adjusted to force VRS1=VRS2. For 3 or more channels, the same averaging concept is true; the injected currents (IT) will drive the references such that the sense voltages are nearly identical.

A capacitor from TRO to ground (CTRO) sets the dominant pole of the current share loop. The pole location is determined by gm, CTRO and the impedance of the regulator trim pin. The current share loop frequency response does not need to be fast and in fact should be less than or equal to 1/10th the regulator bandwidth. Since similar regulators will have similar transient responses to a load step, the LM5080 only needs to correct the differences in each regulator's

# Reference Adjustment Operation Mode (Continued)

voltage reference and feedback divider which do not require a fast response. In some systems a small resistor (RTRO) in series with CTRO can improve stability by introducing a zero at high frequencies to increase the phase margin of the current share loop.

It is essential that the VCC pins of all LM5080's be tied to the same point in this mode. Any mismatch in the VCC voltages

between LM5080's will significantly contribute to current share errors. The current sense resistors should be located as close to the load as possible to minimize trace resistance in series with the sense resistors which can also contribute to sharing errors. In this mode, the best accuracy will be achieved with lower VCC values since any mismatch in the gain resistors internal to the LM5080 will affect the current share accuracy.

FIGURE 1. Reference Adjust Mode Implementation

FIGURE 2. LM5080 Showing the RSO Buffer Configured to Boost Transconductance

The effective output current from the TRO pin can be multiplied to increase the current share loop gain if necessary. R1 should be at least  $10k\Omega$ .

IT1 = ITRO x

$$\left(1 + \frac{R1}{R2}\right)$$

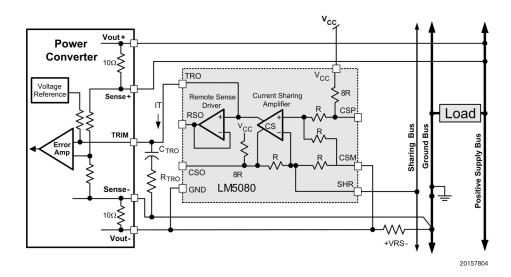

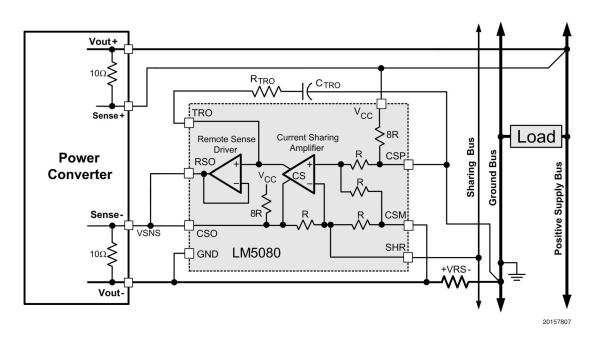

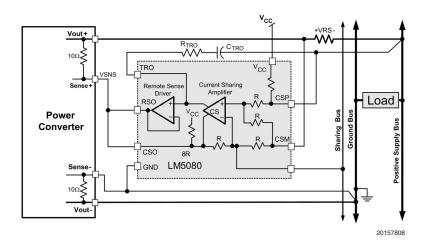

## **Remote Sense Adjust Modes**

The two remote sense adjust modes (positive and negative) achieve current sharing by controlling either remote sense input of the power converter. These configurations for the LM5080 are shown in Figures 3 and 4. To understand the sharing mechanism, assume for a moment the SHR pin is disconnected from the share bus. Connecting RSO and CSO configures the current sharing amplifier as a differential amplifier with a gain of one. The CSP and RSO voltage will be identical and independent of the voltage across the sense resistor. Hence the voltage regulation loop of each power converter is unaffected by the LM5080 when the SHR bus is open.

When the SHR pins are connected, the small signal transfer functions between the sense resistor voltages (VRS) and the power supplies negative remote sense voltages (VSNS) are:

$$VSNS1 = A/4 \times (VRS1 - VRS2)$$

$$VSNS2 = A/4 \times (VRS2 - VRS1)$$

where

$$A = \frac{Gm \times Ro}{(j_{\omega} \times Ro \times C_{TRO} + 1)}$$

gm = current share amplifier transconductance (8.7mA/V) Ro = output impedance of TRO pin (typically 6 M $\Omega$ ).

Provided the current sharing is equal (VRS1=VRS2), the VSNS voltages will remain unchanged. However, any difference between VRS1 and VRS2 will drive the VSNS1 and VSNS2 voltages in opposite polarities. As a result the power converter output voltages will be adjusted to force VRS1=VRS2.

A capacitor from TRO to ground will compensate the differential amplifier as well as set the dominant pole of the current share loop. CTRO should be at least 2 nF to insure stability of the differential amplifier. In some systems a small resistor (RTRO) in series with CTRO will improve stability of the current share loop by introducing a zero at high frequencies.

In the remote sense modes, it is essential the CSP pins of all LM5080's be tied to the exact same location on the PC board. Any mismatch in the CSP voltages between LM5080's will contribute to current share errors. As in the reference adjust mode, the current sense resistors should be located as close to the load as possible to minimize trace resistance in series with the sense resistors. In the remote sense positive mode, VCC must be biased at least 2V higher than the output regulation voltage to maintain CSP and CSM in the proper common mode range.

FIGURE 3. Remote Sense Negative Mode Implementation

## Remote Sense Adjust Modes (Continued)

FIGURE 4. Remote Sense Positive Mode Implementation

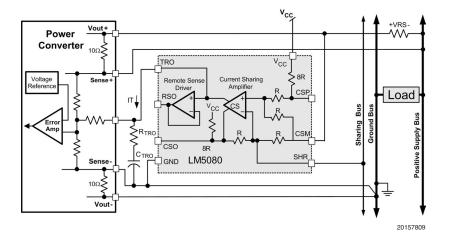

# Feedback Adjustment Mode

The feedback adjust mode configuration is shown in Figure 5. It is very similar to the reference adjust mode except the current sensing is done on the high side of the load and the correction is applied to the feedback resistor divider in the voltage regulation loop.

Similar to the reference adjust mode, the transfer functions between the sense resistor voltages (VRS) and the currents injected into the power converter TRIM pin (IT) are:

IT1 = 0.9 x gm x (VRS1 - VRS2)

$IT2 = 0.9 \times gm \times (VRS2 - VRS1)$

where gm = current share amplifier transconductance (8.7mA/V).

As previously described, provided the current sharing is equal (VRS1=VRS2), the correction current to the reference (IT) will be zero. However, any difference between VRS1 and VRS2 will drive the TRIM pin currents in opposite polarities. As a result the power converter output voltages will be adjusted to force VRS1=VRS2.

In this mode, VCC must be biased at least 2V higher than the output regulation voltage to maintain CSP and CSM in the proper common mode range. It is essential the VCC pins of all LM5080's be tied to the same point in this mode. Any mismatch in the VCC voltages between LM5080's will contribute to current share errors. For the same reasons as discussed in the above two operating modes, the current sense resistors should be located as close to the load as possible. In this mode, the best accuracy will be achieved with lower VCC values since any mismatch in the gain resistors internal to the LM5080 will affect the current share accuracy.

FIGURE 5. Feedback Adjust Mode Implementation

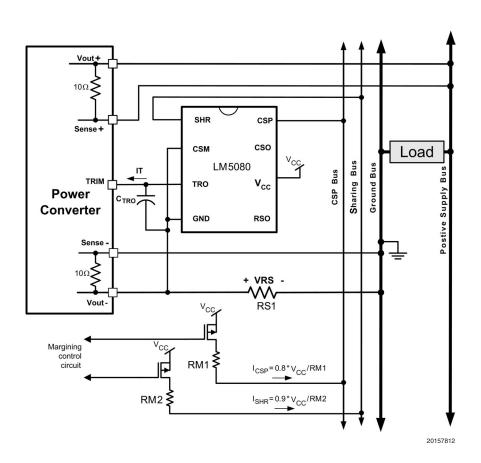

# **Voltage Margining**

Shifting the output regulation voltage up or down by a small amount is referred to as voltage margining. In the remote sense adjust modes and the feedback adjust modes, this can be done by connecting all of the power converter TRIM pins together and injecting a positive or negative current. However, in the reference adjust mode, the TRIM pin is used for current sharing. An alternative margining method is to inject a current into the SHR share bus. This will simultaneously shift the regulation voltages of all power converter's while maintaining equal current sharing. The injected current is split equally between the LM5080's SHR inputs and added to the TRIM pin currents creating an equal offset voltage for all of the power converter references. The trim pin current injected into each power converter's reference (IT) is dependent on the magnitude of the total injected current into the SHR bus (ISHR), the number of LM5080's on the SHR bus (N) and any transconductance boost supplied (R1 & R2):

$$IT1 = I_{SHR} x \left(\frac{22.5}{21x N}\right) x \left(1 + \frac{R1}{R2}\right)$$

An alternate method to shift the regulation voltage is to tie all the CSP pins together and inject a current into that node. The trim pin current injected into each power converter's reference (IT) attributed to the current injected into the CSP node (ICSP) is derived to be:

$$IT1 = I_{CSP} x \left(\frac{20}{21x N}\right) x \left(1 + \frac{R1}{R2}\right)$$

Figure 6 shows a margining up and down application implemented using pull up resistors to VCC. Since the SHR and CSP voltages are approximately 0.1 x VCC and 0.2 x VCC respectively, the injected current can be independently controlled with RM1 and RM2.

FIGURE 6. One Method of Implementing Voltage Margining

## **General Design Procedure**

- Select an appropriate sense resistor value. More sense voltage will result in better load sharing but more efficiency loss. Sense voltages of 50mV or more are recommended. In addition, the sense voltage at full load should be less than 5% of VCC in applications that control the remote sense terminals of the power supply.

- 2. For the reference adjust and feedback adjust modes, determine if transconductance (gm) boosting is required. Boosting the transconductance also boosts the TRO pin current limit. The TRO pin current limit (approximately 10μA typical) multiplied by the reference impedance determines the maximum correction the LM5080 can make to the reference. The LM5080 must have enough TRO current to adjust the converter output voltage by at least the accuracy of the reference. For example, if the reference accuracy is ±2%, the LM5080 must have the ability to adjust the reference by at least 2% (in the event one converter is 2% high and the other 2% low).

- 3. Compensate the current share loop by selecting an appropriate capacitance for CTRO. The compensation

- of the current share loop is dependent on the frequency response of the output voltage to the controlling node of the converter (TRIM pin, feedback divider or remote sense pins). Given the wide variety of converter designs and the many operating modes of the LM5080, selection of CTRO is best accomplished using a simple iterative procedure. Start with a large capacitance in TRO (100µF or more). While monitoring the load current in each converter with a current probe, determine the minimum CTRO required for stability by decreasing CTRO until the current sharing becomes unstable under step loads. The step loads should be more than 50% of the load range and applied at a frequency well below the cross over frequency of the converter. The TRO capacitance can be further reduced by introducing some resistance (RTRO) in series with CTRO to cancel the 2nd order poles within the converter.

- If RTRO > 100 Ω in either remote sense mode, a second CTRO capacitor (~ 2nF) should be added between TRO and CSP to keep the error amplifier stable.

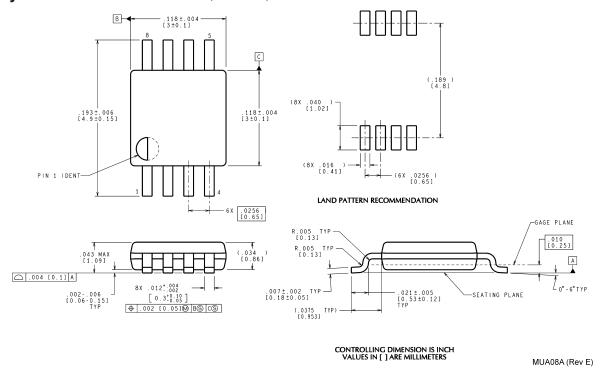

### Physical Dimensions inches (millimeters) unless otherwise noted

8 Lead MSOP Package **NS Package Number MUA08A**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

**National Semiconductor Americas Customer** Support Center

Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560