National Semiconductor

# COP87L88CL/COP87L84CL 8-Bit **One-Time Programmable (OTP) Microcontroller**

### **General Description**

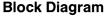

The COP87L88CL/COP87L84CL OTP microcontrollers are members of the COP8™ feature family using an 8-bit core architecture. It is pin and software compatible to the mask ROM COP888CL/COP884CL product family.

(Continued)

# **Key Features**

- Two 16-bit timers, each with two 16-bit registers supporting:

- Processor independent PWM mode

- External event counter mode

- Input capture mode

- 4 kbytes on-board EPROM with security feature

- 128 bytes on-board RAM

# **Additional Peripheral Features**

- Idle timer

- Multi-Input Wake-Up (MIWU) with optional interrupts (8)

- WATCHDOG<sup>TM</sup> and clock monitor logic

- MICROWIRE/PLUS™ serial I/O

### I/O Features

### Memory mapped I/O

- Software selectable I/O options (TRI-STATE® output, push-pull output, weak pull-up input, high impedance input)

- Schmitt trigger inputs on ports G and L

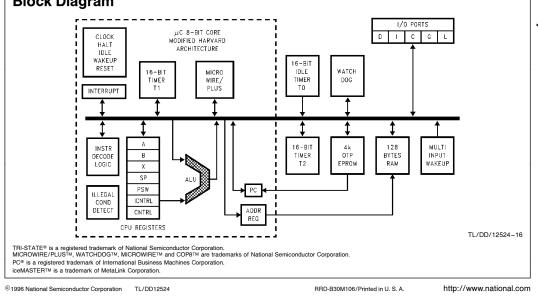

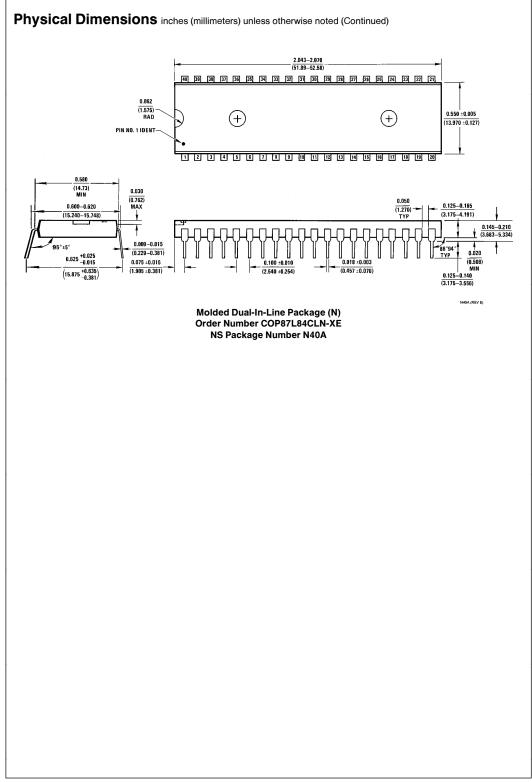

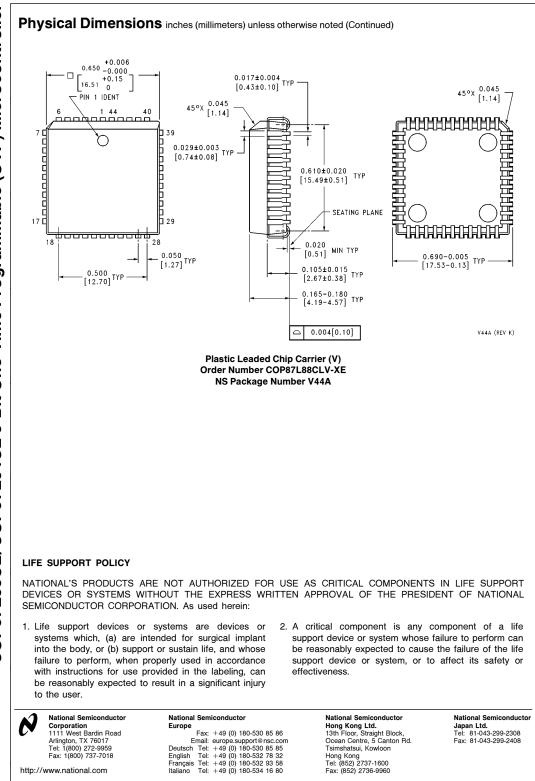

- Packages:

- 44 PLCC with 39 I/O pins

- 40 DIP with 33 I/O pins

- 28 DIP with 24 I/O pins

- 28 SO with 24 I/O pins (contact local sales office for availability)

# **CPU/Instruction Set Features**

- 1 μs instruction cycle time

- Ten multi-source vectored interrupts servicing External interrupt

- Idle timer T0

- Two timers (each with 2 Interrupts)

- MICROWIRE/PLUS

- Multi-Input Wake Up

- Software trap

- Default VIS (default interrupt)

- Versatile and easy to use instruction set

- 8-bit Stack Pointer SP—stack in RAM

- Two 8-bit register indirect data memory pointers (B and X)

# **Fully Static CMOS**

- Two power saving modes: HALT and IDLE

- Single supply operation: 2.7V-5.5V

- Temperature range: -40°C to +85°C

# **Development Support**

- Emulation device for the COP888CL/COP884CL

- Real time emulation and full program debug offered by MetaLink Development System

COP87L88CL/COP87L84CL 8-Bit One-Time Programmable (OTP) Microcontroller

PRELIMINARY

September 1996

### General Description (Continued)

The device is a fully static part, fabricated using double-metal silicon gate microCMOS technology. Features include an 8-bit memory mapped architecture, MICROWIRE/PLUS™ serial I/O, two 16-bit timer/counters supporting three modes (Processor Independent PWM generation, External Event counter, and Input Capture mode capabilities). Each I/O pin has software selectable configurations. The devices operates over a voltage range of 2.7V to 5.5V. High throughput is achieved with an efficient, regular instruction set operating at a maximum of 1  $\mu$ s per instruction rate.

| Port                                                         | Туре                                                 | Alt. Fun                                                     | Alt. Fun   | 28-Pin<br>Pkg.                               | 40-Pin<br>Pkg.                               | 44-Pi<br>Pkg                                 |

|--------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------|------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| L0<br>L1<br>L2<br>L3<br>L4<br>L5<br>L6<br>L7                 | 1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0 | MIWU<br>MIWU<br>MIWU<br>MIWU<br>MIWU<br>MIWU<br>MIWU<br>MIWU | T2A<br>T2B | 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | 17<br>18<br>19<br>20<br>25<br>26<br>27<br>28 |

| G0<br>G1<br>G2<br>G3<br>G4<br>G5<br>G6<br>G7                 | I/O<br>WDOUT<br>I/O<br>I/O<br>I/O<br>I<br>I/CKO      | INT<br>T1B<br>T1A<br>SO<br>SK<br>SI<br>Halt Restart          |            | 25<br>26<br>27<br>28<br>1<br>2<br>3<br>4     | 35<br>36<br>37<br>38<br>3<br>4<br>5<br>6     | 39<br>40<br>41<br>42<br>3<br>4<br>5<br>6     |

| D0<br>D1<br>D2<br>D3                                         | 0<br>0<br>0<br>0                                     |                                                              |            | 19<br>20<br>21<br>22                         | 25<br>26<br>27<br>28                         | 29<br>30<br>31<br>32                         |

| 0<br> 1<br> 2<br> 3                                          |                                                      |                                                              |            | 7<br>8                                       | 9<br>10<br>11<br>12                          | 9<br>10<br>11<br>12                          |

| 4<br> 5<br> 6<br> 7                                          |                                                      |                                                              |            | 9<br>10                                      | 13<br>14                                     | 13<br>14<br>15<br>16                         |

| D4<br>D5<br>D6<br>D7                                         | 0<br>0<br>0<br>0                                     |                                                              |            |                                              | 29<br>30<br>31<br>32                         | 33<br>34<br>35<br>36                         |

| C0<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7                 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O        |                                                              |            |                                              | 39<br>40<br>1<br>2                           | 43<br>44<br>1<br>2<br>21<br>22<br>23<br>24   |

| Unused*<br>Unused*<br>V <sub>CC</sub><br>GND<br>CKI<br>RESET |                                                      |                                                              |            | 6<br>23<br>5<br>24                           | 16<br>15<br>8<br>33<br>7<br>34               | 8<br>37<br>7<br>38                           |

# Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications. Supply Voltage (V<sub>CC</sub>) 7V

Voltage at Any Pin-0.3V to  $V_{CC} + 0.3V$ Total Current into  $V_{CC}$  Pin (Source)100 mA

Total Current out of GND Pin (Sink)

110 mA -65°C to +140°C

Storage Temperature Range

$-65^{\circ}$ C to  $+140^{\circ}$ C

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

| Parameter                                                                                                                                                           | Conditions                                                                                                                                                                                       | Min                                                               | Тур                  | Max                                                               | Units                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|-------------------------------------------------------------------|----------------------------|

| Operating Voltage                                                                                                                                                   |                                                                                                                                                                                                  | 2.7                                                               |                      | 5.5                                                               | V                          |

| Power Supply Ripple (Note 1)                                                                                                                                        | Peak-to-Peak                                                                                                                                                                                     |                                                                   |                      | 0.1 V <sub>CC</sub>                                               | V                          |

| Supply Current (Note 2)<br>CKI = 10 MHz<br>CKI = 4 MHz                                                                                                              | $V_{CC} = 5.5V, t_c = 1 \ \mu s$<br>$V_{CC} = 4.0V, t_c = 2.5 \ \mu s$                                                                                                                           |                                                                   |                      | 16.5<br>6.5                                                       | mA<br>mA                   |

| HALT Current (Note 3)                                                                                                                                               | $V_{CC} = 5.5V, CKI = 0 MHz$                                                                                                                                                                     |                                                                   |                      | 12                                                                | μΑ                         |

| IDLE Current, CKI = 10 MHz<br>CKI = 1 MHz                                                                                                                           | $V_{CC} = 5.5V, t_c = 1 \ \mu s$<br>$V_{CC} = 4.0V, t_c = 10 \ \mu s$                                                                                                                            |                                                                   |                      | 3.5<br>0.7                                                        | mA<br>mA                   |

| Input Levels<br>RESET<br>Logic High<br>Logic Low<br>CKI (External and Crystal Osc. Modes)<br>Logic High<br>Logic Low<br>All Other Inputs<br>Logic High<br>Logic Low |                                                                                                                                                                                                  | 0.8 V <sub>CC</sub><br>0.7 V <sub>CC</sub><br>0.7 V <sub>CC</sub> |                      | 0.2 V <sub>CC</sub><br>0.2 V <sub>CC</sub><br>0.2 V <sub>CC</sub> | v                          |

| Hi-Z Input Leakage                                                                                                                                                  | $V_{CC} = 5.5V$                                                                                                                                                                                  | -2                                                                |                      | +2                                                                | μA                         |

| Input Pullup Current                                                                                                                                                | $V_{CC} = 5.5V$                                                                                                                                                                                  | 40                                                                |                      | 250                                                               | μA                         |

| G and L Port Input Hysteresis                                                                                                                                       |                                                                                                                                                                                                  |                                                                   | 0.05 V <sub>CC</sub> | 0.35 V <sub>CC</sub>                                              | V                          |

| Output Current Levels<br>D Outputs<br>Source<br>Sink (Note 4)<br>All Others<br>Source (Weak Pull-Up Mode)<br>Source (Push-Pull Mode)<br>Sink (Push-Pull Mode)       | $\begin{split} & V_{CC} = 4.5V, V_{OH} = 3.3V \\ & V_{CC} = 4.5V, V_{OL} = 1V \\ & V_{CC} = 4.5V, V_{OH} = 2.7V \\ & V_{CC} = 4.5V, V_{OH} = 3.3V \\ & V_{CC} = 4.5V, V_{OL} = 0.4V \end{split}$ | 0.4<br>10<br>10<br>0.4<br>1.6                                     |                      | 100                                                               | mA<br>mA<br>μA<br>mA<br>mA |

| TRI-STATE Leakage                                                                                                                                                   | $V_{CC} = 5.5V$                                                                                                                                                                                  | -2                                                                |                      | +2                                                                | μΑ                         |

| Allowable Sink/Source<br>Current per Pin<br>D Outputs (Sink)<br>All others                                                                                          |                                                                                                                                                                                                  |                                                                   |                      | 15<br>3                                                           | mA                         |

| Maximum Input Current<br>without Latchup (Note 5)                                                                                                                   | T <sub>A</sub> = 25°C                                                                                                                                                                            |                                                                   |                      | ±100                                                              | mA                         |

| RAM Retention Voltage, V <sub>r</sub>                                                                                                                               | 500 ns Rise<br>and Fall Time (Min)                                                                                                                                                               | 2                                                                 |                      |                                                                   | v                          |

| Input Capacitance                                                                                                                                                   |                                                                                                                                                                                                  |                                                                   |                      | 7                                                                 | pF                         |

| Load Capacitance on D2                                                                                                                                              |                                                                                                                                                                                                  |                                                                   |                      | 1000                                                              | pF                         |

Note 2: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at rails and outputs open.

Note 3: The HALT mode will stop CKI from oscillating in the RC and the Crystal configurations by bringing CKI high. Test conditions: All inputs tied to V<sub>CC</sub>, L and G ports in the TRI-STATE mode and tied to ground, all outputs low and tied to ground. The clock monitor is disabled.

Note 4: The user must guarantee that D2 pin does not source more than 10 mA during RESET. If D2 sources more than 10 mA during RESET, the device will go into programming mode.

Note 5: Pins G5 and RESET are designed with a high voltage input network for factory testing. These pins allow input voltages greater than  $V_{CC}$  and the pins will have sink current to  $V_{CC}$  when biased at voltages greater than  $V_{CC}$  (the pins do not have source current when biased at a voltage below  $V_{CC}$ ). The effective resistance to  $V_{CC}$  is 750 $\Omega$  (typical). These two pins will not latch up. The voltage at the pins must be limited to less than 14V.

| Parameter                                                                                                                                      | Conditions                                                                                                                           | Min         | Тур    | Max      | Unite          |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|----------|----------------|

| Instruction Cycle Time (t <sub>c</sub> )<br>Crystal or Resonator<br>R/C Oscillator                                                             |                                                                                                                                      | 1<br>3      |        | DC<br>DC | μs             |

| Inputs<br><sup>t</sup> SETUP<br><sup>t</sup> HOLD                                                                                              |                                                                                                                                      | 200<br>60   |        |          | ns             |

| Output Propagation Delay<br><sup>t</sup> PD1, t <sub>PD0</sub><br>SO, SK<br>All Others                                                         | $\label{eq:relation} \begin{split} R_L &= 2.2k, C_L = 100 \ pF \\ \\ 4V &\leq V_{CC} \leq 6V \\ 4V &\leq V_{CC} \leq 6V \end{split}$ |             |        | 0.7<br>1 | μs             |

| MICROWIRE™ Setup Time (t <sub>UWS</sub> )<br>MICROWIRE Hold Time (t <sub>UWH</sub> )<br>MICROWIRE Output Propagation Delay (t <sub>UPD</sub> ) |                                                                                                                                      | 20<br>56    |        | 220      | ns             |

| Input Pulse Width<br>Interrupt Input High Time<br>Interrupt Input Low Time<br>Timer Input High Time<br>Timer Input Low Time                    |                                                                                                                                      | 1<br>1<br>1 |        |          | t <sub>c</sub> |

| Reset Pulse Width                                                                                                                              |                                                                                                                                      | 1           |        |          | μs             |

| SI<br>SI<br>S0                                                                                                                                 |                                                                                                                                      |             |        |          |                |

| -<br>50 _                                                                                                                                      |                                                                                                                                      | TL/DD/12    | 2524-4 |          |                |

| -<br>50 _                                                                                                                                      |                                                                                                                                      |             | 2524-4 |          |                |

| -<br>50 _                                                                                                                                      |                                                                                                                                      |             | 2524-4 |          |                |

| -<br>50 _                                                                                                                                      |                                                                                                                                      |             | 2524-4 |          |                |

| -<br>50 _                                                                                                                                      |                                                                                                                                      |             | 2524-4 |          |                |

| -<br>50 _                                                                                                                                      |                                                                                                                                      |             | 2524-4 |          |                |

### **Pin Descriptions**

V<sub>CC</sub> and GND are the power supply pins.

CKI is the clock input. This can come from an R/C generated oscillator, or a crystal oscillator (in conjunction with CKO). See Oscillator Description section.

RESET is the master reset input. See Reset Description section.

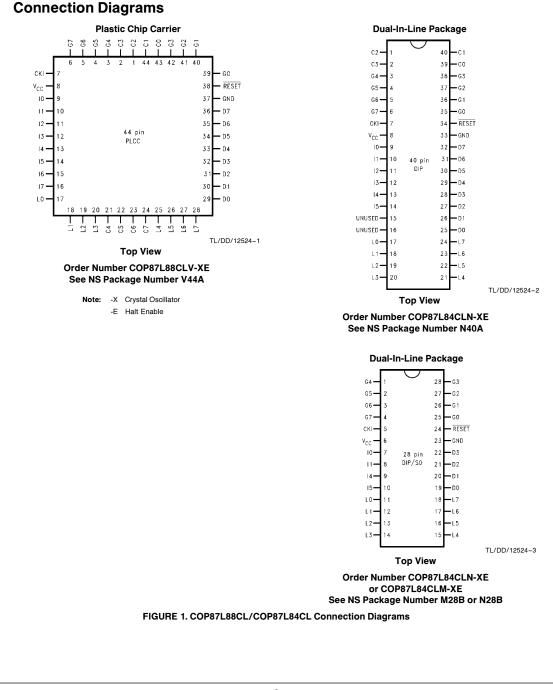

The device contains three bidirectional 8-bit I/O ports (C, G and L), where each individual bit may be independently configured as an input (Schmitt trigger inputs on ports G and L), output or TRI-STATE under program control. Three data memory address locations are allocated for each of these I/O ports. Each I/O port has two associated 8-bit memory mapped registers, the CONFIGURATION register and the output DATA register. A memory mapped address is also reserved for the input pins of each I/O port. (See the memory map for the various addresses associated with the I/O ports.) *Figure 3* shows the I/O port configurations. The DATA and CONFIGURATION registers allow for each port bit to be individually configured under software control as shown below:

| CONFIGURATION<br>Register | DATA<br>Register | Port Set-Up                      |

|---------------------------|------------------|----------------------------------|

| 0                         | 0                | Hi-Z Input<br>(TRI-STATE Output) |

| 0                         | 1                | Input with Weak Pull-Up          |

| 1                         | 0                | Push-Pull Zero Output            |

| 1                         | 1                | Push-Pull One Output             |

#### FIGURE 3. I/O Port Configurations

PORT L is an 8-bit I/O port. All L-pins have Schmitt triggers on the inputs.

Port L supports Multi-Input Wakeup (MIWU) on all eight pins. L4 and L5 are used for the timer input functions T2A and T2B.

Port L has the following alternate features:

- L0 MIWU

- L1 MIWU

- L2 MIWU

- L3 MIWU

- L4 MIWU or T2A

- L5 MIWU or T2B

- L6 MIWU

- L7 MIWU

Port G is an 8-bit port with 5 I/O pins (G0, G2–G5), an input pin (G6), and two dedicated output pins (G1 and G7). Pins G0 and G2–G6 all have Schmitt Triggers on their inputs. Pin G1 serves as the dedicated WDOUT WATCHDOG output, while pin G7 is either input or output depending on the oscillator mask option selected. With the crystal oscillator option selected, G7 serves as the dedicated output pin for the CKO clock output. With the single-pin R/C oscillator mask option selected, G7 serves as a general purpose input pin, but is also used to bring the device out of HALT mode with a low to high transition. There are two registers associated with the G Port, a data register and a configuration register. Therefore, each of the 5 I/O bits (G0, G2–G5) can be individually configured under software control.

Since G6 is an input only pin and G7 is the dedicated CKO clock output pin or general purpose input (R/C clock configuration), the associated bits in the data and configuration registers for G6 and G7 are used for special purpose functions as outlined below. Reading the G6 and G7 data bits will return zeros.

Note that the chip will be placed in the HALT mode by writing a "1" to bit 7 of the Port G Data Register. Similarly the chip will be placed in the IDLE mode by writing a "1" to bit 6 of the Port G Data Register.

Writing a "1" to bit 6 of the Port G Configuration Register enables the MICROWIRE/PLUS to operate with the alternate phase of the SK clock. The G7 configuration bit, if set high, enables the clock start up delay after HALT when the R/C clock configuration is used.

|    | Config Reg.  | Data Reg. |

|----|--------------|-----------|

| G7 | CLKDLY       | HALT      |

| G6 | Alternate SK | IDLE      |

Port G has the following alternate features:

- G0 INTR (External Interrupt Input)

- G2 T1B (Timer T1 Capture Input)

- G3 T1A (Timer T1 I/O)

- G4 SO (MICROWIRE Serial Data Output)

- G5 SK (MICROWIRE Serial Clock)

- G6 SI (MICROWIRE Serial Data Input)

### Pin Descriptions (Continued)

Port G has the following dedicated functions:

- G1 WDOUT WATCHDOG and/or Clock Monitor dedicated output

- G7 CKO Oscillator dedicated output or general purpose input

Port C is an 8-bit I/O port. The 28-pin device does not have a full complement of Port C pins. The unavailable pins are not terminated. A read operation for these unterminated pins will return unpredictable values.

Port I is an 8-bit Hi-Z input port. The 28-pin device does not have a full complement of Port I pins. The unavailable pins are not terminated (i.e. they are floating). A read operation from these unterminated pins will return unpredictable values. The user should ensure that the software takes this into account by either masking out these inputs, or else restricting the accesses to bit operations only. If unterminated, Port I pins will draw power only when addressed. The I port leakage current may be higher in 28-pin devices.

Port D is a recreated 8-bit output port that is preset high when RESET goes low. D port recreation is one clock cycle behind the normal port timing. The user can tie two or more D port outputs (except D2 pin) together in order to get a higher drive.

### **Functional Description**

The architecture of the device is modified Harvard architecture. With the Harvard architecture, the control store program memory (ROM) is separated from the data store memory (RAM). Both ROM and RAM have their own separate addressing space with separate address buses. The architecture, though based on Harvard architecture, permits transfer of data from ROM to RAM.

#### **CPU REGISTERS**

The CPU can do an 8-bit addition, subtraction, logical or shift operation in one instruction ( $t_c$ ) cycle time. There are five CPU registers:

There are live CFU registers.

A is the 8-bit Accumulator Register

PC is the 15-bit Program Counter Register

PU is the upper 7 bits of the program counter (PC) PL is the lower 8 bits of the program counter (PC)

B is an 8-bit RAM address pointer, which can be optionally post auto incremented or decremented.

X is an 8-bit alternate RAM address pointer, which can be optionally post auto incremented or decremented.

SP is the 8-bit stack pointer, which points to the subroutine/ interrupt stack (in RAM). The SP is initialized to RAM address 06F with reset.

All the CPU registers are memory mapped with the exception of the Accumulator (A) and the Program Counter (PC).

#### PROGRAM MEMORY

Program memory consists of 4 kbytes of OTP EPROM. These bytes may hold program instructions or constant data (data tables for the LAID instruction, jump vectors for the JID instruction, and interrupt vectors for the VIS instruction). The program memory is addressed by the 15-bit program counter (PC). All interrupts vector to program memory location 0FF Hex. The device can be configured to inhibit external reads of the program memory. This is done by programming the Security Byte.

#### SECURITY FEATURE

The program memory array has an associate Security Byte that is located outside of the program address range. This byte can be addressed only from programming mode by a programmer tool.

Security is an optional feature and can only be asserted after the memory array has been programmed and verified. A secured part will read all 00(hex) by a programmer. The part will fail Blank Check and will fail Verify operations. A Read operation will fill the programmer's memory with 00(hex). The Security Byte itself is always readable with a value of 00(hex) if unsecure and FF(hex) if secure.

### DATA MEMORY

The data memory address space includes the on-chip RAM and data registers, the I/O registers (Configuration, Data and Pin), the control registers, the MICROWIRE/PLUS SIO shift register, and the various registers, and counters associated with the timers (with the exception of the IDLE timer). Data memory is addressed directly by the instruction or indirectly by the B, X and SP pointers.

The device has 128 bytes of RAM. Sixteen bytes of RAM are mapped as "registers" at addresses 0F0 to 0FF Hex. These registers can be loaded immediately, and also decremented and tested with the DRSZ (decrement register and skip if zero) instruction. The memory pointer registers X, SP, and B are memory mapped into this space at address locations 0FC to 0FE Hex respectively, with the other registers (other than reserved register 0FF) being available for general usage.

The instruction set permits any bit in memory to be set, reset or tested. All I/O and registers on the device (except A and PC) are memory mapped; therefore, I/O bits and register bits can be directly and individually set, reset and tested. The accumulator (A) bits can also be directly and individually tested.

#### Reset

The  $\overline{\text{RESET}}$  input when pulled low initializes the microcontroller. Initialization will occur whenever the  $\overline{\text{RESET}}$  input is pulled low. Upon initialization, the data and configuration registers for Ports L, G, and C are cleared, resulting in these Ports being initialized to the TRI-STATE mode. Pin G1 of the G Port is an exception (as noted below) since pin G1 is dedicated as the WATCHDOG and/or Clock Monitor error output pin. Port D is initialized high with  $\overline{\text{RESET}}$ . The PC, PSW, CNTRL, ICNTRL, and T2CNTRL control registers are cleared. The Multi-Input Wakeup registers WKEN, WKEDG, and WKPND are cleared. The Stack Pointer, SP, is initialized to 6F Hex.

The device comes out of reset with both the WATCHDOG logic and the Clock Monitor detector armed, and with both the WATCHDOG service window bits set and the Clock Monitor bit set. The WATCHDOG and Clock Monitor detector circuits are inhibited during reset. The WATCHDOG service window bits are initialized to the maximum WATCHDOG service window of 64k  $t_c$  clock cycles. The Clock Monitor bit is initialized high, and will cause a Clock Monitor rofolowing reset if the clock has not reached the minimum specified frequency at the termination of reset. A Clock Monitor

### Reset (Continued)

error will cause an active low error output on pin G1. This error output will continue until 16–32  $t_{\rm c}$  clock cycles following the clock frequency reaching the minimum specified value, at which time the G1 output will enter the TRI-STATE mode.

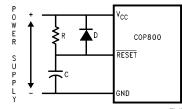

The external RC network shown in *Figure 4* should be used to ensure that the  $\overrightarrow{\text{RESET}}$  pin is held low until the power supply to the chip stabilizes.

Note: In continual state of reset, the device will draw excessive current.

TL/DD/12524-6

$\rm RC > 5 \times$  Power Supply Rise Time

FIGURE 4. Recommended Reset Circuit

### **Oscillator Circuits**

The chip can be driven by a clock input on the CKI input pin which can be between DC and 10 MHz. The CKO output clock is on pin G7 (crystal configuration). The CKI input frequency is divided down by 10 to produce the instruction cycle clock ( $1/t_c$ ).

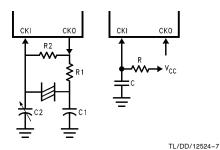

Figure 5 shows the Crystal and R/C diagrams.

FIGURE 5. Crystal and R/C Oscillator Diagrams

#### CRYSTAL OSCILLATOR

CKI and CKO can be connected to make a closed loop crystal (or resonator) controlled oscillator.

Table I shows the component values required for various standard crystal values.

| TABLE I. Crystal Oscillator | Configuration, T <sub>A</sub> | = 25°C |

|-----------------------------|-------------------------------|--------|

|-----------------------------|-------------------------------|--------|

| <b>R1</b><br>(kΩ) | R2<br>(MΩ) | C1<br>(pF) | C2<br>(pF) | CKI Freq<br>(MHz) | Conditions    |

|-------------------|------------|------------|------------|-------------------|---------------|

| 0                 | 1          | 30         | 30-36      | 10                | $V_{CC} = 5V$ |

| 0                 | 1          | 30         | 30-36      | 4                 | $V_{CC} = 5V$ |

| 0                 | 1          | 200        | 100-150    | 0.455             | $V_{CC} = 5V$ |

#### **R/C OSCILLATOR**

By selecting CKI as a single pin oscillator input, a single pin R/C oscillator circuit can be connected to it. CKO is available as a general purpose input, and/or HALT restart pin. Table II shows the variation in the oscillator frequencies as functions of the component (R and C) values.

| <b>R</b><br>(kΩ) | C<br>(pF) | CKI Freq<br>(MHz) | Instr. Cycle<br>(μs) | Conditions    |

|------------------|-----------|-------------------|----------------------|---------------|

| 3.3              | 82        | 2.2–2.7           | 3.7-4.6              | $V_{CC} = 5V$ |

| 5.6              | 100       | 1.1–1.3           | 7.4–9.0              | $V_{CC} = 5V$ |

| 6.8              | 100       | 0.9–1.1           | 8.8–10.8             | $V_{CC} = 5V$ |

Note:  $3k \le R \le 200k$ ,  $50 \text{ pF} \le C \le 200 \text{ pF}$

# **Control Registers**

### CNTRL Register (Address X'00EE)

The Timer1 (T1) and MICROWIRE/PLUS control register contains the following bits:

| SL1 & SL0 Select | the MICROWIRE/PLUS   | clock divide |

|------------------|----------------------|--------------|

| by (00           | = 2, 01 = 4, 1x = 8) |              |

| IEDG | External interrupt edge polarity select |

|------|-----------------------------------------|

|      | (0 = Rising edge, 1 = Falling edge)     |

MSEL Selects G5 and G4 as MICROWIRE/PLUS signals SK and SO respectively

|           |                            | T1 Unde<br>mode 3                 | erflow Inte                      | errupt P | ending   | Flag in |  |

|-----------|----------------------------|-----------------------------------|----------------------------------|----------|----------|---------|--|

| T1C1      | Timer                      | T1 mod                            | e control                        | bit      |          |         |  |

| T1C2      | Timer                      | T1 mod                            | e control                        | bit      |          |         |  |

| T1C3      | Timer                      | T1 mod                            | e control                        | bit      |          |         |  |

| T1C3 T10  | C2 T1C                     | 1 T1C0                            | MSEL                             | IEDG     | SL1      | SL0     |  |

| Bit 7     |                            |                                   |                                  |          |          | Bit 0   |  |

| PSW Regis | ster (Add                  | dress X'(                         | 00EF)                            |          |          |         |  |

| The PSW r | egister c                  | ontains t                         | he followi                       | ng sele  | ct bits: |         |  |

| GIE       | Global                     | interrupt                         | enable (e                        | nables   | interrup | ots)    |  |

| EXEN      | Enable                     | external                          | interrupt                        |          |          |         |  |

| BUSY      | MICRO                      | MICROWIRE/PLUS busy shifting flag |                                  |          |          |         |  |

| EXPND     | External interrupt pending |                                   |                                  |          |          |         |  |

| T1ENA     |                            |                                   | pt Enable<br>oture edge          |          | ner Un   | derflow |  |

| T1PNDA    | in mode                    |                                   | ot Pending<br>Inderflow<br>de 3) |          |          |         |  |

| С         | Carry F                    | lag                               |                                  |          |          |         |  |

| HC        | Half Ca                    | rry Flag                          |                                  |          |          |         |  |

| нсст      | 1PNDA                      | T1ENA                             | EXPND                            | BUSY     | EXEN     | I GIE   |  |

|           |                            |                                   |                                  |          |          |         |  |

Carry) instructions will respectively set or clear both the car-ry flags. In addition to the SC and RC instructions, ADC, SUBC, RRC and RLC instructions affect the carry and Half Carry flags.

|                    | egister (Address X′00E8)                                                                                              |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                    | L register contains the following bits:                                                                               |  |  |  |  |  |

| T1ENB              | Timer T1 Interrupt Enable for T1B Input capture edge                                                                  |  |  |  |  |  |

| T1PNDB             | Timer T1 Interrupt Pending Flag for T1B cap-                                                                          |  |  |  |  |  |

| WEN                | Enable MICROWIRE/PLUS interrupt                                                                                       |  |  |  |  |  |

| WPND               | MICROWIRE/PLUS interrupt pending                                                                                      |  |  |  |  |  |

| T0EN               | Timer T0 Interrupt Enable (Bit 12 toggle)                                                                             |  |  |  |  |  |

| <b>T0PND</b>       | Timer T0 Interrupt pending                                                                                            |  |  |  |  |  |

| LPENL              | Port Interrupt Enable (Multi-Input Wak-<br>eup/Interrupt)                                                             |  |  |  |  |  |

|                    | Bit 7 could be used as a flag                                                                                         |  |  |  |  |  |

| T2CNTRL            | Register (Address X'00C6)                                                                                             |  |  |  |  |  |

| Unused LP          | EN TOPND TOEN WPND WEN T1PNDB T1ENB                                                                                   |  |  |  |  |  |

| Bit 7              | Bit 0                                                                                                                 |  |  |  |  |  |

| The T2CNT          | RL register contains the following bits:                                                                              |  |  |  |  |  |

| T2ENB              | Timer T2 Interrupt Enable for T2B Input capture edge                                                                  |  |  |  |  |  |

| T2PNDB             | Timer T2 Interrupt Pending Flag for T2B cap-<br>ture edge                                                             |  |  |  |  |  |

| T2ENA              | Timer T2 Interrupt Enable for Timer Underflow or T2A Input capture edge                                               |  |  |  |  |  |

| T2PNDA             | Timer T2 Interrupt Pending Flag (Autoreload RA<br>in mode 1, T2 Underflow in mode 2, T2A cap-<br>ture edge in mode 3) |  |  |  |  |  |

| T2C0               | Timer T2 Start/Stop control in timer modes 1<br>and 2 Timer T2 Underflow Interrupt Pending<br>Flag in timer mode 3    |  |  |  |  |  |

| T2C1               | Timer T2 mode control bit                                                                                             |  |  |  |  |  |

| T2C2               | Timer T2 mode control bit                                                                                             |  |  |  |  |  |

| T2C3               | Timer T2 mode control bit                                                                                             |  |  |  |  |  |

| T2C3 T2C2<br>Bit 7 | PT2C1 T2C0 T2PNDA T2ENA T2PNDB T2ENB<br>Bit 0                                                                         |  |  |  |  |  |

|                    |                                                                                                                       |  |  |  |  |  |

### Timers

The device contains a very versatile set of timers (T0, T1, T2). All timers and associated autoreload/capture registers power up containing random data.

#### TIMER T0 (IDLE TIMER)

The device supports applications that require maintaining real time and low power with the IDLE mode. This IDLE mode support is furnished by the IDLE timer T0, which is a 16-bit timer. The Timer T0 runs continuously at the fixed rate of the instruction cycle clock,  $t_c.$  The user cannot read or write to the IDLE Timer T0, which is a count down timer.

The Timer T0 supports the following functions:

Exit out of the Idle Mode (See Idle Mode description) WATCHDOG logic (See WATCHDOG description)

Start up delay out of the HALT mode

The IDLE Timer T0 can generate an interrupt when the thirteenth bit toggles. This toggle is latched into the T0PND pending flag, and will occur every 4 ms at the maximum clock frequency ( $t_c = 1 \ \mu$ s). A control flag T0EN allows the interrupt from the thirteenth bit of Timer T0 to be enabled or disabled. Setting T0EN will enable the interrupt, while resetting it will disable the interrupt.

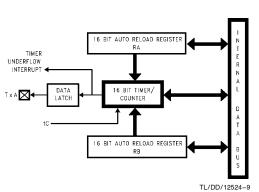

#### TIMER T1 AND TIMER T2

The device has a set of two powerful timer/counter blocks, T1 and T2. The associated features and functioning of a timer block are described by referring to the timer block Tx. Since the two timer blocks, T1 and T2, are identical, all comments are equally applicable to either timer block.

Each timer block consists of a 16-bit timer, Tx, and two supporting 16-bit autoreload/capture registers, RxA and RxB. Each timer block has two pins associated with it, TxA and TxB. The pin TxA supports I/O required by the timer block, while the pin TxB is an input to the timer block. The powerful and flexible timer block allows the device to easily perform all timer functions with minimal software overhead. The timer block has three operating modes: Processor Independent PWM mode, External Event Counter mode, and Input Capture mode.

The control bits TxC3, TxC2, and TxC1 allow selection of the different modes of operation.

#### Mode 1. Processor Independent PWM Mode

As the name suggests, this mode allows the device to generate a PWM signal with very minimal user intervention. The user only has to define the parameters of the PWM signal (ON time and OFF time). Once begun, the timer block will continuously generate the PWM signal completely independent of the microcontroller. The user software services the timer block only when the PWM parameters require updating.

In this mode the timer Tx counts down at a fixed rate of  $t_{\rm c}.$  Upon every underflow the timer is alternately reloaded with the contents of supporting registers, RxA and RxB. The very first underflow of the timer causes the timer to reload from the register RxA. Subsequent underflows cause the timer to be reloaded from the registers alternately beginning with the register RxB.

The Tx Timer control bits, TxC3, TxC2 and TxC1 set up the timer for PWM mode operation.

Figure 6 shows a block diagram of the timer in PWM mode.

### FIGURE 6. Timer in PWM Mode

The underflows can be programmed to toggle the TxA output pin. The underflows can also be programmed to generate interrupts.

Underflows from the timer are alternately latched into two pending flags, TxPNDA and TxPNDB. The user must reset these pending flags under software control. Two control enable flags, TxENA and TxENB, allow the interrupts from the timer underflow to be enabled or disabled. Setting the timer enable flag TxENA will cause an interrupt when a timer underflow causes the RxA register to be reloaded into the timer. Setting the timer enable flag TxENB will cause an interrupt when a timer underflow causes the RxB register to be reloaded into the timer. Resetting the timer enable flags will disable the associated interrupts.

Either or both of the timer underflow interrupts may be enabled. This gives the user the flexibility of interrupting once per PWM period on either the rising or falling edge of the PWM output. Alternatively, the user may choose to interrupt on both edges of the PWM output.

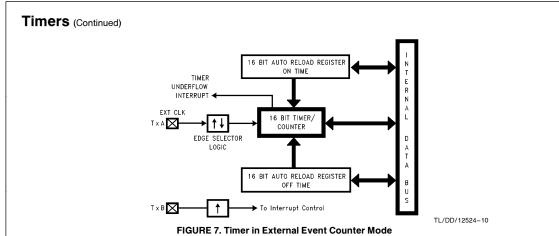

#### Mode 2. External Event Counter Mode

This mode is quite similar to the processor independent PWM mode described above. The main difference is that the timer, Tx, is clocked by the input signal from the TxA pin. The Tx timer control bits, TxC3, TxC2 and TxC1 allow the timer to be clocked either on a positive or negative edge from the TxA pin. Underflows from the timer are latched into the TxPNDA pending flag. Setting the TxENA control flag will cause an interrupt when the timer underflows.

In this mode the input pin TxB can be used as an independent positive edge sensitive interrupt input if the TxENB control flag is set. The occurrence of a positive edge on the TxB input pin is latched into the TxPNDB flag.

*Figure 7* shows a block diagram of the timer in External Event Counter mode.

Note: The PWM output is not available in this mode since the TxA pin is being used as the counter input clock.

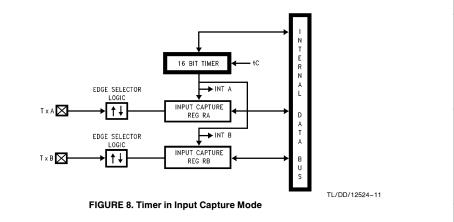

Mode 3. Input Capture Mode

The device can precisely measure external frequencies or time external events by placing the timer block, Tx, in the input capture mode.

In this mode, the timer Tx is constantly running at the fixed  $t_{\rm C}$  rate. The two registers, RxA and RxB, act as capture registers. Each register acts in conjunction with a pin. The register RxA acts in conjunction with the TxA pin and the register RxB acts in conjunction with the TxB pin.

The timer value gets copied over into the register when a trigger event occurs on its corresponding pin. Control bits, TxC3, TxC2 and TxC1, allow the trigger events to be specified either as a positive or a negative edge. The trigger condition for each input pin can be specified independently.

The trigger conditions can also be programmed to generate interrupts. The occurrence of the specified trigger condition on the TxA and TxB pins will be respectively latched into the pending flags, TxPNDA and TxPNDB. The control flag TxENA allows the interrupt on TxA to be either enabled or disabled. Setting the TxENA flag enables interrupts to be generated when the selected trigger condition occurs on the TxA pin. Similarly, the flag TxENB controls the interrupts from the TxB pin.

Underflows from the timer can also be programmed to generate interrupts. Underflows are latched into the timer TxC0 pending flag (the TxC0 control bit serves as the timer underflow interrupt pending flag in the Input Capture mode). Consequently, the TxC0 control bit should be reset when entering the Input Capture mode. The timer underflow interrupt is enabled with the TxENA control flag. When a TxA interrupt occurs in the Input Capture mode, the user must check both whether a TxA input capture or a timer underflow (or both) caused the interrupt.

*Figure 8* shows a block diagram of the timer in Input Capture mode.

#### TIMER CONTROL FLAGS

The timers T1 and T2 have indentical control structures. The control bits and their functions are summarized below.

- TxC0 Timer Start/Stop control in Modes 1 and 2 (Processor Independent PWM and External Event Counter), where 1 = Start, 0 = Stop Timer Underflow Interrupt Pending Flag in Mode 3 (Input Capture)

- TxPNDA Timer Interrupt Pending Flag

- TxPNDB Timer Interrupt Pending Flag

- TxENA Timer Interrupt Enable Flag

- TxENB Timer Interrupt Enable Flag

- 1 = Timer Interrupt Enabled

- 0 = Timer Interrupt Disabled

- TxC3 Timer mode control

- TxC2 Timer mode control

- TxC1 Timer mode control

| ТхСЗ | TxC2 | TxC1 | Timer Mode                                                      | Interrupt A<br>Source                     | Interrupt B<br>Source | Timer<br>Counts Or |

|------|------|------|-----------------------------------------------------------------|-------------------------------------------|-----------------------|--------------------|

| 0    | 0    | 0    | MODE 2 (External<br>Event Counter)                              | Timer<br>Underflow                        | Pos. TxB<br>Edge      | TxA<br>Pos. Edge   |

| 0    | 0    | 1    | MODE 2 (External<br>Event Counter)                              | Timer<br>Underflow                        | Pos. TxB<br>Edge      | TxA<br>Neg. Edge   |

| 1    | 0    | 1    | MODE 1 (PWM)<br>TxA Toggle                                      | Autoreload<br>RA                          | Autoreload<br>RB      | t <sub>c</sub>     |

| 1    | 0    | 0    | MODE 1 (PWM)<br>No TxA Toggle                                   | Autoreload<br>RA                          | Autoreload<br>RB      | t <sub>c</sub>     |

| 0    | 1    | 0    | MODE 3 (Capture)<br>Captures:<br>TxA Pos. Edge<br>TxB Pos. Edge | Pos. TxA<br>Edge or<br>Timer<br>Underflow | Pos. TxB<br>Edge      | t <sub>c</sub>     |

| 1    | 1    | 0    | MODE 3 (Capture)<br>Captures:<br>TxA Pos. Edge<br>TxB Neg. Edge | Pos. TxA<br>Edge or<br>Timer<br>Underflow | Neg. TxB<br>Edge      | t <sub>c</sub>     |

| 0    | 1    | 1    | MODE 3 (Capture)<br>Captures:<br>TxA Neg. Edge<br>TxB Pos. Edge | Neg. TxA<br>Edge or<br>Timer<br>Underflow | Pos. TxB<br>Edge      | t <sub>c</sub>     |

| 1    | 1    | 1    | MODE 3 (Capture)<br>Captures:<br>TxA Neg. Edge<br>TxB Neg. Edge | Neg. TxA<br>Edge or<br>Timer<br>Underflow | Neg. TxB<br>Edge      | t <sub>c</sub>     |

### **Power Save Modes**

The device offers the user two power save modes of operation: HALT and IDLE. In the HALT mode, all microcontroller activities are stopped. In the IDLE mode, the on-board oscillator circuitry and timer T0 are active but all other microcontroller activities are stopped. In either mode, all on-board RAM, registers, I/O states, and timers (with the exception of T0) are unaltered.

### HALT MODE

The device is placed in the HALT mode by writing a "1" to the HALT flag (G7 data bit). All microcontroller activities, including the clock, timers, are stopped. The WATCHDOG logic is disabled during the HALT mode. However, the clock monitor circuitry, if enabled, remains active and will cause the WATCHDOG output pin (WDOUT) to go low. If the HALT mode is used and the user does not want to activate the WDOUT pin, the Clock Monitor should be disabled after the device comes out of reset (resetting the Clock Monitor control bit with the first write to the WDSVR register). In the HALT mode, the power requirements are minimal and the applied voltage (V<sub>CC</sub>) may be decreased to Vr (Vr = 2.0V) without altering the state of the machine.

The device supports three different ways of exiting the HALT mode. The first method of exiting the HALT mode is

with the Multi-Input Wakeup feature on the L port. The second method is with a low to high transition on the CKO (G7) pin. This method precludes the use of the crystal clock configuration (since CKO becomes a dedicated output), and so may be used with an RC clock configuration. The third method of exiting the HALT mode is by pulling the RESET pin low.

Since a crystal or ceramic resonator may be selected as the oscillator, the Wakeup signal is not allowed to start the chip running immediately since crystal oscillators and ceramic resonators have a delayed start up time to reach full amplitude and frequency stability. The IDLE timer is used to generate a fixed delay to ensure that the oscillator has indeed stabilized before allowing instruction execution. In this case, upon detecting a valid Wakeup signal, only the oscillator circuitry is enabled. The IDLE timer is loaded with a value of 256 and is clocked with the t<sub>c</sub> instruction cycle clock. The t<sub>c</sub> clock is derived by dividing the oscillator clock down by a factor of 10. The Schmitt trigger following the CKI inverter on the chip ensures that the IDLE timer is clocked only when the oscillator has a sufficiently large amplitude to meet the Schmitt trigger specifications. This Schmitt trigger is not part of the oscillator closed loop. The startup timeout from the IDLE timer enables the clock signals to be routed to the rest of the chip.

### Power Save Modes (Continued)

If an RC clock option is being used, the fixed delay is introduced optionally. A control bit, CLKDLY, mapped as configuration bit G7, controls whether the delay is to be introduced or not. The delay is included if CLKDLY is set, and excluded if CLKDLY is reset. The CLKDLY bit is cleared on reset.

The WATCHDOG detector circuit is inhibited during the HALT mode. However, the clock monitor circuit, if enabled, remains active during HALT mode in order to ensure a clock monitor error if the device inadvertently enters the HALT mode as a result of a runaway program or power glitch.

#### IDLE MODE

The device is placed in the IDLE mode by writing a "1" to the IDLE flag (G6 data bit). In this mode, all activity, except the associated on-board oscillator circuitry, the WATCH-DOG logic, the clock monitor and the IDLE Timer T0, is stopped.

As with the HALT mode, the device can be returned to normal operation with a reset, or with a Multi-Input Wake-up from the L Port. Alternately, the microcontroller resumes normal operation from the IDLE mode when the thirteenth bit (representing 4.096 ms at internal clock frequency of 1 MHz,  $t_c=1~\mu s)$  of the IDLE Timer toggles.

This toggle condition of the thirteenth bit of the IDLE Timer T0 is latched into the T0PND pending flag.

The user has the option of being interrupted with a transition on the thirteenth bit of the IDLE Timer T0. The interrupt can be enabled or disabled via the T0EN control bit. Setting the T0EN flag enables the interrupt and vice versa.

The user can enter the IDLE mode with the Timer T0 interrupt enabled. In this case, when the T0PND bit gets set, the device will first execute the Timer T0 interrupt service routine and then return to the instruction following the "Enter Idle Mode" instruction.

Alternatively, the user can enter the IDLE mode with the IDLE Timer T0 interrupt disabled. In this case, the device will resume normal operation with the instruction immediately following the "Enter IDLE Mode" instruction.

Note: It is necessary to program two NOP instructions following both the set HALT mode and set IDLE mode instructions. These NOP instructions are necessary to allow clock resynchronization following the HALT or IDLE modes. Due to the on-board 8k EPROM with port recreation logic, the HALT/IDLE current is much higher compared to the equivalent masked device (COP888CL/COP884CL).

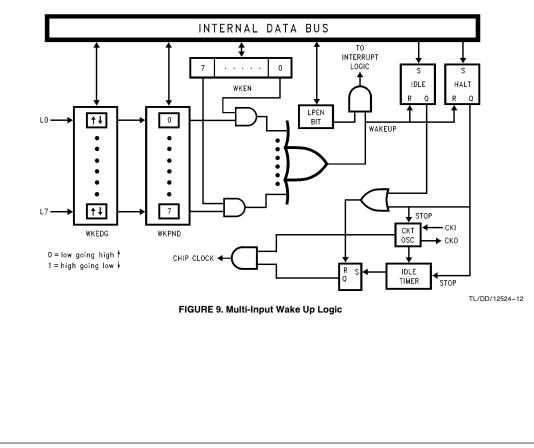

### Multi-Input Wakeup

The Multi-Input Wakeup feature is used to return (wakeup) the device from either the HALT or IDLE modes. Alternately Multi-Input Wakeup/Interrupt feature may also be used to generate up to 8 edge selectable external interrupts.

Figure 9 shows the Multi-Input Wakeup logic.

### Multi-Input Wakeup (Continued)

The Multi-Input Wakeup feature utilizes the L Port. The user selects which particular L port bit (or combination of L Port bits) will cause the device to exit the HALT or IDLE modes. The selection is done through the Reg: WKEN. The Reg: WKEN is an 8-bit read/write register, which contains a control bit for every L port bit. Setting a particular WKEN bit enables a Wakeup from the associated L port pin.

The user can select whether the trigger condition on the selected L Port pin is going to be either a positive edge (low to high transition) or a negative edge (high to low transition). This selection is made via the Reg: WKEDG, which is an 8-bit control register with a bit assigned to each L Port pin. Setting the control bit will select the trigger condition to be a negative edge on that particular L Port pin. Resetting the bit selects the trigger condition to be a positive edge. Changing an edge select entails several steps in order to avoid a pseudo Wakeup condition as a result of the edge change. First, the associated WKEN bit should be reset, followed by the edge select change in WKEDG. Next, the associated WKEN bit should be cleared, followed by the associated WKEN bit being re-enabled.

An example may serve to clarify this procedure. Suppose we wish to change the edge select from positive (low going high) to negative (high going low) for L Port bit 5, where bit 5 has previously been enabled for an input interrupt. The program would be as follows:

- RBIT 5, WKEN

- SBIT 5, WKEDG

- RBIT 5, WKPND

- SBIT 5, WKEN

If the L port bits have been used as outputs and then changed to inputs with Multi-Input Wakeup/Interrupt, a safety procedure should also be followed to avoid inherited pseudo wakeup conditions. After the selected L port bits have been changed from output to input but before the associated WKEN bits are enabled, the associated edge select bits in WKEDG should be set or reset for the desired edge selects, followed by the associated WKPND bits being cleared.

This same procedure should be used following reset, since the L port inputs are left floating as a result of reset.

The occurrence of the selected trigger condition for Multi-Input Wakeup is latched into a pending register called WKPND. The respective bits of the WKPND register will be set on the occurrence of the selected trigger edge on the corresponding Port L pin. The user has the responsibility of clearing these pending flags. Since WKPND is a pending register for the occurrence of selected wakeup conditions, the device will not enter the HALT mode if any Wakeup bit is both enabled and pending. Consequently, the user has the responsibility of clearing the pending flags before attempting to enter the HALT mode.

The WKEN, WKPND and WKEDG are all read/write registers, and are cleared at reset.

#### **PORT L INTERRUPTS**

Port L provides the user with an additional eight fully selectable, edge sensitive interrupts which are all vectored into the same service subroutine.

The interrupt from Port L shares logic with the wake up circuitry. The register WKEN allows interrupts from Port L to be individually enabled or disabled. The register WKEDG specifies the trigger condition to be either a positive or a negative edge. Finally, the register WKPND latches in the pending trigger conditions.

The GIE (Global Interrupt Enable) bit enables the interrupt function. A control flag, LPEN, functions as a global interrupt enable for Port L interrupts. Setting the LPEN flag will enable interrupts and vice versa. A separate global pending flag is not needed since the register WKPND is adequate.

Since Port L is also used for waking the device out of the HALT or IDLE modes, the user can elect to exit the HALT or IDLE modes either with or without the interrupt enabled. If he elects to disable the interrupt, then the device will restart execution from the instruction immediately following the instruction that placed the microcontroller in the HALT or IDLE modes. In the other case, the device will first execute the interrupt service routine and then revert to normal operation.

The Wakeup signal will not start the chip running immediately since crystal oscillators or ceramic resonators have a finite start up time. The IDLE Timer (T0) generates a fixed delay to ensure that the oscillator has indeed stabilized before allowing the execution of instructions. In this case, upon detecting a valid Wakeup signal, only the oscillator circuitry and the IDLE Timer T0 are enabled. The IDLE Timer is loaded with a value of 256 and is clocked from the  $t_{\rm c}$ instruction cycle clock. The  $t_{\mbox{c}}$  clock is derived by dividing down the oscillator clock by a factor of 10. A Schmitt trigger following the CKI on-chip inverter ensures that the IDLE timer is clocked only when the oscillator has a sufficiently large amplitude to meet the Schmitt trigger specifications. This Schmitt trigger is not part of the oscillator closed loop. The startup timeout from the IDLE timer enables the clock signals to be routed to the rest of the chip.

If the RC clock option is used, the fixed delay is under software control. A control flag, CLKDLY, in the G7 configuration bit allows the clock start up delay to be optionally inserted. Setting CLKDLY flag high will cause clock start up delay to be inserted and resetting it will exclude the clock start up delay. The CLKDLY flag is cleared during reset, so the clock start up delay is not present following reset with the RC clock options.

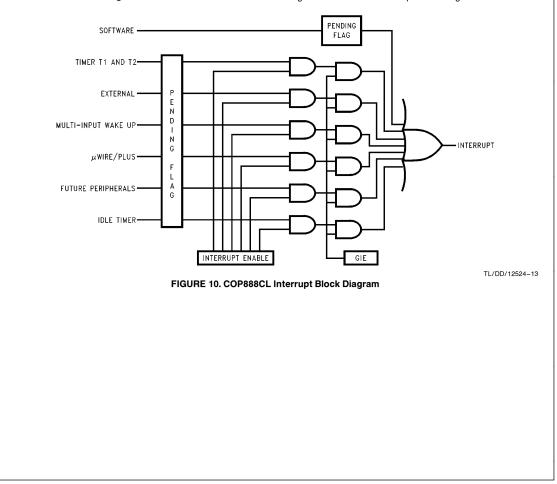

### Interrupts

The device supports a vectored interrupt scheme. It supports a total of ten interrupt sources. The following table lists all the possible interrupt sources, their arbitration ranking and the memory locations reserved for the interrupt vector for each source.

| Venter                 |                |                                                |                                  |  |

|------------------------|----------------|------------------------------------------------|----------------------------------|--|

| Arbitration<br>Ranking | Source         | Description                                    | Vector<br>Address<br>Hi-Low Byte |  |

| (1) Highest            | Software       | INTR Instruction                               | 0yFE-0yFF                        |  |

| (2)                    | Reserved       | for Future Use                                 | 0yFC-0yFD                        |  |

| (3)                    | External       | Pin G0 Edge                                    | 0yFA-0yFB                        |  |

| (4)                    | Timer T0       | Underflow                                      | 0yF8-0yF9                        |  |

| (5)                    | Timer T1       | T1A/Underflow                                  | 0yF6-0yF7                        |  |

| (6)                    | Timer T1       | T1B                                            | 0yF4-0yF5                        |  |

| (7)                    | MICROWIRE/PLUS | BUSY Goes Low                                  | 0yF2-0yF3                        |  |

| (8)                    | Reserved       | for Future Use                                 | 0yF0-0yF1                        |  |

| (9)                    | Reserved       | for UART                                       | 0yEE-0yEF                        |  |

| (10)                   | Reserved       | for UART                                       | 0yEC-0yED                        |  |

| (11)                   | Timer T2       | T2A/Underflow                                  | 0yEA-0yEB                        |  |

| (12)                   | Timer T2       | T2B                                            | 0yE8-0yE9                        |  |

| (13)                   | Reserved       | for Future Use                                 | 0yE6-0yE7                        |  |

| (14)                   | Reserved       | for Future Use                                 | 0yE4-0yE5                        |  |

| (15)                   | Port L/Wakeup  | Port L Edge                                    | 0yE2-0yE3                        |  |

| (16) Lowest            | Default        | VIS Instr. Execution<br>without Any Interrupts | 0yE0-0yE1                        |  |

y is VIS page,  $y \neq 0$ .

Two bytes of program memory space are reserved for each interrupt source. All interrupt sources except the software interrupt are maskable. Each of the maskable interrupts have an Enable bit and a Pending bit. A maskable interrupt is active if its associated enable and pending bits are set. If GIE = 1 and an interrupt is active, then the processor will be interrupted as soon as it is ready to start executing an instruction except if the above conditions happen during the Software Trap service routine. This exception is described in the Software Trap sub-section.

The interruption process is accomplished with the INTR instruction (opcode 00), which is jammed inside the Instruction Register and replaces the opcode about to be executed. The following steps are performed for every interrupt:

- 1. The GIE (Global Interrupt Enable) bit is reset.

- 2. The address of the instruction about to be executed is pushed into the stack.

- 3. The PC (Program Counter) branches to address 00FF. This procedure takes 7 t<sub>c</sub> cycles to execute.

At this time, since GIE = 0, other maskable interrupts are disabled. The user is now free to do whatever context switching is required by saving the context of the machine in the stack with PUSH instructions. The user would then program a VIS (Vector Interrupt Select) instruction in order to branch to the interrupt service routine of the highest priority interrupt enabled and pending at the time of the VIS. Note that this is not necessarily the interrupt that caused the branch to address location 00FF Hex prior to the context switching.

Thus, if an interrupt with a higher rank than the one which caused the interruption becomes active before the decision of which interrupt to service is made by the VIS, then the interrupt with the higher rank will override any lower ones and will be acknowledged. The lower priority interrupt(s) are still pending, however, and will cause another interrupt immediately following the completion of the interrupt service routine associated with the higher priority interrupt just serviced. This lower priority interrupt will occur immediately following the RETI (Return from Interrupt) instruction at the end of the interrupt service.

### Interrupts (Continued)

Inside the interrupt service routine, the associated pending bit has to be cleared by software. The RETI (Return from Interrupt) instruction at the end of the interrupt service routine will set the GIE (Global Interrupt Enable) bit, allowing the processor to be interrupted again if another interrupt is active and pending.

The VIS instruction looks at all the active interrupts at the time it is executed and performs an indirect jump to the beginning of the service routine of the one with the highest rank.

The addresses of the different interrupt service routines, called vectors, are chosen by the user and stored in ROM in a table starting at 01E0 (assuming that VIS is located between 00FF and 01DF). The vectors are 15-bit wide and therefore occupy 2 ROM locations.

VIS and the vector table must be located in the same 256-byte block (0y00 to 0yFF) except if VIS is located at the last address of a block. In this case, the table must be in the next block. The vector table cannot be inserted in the first 256-byte block.

The vector of the maskable interrupt with the lowest rank is located at 0yE0 (Hi-Order byte) and 0yE1 (Lo-Order byte) and so forth in increasing rank number. The vector of the

maskable interrupt with the highest rank is located at 0yFA (Hi-Order byte) and 0yFB (Lo-Order byte).

The Software Trap has the highest rank and its vector is located at 0yFE and 0yFF.

If, by accident, a VIS gets executed and no interrupt is active, then the PC (Program Counter) will branch to a vector located at 0yE0-0yE1.

#### WARNING

A Default VIS interrupt handler routine must be present. As a minimum, this handler should confirm that the GIE bit is cleared (this indicates that the interrupt sequence has been taken), take care of any required housekeeping, restore context and return. Some sort of Warm Restart procedure should be implemented. These events can occur without any error on the part of the system designer or programmer.

Note: There is always the possibility of an interrupt occurring during an instruction which is attempting to reset the GIE bit or any other interrupt enable bit. If this occurs when a single cycle instruction is being used to reset the interrupt enable bit, the interrupt enable bit will be reset but an interrupt may still occur. This is because interrupt processing is started at the same time as the interrupt bit is being reset. To avoid this scenario, the user should always use a two, three, or four cycle instruction to reset interrupt enable bits.

Figure 10 shows the Interrupt block diagram.

## Interrupts (Continued)

#### SOFTWARE TRAP

The Software Trap (ST) is a special kind of non-maskable interrupt which occurs when the INTR instruction (used to acknowledge interrupts) is fetched from ROM and placed inside the instruction register. This may happen when the PC is pointing beyond the available ROM address space or when the stack is over-popped.

When an ST occurs, the user can re-initialize the stack pointer and do a recovery procedure (similar to reset, but not necessarily containing all of the same initialization procedures) before restarting.

The occurrence of an ST is latched into the ST pending bit. The GIE bit is not affected and the ST pending bit (not accessible by the user) is used to inhibit other interrupts and to direct the program to the ST service routine with the VIS instruction. The RPND instruction is used to clear the software interrupt pending bit. This bit is also cleared on reset.

The ST has the highest rank among all interrupts.

Nothing (except another ST) can interrupt an ST being serviced.

### WATCHDOG

The device contains a WATCHDOG and clock monitor. The WATCHDOG is designed to detect the user program getting stuck in infinite loops resulting in loss of program control or "runaway" programs. The Clock Monitor is used to detect the absence of a clock or a very slow clock below a specified rate on the CKI pin.

The WATCHDOG consists of two independent logic blocks: WD UPPER and WD LOWER. WD UPPER establishes the upper limit on the service window and WD LOWER defines the lower limit of the service window.

Servicing the WATCHDOG consists of writing a specific value to a WATCHDOG Service Register named WDSVR which is memory mapped in the RAM. This value is composed of three fields, consisting of a 2-bit Window Select, a 5-bit Key Data field, and the 1-bit Clock Monitor Select field. Table III shows the WDSVR register.

| TABLE III. WATCHDOG Service | Register (WDSVR) |

|-----------------------------|------------------|

|-----------------------------|------------------|

| Window<br>Select |   |   | к | ey Da | ta |   | Clock<br>Monitor |

|------------------|---|---|---|-------|----|---|------------------|

| Х                | Х | 0 | 1 | 1     | 0  | 0 | Y                |

| 7                | 6 | 5 | 4 | 3     | 2  | 1 | 0                |

The lower limit of the service window is fixed at 2048 instruction cycles. Bits 7 and 6 of the WDSVR register allow the user to pick an upper limit of the service window.

Table IV shows the four possible combinations of lower and upper limits for the WATCHDOG service window. This flexibility in choosing the WATCHDOG service window prevents any undue burden on the user software.

Bits 5, 4, 3, 2 and 1 of the WDSVR register represent the 5-bit Key Data field. The key data is fixed at 01100. Bit 0 of the WDSVR Register is the Clock Monitor Select bit.

### TABLE IV. WATCHDOG Service Window Select

| WDSVR<br>Bit 7 | WDSVR<br>Bit 6 | Service Window<br>(Lower-Upper Limits) |

|----------------|----------------|----------------------------------------|

| 0              | 0              | 2k–8k t <sub>c</sub> Cycles            |

| 0              | 1              | 2k-16k t <sub>c</sub> Cycles           |

| 1              | 0              | 2k-32k t <sub>c</sub> Cycles           |

| 1              | 1              | 2k-64k t <sub>c</sub> Cycles           |

### Clock Monitor

The Clock Monitor aboard the device can be selected or deselected under program control. The Clock Monitor is guaranteed not to reject the clock if the instruction cycle clock ( $1/t_c$ ) is greater or equal to 10 kHz. This equates to a clock input rate on CKI of greater or equal to 100 kHz.

### WATCHDOG Operation

The WATCHDOG and Clock Monitor are disabled during reset. The device comes out of reset with the WATCHDOG armed, the WATCHDOG Window Select (bits 6, 7 of the WDSVR Register) set, and the Clock Monitor bit (bit 0 of the WDSVR Register) enabled. Thus, a Clock Monitor error will occur after coming out of reset, if the instruction cycle clock frequency has not reached a minimum specified value, including the case where the oscillator fails to start.

The WDSVR register can be written to only once after reset and the key data (bits 5 through 1 of the WDSVR Register) must match to be a valid write. This write to the WDSVR register involves two irrevocable choices: (i) the selection of the WATCHDOG service window (ii) enabling or disabling of the Clock Monitor. Hence, the first write to WDSVR Register involves selecting or deselecting the Clock Monitor, select the WATCHDOG service window and match the WATCHDOG key data. Subsequent writes to the WDSVR register will compare the value being written by the user to the WATCHDOG service window value and the key data (bits 7 through 1) in the WDSVR Register. Table V shows the sequence of events that can occur.

The user must service the WATCHDOG at least once before the upper limit of the service window expires. The WATCHDOG may not be serviced more than once in every lower limit of the service window. The user may service the WATCHDOG as many times as wished in the time period between the lower and upper limits of the service window. The first write to the WDSVR Register is also counted as a WATCHDOG service.

The WATCHDOG has an output pin associated with it. This is the WDOUT pin, on pin 1 of the port G. WDOUT is active low. The WDOUT pin is in the high impedance state in the inactive state. Upon triggering the WATCHDOG, the logic will pull the WDOUT (G1) pin low for an additional 16  $t_c$ -32  $t_c$  cycles after the signal level on WDOUT pin goes below the lower Schmitt trigger threshold. After this delay, the device will stop forcing the WDOUT output low.

The WATCHDOG service window will restart when the WDOUT pin goes high It is recommended that the user tie the WDOUT pin back to  $V_{CC}$  through a resistor in order to pull WDOUT high.

A WATCHDOG service while the WDOUT signal is active will be ignored. The state of the WDOUT pin is not guaranteed on reset, but if it powers up low then the WATCHDOG will time out and WDOUT will enter high impedance state.

### WATCHDOG Operation (Continued)

TABLE V. WATCHDOG Service Actions

| Key<br>Data | Window<br>Data | Clock<br>Monitor | Action                                |

|-------------|----------------|------------------|---------------------------------------|

| Match       | Match          | Match            | Valid Service: Restart Service Window |

| Don't Care  | Mismatch       | Don't Care       | Error: Generate WATCHDOG Output       |

| Mismatch    | Don't Care     | Don't Care       | Error: Generate WATCHDOG Output       |

| Don't Care  | Don't Care     | Mismatch         | Error: Generate WATCHDOG Output       |

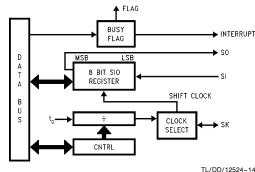

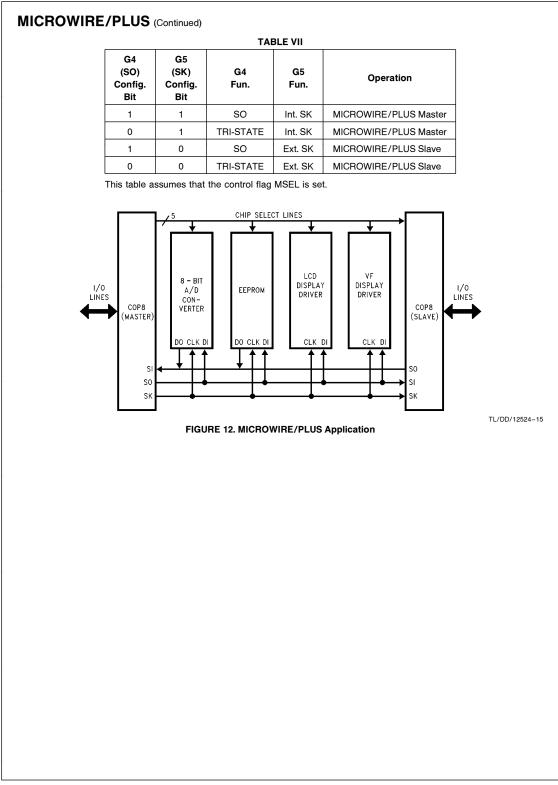

#### TABLE VI. MICROWIRE/PLUS Master Mode Clock Select

| SL1 | SL0 | SK             |