# MOS INTEGRATED CIRCUIT

# $\mu$ PD78323,78324

## 16/8-BIT SINGLE-CHIP MICROCONTROLLER

#### **DESCRIPTION**

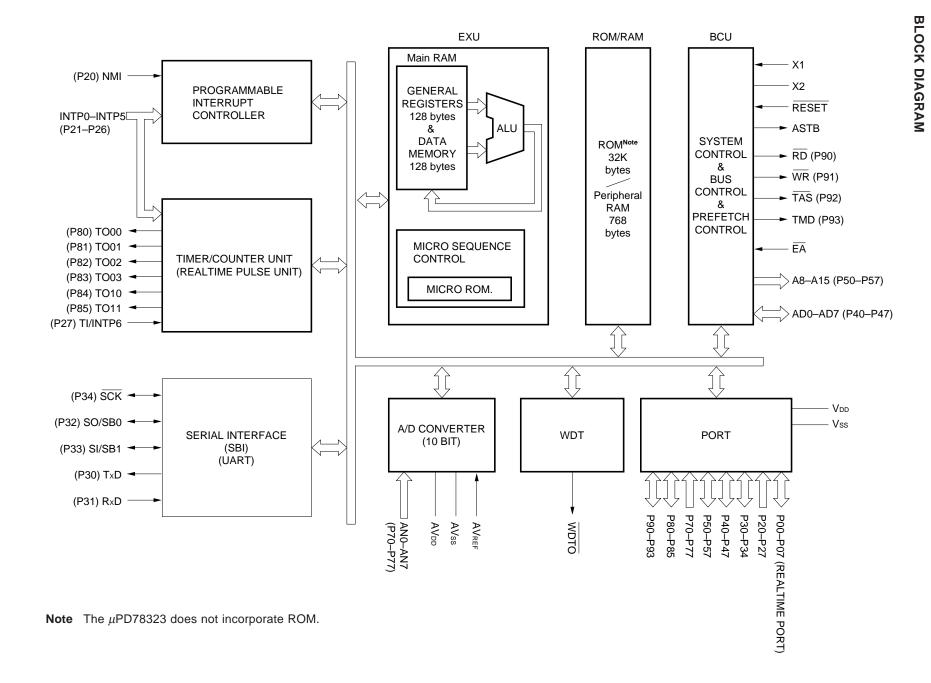

The  $\mu$ PD78324 is a 16/8-bit single-chip microcontroller that incorporates a high-performance 16-bit CPU. The  $\mu$ PD78324 is one of 78K/III series. The internal capacity is significantly increased compared with the conventional  $\mu$ PD78322.

A realtime pulse unit for realtime pulse control required in motor control, an A/D converter, a ROM, and a RAM have been integrated into one chip.

The  $\mu$ PD78324 incorporates 32K-byte mask ROM and 1024-byte RAM.

The  $\mu$ PD78323 is a ROM-less version of the  $\mu$ PD78324. Also, It is provided the  $\mu$ PD78P324 as an on-chip PROM product.

Detailed information about product features and specifications can be found in the following document.  $\mu$ PD78322 User's Manual : IEU-1248

#### **FEATURES**

- Internal 16-bit architecture and external 8-bit data bus

- · High-speed processing by pipeline control and instruction prefetch

- Minimum instruction execution time: 250 ns (with 16 MHz external clock in operation)

- Instruction set suitable for control operations (μPD78312 upward compatible)

- Multiply/divide instructions (16 bits × 16 bits, 32 bits ÷ 16 bits)

- · Bit manipulation instruction

- String instruction, etc.

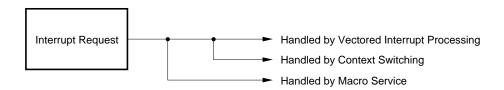

- · On-chip high-function interrupt controller

- 3-level priority specifiable

- 3-type interrupt processing mode selectable

(Vectored interrupt function, context switching function, and macro service function)

- Variety of peripheral hardware

- · Realtime pulse unit

- 8-channel, 10-bit A/D converter

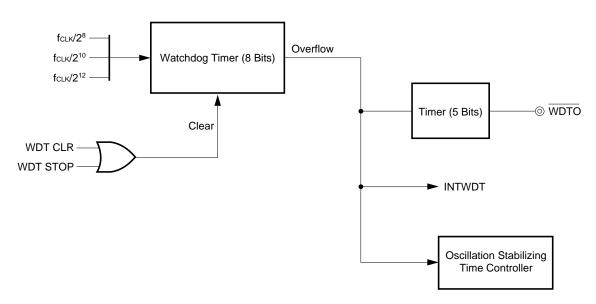

- Watchdog timer

- Powerful serial interface (with an on-chip dedicated baud rate generator)

• UART ..... 1 channel

- SBI (NEC Standard Serial Bus Interface) ..... 1 channel

- 3-wire serial I/O

#### **APPLICATIONS**

Motor control devices

Unless there are any particular differences, the  $\mu$ PD78324 is described as the representative model in this document.

The information in this document is subject to change without notice.

## ORDERING INFORMATION

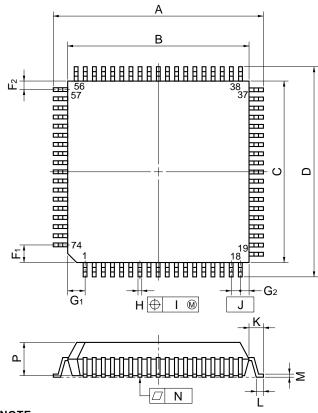

| Part Number                                  | Package                         | On-chip ROM |

|----------------------------------------------|---------------------------------|-------------|

| μPD78323GJ-5BJ                               | 74-pin plastic QFP (20 × 20 mm) | None        |

| μPD78323LP                                   | 68-pin plastic QFJ (□950 mil)   | None        |

| $\mu$ PD78324GJ- $\times \times \times$ -5BJ | 74-pin plastic QFP (20 × 20 mm) | Mask ROM    |

| $\mu$ PD78324LP- $\times \times \times$      | 68-pin plastic QFJ (□950 mil)   | Mask ROM    |

**Remark**  $\times \times \times$  Indicates ROM code number.

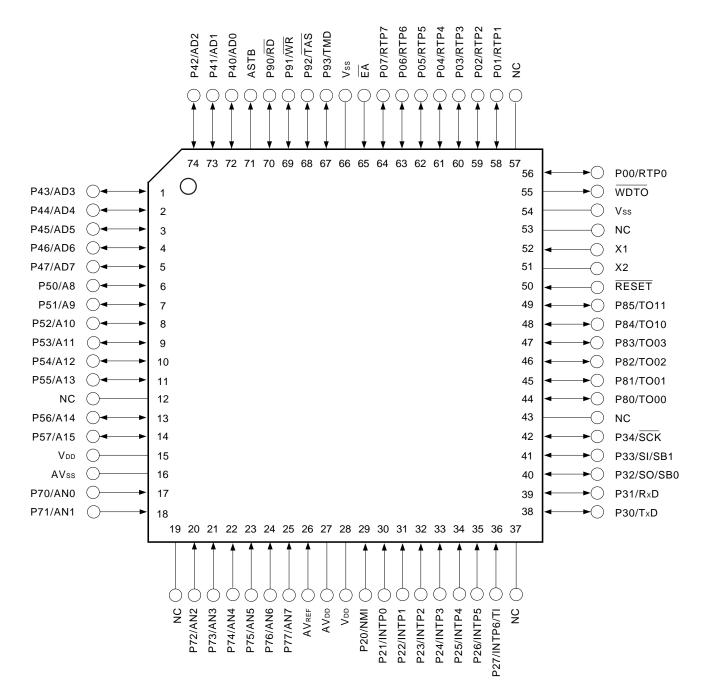

## PIN CONFIGURATION

• 74-pin plastic QFP (20  $\times$  20 mm)  $\mu$ PD78323GJ-5BJ  $\mu$ PD78324GJ- $\times\times$ -5BJ

Caution The NC pin should be connected to VSS for noise control (can also be left open).

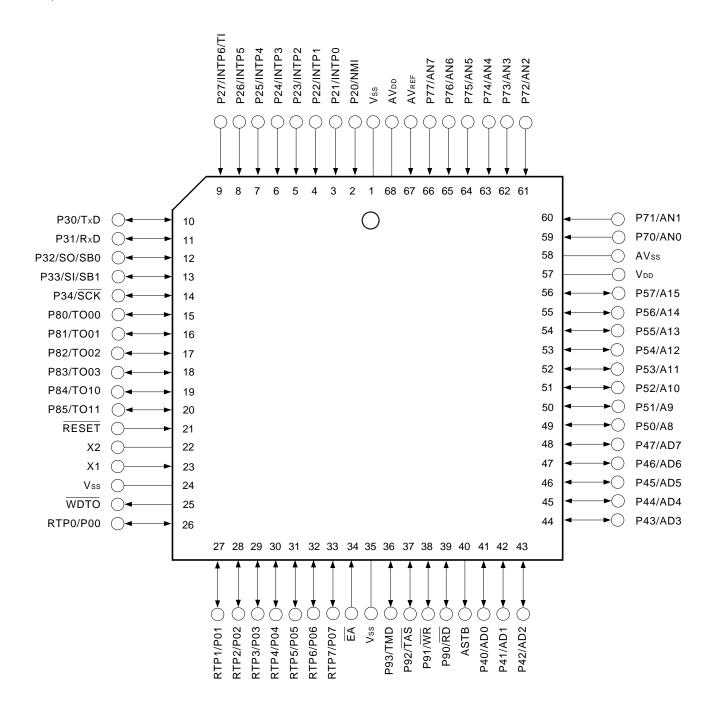

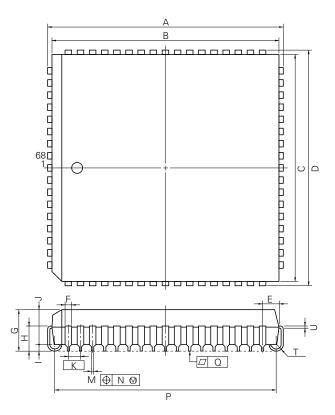

• 68-pin plastic QFJ ( $\square$  950 mil)  $\mu$ PD78323LP  $\mu$ PD78324LP- $\times\times$

| INTP0 to INTP6 : Interrupt F RTP0 to RTP7 : Realtime F TI : Timer Inpu TxD : Transmit I RxD : Receive D SB0/SO : Serial Bus | Port<br>ut<br>Data<br>ata<br>/Serial Output<br>/Serial Input<br>ck | X1, X2 WDTO EA TMD TAS WR RD ASTB AD0 to AD7 A8 to A15 AN0 to AN7 AVREF AVSS AVDD VDD VSS | : Reset : Crystal : Watchdog Timer Output : External Access : Turbo Mode : Turbo Access Strobe : Write Strobe : Read Strobe : Address Strobe : Address Strobe : Address Bus : Analog Input : Analog Reference Voltage : Analog Vss : Analog VDD : Power Supply : Ground : Non-connection |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## **GENERAL DESCRIPTION OF FUNCTIONS**

| Basic instructions                                                                                                                                                          | 111                                                                                                                                                                                                   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Minimum instruction execution time                                                                                                                                          | 250 ns (with 16 MHz external clock in operation)                                                                                                                                                      |  |

| Internal memory                                                                                                                                                             | <ul> <li>ROM : 32K bytes (μPD78324)         None (μPD78323)     </li> <li>RAM : 1K bytes</li> </ul>                                                                                                   |  |

| Memory space                                                                                                                                                                | 64K bytes                                                                                                                                                                                             |  |

| General registers                                                                                                                                                           | 8 bits × 16 × 8 banks (memory mapping)                                                                                                                                                                |  |

| I/O line                                                                                                                                                                    | <ul> <li>Input port : 16 (dual-function as analog input: 8)</li> <li>Input/output port : 39 (μPD78324)</li> <li>21 (μPD78323)</li> </ul>                                                              |  |

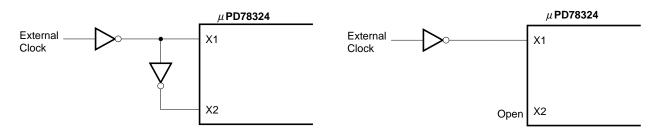

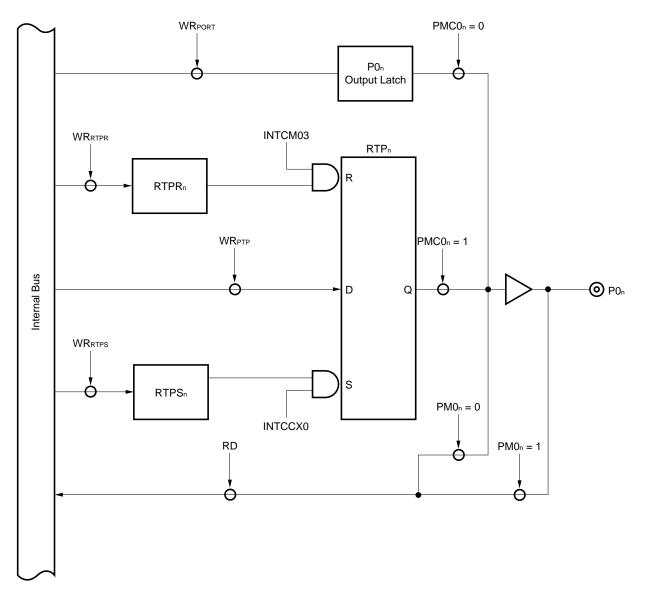

| Real-time pulse unit                                                                                                                                                        | • 18/16-bit free running timer × 1  • 16-bit timer/event counter × 1  • 16-bit compare register × 6  • 18-bit capture register × 4  • 18-bit capture/compare register × 2  • Realtime output port × 8 |  |

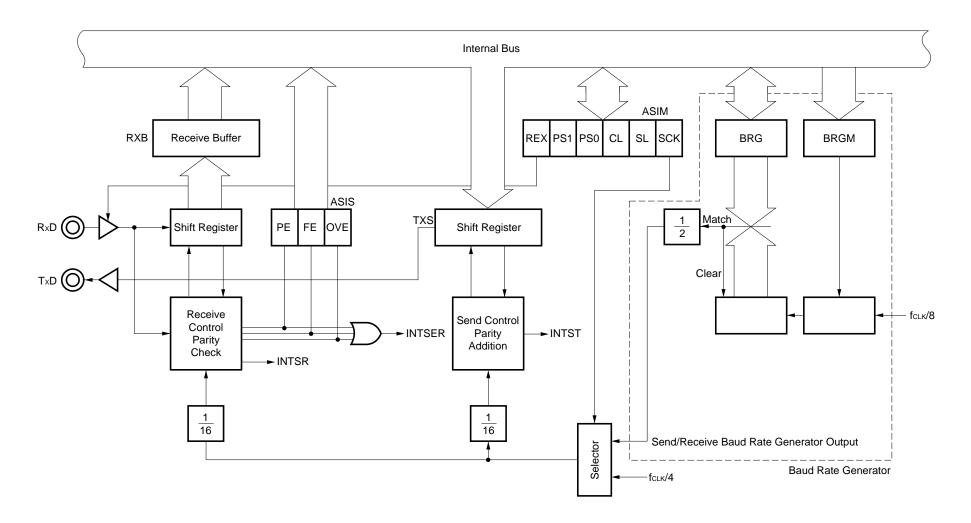

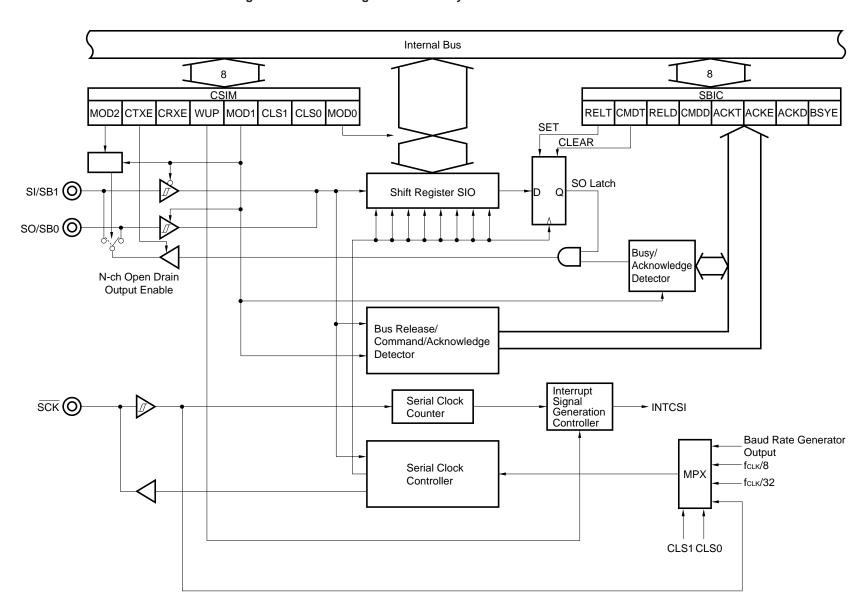

| Serial communication interface                                                                                                                                              | Serial interface with a dedicated baud rate generator  UART: 1 channel  SBI (NEC Serial Bus Interface): 1 channel                                                                                     |  |

| A/D converter                                                                                                                                                               | 10-bit resolution (8 analog inputs)                                                                                                                                                                   |  |

| External: 8, internal: 14 (dual-function as external: 2)     • 3 processing modes     (vectored interrupt function, context switching function, and macro service function) |                                                                                                                                                                                                       |  |

| Test factor Internal: 1                                                                                                                                                     |                                                                                                                                                                                                       |  |

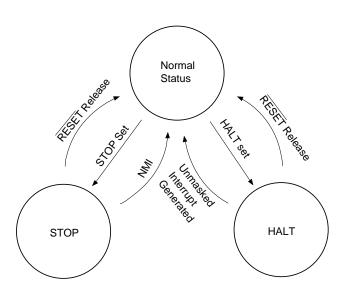

| Standby                                                                                                                                                                     | STOP mode/HALT mode                                                                                                                                                                                   |  |

| Instruction set                                                                                                                                                             | 16-bit transfer/operation instruction, multiplication/division instruction ( $16 \times 16$ , $32 \div 16$ ), bit manipulation instruction, string instruction, etc.                                  |  |

| Others                                                                                                                                                                      | On-chip watchdog timer                                                                                                                                                                                |  |

| Package                                                                                                                                                                     | • 68-pin plastic QFJ (□ 950 mil)     • 74-pin plastic QFP (20 × 20 mm)                                                                                                                                |  |

# DIFFERENCES BETWEEN $\mu$ PD78324 AND 78323

| Product Name Item                   |                  | μPD78324                                                                                                                                                                                                                                                                 | μPD78323                                                                                 |  |

|-------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| Internal ROM 32K bytes              |                  | 32K bytes                                                                                                                                                                                                                                                                | None                                                                                     |  |

|                                     | Input            | 16 (dual-function a                                                                                                                                                                                                                                                      | as analog input: 8)                                                                      |  |

| I/O line                            | Input<br>/output | 39                                                                                                                                                                                                                                                                       | 21                                                                                       |  |

| Port 4<br>(P40 to P                 | 47)              | Specifiable as I/O as an 8-bit unit. Functions as multiplexed address/data buses (AD0 to AD7) in the external memory expansion mode.                                                                                                                                     | Functions always as multiplexed address/data buses.                                      |  |

| Port 5<br>(P50 to P57)              |                  | Specifiable as I/O bit-wise. Functions as address bus (A8 to A15) in the external memory expansion mode.                                                                                                                                                                 | Functions always as address bus.                                                         |  |

| Port 9<br>(P90 to P93)              |                  | Specifiable as I/O bit-wise. In the external memory expansion mode, P90 and P91 function as RD strobe signal output and WR strobe signal output, respectively. In the external memory high-speed fetch mode, P92 P93 function as TAS output and TMD output respectively. | Always P90 and P91 function as RD strobe and WR strobe signal output, respectively.      |  |

| Memory expansion mode register (MM) |                  | Port 4 I/O mode is set as an 8-bit unit .                                                                                                                                                                                                                                | In the μPD78324 emulation mode, turbo acces acces manager (μPD71P301)Note PA and PB pins |  |

| Port 5 mode register (PM5)          |                  | Port 5 I/O mode is set bit-wise.                                                                                                                                                                                                                                         | are controlled as port 4 and port 5 emulation pins.                                      |  |

Note Maintenance product

+

# CONTENTS

| 1. | LIST OF PIN FUNCTIONS 11                 |                                                                     |    |  |  |  |

|----|------------------------------------------|---------------------------------------------------------------------|----|--|--|--|

|    | 1.1                                      | PORT PINS                                                           | 11 |  |  |  |

|    | 1.2                                      | PINS OTHER THAN PORTS                                               | 12 |  |  |  |

|    | 1.3                                      | PIN INPUT/OUTPUT CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS | 14 |  |  |  |

| 2. | CPU                                      | ARCHITECTURE                                                        | 16 |  |  |  |

|    | 2.1                                      | MEMORY SPACE                                                        | 16 |  |  |  |

|    | 2.2                                      | PROCESSOR REGISTERS                                                 | 19 |  |  |  |

|    |                                          | 2.2.1 Control Registers                                             | 20 |  |  |  |

|    |                                          | 2.2.2 General Registers                                             | 22 |  |  |  |

|    |                                          | 2.2.3 Special Function Registers (SFR)                              | 24 |  |  |  |

|    | 2.3                                      | DATA MEMORY ADDRESSING                                              | 29 |  |  |  |

|    |                                          | 2.3.1 General Register Addressing                                   | 29 |  |  |  |

|    |                                          | 2.3.2 Short Direct Addressing                                       | 29 |  |  |  |

|    |                                          | 2.3.3 Special Function Register (SFR) Addressing                    | 29 |  |  |  |

| 3. | BLO                                      | CK FUNCTIONS                                                        | 30 |  |  |  |

|    | 3.1                                      | BUS CONTROL UNIT (BCU)                                              | 30 |  |  |  |

|    | 3.2                                      | EXECUTION UNIT (EXU)                                                | 30 |  |  |  |

|    | 3.3                                      | ROM/RAM                                                             | 30 |  |  |  |

|    | 3.4                                      | INTERRUPT CONTROLLER                                                | 30 |  |  |  |

|    | 3.5                                      | PORT FUNCTIONS                                                      | 31 |  |  |  |

|    | 3.6                                      | CLOCK GENERATOR                                                     | 32 |  |  |  |

|    | 3.7                                      | REALTIME PULSE UNIT (RPU)                                           | 34 |  |  |  |

|    |                                          | 3.7.1 Configuration                                                 | 34 |  |  |  |

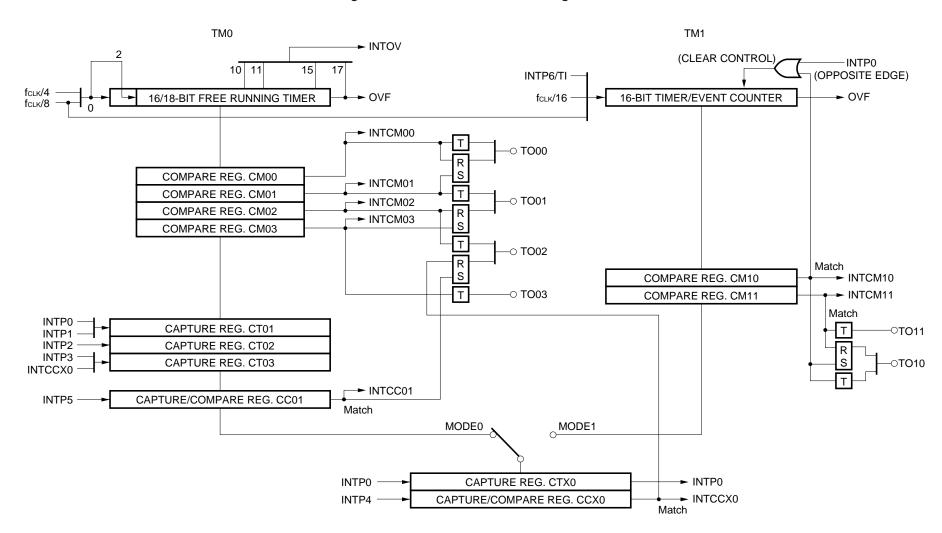

|    |                                          | 3.7.2 Realtime Output Function                                      | 36 |  |  |  |

|    | 3.8                                      | A/D CONVERTER                                                       | 37 |  |  |  |

|    | 3.9                                      | SERIAL INTERFACE                                                    | 37 |  |  |  |

|    | 3.10                                     | WATCHDOG TIMER                                                      | 40 |  |  |  |

| 4. | INTE                                     | RRUPT FUNCTIONS                                                     | 41 |  |  |  |

|    | 4.1                                      | OVERVIEW                                                            |    |  |  |  |

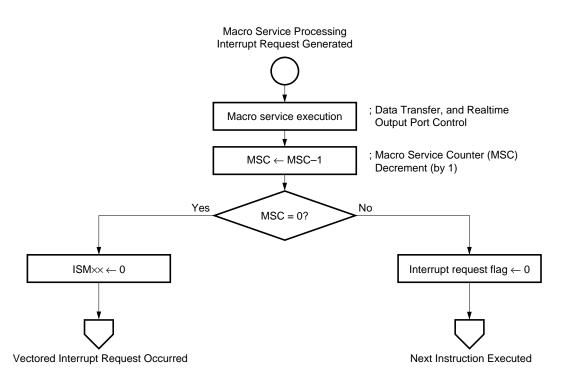

|    | 4.2                                      | MACRO SERVICE                                                       | 42 |  |  |  |

|    | 4.3                                      | CONTEXT SWITCHING FUNCTION                                          | 44 |  |  |  |

|    |                                          | 4.3.1 Context Switching Function at Interrupt Request               | 44 |  |  |  |

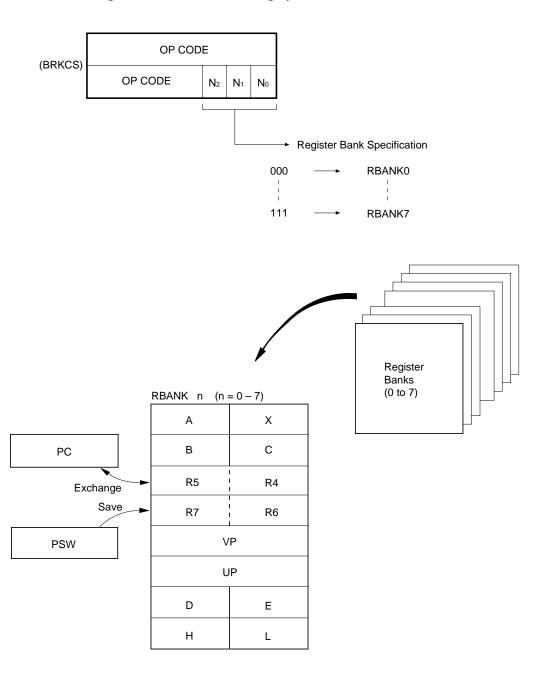

|    |                                          | 4.3.2 Context Switching Function by BRKCS Instruction               | 45 |  |  |  |

| 5. | STA                                      | NDBY FUNCTIONS                                                      | 46 |  |  |  |

| 6. | 6. EXTERNAL DEVICE EXPANSION FUNCTION 47 |                                                                     |    |  |  |  |

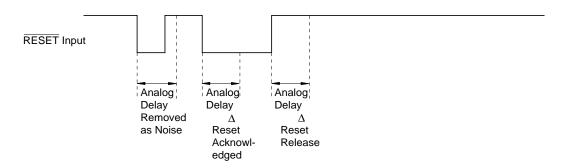

| 7. | OPE                                      | RATION AFTER RESET                                                  | 48 |  |  |  |

| 8. | INST                                     | RUCTION SET                                                         | 49 |  |  |  |

| 9. | ELE                                      | CTRICAL SPECIFICATIONS                                              | 63 |  |  |  |

| 10. PACKAGE DRAWINGS                        | 74   |

|---------------------------------------------|------|

| 11. RECOMMENDED SOLDERING CONDITIONS        | 76   |

| APPENDIX A. LIST OF 78K/III SERIES PRODUCTS | 77   |

| APPENDIX B. TOOLS                           | . 79 |

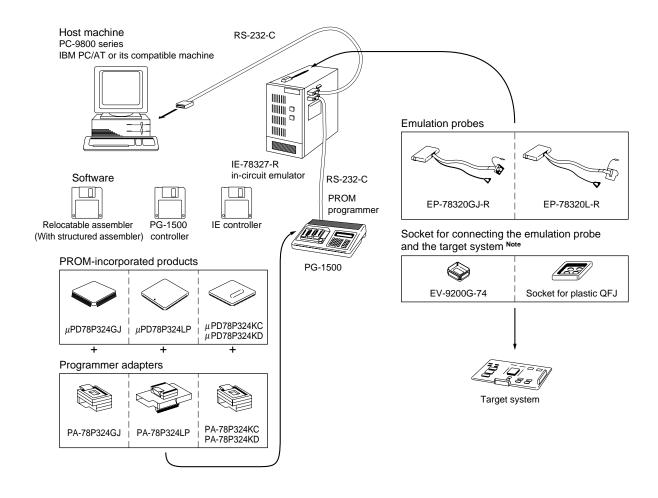

| B.1 DEVELOPMENT TOOLS                       | 79   |

| B.2 EVALUATION TOOLS                        | 83   |

| B.3 EMBEDDED SOFTWARE                       | 83   |

## 1. LIST OF PIN FUNCTIONS

## 1.1 PORT PINS

| Pin Name   | I/O              | Function                                                                                                     | Dual-<br>Function Pin |

|------------|------------------|--------------------------------------------------------------------------------------------------------------|-----------------------|

| P00 to P07 | Input/<br>output | Port 0 8-bit input/output port Input/output can be specified bit-wise Also serves as a realtime output port. | RTP0 to               |

| P20        |                  |                                                                                                              | NMI                   |

| P21        |                  |                                                                                                              | INTP0                 |

| P22        |                  |                                                                                                              | INTP1                 |

| P23        | 1                | Port 2                                                                                                       | INTP2                 |

| P24        | Input            | Dedicated port for 8-bit input                                                                               | INTP3                 |

| P25        |                  |                                                                                                              | INTP4                 |

| P26        |                  | INTP5                                                                                                        |                       |

| P27        |                  |                                                                                                              | INTP6/TI              |

| P30        |                  |                                                                                                              | TxD                   |

| P31        |                  | Port 3                                                                                                       | RxD                   |

| P32        | Input/           | 5-bit input/output port                                                                                      | SO/SB0                |

| P33        | output           | utput Input/output can be specified bit-wise                                                                 | SI/SB1                |

| P34        |                  |                                                                                                              | SCK                   |

| P40 to P47 | Input/<br>output | Port 4 8-bit input/output port Input/output can be specified in 8-bit unit.                                  | AD0 to AD7            |

| P50 to P57 | Input/<br>output | Port 5 8-bit input/output port Input/output can be specified bit-wise                                        | A8 to A15             |

| P70 to P77 | Input            | Port 7 Dedicated port for 8-bit input                                                                        | AN0 to AN7            |

| P80        |                  |                                                                                                              | TO00                  |

| P81        |                  |                                                                                                              | TO01                  |

| P82        | Input/           | Port 8 6-bit input/output port                                                                               | TO02                  |

| P83        | output           | Input/output can be specified bit-wise                                                                       | TO03                  |

| P84        |                  |                                                                                                              | TO10                  |

| P85        |                  |                                                                                                              | TO11                  |

| P90        |                  |                                                                                                              | RD                    |

| P91        | Input/           | Port 9 4-bit input/output port                                                                               | WR                    |

| P92        | output           | Input/output can be specified bit-wise                                                                       | TAS                   |

| P93        | 1                |                                                                                                              | TMD                   |

# 1.2 PINS OTHER THAN PORTS (1/2)

| Pin Name     | I/O              | Function                                                                                                                                           | Dual-<br>Function Pi |

|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| RTP0 to RTP7 | Output           | Realtime output port which generates pulses in synchronization with the trigger signal transmitted from the realtime pulse unit (RPU).             |                      |

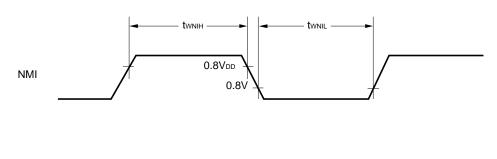

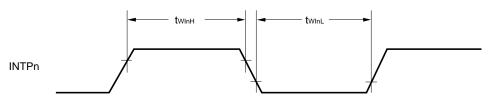

| NMI          | Input            | Nonmaskable interrupot request input capable of specifying the effective at the rising or falling edge by a mode register.                         |                      |

| INTP0        |                  |                                                                                                                                                    | P21                  |

| INTP1        |                  |                                                                                                                                                    | P22                  |

| INTP2        |                  |                                                                                                                                                    | P23                  |

| INTP3        | Input            | External interrupt request input capable of specifying the effective edgy by a mode                                                                | P24                  |

| INTP4        |                  | register.                                                                                                                                          | P25                  |

| INTP5        |                  |                                                                                                                                                    | P26                  |

| INTP6        |                  |                                                                                                                                                    | P27/TI               |

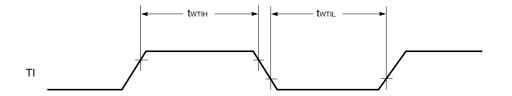

| TI           | Input            | External count clock input to timer 1 (TM1)                                                                                                        | P27/INTP             |

| TxD          | Output           | Serial data output of asynchronous serial interface (UART)                                                                                         | P30                  |

| RxD          | Input            | Serial data input of asynchronous serial interface (UART)                                                                                          | P31                  |

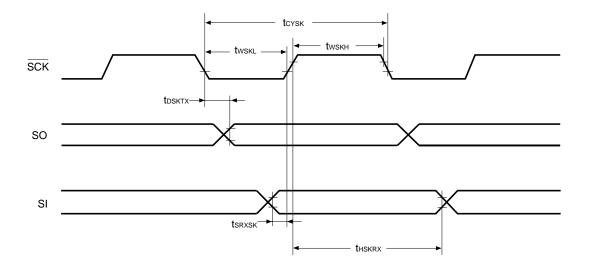

| SO           | Output           | Serial data output of clock synchronous serial interface in 3-wire mode                                                                            | P32/SB0              |

| SI           | Input            | Serial data input of clock synchronous serial interface in 3-wire mode                                                                             | P33/SB1              |

| SB0          | Input            | Serial data output of clock synchronous serial interface in SBI mode                                                                               |                      |

| SB1          | /output          |                                                                                                                                                    |                      |

| SCK          | Input<br>/output | Serial clock input/output of clock synchronous serial interface                                                                                    |                      |

| AD0 to AD7   | Input<br>/output | Multiplexed address/data bus for external memory expansion                                                                                         |                      |

| A8 to A15    | Output           | Address bus for external memory expansion                                                                                                          | P50 to P5            |

| TO00         |                  |                                                                                                                                                    | P80                  |

| TO01         |                  |                                                                                                                                                    | P81                  |

| TO02         |                  |                                                                                                                                                    | P82                  |

| TO03         | Output           | Pulse output from the realtime pulse unit                                                                                                          | P83                  |

| TO10         |                  |                                                                                                                                                    | P84                  |

| TO11         |                  |                                                                                                                                                    | P85                  |

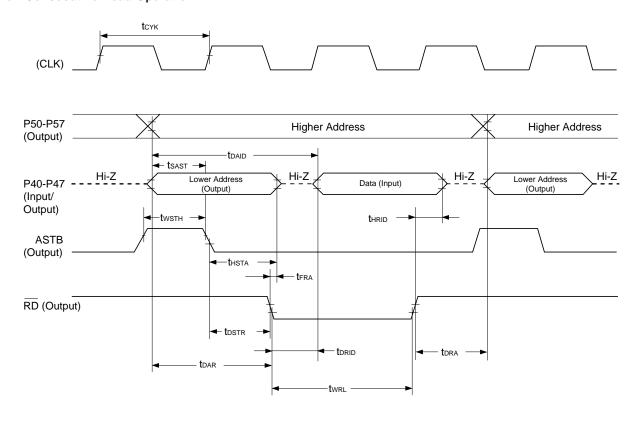

| RD           |                  | Strobe signal output generated for external memory read operation                                                                                  | P90                  |

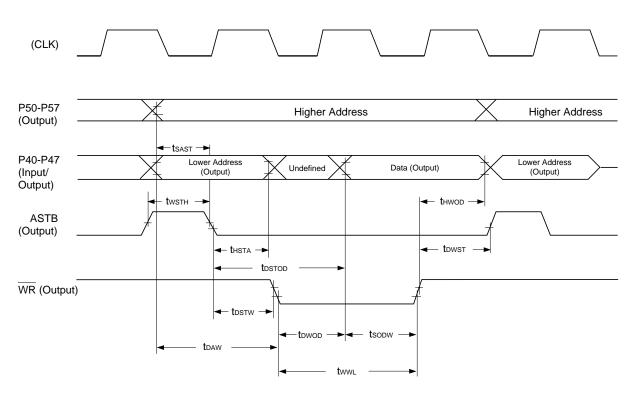

| WR           |                  | Strobe signal output generated for external memory write operation                                                                                 | P91                  |

| TAS          | Output           |                                                                                                                                                    | P92                  |

| TMD          |                  | Control signal output generated for access to turbo access manager μPD71P301Note                                                                   | P93                  |

| WDTO         | Output           | Signal output indicating that the watchdog timer has generated a nonmascable interrupt.                                                            |                      |

| ASTB         | Output           | Timing signal output generated for externally latching the address information output from pins AD0 to AD7 in order to access the external memory. |                      |

Note Maintenance product

## 1.2 PINS OTHER THAN PORTS (2/2)

| Pin Name        | I/O   | Function                                                                                                                                                                                                                                                                                                                                      |   |

|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| ĒĀ              | Input | In the $\mu$ PD78324, $\overline{\text{EA}}$ pin is normally connected to V <sub>DD</sub> . Connecting $\overline{\text{EA}}$ pin to Vss sets the ROM-less mode and accesses the external memory. In the $\mu$ PD78323, this pin should be fixed to "0" (low level). The $\overline{\text{EA}}$ pin level cannot be changed during operation. | _ |

| AN0 to AN7      | Input | A/D converter analog input.                                                                                                                                                                                                                                                                                                                   | _ |

| AVREF           | Input | A/D converter reference voltage input.                                                                                                                                                                                                                                                                                                        | _ |

| AVDD            | _     | A/D converter analog power supply                                                                                                                                                                                                                                                                                                             | _ |

| AVss            | _     | A/D converter GND                                                                                                                                                                                                                                                                                                                             | _ |

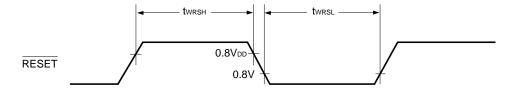

| RESET           | Input | System reset input                                                                                                                                                                                                                                                                                                                            |   |

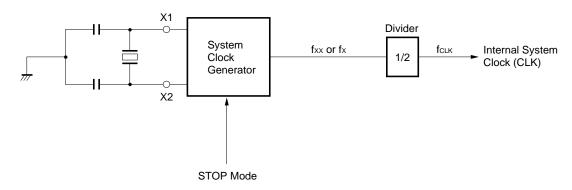

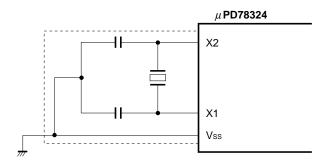

| X1              | Input | Crystal connect pin for sysem clock oscillation. When an external clock is supplied, the clock is input to X1 and the inverted clock is input to X2. (X2 can also be left open.)                                                                                                                                                              |   |

| X2              | _     |                                                                                                                                                                                                                                                                                                                                               |   |

| V <sub>DD</sub> |       | Positive power supply                                                                                                                                                                                                                                                                                                                         |   |

| Vss             | _     | GND pin                                                                                                                                                                                                                                                                                                                                       |   |

| NC              | _     | Not internally connected. Connected to Vss (GND) (can also be left open).                                                                                                                                                                                                                                                                     |   |

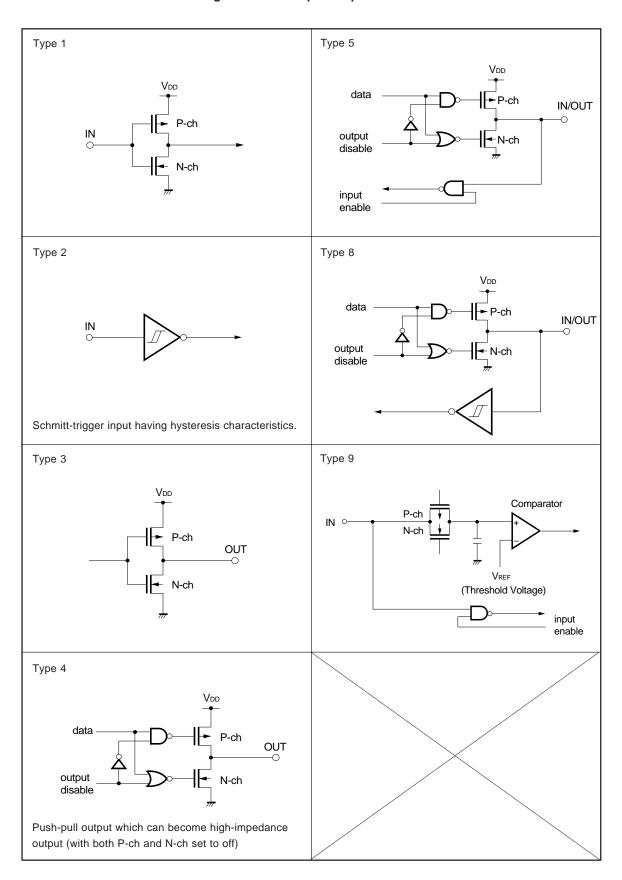

## 1.3 PIN INPUT/OUTPUT CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS

The pin input/output circuits, partly simplified, are shown in Table 1-1 and Figure 1-1.

Table 1-1. I/O Circuit Types of Pins and Their Recommended Connection Methods when Unused

| Pin                                               | Input/Output<br>Circuit Type | Recommended Connection Method                                                                                  |

|---------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------|

| P00/RTP0 to P07/RTP7                              | 5                            | Input mode : Individually connected to V <sub>DD</sub> or V <sub>SS</sub> via resistor Output mode: Leave open |

| P20/NMI<br>P21/INTP0 to P26/INTP5<br>P27/INTP6/TI | 2                            | Connected to Vss                                                                                               |

| P30/TxD<br>P31/RxD                                | 5                            |                                                                                                                |

| P32/SO/SB0<br>P33/SI/SB1<br>P34/SCK               | 8                            | Input mode : Individually connected to VDD or Vss via resistor Output mode: Leave open                         |

| P40/AD0 to P47/AD7<br>P50/A8 to P57/A15           | 5                            |                                                                                                                |

| P70/AN0 to P77/AN7                                | 9                            | Connected to Vss                                                                                               |

| P80/TO00 to P83/TO03<br>P84/TO10, P85/TO11        | 5                            |                                                                                                                |

| P90/RD<br>P91/WR<br>P92/TAS<br>P93/TMD            | 5                            | Input mode: Individually connected to Vod or Vss via resistor Output mode: Leave open                          |

| WDTO                                              | 3                            | Logy open                                                                                                      |

| ASTB                                              | 4                            | Leav open                                                                                                      |

| ĒĀ                                                | 1                            |                                                                                                                |

| RESET                                             | 2                            |                                                                                                                |

| AVREF, AVSS                                       |                              | Connected to Vss                                                                                               |

| AVDD                                              |                              | Connected to V <sub>DD</sub>                                                                                   |

| NC                                                |                              | Connected to Vss (can also be left open)                                                                       |

Figure 1-1. Pin Input/Output Circuits

## 2. CPU ARCHITECTURE

#### 2.1 MEMORY SPACE

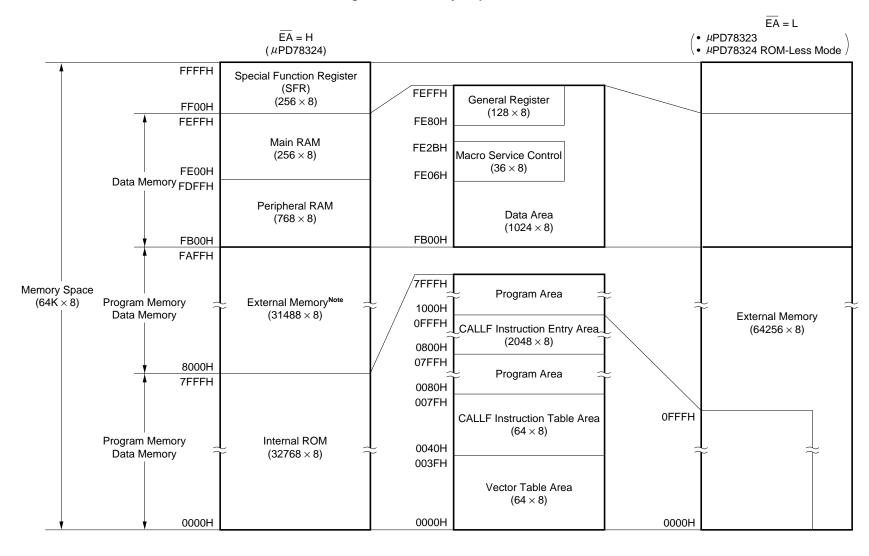

In the  $\mu$ PD78324 a maximum of 64K bytes of memory can be addressed (see **Figure 2-1**).

Program fetches can be performed within the area from 0000H to FDFFH. However, when external memory expansion is implemented in the area from FE00H to FFFFH (main RAM and special function register area), program fetches can also be performed on this area. In this case, a program fetch is performed on the external memory, not on the main RAM or special function registers.

## (1) Vector table area

Interrupt request from the peripheral hardware, reset input, external interrupt request and interrupt branch address by break instruction are stored in the 0000H to 003FH 64-byte area. Generation of an interrupt request sets the even address content of each table in the lower 8 bits of the program counter (PC) and the odd address content in the higher 8 bits.

| Interrupt Sour | ce \                                  | /ector | Table Address |

|----------------|---------------------------------------|--------|---------------|

| RESET          | (RESET pin input)                     |        | 0000H         |

| NMI            | (NMI pin input)                       |        | 0002H         |

| WDT            | (Watchdog timer)                      |        | 0004H         |

| TMF0           | (Realtime pulse unit)                 |        | 0006H         |

| EXF0           | (INTP0 pin input)                     |        | H8000         |

| EXF1           | (INTP1 pin input)                     |        | 000AH         |

| EXF2           | (INTP2 pin input)                     |        | 000CH         |

| EXF3           | (INTP3 pin input)                     |        | 000EH         |

| EXF4/CCFX0     | (INTP4 pin input/realtime pulse unit) |        | 0010H         |

| EXF5/CCFX1     | (INTP5 pin input/realtime pulse unit) |        | 0012H         |

| EXF6/TI        | (INTP6/TI pin input)                  |        | 0014H         |

| CMF00          | (Realtime pulse unit)                 |        | 0016H         |

| CMF01          | (Realtime pulse unit)                 |        | 0018H         |

| CMF02          | (Realtime pulse unit)                 |        | 001AH         |

| CMF03          | (Realtime pulse unit)                 |        | 001CH         |

| CMF10          | (Realtime pulse unit)                 |        | 001EH         |

| CMF11          | (Realtime pulse unit)                 |        | 0020H         |

| SRF            | (Serial receive complete)             |        | 0024H         |

| STF            | (Serial send complete)                |        | 0026H         |

| CSIIF          | (Clock synchronous serial interface)  |        | 0028H         |

| ADF            | (A/D converter)                       |        | 002AH         |

| Operation code | trap                                  |        | 003CH         |

| BRK            | (Break instruction)                   |        | 003EH         |

If bit 1 (TPF) of CPU control word (CCW) is set to 1, the 8002H to 803FH external memory area is used as an interrupt vector table in place of 0002H to 003FH.

## (2) CALLT table area

32 tables of call addresses of 1-byte call instruction (CALLT) can be stored in the 0040H to 007FH 64-byte area. If bit 1 (TPF) of CPU control word (CCW) is set to 1, the 8040H to 807FH external memory area is used as a CALLT instruction table in place of 0040H to 007FH.

## (3) CALLF entry area

The 0800H to 0FFFH area can be directly subroutine-called by 2-byte call instruction (CALLF).

#### (4) On-chip RAM area

A 1024-byte RAM is built in FB00H to FEFFH. This area is composed of the following 2 RAMs.

Peripheral RAM : FB00H to FDFFH (768 bytes)Main RAM : FE00H to FEFFH (256 bytes)

The main RAM can be accessed at high speed.

In the main RAM area, the macro service control word and general register group composed of 8 register banks are mapped onto the 36 bytes from FE06H to FE2BH and the 128 bytes from FE80H to FEFFH, respectively.

## (5) Special function register (SFR) area

Registers having specially assigned functions, such as on-chip peripheral hardware mode registers and control registers, are mapped in the FF00H to FFFFH area. Addresses without mapped registers cannot be accessed.

## (6) External memory area

The μPD78324 can add external memories (ROM, RAM) to the 32K-byte (8000H to FFFFH) area.

The  $\mu$ PD78323 can connect external memories (ROM, RAM) to the 64K-byte (0000H to FFFFH) area.

Each external memory can be accessed using P40/AD0 to P47/AD7 (multiplexed address/data bus), P50/A8 to P57/A15 (address bus) and  $\overline{RD}$ ,  $\overline{WR}$  and ASTB signals.

The external access area is mapped in the FFD0H to FFDFH 16-byte area of the special function register (SFR). In this way, the external memory can be accessed by SFR addressing.

Dedicated pins ( $\overline{TAS}$  and TMD pins) are provided to connect turbo access manager ( $\mu$ PD71P301)<sup>Note</sup>. If the  $\mu$ PD71P301 is used, the program processing speed equal to that of the on-chip ROM can be obtained.

Note Maintenance product

Figure 2-1. Memory Map

Note Accessed in external memory expansion mode.

Caution For word access (including stack operations) to the main RAM area (FE00H-FEFFH), the address that specifies the operand must be an even value.

## 2.2 PROCESSOR REGISTERS

The processor registers consist mainly of three groups. They are general registers consisting of 8 banks of sixteen 8-bit registers, control registers consisting of one 8-bit register and three 16-bit registers, and special function registers such as peripheral hardware I/O mode registers.

Control Registers

15

PC

PSW

SP

Figure 2-2. Register Configuration

CCW

Special Function Registers

| 7 0     | 7 0                       |

|---------|---------------------------|

| SFR 255 | SFR 254                   |

| SFR 253 | SFR 252                   |

| SFR 251 | SFR 250                   |

| SFR 249 | SFR 248                   |

| ≅       | $\widetilde{\mathcal{T}}$ |

| SFR 1   | SFR 0                     |

Remark The CCWs of the control registers are mapped in the special function register (SFR) area.

## 2.2.1 Control Register

The control registers carry out dedicated functions such as control of the program sequence, status and stack memory, and modification of operand addressing. They consist of three 16-bit registers and one 8-bit register.

## (1) Program counter (PC)

This is a 16-bit register which holds the address information of the next program to be executed. It is normally incremented according to the number of bytes of the instruction to be fetched. If an instruction with data branch is executed, immediate data and the register content are set. RESET input sets and branches the data of 0000H and 0001H reset vector tables in the PC.

## (2) Program status word (PSW)

This is a 16-bit register consisting of various flags which are set or reset by the result of instruction execution. Read/write access is carried out in units of the higher 8 bits (PSWH) or lower 8 bits (PSWL). Each flag can be operated using the bit operation instruction. If an interrupt request is made or BRK instruction is executed, data is automatically saved in the stack and is recovered by RETI or RETB instruction.

All bits are reset to 0 by RESET input.

Figure 2-3. PSW Format

## (a) Interrupt priority level transition flag (LT)

|      | 7  | 6    | 5    | 4    | 3  | 2   | 1  | 0  |

|------|----|------|------|------|----|-----|----|----|

| PSWH | UF | RBS2 | RBS1 | RBS0 | 0  | 0   | 0  | 0  |

|      | 7  | 6    | 5    | 4    | 3  | 2   | 1  | 0  |

| PSWL | S  | Z    | RSS  | AC   | IE | P/V | LT | CY |

This flag is used to control the interrupt priority. For normal operation of the interrupt control circuit, this bit must not be operated by a program.

#### (b) Carry flag (CY)

If a carry is generated out of bit 7 or 15 as a result of the execution of an operation instruction or a borrow is generated into bit 7 or 15, this flag is set to 1. In all other cases, this flag is reset to 0. This flag can be tested by the conditional branch instruction

When a bit control instruction is executed, this flag functions as a bit accumulator.

#### (c) Zero flag (Z)

When the operation result is zero, this flag is set to 1. In all other cases, this flag is reset to 0. This flag can be tested by the conditional branch instruction.

#### (d) Sign flag (S)

When MSB of the operation result is "1", this flag is set to 1. When the MSB is "0", this flag is reset to 0. This flag can be tested by the conditional branch instruction.

## (e) Parity/overflow flag (P/V)

Only when an overflow or underflow occurs as two's complement during execution of an arithmetic operation instruction, this flag is set to 1. In all other cases, it is reset to 0 (overflow flag operation).

If the bit number of the operation result set to 1 is even during execution of an logic operation instruction, this flag is set to 1. If the bit number is odd, this flag is reset to 0 (parity flag operation).

This flag can be tested by the conditional branch instruction.

## (f) Auxiliary carry flag (AC)

If a carry is generated out of bit 3 as a result of operation or a borrow is generated into bit 3, this flag is set to 1. In all other cases, this flag is reset to 0. This flag can be tested by the conditional branch instruction.

## (g) Register set select flag (RSS)

This flag is used to specify general registers X, A, C and B. As shown in Table 2-1, the RSS value determines the relationship between the functional register and the absolute register.

Thus, another register set (X, A, C, B) can be used by switching the RSS flag.

## (h) Interrupt request enable flag (IE)

This flag is used to indicate interrupt request enable/disable. This flag is set to 1 by execution of EI instruction and is reset to 0 byexecution of DI instruction or acceptance of an interrupt.

## (i) Register bank select flag (RBS0 to RBS2)

This is a 3-bit flag to select one of eight register banks (RBANK0 to RBANK7).

#### (j) User flag (UF)

This flag is set or reset in the user program and can be used for program control.

#### (3) Stack pointer (SP)

This is a 16-bit register which holds the first address of the stack area (LIFO format) of the memory.

It is operated by a dedicated instruction.

SP is decremented before write (save) operation into the stack memory and is incremented after read (return) operation from the stack memory.

Since SP becomes indeterminate by RESET input, it must be set before subroutine call.

16 Dit Drassasina

## (4) CPU control word (CCW)

This is an 8-bit register consisting of CPU control related flags. It is mapped in the special function register area and can be controlled by the software.

All bits are reset to 0 by RESET input.

Figure 2-4. CCW Format

| 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 | _   |

|---|---|---|---|---|---|-----|---|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | TPF | 0 | ccw |

## • Table position flag (TPF)

This flag is used to specify the interrupt vector table area and the memory area used as CALLT instruction table area. As TPF has been reset to 0 after application of RESET input, the 0000H to 007FH address is used as each table area. The 8002H to 807FH address of the external memory area in place of 0002H to 007FH address can be used as each table area by setting TPF to 1 using the software. The vector tables of the BRK instruction, operation code trap interrupt and reset input are fixed to 003EH, 003CH and 0000H, respectively, and they are not affected by TPF.

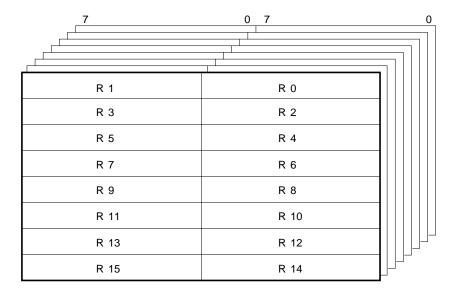

## 2.2.2 General Registers

These are 128-byte registers mapped in the special area (FE80H to FEFFH) of the internal RAM space. They consist of eight register banks. The general register in the bank consists of sixteen 8-bit registers.

Figure 2-5. General Register Memory Location

0 Dit Decesion

|       |       | 8-Bit Pro | ocessing |   | 16-Bi | t Proce | ssing |

|-------|-------|-----------|----------|---|-------|---------|-------|

| FEFFH | RBNK0 | R15       | R14      |   | (FH)  | RP7     | (EH)  |

|       | RBNK1 | R13       | R12      |   | (DH)  | RP6     | (CH)  |

|       | RBNK2 | R11       | R10      |   | (BH)  | RP5     | (AH)  |

|       | RBNK3 | R9        | R8       |   | (9H)  | RP4     | (8H)  |

|       | RBNK4 | R7        | R6       |   | (7H)  | RP3     | (6H)  |

|       | RBNK5 | R5        | R4       |   | (5H)  | RP2     | (4H)  |

|       | RBNK6 | R3        | R2       |   | (3H)  | RP1     | (2H)  |

| FE80H | RBNK7 | R1        | R0       |   | (1H)  | RP0     | (0H)  |

|       |       | 7 0       | 7 0      | ) | 15    |         | 0     |

The sixteen 8-bit registers can function as eight 16-bit register pairs (RP0 to RP7) as well.

As shown in Table 2-1, the sixteen 8-bit registers are characterized by functional names. The X register functions as the lower half of the 16-bit accumulator, the A register functions as the upper half of the 8-bit or 16-bit accumulator, the B and C registers function as a counter, and DE, HL, VP and UP function as address register pairs. In particular the VP register is function as a base register and the UP register is as a user stack pointer.

The unique function register charges as shown in Table 2-1 according to the value of the register set select flag (RSS) in the PSW. Thus, if the program is described by the functional name, another register set of X, A, C and B can be used by means of the RSS flag.

The  $\mu$ PD78324 can carry out processed data addressing operations, implied addressing by functional names with importance attached to the unique function of each register and register addressing by absolute names with a view to fast processing with a small number of data transfers or creating highly descriptive programs.

Table 2-1. General Register Configuration

| Absolute | Functional Name |         |  |  |

|----------|-----------------|---------|--|--|

| Name     | RSS = 0         | RSS = 1 |  |  |

| R0       | X               |         |  |  |

| R1       | А               |         |  |  |

| R2       | С               |         |  |  |

| R3       | В               |         |  |  |

| R4       |                 | X       |  |  |

| R5       |                 | А       |  |  |

| R6       |                 | С       |  |  |

| R7       |                 | В       |  |  |

| R8       | VPL             | VP∟     |  |  |

| R9       | VРн             | VРн     |  |  |

| R10      | UP∟             | UP∟     |  |  |

| R11      | UРн             | UРн     |  |  |

| R12      | Е               | E       |  |  |

| R13      | D               | D       |  |  |

| R14      | L               | L       |  |  |

| R15      | Н               | Н       |  |  |

| Absolute | Function | al Name |

|----------|----------|---------|

| Name     | RSS = 0  | RSS = 1 |

| RP0      | AX       |         |

| RP1      | ВС       |         |

| RP2      |          | AX      |

| RP3      |          | ВС      |

| RP4      | VP       | VP      |

| RP5      | UP       | UP      |

| RP6      | DE       | DE      |

| RP7      | HL       | HL      |

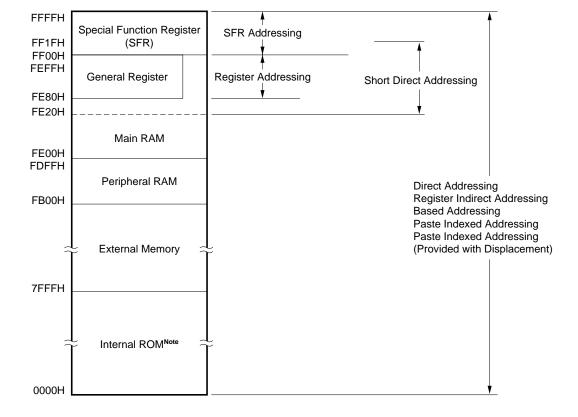

## 2.2.3 Special Function Registers (SFR)

These registers are provided with special functions. They include various peripheral hardware mode registers and control registers (CCW).

The special function registers are assigned in the FF00H to FFFFH 256-byte space. Short direct memory addressing is applied to the FF00H to FF1FH 32-byte area for processing with a short word length.

The bit manipulation, arithmetic and transfer instructions can be executed in all areas. The FFD0H to FFDFH 16-byte area is externally accessible by SFR addressing. Thus, the external memory can be accessed and the external device bit manipulation can be carried out by an instruction having a short word length.

Table 2-2 lists the special function registers (SFR). The items in the table have the following meanings.

| • Symbol             | Indicates the address of the built-in special function register.                   |

|----------------------|------------------------------------------------------------------------------------|

|                      | Can be described in the instruction operand column.                                |

| • R/W                | .Indicates if the corresponding special function register can read or write.       |

|                      | R/W : Read/write enable                                                            |

|                      | R : Read only enable (register bit test enable)                                    |

|                      | W : Write only enable                                                              |

| • Manipulable bit un | it                                                                                 |

|                      | Indicates the applicable operation bit unit for the corresponding special function |

|                      | register.                                                                          |

|                      | 16-bit manipulable SFR can be described in operand sfrp. When specified by an      |

|                      | address, an even address is described.                                             |

|                      | 1-bit manipulable SFR can be described by the bit operation instruction.           |

| • On reset           | .Indicates the state of each register when RESET is input.                         |

- Cautions 1. Addresses for which no special function registers have been assigned cannot be accessed in the FF00H to FFFFH area.

- 2. Do not write to the read only register. If data is written, the internal circuit may malfunction.

Table 2-2. List of Special Function Registers (1/4)

| Address | Created Function Designation (CFD) Name | Symbol    | R/W   | Mani  | pulable Bi | t Unit  | On Reset   |

|---------|-----------------------------------------|-----------|-------|-------|------------|---------|------------|

| Address | Special Function Register (SFR) Name    | Symbol    | IK/VV | 1 bit | 8 bits     | 16 bits | On Reset   |

| FF00H   | Port 0                                  | P0        | R/W   | 0     | 0          |         |            |

| FF02H   | Port 2                                  | P2        | R     | _     | 0          |         |            |

| FF03H   | Port 3                                  | P3        |       | 0     | 0          |         |            |

| FF04H   | Port 4                                  | P4        | R/W   | 0     | 0          |         |            |

| FF05H   | Port 5                                  | P5        |       | 0     | 0          |         | Undefined  |

| FF07H   | Port 7                                  | P7        | R     | _     | 0          |         |            |

| FF08H   | Port 8                                  | P8        | 5 044 | 0     | 0          |         |            |

| FF09H   | Port 9                                  | P9        | R/W   | 0     | 0          |         |            |

| FF0AH   | Free running counter                    | T1401114  |       |       |            |         |            |

| FF0BH   | (lower 16 bits) Note                    | TM0LW     |       |       |            |         | 0000H      |

| FF10H   | Capture register X0                     | 071/01/11 |       | _     | _          |         |            |

| FF11H   | (lower 16 bits) Note                    | CTX0LW    |       | _     |            |         |            |

| FF12H   | Capture register 01                     |           |       |       |            |         |            |

| FF13H   | (lower 16 bits) Note                    | CT01LW    | R     |       |            | 0       |            |

| FF14H   | Capture register 02                     |           | 1     |       |            | - 0     |            |

| FF15H   | (lower 16 bits) Note                    | CT02LW    |       |       |            |         |            |

| FF16H   | Capture register 03                     |           |       |       |            |         | Undefined  |

| FF17H   | (lower 16 bits) Note                    | CT03LW    |       |       |            |         |            |

| FF18H   | Capture/compoare register X0            |           |       | _     |            |         |            |

| FF19H   | (lower 16 bits) Note                    | CCX0LW    |       |       |            |         |            |

| FF1AH   | Capture/compoare register 01            | 00041114  | R/W   | _     |            |         |            |

| FF1BH   | (lower 16 bits) Note                    | CC01LW    |       | _     | _          |         |            |

| FF20H   | Port 0 mode register                    | PM0       |       | _     | 0          |         | FFH        |

| FF23H   | Port 3 mode register                    | PM3       | 1     |       | 0          |         | ×××1 1111B |

| FF25H   | Port 5 mode register                    | PM5       | w     |       | 0          |         | FFH        |

| FF28H   | Port 8 mode register                    | PM8       | 1     |       | 0          |         | ××11 1111B |

| FF29H   | Port 9 mode register                    | PM9       |       |       | 0          | _       | ×××× 1111B |

| FF2AH   | Free runnting counter                   |           |       |       |            | 0       |            |

| FF2BH   | (higher 16 bits) Note                   | TM0UW     |       |       |            |         |            |

| FF2CH   |                                         |           | 1     |       |            |         | 0000H      |

| FF2DH   | Timer register 1                        | TM1       |       |       |            | 0       |            |

| FF30H   | Capture register X0                     |           |       |       |            |         |            |

| FF31H   | (higher 16 bits) Note                   | CTX0UW    | R     |       |            |         |            |

| FF32H   | Capture register 01                     |           | †     | _     |            |         |            |

| FF33H   | (higher 16 bits) Note                   | CT01UW    |       | _     | _          |         | Undefined  |

| FF34H   | Capture register 02                     |           | 1     |       | _          |         |            |

| FF35H   | (higher 16 bits) Note                   | CT02UW    |       |       |            |         |            |

Note Upper or lower half of 18-bit register.

Table 2-2. List of Special Function Registers (2/4)

| Address | Charles Function Desister (CED) Nove  | Symbol     | R/W    | Mani  | pulable Bi | t Unit  | On Reset                       |  |

|---------|---------------------------------------|------------|--------|-------|------------|---------|--------------------------------|--|

| Address | Special Function Register (SFR) Name  | Symbol     | IN/VV  | 1 bit | 8 bits     | 16 bits | On Reset                       |  |

| FF36H   | Capture register 03                   | CT03UW     | R      |       |            | . 0     |                                |  |

| FF37H   | (higher 16 bits) Note                 | 01000W   K |        |       |            |         |                                |  |

| FF38H   | Capture/compoare register X0          | CCX0UW     |        |       |            |         | Undefined                      |  |

| FF39H   | (higher 16 bits) Note                 | CCXOOVV    | R/W    |       |            |         | Ondenned                       |  |

| FF3AH   | Capture/compoare register 01          | CC01UW     | IK/VV  |       |            |         |                                |  |

| FF3BH   | (higher 16 bits) Note                 | CCOTOVV    |        |       |            |         |                                |  |

| FF40H   | Port 0 mode control register          | PMC0       | W      |       | 0          |         | 0011                           |  |

| FF41H   | Realtime output port reset register   | RTPS       | R/W    | 0     | 0          |         | 00H                            |  |

| FF43H   | Port 3 mode control register          | PMC3       | 10/    |       | 0          |         | $\times \times \times 0$ 0000B |  |

| FF48H   | Port 8 mode control register          | PMC8       | - W    |       | 0          |         | ×× 00 0000B                    |  |

| FF4CH   | Bandania anno anto                    | 550        |        | _     |            |         |                                |  |

| FF4DH   | Baud rate generator                   | BRG        |        | _     |            |         | Undefined                      |  |

| FF60H   | Realtime output port register         | RTP        | R/W    | 0     | 0          |         |                                |  |

| FF61H   | Realtime output port reset register   | RTPR       | - K/VV | 0     | 0          |         |                                |  |

| FF62H   | Port read control register            | PRDC       |        | 0     | 0          |         | 00H                            |  |

| FF68H   | A/D converter mode register           | ADM        |        | 0     | 0          |         |                                |  |

|         | A/D conversion result register        |            |        |       | 0          |         |                                |  |

| FF6AH   | (for 16-bit access)                   | ADCR       |        |       |            |         |                                |  |

|         | A/D conversion result register        | ADCRH      | R      |       | 0          |         |                                |  |

| FF6BH   | (for upper 8-bit access)              | ADCRH      |        |       |            |         |                                |  |

| FF70H   | Campana na miatan 00                  | CMOO       | R/W    |       |            |         |                                |  |

| FF71H   | Compare register 00                   | CM00       | IK/VV  | _     |            |         |                                |  |

| FF72H   |                                       | CM01       |        | _     |            | _       |                                |  |

| FF73H   | Compare register 01                   | CIVIOT     |        | _     |            |         |                                |  |

| FF74H   |                                       | 01100      |        | _     |            |         | Undefined                      |  |

| FF75H   | Compare register 02                   | CM02       |        | _     |            |         |                                |  |

| FF76H   |                                       | 01100      |        | _     |            |         |                                |  |

| FF77H   | Compare register 03                   | CM03       |        | _     |            |         |                                |  |

| FF7CH   | _                                     |            |        | _     |            | _       |                                |  |

| FF7DH   | Compare register 10                   | CM10       | R/W    | _     |            |         |                                |  |

| FF7EH   |                                       |            |        | _     |            |         | -                              |  |

| FF7FH   | Compare register 11                   | CM11       |        | _     |            |         |                                |  |

|         | Clock synchronous serial              |            | 1      |       |            |         |                                |  |

| FF80H   | interface mode register               | CSIM       |        | 0     |            |         | 00H                            |  |

| FF82H   | Serial bus interface control register | SBIC       | 1      | 0     | 0          |         | UUH                            |  |

| FF86H   | Serial I/O shift register             | SIO        | -      | 0     | 0          |         | Undefined                      |  |

Note Upper or lower half of 18-bit register.

Table 2-2. List of Special Function Registers (3/4)

| Address  | Consider Franchisco Descriptor (CFD) Manage   | Syn   | abal     | R/W     | Mani  | pulable Bi | t Unit  | On Reset                                                                                                                                |

|----------|-----------------------------------------------|-------|----------|---------|-------|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Address  | Special Function Register (SFR) Name          | Syn   | IDOI     | R/VV    | 1 bit | 8 bits     | 16 bits | On Reset                                                                                                                                |

| FFOOLI   | Asynchronous serial interface                 | Δ.9   | SIM      | R/W     | 0     | 0          |         | 80H                                                                                                                                     |

| FF88H    | mode register                                 | / **  | 211VI    | TC/ VV  |       |            |         |                                                                                                                                         |

| FF8AH    | Asynchronous serial interface                 | AS    | ASIS     |         | 0     |            |         | 00H                                                                                                                                     |

|          | status register                               |       |          |         |       |            |         |                                                                                                                                         |

| FF8CH    | Serial receive buffer :UART                   | R)    | KB       |         |       | 0          |         | Undefined                                                                                                                               |

| FF8EH    | Serial send shift register :UART              | T     | (S       | W       |       | 0          |         |                                                                                                                                         |

| FFB0H    | Timer control register                        | TN    | ЛС       | _       | 0     | 0          |         |                                                                                                                                         |

| FFB1H    | Baud rate generator mode register             | BR    | GM       |         | 0     | 0          |         |                                                                                                                                         |

| FFB2H    | Prescalar mode register                       | PF    | RM       | R/W     | 0     | 0          |         | 00H                                                                                                                                     |

| FFB8H    | Timer output control register 0               | TO    | C0       |         | 0     | 0          |         | 0011                                                                                                                                    |

| FFB9H    | Timer output control register 1               | ТО    | C1       |         | 0     | 0          |         |                                                                                                                                         |

| FFBFH    | RPU mode register                             | RP    | UM       |         | 0     | 0          |         |                                                                                                                                         |

| FFC0H    | Standby control register                      | ST    | ВС       | R/WNote | 0     | 0          |         | 0000 × 000B                                                                                                                             |

| FFC1H    | CPU control word                              | CC    | W        | R/W     | 0     | 0          |         |                                                                                                                                         |

| FFC2H    | Watchdog timer mode register                  | WI    | DM       | R/WNote | 0     | 0          |         | 00H                                                                                                                                     |

| FFC4H    | Memory expansion mode register                | M     | MM       |         | 0     | 0          |         |                                                                                                                                         |

| FFC6H    | Programmable weight control register          | PV    | VC       |         | 0     | 0          |         | 22H                                                                                                                                     |

| FFC9H    | Fetch cycle control register                  | FC    | CC       |         | 0     | 0          |         | 00H                                                                                                                                     |

| FFD0H to | External acces area                           |       |          |         | 0     |            |         | Undefined                                                                                                                               |

| FFDFH    | External access area                          |       |          |         |       |            |         | - Chaomica                                                                                                                              |

| FFE0H    | Interrupt request flag rgister 0L             | IF0L  | IF0      |         | 0     | 0          |         |                                                                                                                                         |

| FFE1H    | Interrupt request flag rgister 0H             | IF0H  |          |         | 0     | 0          |         | 00H                                                                                                                                     |

| FFE2H    | Interrupt request flag rgister 1L             | IF1L  | IF1      |         | 0     | 0          |         |                                                                                                                                         |

| FFE3H    | _                                             |       |          |         |       |            |         |                                                                                                                                         |

| FFE4H    | Interrupt mask flag rgister 0L                | MK0L  | MK0      | R/W     | 0     | 0          |         | FFH                                                                                                                                     |

| FFE5H    | Interrupt mask flag rgister 0H                | MK0H  |          |         | 0     | 0          | 0       |                                                                                                                                         |

| FFE6H    | Interrupt mask flag rgister 1L                | MK1L  | MK1      |         | 0     | 0          |         | $\times \times $ |