# MOS INTEGRATED CIRCUIT μ**PD78212, 78213, 78214**

# **8-BIT SINGLE-CHIP MICROCOMPUTER**

# DESCRIPTION

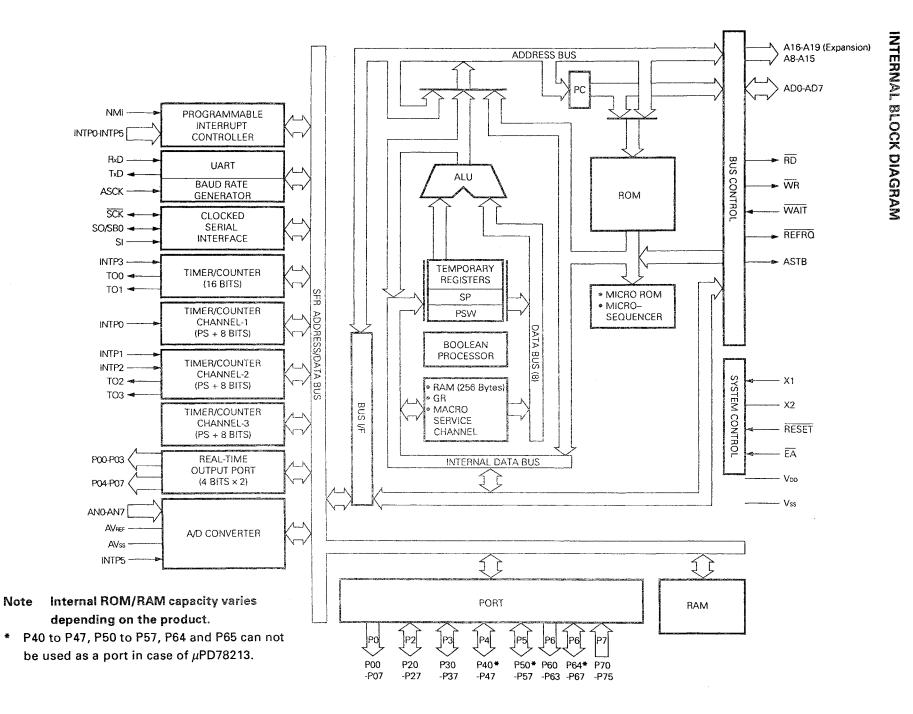

The  $\mu$ PD78212, 78213 and 78214 are 78K/II series products. The 78K/II series is an 8-bit single chip microcomputer which can access the memory space of 1M byte with an external expansion.

Functions are described in detail the following User's Manual, which should be read when carrying out design work.

$\mu$ PD78214 Series User's Manual Hardware Volume : IEM-1236

78K/II Series User's Manual Instruction Volume : IEU-1311

### FEATURES

• High-speed instruction execution (at 12 MHz operation) : 333 ns (μPD78212 and 78214)

500 ns (µPD78213)

On-chip memory ROM : 8K bytes (µPD78212)

16K bytes (μPD78214)

RAM : 384 bytes (µPD78212)

512 bytes (µPD78213, 78214)

- On-chip high-performance interrupt controller

- On-chip A/D converter (8 bits × 8 channels)

- I/O pin : 54 pins

- Real-time output port (8  $\times$  1 or 4  $\times$  2)

- Serial interface : 2 channels

- Timer/counter (16  $\times$  1 and 8  $\times$  3)

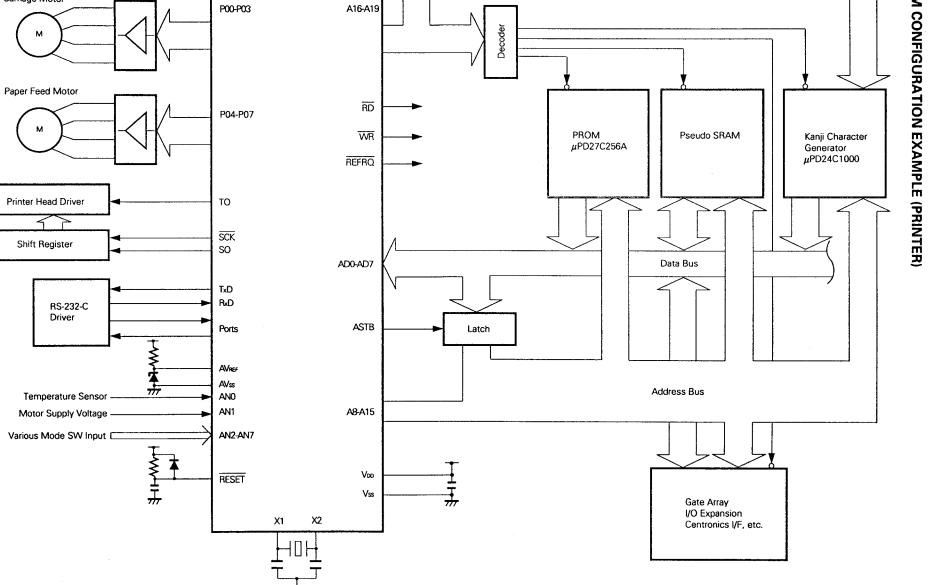

# APPLICATION

OA equipment such as printer, typewriter, PPC, FAX, etc., electronic instrument, inverter, camera

# **ORDERING INFORMATION**

| Ordering Code      | Package                               | Quality Grade |

|--------------------|---------------------------------------|---------------|

| μPD78212CW-×××     | 64-pin plastic shrink DIP (750 mil)   | Standard      |

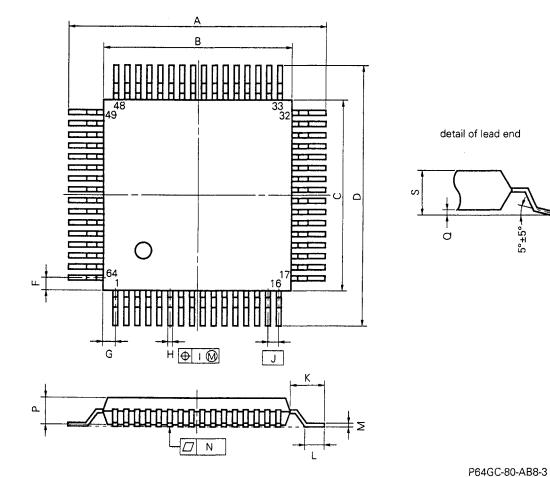

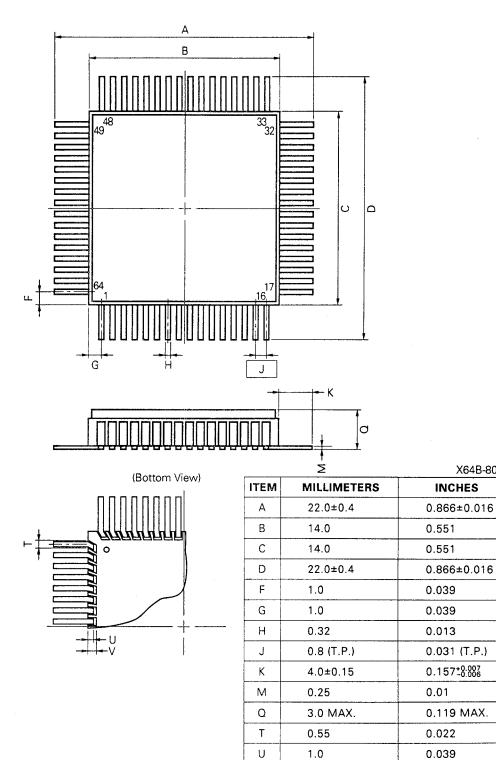

| μPD78212GC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm) | Standard      |

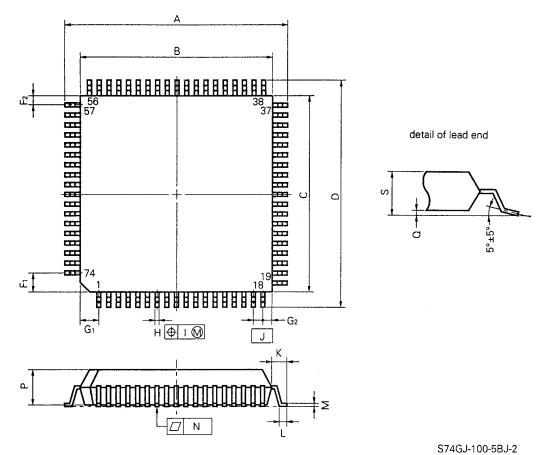

| μPD78212GJ-xxx-5BJ | 74-pin plastic QFP (20 × 20 mm)       | Standard      |

| μPD78213GC-AB8     | 64-pin plastic QFP (14 $	imes$ 14 mm) | Standard      |

| μPD78213GJ-5BJ     | 74-pin plastic QFP (20 × 20 mm)       | Standard      |

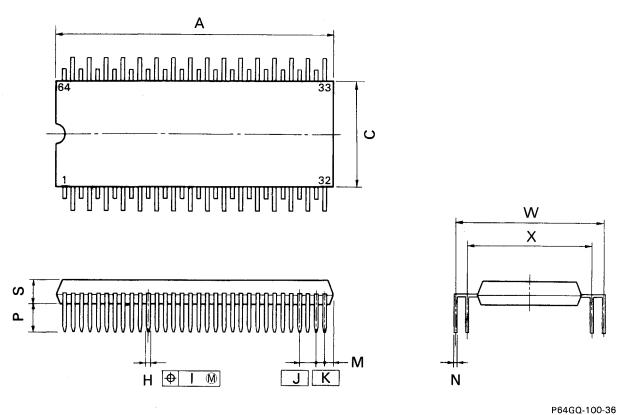

| μPD78213GQ-36      | 64-pin plastic QUIP                   | Standard      |

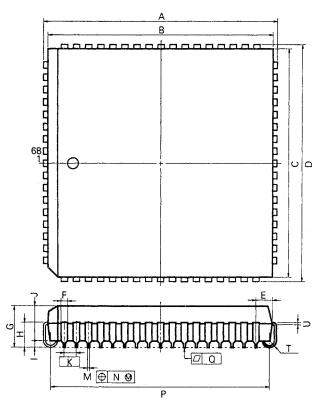

| µPD78213Ŀ          | 68-pin plastic QFJ (⊟950 mil)         | Standard      |

| μPD78214CW-xxx     | 64-pin plastic shrink DIP (750 mil)   | Standard      |

| μPD78214GC-xxx-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm) | Standard      |

| μPD78214GJ-xxx-5BJ | 74-pin plastic QFP (20 × 20 mm)       | Standard      |

| μPD78214GQ-xxx-36  | 64-pin plastic QUIP                   | Standard      |

| μPD78214L-×××      | 68-pin plastic QFJ (⊟950 mil)         | Standard      |

**Remarks** "xxx" means the specified ROM code.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

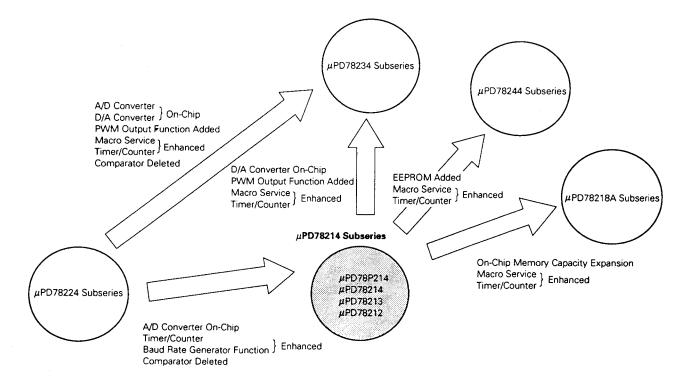

# 78K/II PRODUCT LINE-UP DIAGRAM

# **FUNCTION LIST**

| Product Name                                                       |                      | μPD78213           |                                                                                                                                                                 | μPD78212                                                    | μPD78214                                                           |                                                            |  |

|--------------------------------------------------------------------|----------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------|--|

| Basic instruction (Mnemonic)                                       |                      |                    |                                                                                                                                                                 | 65                                                          |                                                                    |                                                            |  |

| Minimum instruction execu-<br>tion time (at 12 MHz opera-<br>tion) |                      | 500 ns             |                                                                                                                                                                 | 333 ns                                                      |                                                                    |                                                            |  |

| On-chip n                                                          | nemory               | ROM                | ROM-less 8K bytes                                                                                                                                               |                                                             | 16K bytes                                                          |                                                            |  |

| capacity                                                           |                      | RAM                | 512 bytes                                                                                                                                                       |                                                             | 384 bytes                                                          | 512 bytes                                                  |  |

| Memory s                                                           | space                |                    | Program memory: 64K bytes, data memory: 1M byte                                                                                                                 |                                                             |                                                                    |                                                            |  |

|                                                                    | Input                | <u></u>            |                                                                                                                                                                 |                                                             | 14                                                                 |                                                            |  |

|                                                                    | Output               |                    |                                                                                                                                                                 |                                                             | 12                                                                 |                                                            |  |

| I/O pins                                                           | 1/0                  |                    | 10                                                                                                                                                              |                                                             |                                                                    | 28                                                         |  |

|                                                                    | Total                |                    |                                                                                                                                                                 |                                                             |                                                                    |                                                            |  |

| ·····                                                              |                      | ı pull-up          | 36                                                                                                                                                              |                                                             |                                                                    | 54                                                         |  |

| Pins<br>with                                                       | resistor             |                    | 10                                                                                                                                                              |                                                             |                                                                    | 34                                                         |  |

| addi-<br>tional                                                    | LED dire<br>output   | ect drive          |                                                                                                                                                                 |                                                             |                                                                    | 16                                                         |  |

| func-<br>tion*                                                     | Transist<br>drive ou | or direct<br>utput | 8                                                                                                                                                               |                                                             |                                                                    |                                                            |  |

| ROM-less                                                           | mode se              | etting             | ROM-less product EA pin = High-level                                                                                                                            |                                                             | n = High-level                                                     |                                                            |  |

| Real-time                                                          | output p             | ort                | 4 bits × 2 or 8 bits × 1                                                                                                                                        |                                                             |                                                                    |                                                            |  |

| General re                                                         | egister              |                    | 8 bits × 8 × 4 banks (memory mapping)                                                                                                                           |                                                             |                                                                    |                                                            |  |

|                                                                    |                      |                    | 16-bit timer/counter                                                                                                                                            | Cap                                                         | er register × 1<br>ture register × 1<br>npare register × 2         | Pulse output enable<br>( Toggle output<br>PWM/PPG output ) |  |

| Timer/cou                                                          | Inter                |                    | 8-bit timer/counter 1                                                                                                                                           | Cap                                                         | er register × 1<br>ture/compare register × 1<br>npare register × 1 | Pulse output enable<br>( Real-time output:<br>4 bits × 2   |  |

|                                                                    |                      |                    | 8-bit timer/counter 2                                                                                                                                           | timer/counter 2 { Capture register × 1 Compare register × 2 |                                                                    | Pulse output enable<br>( Toggle output<br>PWM/PPG output ) |  |

|                                                                    |                      |                    | 8-bit timer/counter 3 Timer register × 1                                                                                                                        |                                                             |                                                                    |                                                            |  |

| Serial inte                                                        | erface               |                    | UART<br>CSI (3-wire serial I/O, SE                                                                                                                              | :<br>31) :                                                  | 1 channel (specialized bau<br>1 channel                            | d rate generator incorporated)                             |  |

| A/D conve                                                          | erter                |                    | 8-bit resolution × 8 channels                                                                                                                                   |                                                             |                                                                    |                                                            |  |

| Interrupt                                                          |                      |                    | 19 sources (external 7, internal 12) + BRK instruction<br>Priority order of 2 levels (programmable)<br>2 types of servicing (vectored interrupt, macro service) |                                                             |                                                                    |                                                            |  |

| Instruction set                                                    |                      |                    | 16-bit oneration<br>Multiplication/division (8 bits × 8 bits, 16 bits ÷ 8 bits)<br>Bit manipulation<br>BCD adjustment, others                                   |                                                             |                                                                    |                                                            |  |

| Package                                                            |                      |                    | 64-pin plastic shrink DIP<br>64-pin plastic QUIP (exc<br>68-pin plastic QFJ (exce<br>64-pin plastic QFP (14 ×<br>74-pin plastic QFP (20 ×                       | '(750 µ<br>ept µP<br>pt ⊡95<br>14 mm                        | D78212)<br>50 mil and µPD78212)<br>n)                              |                                                            |  |

\* Pins with additional function included in the I/O pin.

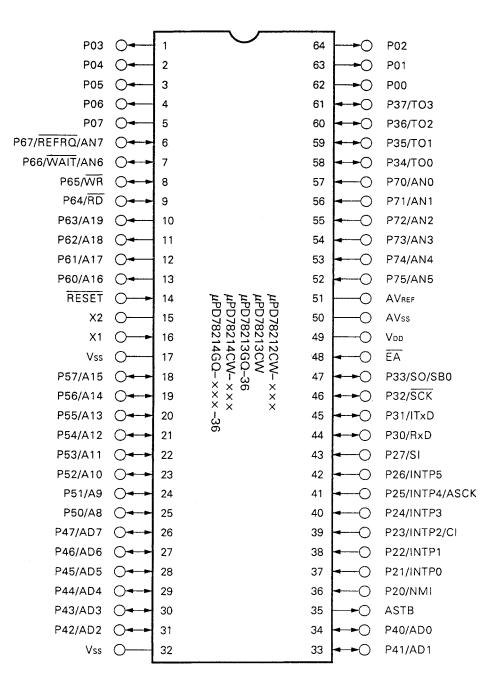

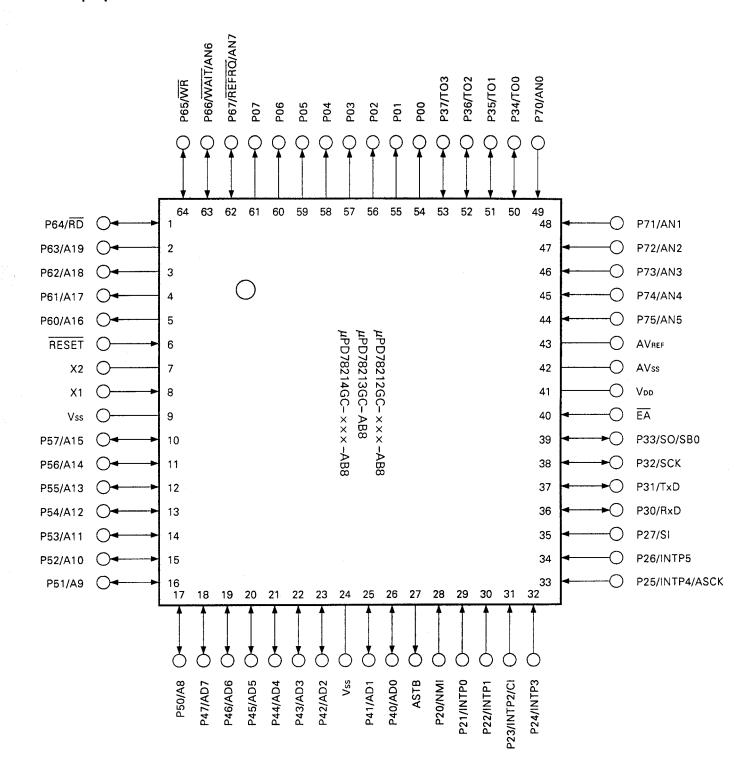

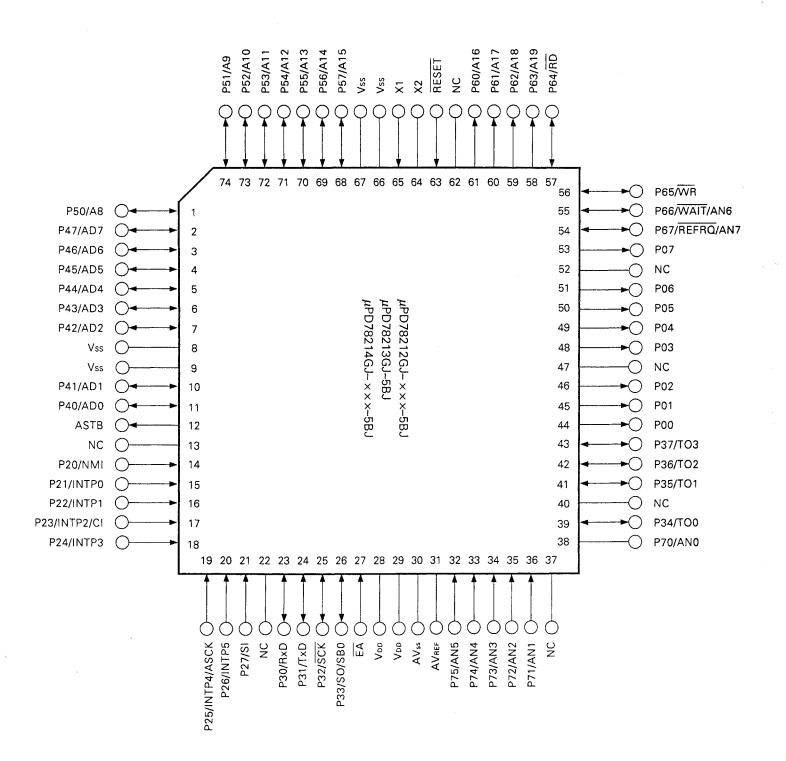

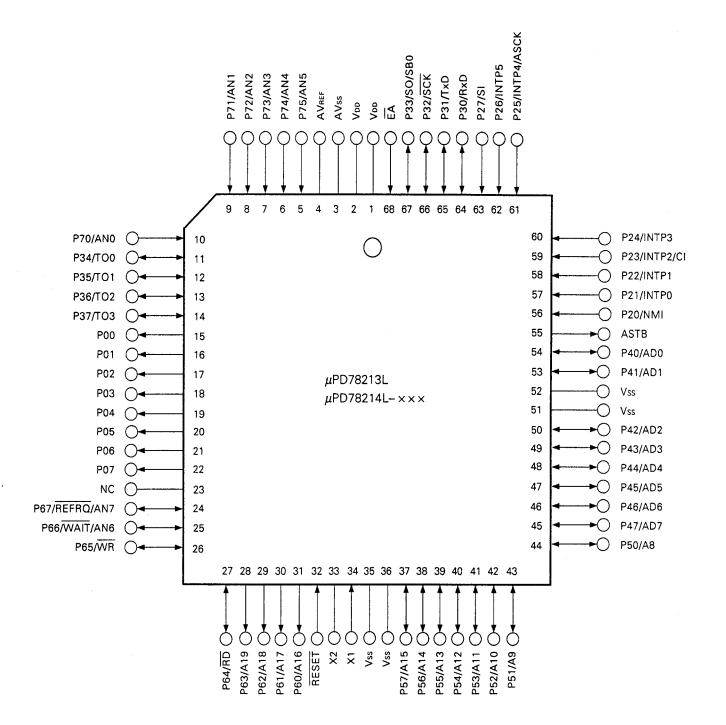

#### **PIN CONFIGURATION (TOP VIEW)**

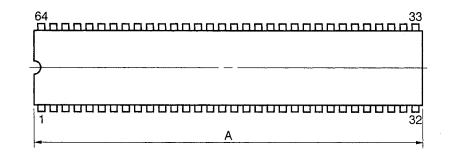

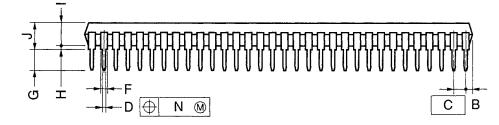

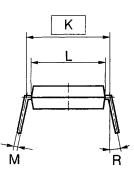

64-pin plastic shrink DIP, 64-pin plastic QUIP

64-pin plastic QFP

74-pin plastic QFP

68-pin plastic QFJ

|                              |                                                                                                                                                                                                                                                                                                                                                                                  | <b>—</b> . <b>—</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| : Port 0                     | RD                                                                                                                                                                                                                                                                                                                                                                               | : Read Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| : Port 2                     | WR                                                                                                                                                                                                                                                                                                                                                                               | : Write Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| : Port 3                     | WAIT                                                                                                                                                                                                                                                                                                                                                                             | : Wait                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| : Port 4                     | ASTB                                                                                                                                                                                                                                                                                                                                                                             | : Address Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| : Port 5                     | REFRO                                                                                                                                                                                                                                                                                                                                                                            | : Refresh Request                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| : Port 6                     | RESET                                                                                                                                                                                                                                                                                                                                                                            | : Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| : Port 7                     | X1, X2                                                                                                                                                                                                                                                                                                                                                                           | : Crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| : Timer Output               | ĒĀ                                                                                                                                                                                                                                                                                                                                                                               | : External Access                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| : Clock Input                | AN0 to AN7                                                                                                                                                                                                                                                                                                                                                                       | : Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| : Receive Data               |                                                                                                                                                                                                                                                                                                                                                                                  | : Reference Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| : Transmit Data              | AVss                                                                                                                                                                                                                                                                                                                                                                             | : Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| : Serial Clock               | Vdd                                                                                                                                                                                                                                                                                                                                                                              | : Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| : Asynchronous Serial Clock  | Vss                                                                                                                                                                                                                                                                                                                                                                              | : Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| : Serial Bus                 | NC                                                                                                                                                                                                                                                                                                                                                                               | : Non-connection                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| : Serial Input               |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| : Serial Output              |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| : Non-maskable Interrupt     |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| : Interrupt From Peripherals |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| : Address/Data Bus           |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                              | <ul> <li>Port 3</li> <li>Port 4</li> <li>Port 5</li> <li>Port 6</li> <li>Port 7</li> <li>Timer Output</li> <li>Clock Input</li> <li>Receive Data</li> <li>Transmit Data</li> <li>Serial Clock</li> <li>Asynchronous Serial Clock</li> <li>Serial Bus</li> <li>Serial Input</li> <li>Serial Output</li> <li>Non-maskable Interrupt</li> <li>Interrupt From Peripherals</li> </ul> | <ul> <li>Port 2</li> <li>Port 3</li> <li>Port 4</li> <li>Port 5</li> <li>Port 6</li> <li>Port 7</li> <li>X1, X2</li> <li>Timer Output</li> <li>EA</li> <li>Clock Input</li> <li>AN0 to AN7</li> <li>Receive Data</li> <li>AV<sub>REF</sub></li> <li>Transmit Data</li> <li>Serial Clock</li> <li>Serial Bus</li> <li>Serial Bus</li> <li>Serial Input</li> <li>Serial Output</li> <li>Non-maskable Interrupt</li> <li>Interrupt From Peripherals</li> </ul> |

A8 to A19 : Address Bus

μ**PD78214**

777

μPD78212, 78213, 78214

Stepping Motor Carriage Motor

м

м

# CONTENTS

| 1.                                  | PIN  | FUNCTI   | ONS                                                | 12 |  |  |

|-------------------------------------|------|----------|----------------------------------------------------|----|--|--|

|                                     | 1.1  | PORTS    |                                                    | 12 |  |  |

|                                     | 1.2  | OTHER    | PORTS                                              | 13 |  |  |

|                                     | 1.3  | PIN I/O  | CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS | 14 |  |  |

|                                     |      |          |                                                    |    |  |  |

| 2.                                  |      |          | BLOCK FUNCTION                                     |    |  |  |

|                                     | 2.1  |          | RY SPACE                                           |    |  |  |

|                                     | 2.2  |          |                                                    |    |  |  |

|                                     | 2.3  | REAL-T   | IME OUTPUT PORT                                    | 21 |  |  |

|                                     | 2.4  |          | COUNTER UNIT                                       |    |  |  |

|                                     | 2.5  | A/D CO   | NVERTER                                            | 24 |  |  |

|                                     | 2.6  | SERIAL   | INTERFACE                                          | 26 |  |  |

|                                     |      | 2.6.1    | Asynchronous Serial Interface                      | 27 |  |  |

|                                     |      | 2.6.2    | Clocked Serial Interface                           | 28 |  |  |

| •                                   |      |          |                                                    |    |  |  |

| 3.                                  |      | -        | EXTERNAL CONTROL FUNCTION                          |    |  |  |

|                                     | 3.1  |          | RUPT                                               |    |  |  |

|                                     |      | 3.1.1    | Interrupt Source                                   |    |  |  |

|                                     |      | 3.1.2    | Vectored Interrupt                                 |    |  |  |

|                                     |      | 3.1.3    | Macro Service                                      |    |  |  |

|                                     |      | 3.1.4    | Macro Service Application Example                  |    |  |  |

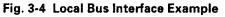

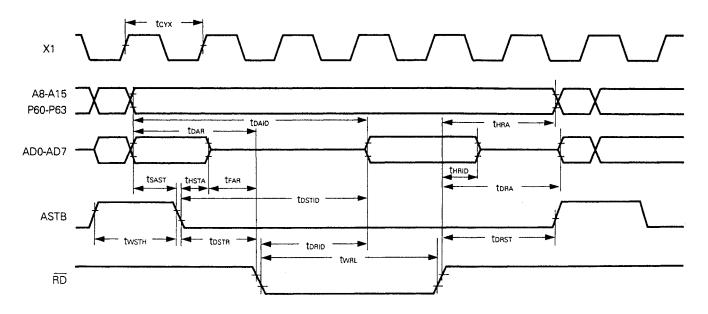

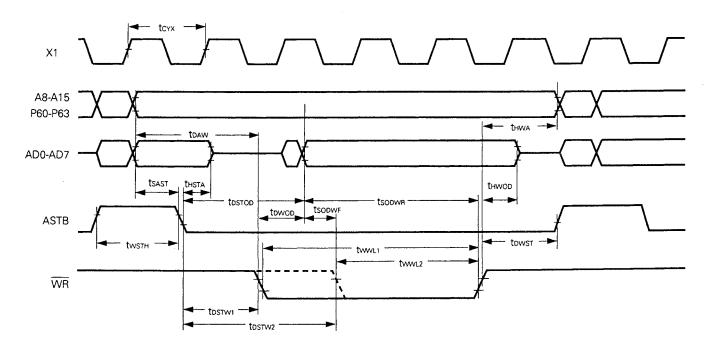

|                                     | 3.2  | LOCAL    | BUS INTERFACE                                      |    |  |  |

|                                     |      | 3.2.1    | Memory Expansion                                   | 35 |  |  |

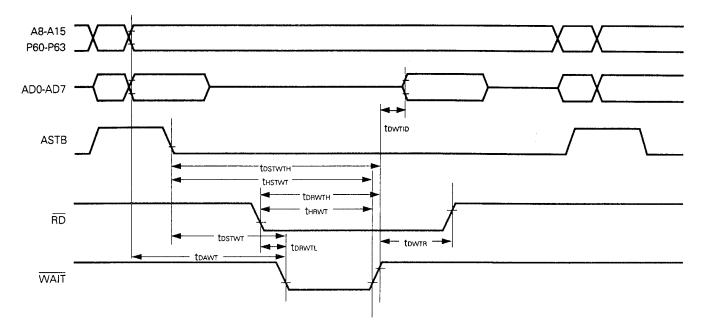

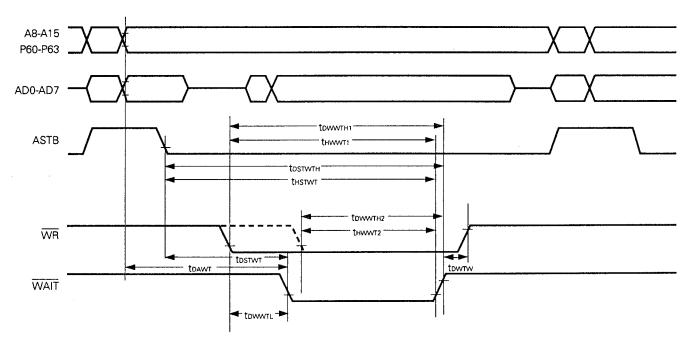

|                                     |      | 3.2.2    | Programmable Wait                                  | 35 |  |  |

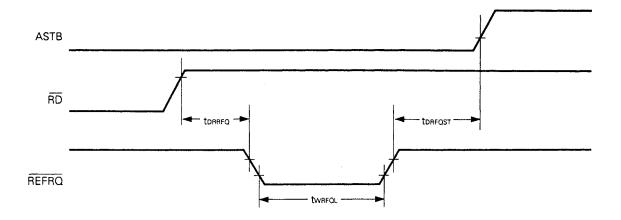

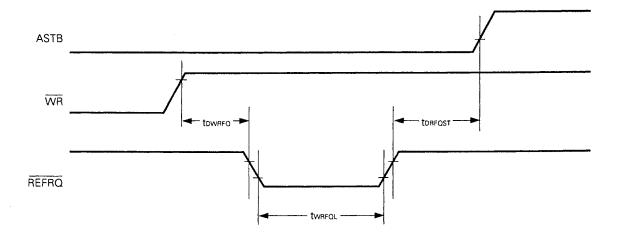

|                                     |      | 3.2.3    | Pseudo-Static RAM Refresh Function                 |    |  |  |

|                                     | 3.3  | STAND    | ВҮ                                                 | 36 |  |  |

|                                     | 3.4  | RESET    |                                                    | 37 |  |  |

| 4.                                  | INS. | TRUCTIO  | ON SET                                             | 38 |  |  |

|                                     |      |          |                                                    |    |  |  |

| 5. ELECTRICAL SPECIFICATIONS        |      |          |                                                    |    |  |  |

| 6. PACKAGE INFORMATION              |      |          |                                                    |    |  |  |

|                                     |      |          |                                                    |    |  |  |

| 7. RECOMMENDED SOLDERING CONDITIONS |      |          |                                                    |    |  |  |

| AP                                  | PEND | DIX A. E | DEVELOPMENT TOOLS                                  | 66 |  |  |

| APPENDIX B. RELATED DOCUMENTS       |      |          |                                                    |    |  |  |

$\star$

\*

# **1. PIN FUNCTIONS**

# 1.1 PORTS

| Pin Name    | 1/0                            | Dual-<br>Function Pin | Function                                                                         |  |

|-------------|--------------------------------|-----------------------|----------------------------------------------------------------------------------|--|

|             |                                |                       | Port 0 (P0):                                                                     |  |

| P00 to P07  | Output                         |                       | Established as a real-time output port (4 bits $\times$ 2)                       |  |

|             | <br>                           |                       | Direct drive of transistors capability                                           |  |

| P20         |                                | NMI                   | Port 2 (P2):                                                                     |  |

| P21         |                                | INTPO                 | P20 cannot be used as a general-purpose port. (Non-maskable interrupt)           |  |

| P22         |                                | INTP1                 | However, the input level can be confirmed in the interrupt routine.              |  |

| P23         | Input                          | INTP2/CI              | The connection of the on-chip pull-up resistor can be specified as a 6-bit batch |  |

| P24         |                                | INTP3                 | for P22 to P27 by software.                                                      |  |

| P25         |                                | INTP4/ASCK            |                                                                                  |  |

| P26         |                                | ΙΝΤΡ5                 |                                                                                  |  |

| P27         |                                | SI                    |                                                                                  |  |

| P30         |                                | RxD                   | Port 3 (P3):                                                                     |  |

| P31         | Innut/                         | TxD                   | The input/output specifiable bit-wise.                                           |  |

| P32         | Input/<br>output SCK<br>SO/SB0 |                       | Input mode pins specifiable for on-chip pull-up resistor connection as a batch   |  |

| P33         |                                |                       | by software.                                                                     |  |

| P34 to P37  |                                | TO0 to TO3            |                                                                                  |  |

|             |                                |                       | Port 4 (P4):                                                                     |  |

|             |                                |                       | The input/output specifiable as an 8-bit batch.                                  |  |

| P40 to P47* | Input/<br>output               | AD0 to AD7            | The connection of the on-chip pull-up resistor specifiable as an 8-bit batch by  |  |

|             | output                         |                       | software.                                                                        |  |

|             |                                |                       | LED direct drive capability.                                                     |  |

|             |                                |                       | Port 5 (P5):                                                                     |  |

|             |                                |                       | The input/output specifiable bit-wise.                                           |  |

| P50 to P57* | Input/                         | A8 to A15             | Input mode pins specifiable for on-chip pull-up resistor connection as a batch   |  |

|             | output                         |                       | by software.                                                                     |  |

|             |                                |                       | LED direct drive capability.                                                     |  |

| P60 to P63  | Output                         | A16 to A19            | Port 6 (P6):                                                                     |  |

| P64*        |                                | RD                    | P64 to P67 enables to specify the input/output bit-wise.                         |  |

| P65*        | input/                         | WR                    | The connection of the on-chip pull-up resistor can be specified as a batch for   |  |

| P66         | output                         | WAIT/AN6              | -                                                                                |  |

| P67         |                                |                       |                                                                                  |  |

|             | Input                          | REFRQ/AN7             |                                                                                  |  |

| P70 to P75  | Input                          | AN0 to AN5            | Port 7 (P7)                                                                      |  |

\* Can not be used as a port in case of the  $\mu$ PD78213.

# 1.2 OTHER PORTS

| Pin Name   | 1/0               | Function                                                                                                                                                                         | Dual-<br>Function Pin  |

|------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| TO0 to TO3 | Output            | Timer output                                                                                                                                                                     | P34 to P37             |

| CI         | Input             | Count clock input to 8-bit timer/counter 2                                                                                                                                       | P23 /INTP2             |

| RxD        | Input             | Serial data input (UART)                                                                                                                                                         | P30                    |

| TxD        | Output            | Serial data output (UART)                                                                                                                                                        | P31                    |

| ASCK       | Input             | Baud rate clock input (UART)                                                                                                                                                     | P25/INTP4              |

| SB0        | Input<br>/output  | Serial data input/output (SBI)                                                                                                                                                   | P33/SO                 |

| SI         | Input             | Serial data input (3-wire serial I/O)                                                                                                                                            | P27                    |

| SO         | Output            | Serial data output (3-wire serial I/O)                                                                                                                                           | P33/SB0                |

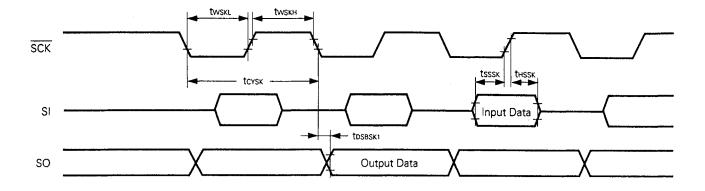

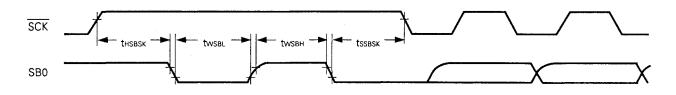

| SCK        | Input<br>/output  | Serial clock input/output (SBI, 3-wire serial I/O)                                                                                                                               | P32                    |

| NMI        | Jourput           |                                                                                                                                                                                  | P20                    |

| INTPO      |                   |                                                                                                                                                                                  | P21                    |

| INTP1      | 1                 |                                                                                                                                                                                  | P22                    |

| INTP2      | Input             | External interrupt request                                                                                                                                                       | P23/CI                 |

| INTP3      |                   |                                                                                                                                                                                  | P24                    |

| INTP4      | -                 |                                                                                                                                                                                  | P25/ASCK               |

| INTP5      | -                 |                                                                                                                                                                                  | P26                    |

| AD0 to AD7 | Input             | Time multiplexing address/data bus (external memory connection)                                                                                                                  | P40 to P47*            |

| A8 to A15  | /output<br>Output | Upper address bus (external memory connection)                                                                                                                                   | P50 to P57*            |

| A16 to A19 | Output            | Upper address when extending address (external memory connection)                                                                                                                | P60 to P63             |

| RD         | Output            | Read strobe into external memory                                                                                                                                                 | P64*                   |

| WR         | Output            | Write strobe into external memory                                                                                                                                                | P65*                   |

| WAIT       | Input             | Wait insertion                                                                                                                                                                   | P66/AN6                |

| ASTB       | Output            | Output Address (A0 to A7) latch timing output (at external memory accessed)                                                                                                      |                        |

| REFRO      | Output            | Refresh pulse output into external pseudo-static memory                                                                                                                          | P67/AN7                |

| RESET      | Input             | Chip reset                                                                                                                                                                       |                        |

| X1         | Input             |                                                                                                                                                                                  |                        |

| X2         |                   | Crystal connection for system clock oscillation (capability of clock input to X1)                                                                                                |                        |

| ĒĀ         | Input             | ROM-less operating specification (external access of the same space as internal ROM). This is used by high level in the $\mu$ PD78212 and 78214, low level in the $\mu$ PD78213. |                        |

| AN0 to AN5 |                   |                                                                                                                                                                                  | P70 to P75             |

| AN6, AN7   | Input             | Analog voltage input for A/D converter                                                                                                                                           | P66/WAIT,<br>P67/REFRQ |

| AVREF      |                   | Reference voltage apply for A/D converter                                                                                                                                        |                        |

| AVss       |                   | GND for A/D converter                                                                                                                                                            |                        |

| VDD        | ]                 | Positive power supply pin                                                                                                                                                        |                        |

| Vss        | ]                 | GND pin                                                                                                                                                                          |                        |

| NC         |                   | Not connected internally                                                                                                                                                         |                        |

\* Can not be used as a port in case of the  $\mu$ PD78213.

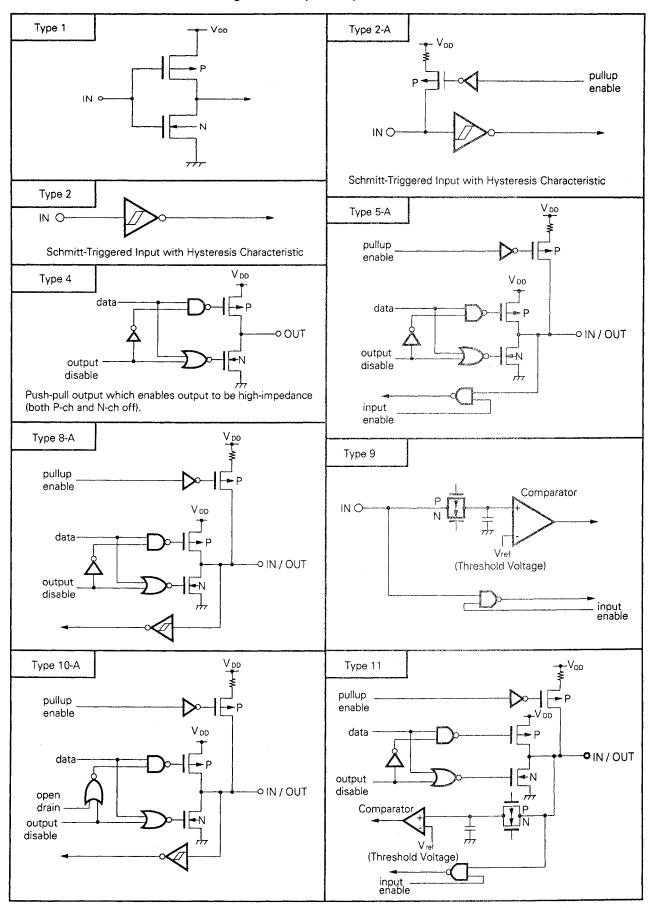

# 1.3 PIN I/O CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS

The input/output circuit type of each pin and recommended connection of unused pins are shown in Table 1-1. For the input/output circuit configuration of each type, see Fig. 1-1.

| Pin Name           | Input/Output<br>Circuit Type | 1/0          | Recommended Connection when not Used |  |

|--------------------|------------------------------|--------------|--------------------------------------|--|

| P00 to P07         | 4                            | Output       | Leave open.                          |  |

| P20/NMI            | 2                            |              | Connected to VDD or Vss.             |  |

| P21/INTP0          |                              |              |                                      |  |

| P22/INTP1          | ······                       |              |                                      |  |

| P23/INTP2/CI       |                              | Input        |                                      |  |

| P24/INTP3          |                              |              | Connected to VDD.                    |  |

| P25/INTP4/ASCK     | - 2-A                        |              |                                      |  |

| P26/INTP5          | 1                            |              |                                      |  |

| P27/SI             | -                            |              |                                      |  |

| P30/RxD            |                              |              |                                      |  |

| P31/TxD            | - 5-A                        |              |                                      |  |

| P32/SCK            | 8-A                          |              |                                      |  |

| P33/SB0/SO         | 10-A                         | Input/output | Input : Connected to Vpp.            |  |

| P34/TO0 to P37/TO3 |                              |              | Output : Leave open.                 |  |

| P40/AD0 to P47/AD7 | 5-A                          |              |                                      |  |

| P50/A8 to P57/A15  | -                            |              |                                      |  |

| P60/A16 to P63/A19 | 4                            | Output       | Leave open.                          |  |

| P64/RD             | 5-A                          |              | Input : Connected to VDD.            |  |

| P65/WR             |                              | Input/output | Output : Leave open.                 |  |

| P66/WAIT/AN6       |                              |              | Input : Connected to VDD.*           |  |

| P67/REFRQ/AN7      | - 11                         |              | Output : Leave open.                 |  |

| P70/AN0 to P75/AN5 | 9                            | Input        | Connected to Vss.                    |  |

| ASTB               | 4                            | Output       | Leave open.                          |  |

| RESET              | 2                            |              |                                      |  |

| ĒĀ                 | 1                            | Innut        |                                      |  |

| AVREF              |                              | Input        | Connected to Vss or Vpp.*            |  |

| AVss               | ]                            |              | Connected to Vss.                    |  |

<sup>★</sup> Note If the input and output are not stable on the dual-function pin as input and output, connect to Voo via a resistor of tens of k. (Especially, if the reset input pin exceeds the low level input voltage at poweron or in case of change the input/output by software.)

**Remarks** The type numbers are standardized by 78K series, therefore they are not always consecutive numbers in each product. (Some circuits are not incorporated.)

\* In the following status, do not apply a voltage outside the range AVss to AVREF to relevant pins, as the  $\mu$ PD78212, 78213 and 78214 may be damaged.

| Status                                   | Pins                                                                                                                                      |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| A/D conversion operation                 | Pins for A/D conversion                                                                                                                   |

| A/D converter not used (or not operated) | Pins selected by the A/D converter mode register (ADM)<br>• MS bit = 1 → Pins which are A/D converted when A/D<br>conversion is specified |

|                                          | • MS bit = 0 $\rightarrow$ AN0 pin                                                                                                        |

When the A/D converter is not used, if the AV<sub>REF</sub> pin is fixed at the V<sub>SS</sub> level, the AN0 (P70) pin is automatically selected after  $\overrightarrow{\text{RESET}}$  input. Fix the AN0 pin at the V<sub>SS</sub> level, or set the AV<sub>REF</sub> pin to the V<sub>DD</sub> level, and set the AN0 pin level to the AV<sub>REF</sub> level or below.

#### Fig. 1-1 Pin Input/Output Circuits

#### 2. INTERNAL BLOCK FUNCTION

#### 2.1 MEMORY SPACE

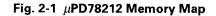

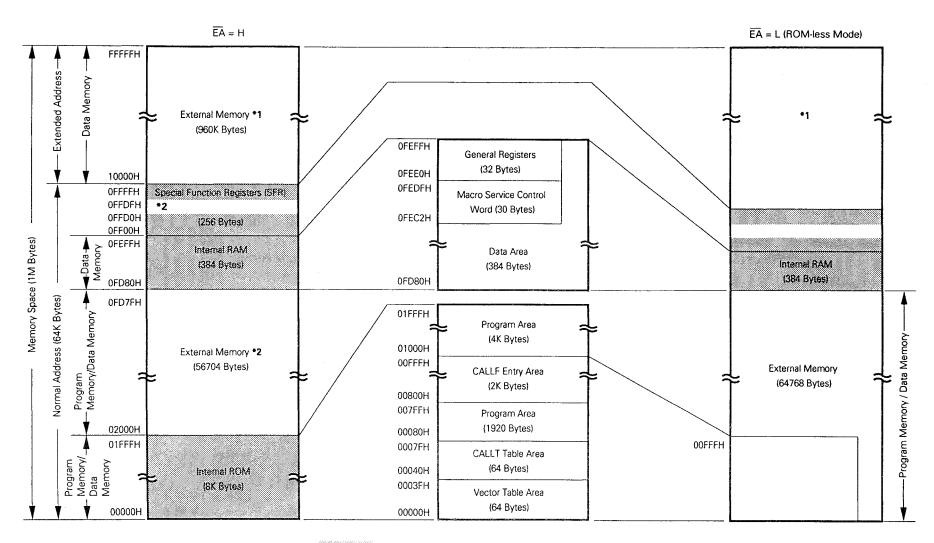

The  $\mu$ PD78212, 78213 and 78214 can access a 1M-byte memory space. The Fig. 2-1 and 2-2 show that memory space. The program memory mapping depends on the EA pin status.

#### (1) In case of the $\mu$ PD78212

The program memory is mapped into the internal ROM (8K bytes: 00000H to 01FFFH) and the external memory (56704 bytes: 02000H to 0FD7FH). The external memory is accessed by the external memory expansion mode. The mapping area into the external memory is shareable with the data memory.

The data memory is mapped into the internal RAM (384 bytes: 0FD80H to 0FEFFH). In the 1M byte extended mode, the external memory (960K bytes: 10000H to FFFFH) is mapped as the expansion data memory.

#### (2) In case of the $\mu$ PD78213

The program memory is mapped into the external memory (64768 bytes: 00000H to 0FCFFH). This area is shareable with a data memory.

The data memory has been mapped into the internal RAM (512 bytes: 0FD00H to 0FEFFH). In the 1M byte expansion mode, the external memory (960K bytes: 10000H to FFFFFH) is mapped as a expansion data memory.

#### (3) In case of the $\mu$ PD78214

The program memory is mapped into the internal ROM (16K bytes: 00000H to 03FFFH) and the external memory (48384 bytes: 04000H to 0FCFFH). The external memory is accessed by the external memory expansion mode. The mapping area into the external memory is shareable with the data memory.

The data memory has been mapped into the internal memory (512 bytes: 0FD00H to 0FEFFH). In the 1M byte extended mode, the external memory (960K bytes: 10000H to FFFFFH) is mapped as the expansion data memory.

\* 1. Accessed by 1M-byte expansion mode. SI

Shaded area denotes internal memory.

2. Accessed by external memory expansion mode.

\* 1. Accessed by 1M-byte expansion mode. Shaded area denotes internal memory.

- 2. Accessed by external memory expansion mode.

- **3**.  $\mu$ PD78213 only when  $\overline{EA} = L$

µPD78212, 78213, 78214

# NEC

# 2.2 PORT

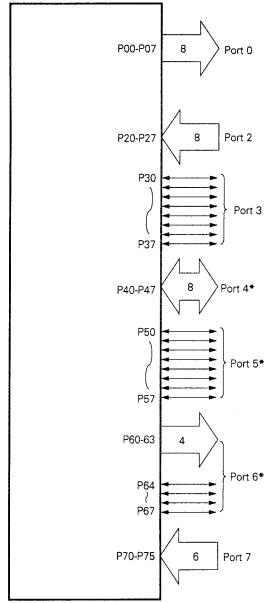

The  $\mu$ PD78212, 78213 and 78214 are equipped with ports as Fig. 2-3, operable for various controls. The function of each port describes Table 2-1. The port 2 to port 6 can be specified to use the on-chip pull-up resistor by software at power-on.

Fig. 2-3 Port Configuration

\* P40 to P47, P50 to P57, P64 and P65 can not be used as a port in case of the  $\mu$ PD78213.

| Name    | Pin Name   | Function                                                                                                                                                              | Designation of Software Pull-Up         |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Port 0  | P00 to P07 | Outputs or high-impedance specifiable as an 8-bit<br>batch.<br>Operable as 4-bit real-time output (P00 to P03, P04<br>to P07).<br>Transistor direct drive capability. | _                                       |

| Port 2  | P20 to P27 | Input port                                                                                                                                                            | 6-bit batch (P22 to P27)                |

| Port 3  | P30 to P37 | Input or output specifiable bit-wise                                                                                                                                  | Input mode pins specifiable as a batch. |

| Port 4* | P40 to P47 | Input or output specifiable as an 8-bit batch.<br>LED direct drive capability.                                                                                        | 8-bit batch                             |

| Port 5* | P50 to P57 | Input or output specifiable bit-wise.<br>LED direct drive capability.                                                                                                 | Input mode pins specifiable as a batch. |

| Port 6* | P60 to P63 | Output port                                                                                                                                                           |                                         |

|         | P64 to P67 | Input or output specifiable bit-wise                                                                                                                                  | Input mode pins specifiable as a batch. |

| Port 7  | P70 to P75 | Input port                                                                                                                                                            | _                                       |

#### Table 2-1 Port Function

\* P40 to P47, P50 to P57, P64 and P65 can not be used as a port in case of the  $\mu$ PD78213.

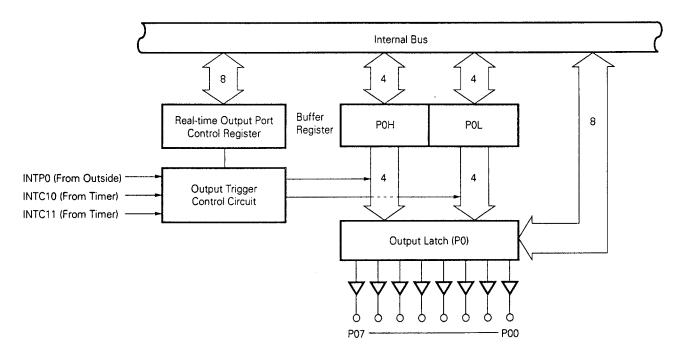

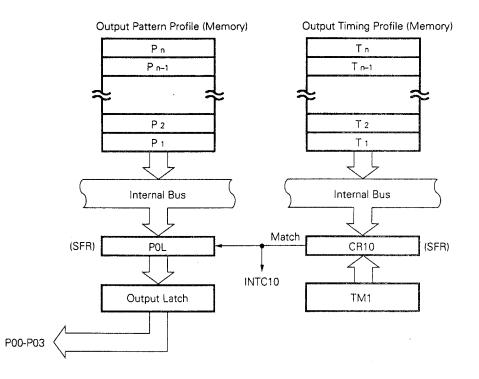

# 2.3 REAL-TIME OUTPUT PORT

The real-time output port outputs the data stored in the buffer in synchronization with a timer match interrupt or external interrupt. Therefore, a pulse output without jitter can be acquired.

Accordingly, this is suitable for the application (open loop control of a stepping motor, etc.) which outputs any pattern at any interval.

As Fig. 2-4, the port 0 and buffer register are the core of the configuration.

Fig. 2-4 Real-Time Output Port Block Diagram

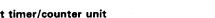

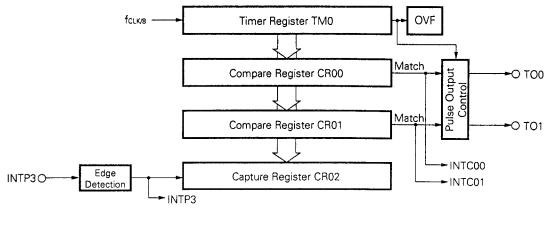

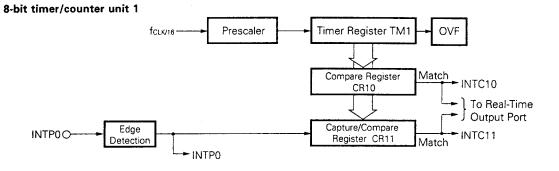

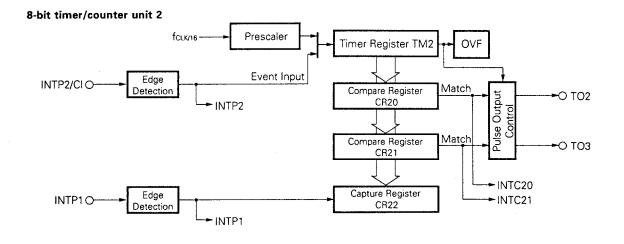

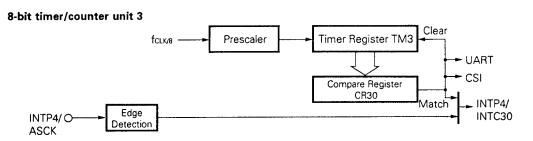

### 2.4 TIMER/COUNTER UNIT

The  $\mu$ PD78212, 78213 and 78214 incorporate one channel of a 16-bit timer/ counter unit and 3 channels of an 8-bit timer/counter unit.

| Тур      | Unit De & Function               | 16-Bit Timer/<br>Counter | 8-Bit Timer/<br>Counter 1 | 8-Bit Timer/<br>Counter 2 | 8-Bit_Timer/<br>Counter 3 |

|----------|----------------------------------|--------------------------|---------------------------|---------------------------|---------------------------|

|          | Interval timer                   | 2ch                      | 2ch                       | 2ch                       | 1ch                       |

| Type     | External event counter           |                          |                           | 0                         |                           |

|          | One shot timer                   | ·                        |                           | 0                         |                           |

|          | Timer output                     | 2ch                      |                           | 2ch                       |                           |

|          | Toggle output                    | 0                        | _                         | 0                         |                           |

| uo       | PWM/PPG output                   | 0                        |                           | 0                         |                           |

| Function | Real-time output                 |                          | 0                         |                           |                           |

| ш        | Pulse amplitude measurement      | 0                        | 0                         | 0                         |                           |

|          | Number of interrupt requests     | 2                        | 2                         | 2                         | 1                         |

|          | Clock source of serial interface |                          |                           |                           | 0                         |

Table 2-2 Types and Functions for Timer/Counter

As 7 interrupt requests are supported in total, this functions as the timer of the 7 channels.

Fig. 2-5 Timer/Counter Unit Block Diagram

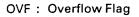

#### 2.5 A/D CONVERTER

The  $\mu$ PD78212, 78213 and 78214 incorporate an analog/digital (A/D) converter with 8 multiplexed analog inputs (AN0 to AN7).

The conversion is a successive approximation and the conversion result is stored in the 8-bit A/D conversion result register (ADCR). Therefore, the conversion can be executed at high speed and accuracy (converting time 30  $\mu$ s approximately: At 12 MHz operation).

This prepares the following modes to start the A/D converting operation.

- Hardware start: Starts the conversion with a trigger input (INTP5).

- Software start: Starts the conversion by setting a bit of A/D converter mode register (ADM).

Also, the following modes are prepared for the operation after started.

- o Scan mode : Selects analog inputs one after another and acquires the converted data from all pins.

- o Select mode : Fixes analog inputs to one pin and acquires the continuous conversion value.

When stopping the above modes and the converting operation, all of them are specified by ADM.

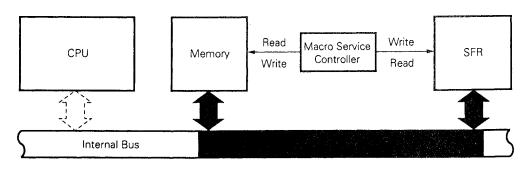

The interrupt request (INTAD) occurs when the converted result is sent to ADCR, the interrupt request INTAD is generated (except the software start select mode). Therefore, by means of the macro service, the converted values can be sent into the memory continuously.

|                | Scan Mode | Select Mode |

|----------------|-----------|-------------|

| Hardware start | 0         | 0           |

| Software start | 0         |             |

#### **Table 2-3 INTAD Generation Mode**

μ**PD78212, 78213, 78214**

Ο

#### 2.6 SERIAL INTERFACE

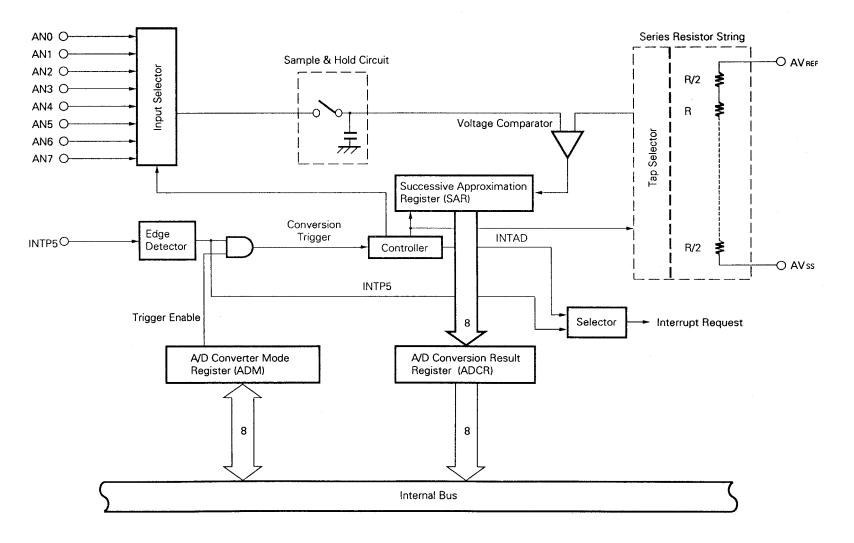

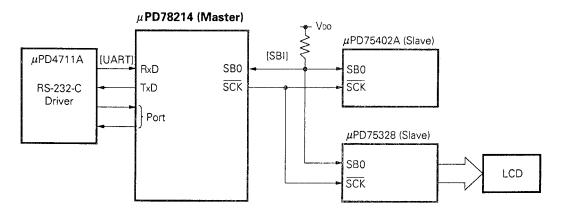

The  $\mu$ PD78212, 78213 and 78214 are equipped with 2 independent channels for serial interfaces.

Asynchronous serial interface (UART)

- O Clocked serial interface (CSI)

- 3-wire serial I/O

- Serial bus interface (SBI)

This enables both a communication with the external system and a local communication in the system simultaneously (see Fig. 2-7).

#### Fig. 2-7 Example of Serial Interface

#### (a) UART + SBI

(b) UART + 3-wire serial I/O

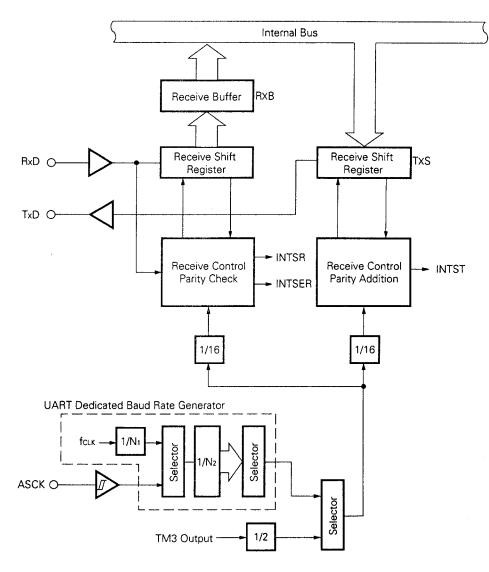

#### 2.6.1 Asynchronous Serial Interface

A UART (Universal Asynchronous Receiver Transmitter) has been incorporated as an asynchronous serial interface. This is the method to transmit the one byte data following the start bit.

As UART dedicated baud rate generator is incorporated, communications are possible with a wide range of any baud rate.

Also, the baud rate can be defined by dividing the input clock for the ASCK pin.

Moreover, a baud rate can be generated with 8-bit timer/ counter 3.

If the UART dedicated baud rate generator is used, the baud rate (31.25 kbps) of the MIDI specification can be acquired.

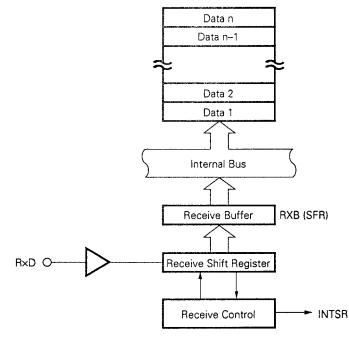

Fig. 2-8 Asynchronous Serial Interface Block Diagram

fclk : Internal system clock frequency (system clock frequency / 2)

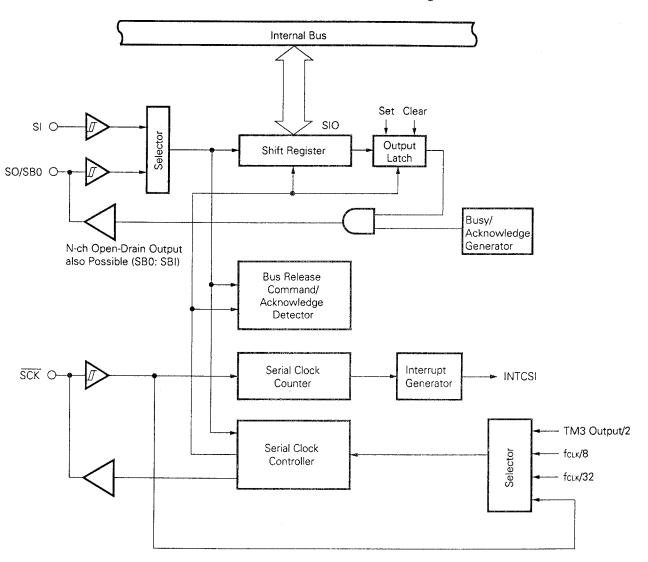

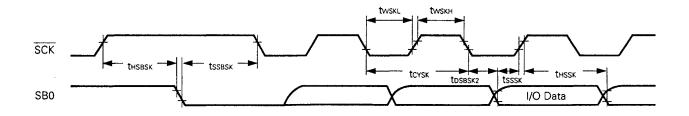

#### 2.6.2 Clocked Serial Interface

This is a method to communicate one byte data in synchronization with the serial clock which is activated by master device and starts to transmit.

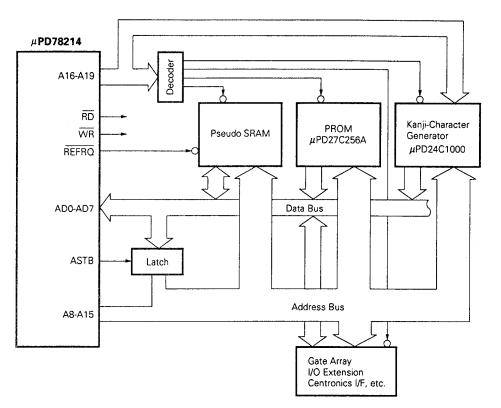

#### Fig. 2-9 Clocked Serial Interface Block Diagram

#### (1) 3-wire serial I/O

This is a interface to communicate with a device which incorporates a conventional clocked serial interface.

Basically, the communication is made through 3 wires of serial clock (SCK) and serial data (SI, SO). In case of connecting with multiple devices, the handshake line is required.

#### (2) SBI

This can communicate with multiple devices through 2 wires of serial clock (SCK) and serial bus (SB0) and this is a NEC standard serial interface.

The master device outputs "address" from the SB0 pin and selects the communicated slave device. Then, "command" and "data" are transmitted and received between the master and slave.

# 3. INTERNAL/EXTERNAL CONTROL FUNCTION

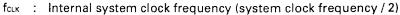

# 3.1 INTERRUPT

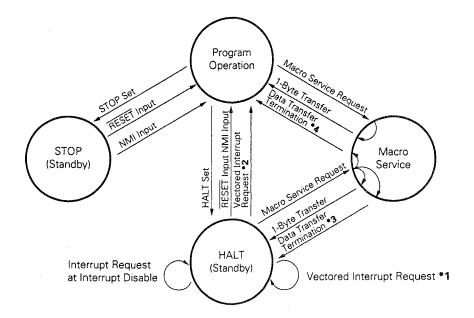

The interrupt request servicing can be selected from 2 modes in the following table.

| Servicing Mode              | Servicing Subject | Servicing                                                                        | PC, PSW Contents |

|-----------------------------|-------------------|----------------------------------------------------------------------------------|------------------|

| Vectored interrupt Software |                   | Branches to service routine, and executes With save and (any servicing contents) |                  |

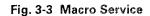

| Macro service               | Firmware          | Data transmission, etc. between memory and                                       | Hold             |

|                             |                   | I/O (fixed servicing contents)                                                   |                  |

# Table 3-1 Interrupt Request Servicing

### 3.1.1 Interrupt Source

NEC

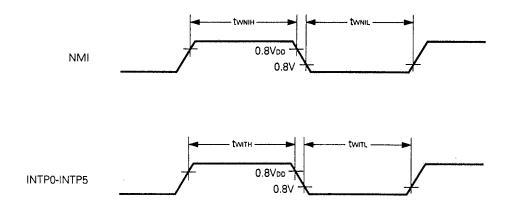

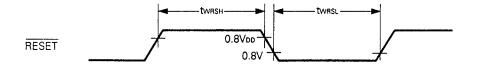

The interrupt source includes the 19 types and a BRK instruction execution as shown in Table 3-2.

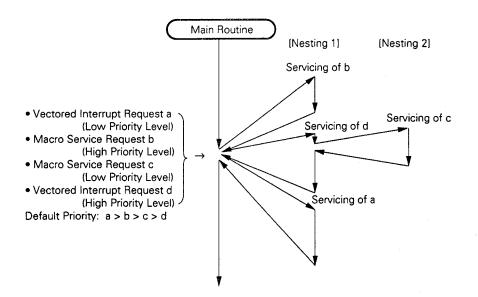

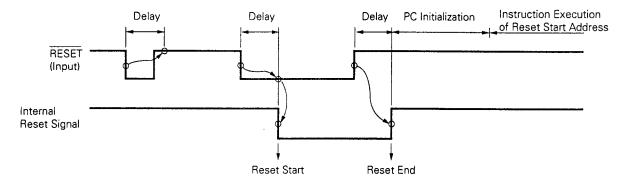

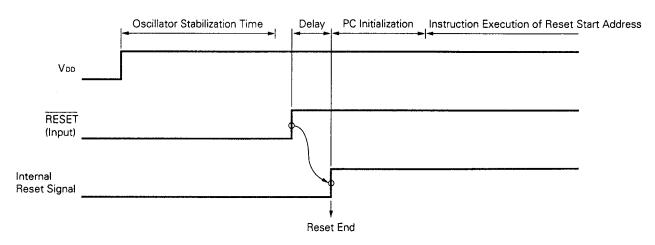

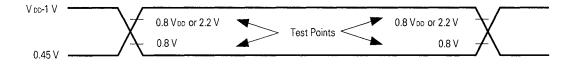

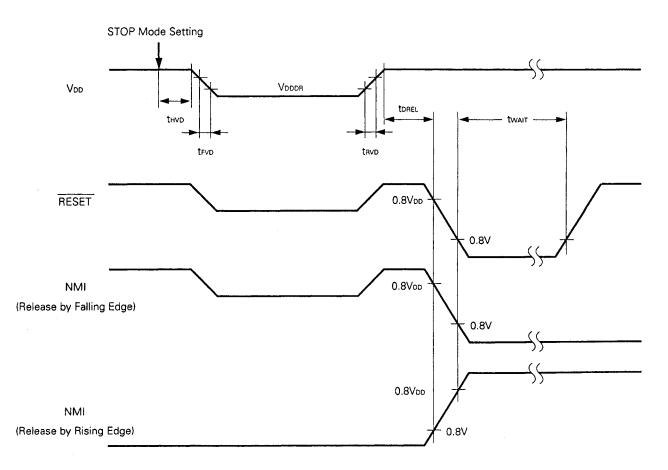

The priority of the interrupt servicing can be set to 2 levels (high and low priority levels). Therefore, it can separate the levels of the nest control which the interrupt is in progress and the interrupt request which occurs simultaneously (see **Fig. 3-1**, **Fig. 3-2**). But the nesting advances certainly in the macro service (not held).

The default priority is the priority level (fixed) to service the interrupt requests which occur at the same level simultaneously (see Fig. 3-2).

| Туре             | Default<br>Priority | Source                                     |                                                    | Internal/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

|------------------|---------------------|--------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                  |                     | Name                                       | Trigger Externa                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| Software         |                     | BRK                                        | Instruction execution                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| Non-<br>Maskable |                     | NMI                                        | Pin input edge detection                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 |