# **Single-Chip 300-Baud Modem**

The MC145442B and MC145443B silicon—gate CMOS single—chip low—speed modems contain a complete frequency shift keying (FSK) modulator, demodulator, and filter. These devices are compatible with CCITT V.21 (MC145442B) and Bell 103 (MC145443B) specifications. Both devices provide full—duplex or half—duplex 300—baud data communication over a pair of telephone lines. They also include a carrier detect circuit for the demodulator section and a duplexer circuit for direct operation on a telephone line through a simple transformer.

- MC145442B Compatible with CCITT V.21

- MC145443B Compatible with Bell 103

- Low–Band and High–Band Band–Pass Filters On–Chip

- Simplex, Half–Duplex, and Full–Duplex Operation

- Originate and Answer Mode

- Analog Loopback Configuration for Self Test

- Hybrid Network Function On-Chip

- Carrier Detect Circuit On-Chip

- Adjustable Transmit Level and CD Delay Timing

- On-Chip Crystal Oscillator (3.579 MHz)

- Single +5 V Power Supply Operation

- Internal Mid-Supply Generator

- Power-Down Mode

- Pin Compatible with MM74HC943

- Capable of Driving -9 dBm into a 600  $\Omega$  Load

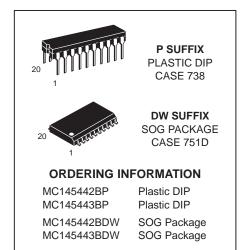

# MC145442B MC145443B

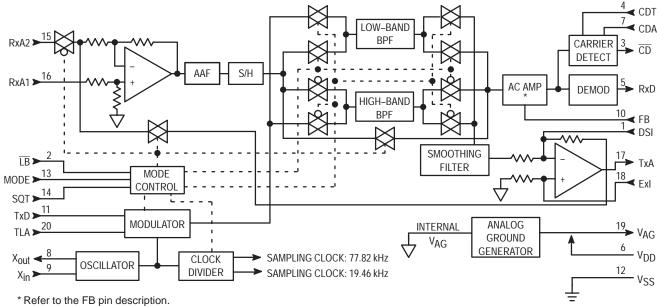

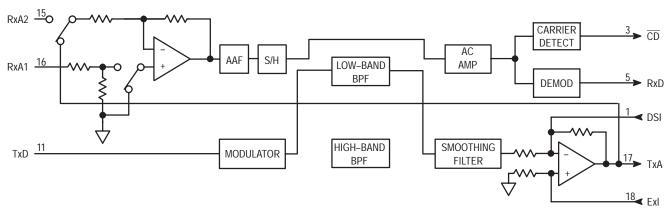

#### **BLOCK DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to VSS)

| Rating                       | Symbol                            | Value                         | Unit |

|------------------------------|-----------------------------------|-------------------------------|------|

| Supply Voltage               | $V_{DD}$                          | -0.5 to 7.0                   | V    |

| DC Input Voltage             | V <sub>in</sub>                   | –0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Output Voltage            | V <sub>out</sub>                  | –0.5 to V <sub>DD</sub> + 0.5 | V    |

| Clamp Diode Current, per Pin | I <sub>IK</sub> , I <sub>OK</sub> | ±20                           | mA   |

| DC Output Current, per Pin   | l <sub>out</sub>                  | ±28                           | mA   |

| Power Dissipation            | PD                                | 500                           | mW   |

| Operating Temperature Range  | TA                                | -40 to 85                     | °C   |

| Storage Temperature Range    | T <sub>stg</sub>                  | -65 to 150                    | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that  $\mathsf{V}_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \le (V_{in})$  or  $V_{out}) \le V_{DD}$ ).

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or V<sub>DD</sub>).

### RECOMMENDED OPERATING CONDITIONS

| Parameter                  | Symbol                             | Min | Max             | Unit |

|----------------------------|------------------------------------|-----|-----------------|------|

| Supply Voltage             | V <sub>DD</sub>                    | 4.5 | 5.5             | V    |

| DC Input or Output Voltage | V <sub>in</sub> , V <sub>out</sub> | 0   | V <sub>DD</sub> | V    |

| Input Rise or Fall Time    | t <sub>r</sub> , t <sub>f</sub>    | _   | 500             | ns   |

| Crystal Frequency*         | f <sub>crystal</sub>               | 3.2 | 5.0             | MHz  |

<sup>\*</sup> Changing the crystal frequency from 3.579 MHz will change the output frequencies. The change in output frequency will be proportional to the change in crystal frequency.

# DC ELECTRICAL CHARACTERISTICS (V<sub>DD</sub> = $5.0 \text{ V} \pm 10\%$ , T<sub>A</sub> = $-40^{\circ}$ to $85^{\circ}$ C)

| (                                                                                                | Symbol                                                                                                                                                                                                                                                                   | Min              | Тур                               | Max                            | Unit                      |    |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------|--------------------------------|---------------------------|----|

| High-Level Input Voltage                                                                         | X <sub>in</sub> , TxD, Mode, SQT                                                                                                                                                                                                                                         | VIH              | V <sub>DD</sub> – 0.8<br>3.15     | _<br>_                         | _<br>_                    | V  |

| Low-Level Input Voltage                                                                          | $\overline{\text{LB}}$ X <sub>in</sub> , TxD, Mode, SQT                                                                                                                                                                                                                  | V <sub>IL</sub>  | _<br>_                            | _<br>_                         | 0.8<br>1.1                | V  |

| High-Level Output Voltage I <sub>OH</sub> = 20 μA I <sub>OH</sub> = 2 mA I <sub>OH</sub> = 20 μA | <u>CD,</u> RxD<br><u>CD,</u> RxD<br>X <sub>out</sub>                                                                                                                                                                                                                     | VOH              | V <sub>DD</sub> – 0.1<br>3.7<br>— | <br><br>V <sub>DD</sub> – 0.05 | _<br>_<br>_<br>_          | V  |

| Low-Level Output Voltage IOL = 20 µA IOL = 2 mA IOL = 20 µA                                      | <u>CD</u> , RxD<br><u>CD</u> , RxD<br>X <sub>Out</sub>                                                                                                                                                                                                                   | VOL              | _<br>_<br>_                       | <br><br>0.05                   | 0.1<br>0.4<br>—           | V  |

| Input Current                                                                                    | $\begin{array}{c} \overline{\text{LB}}, \text{TxD}, \text{Mode, SQT} \\ \text{RxA1, RxA2} \ (0^{\circ} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C}) \\ \text{RxA1, RxA2} \ (-40^{\circ} \leq \text{T}_{\text{A}} < 0^{\circ}\text{C}) \\ X_{\text{in}} \end{array}$ | l <sub>in</sub>  | _<br>_<br>_<br>_                  | <br>10<br><br>                 | ±1.0<br>±12<br>±20<br>±10 | μА |

| Quiesent Supply Current (X                                                                       | in or f <sub>crystal</sub> = 3.579 MHz)                                                                                                                                                                                                                                  | I <sub>DD</sub>  | _                                 | 7                              | 10                        | mA |

| Power–Down Supply Current                                                                        |                                                                                                                                                                                                                                                                          |                  | _                                 | 200                            | 300                       | μΑ |

| Input Capacitance                                                                                | X <sub>in</sub><br>All Other Inputs                                                                                                                                                                                                                                      | C <sub>in</sub>  | _<br>_                            | 10<br>—                        | —<br>10                   | pF |

| V <sub>AG</sub> Output Voltage (I <sub>O</sub> = ±10                                             | 0 μΑ)                                                                                                                                                                                                                                                                    | V <sub>A</sub> G | 2.4                               | 2.5                            | 2.6                       | V  |

| CDA Output Voltage ( $I_0 = \pm 1$                                                               | VCDA                                                                                                                                                                                                                                                                     | 1.1              | 1.2                               | 1.3                            | V                         |    |

| Line Driver Feedback Resisto                                                                     | R <sub>f</sub>                                                                                                                                                                                                                                                           | 10               | 20                                | 30                             | kΩ                        |    |

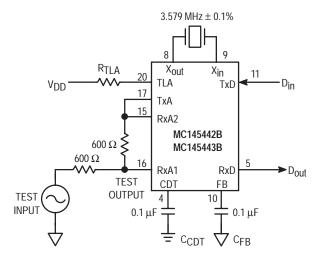

# AC ELECTRICAL CHARACTERISTICS

(VDD = 5.0 V  $\pm 10\%$ , TA =  $-40^{\circ}$  to 85°C, Crystal Frequency = 3.579 MHz  $\pm 0.1\%$ ; See Figure 1)

| Characteristic                                                                                                               |                        |            | Тур        | Max       | Unit |

|------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|------------|-----------|------|

| TRANSMITTER                                                                                                                  |                        |            |            |           |      |

| Power Output on TxA $R_L = 1.2 \text{ k}\Omega, R_{TLA} = \infty$ $R_L = 1.2 \text{ k}\Omega, R_{TLA} = 5.5 \text{ k}\Omega$ |                        | -13<br>-10 | -12<br>-9  | -11<br>-8 | dBm  |

| Second Harmonic Power $R_L = 1.2 \text{ k}\Omega$                                                                            |                        | _          | -56        | _         | dBm  |

| RECEIVE FILTER AND HYBRID                                                                                                    |                        |            | •          | •         | •    |

| Hybrid Input Impedance RxA1, RxA2                                                                                            |                        | 40         | 50         | _         | kΩ   |

| FB Output Impedance                                                                                                          |                        | _          | 16         | _         | kΩ   |

| Adjacent Channel Rejection                                                                                                   |                        |            | _          | _         | dBm  |

| DEMODULATOR                                                                                                                  |                        |            |            |           | •    |

| Receive Carrier Amplitude                                                                                                    |                        | -48        | _          | -12       | dBm  |

| Dynamic Range                                                                                                                |                        | _          | 36         | _         | dB   |

| Bit Jitter (S/N = 30 dB, Input = -38 dBm, Bit Rate = 300 baud)                                                               |                        | _          | 100        | _         | μs   |

| Bit Bias                                                                                                                     |                        | _          | 5          | _         | %    |

| Carrier Detect Threshold (CDA = 1.2 V or CDA grounded through a 0.1 μF capacitor)                                            | On to Off<br>Off to On | _<br>_     | -44<br>-47 | _<br>_    | dBm  |

MOTOROLA MC145442B•MC145443B

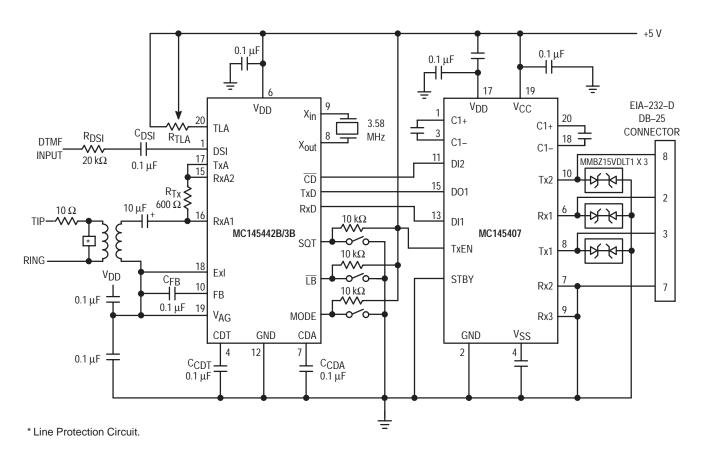

Figure 1. AC Characteristics Evaluation Circuit

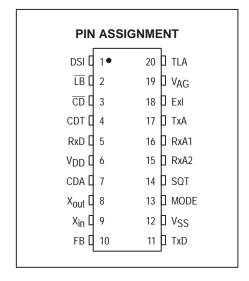

#### **PIN DESCRIPTIONS**

### V<sub>DD</sub> Positive Power Supply (Pin 6)

This pin is normally tied to 5.0 V.

### V<sub>SS</sub> Negative Power Supply (Pin 12)

This pin is normally tied to 0 V.

#### VAG Analog Ground (Pin 19)

Analog ground is internally biased to  $(V_{DD} - V_{SS})/2$ . This pin must be decoupled by a capacitor from  $V_{AG}$  to  $V_{SS}$  and a capacitor from  $V_{AG}$  to  $V_{DD}$ . Analog ground is the common bias line used in the switched capacitor filters, limiter, and slicer in the demodulation circuitry.

# TLA Transmit Level Adjust (Pin 20)

This pin is used to adjust the transmit level. Transmit level adjustment range is typically from –12 dBm to –9 dBm. (See *Applications Information.*)

### TxD Transmit Data (Pin 11)

Binary information is input to the transmit data pin. Data entered for transmission is modulated using FSK techniques. A logic high input level represents a mark and a logic low represents a space (see Table 1).

# TxA Transmit Carrier (Pin 17)

This is the output of the line driver amplifier. The transmit carrier is the digitally synthesized sine wave output of the modulator derived from a crystal oscillator reference. When a 3.579 MHz crystal is used the frequency outputs shown in Table 1 apply. (See *Applications Information*.)

Table 1. Bell 103 and CCITT V.21 Frequency Characteristics

|              | Originate Mode         |         | Answer Mode |         |  |

|--------------|------------------------|---------|-------------|---------|--|

| Data         | Transmit               | Receive | Transmit    | Receive |  |

| Bell 103 (MC | Bell 103 (MC145443B)   |         |             |         |  |

| Space        | 1070 Hz                | 2025 Hz | 2025 Hz     | 1070 Hz |  |

| Mark         | 1270 Hz                | 2225 Hz | 2225 Hz     | 1270 Hz |  |

| CCITT V.21 ( | CCITT V.21 (MC145442B) |         |             |         |  |

| Space        | 1180 Hz                | 1850 Hz | 1850 Hz     | 1180 Hz |  |

| Mark         | 980 Hz                 | 1650 Hz | 1650 Hz     | 980 Hz  |  |

NOTE: Actual frequencies may be ±5 Hz assuming 3.579545 MHz crystal is used.

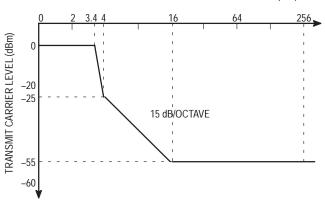

MAXIMUM LEVEL OF OUT–OF–BAND ENERGY RELATIVE TO THE TRANSMIT CARRIER LEVEL INTO 600  $\Omega$  (kHz)

Figure 2. Out-of-Band Energy

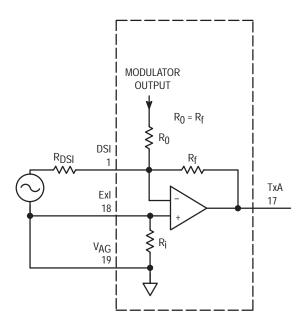

# External Input (Pin 18)

The external input is the non–inverting input to the line driver. It is provided to combine an auxiliary audio signal or speech signal to the phone line using the line driver. This pin should be connected to  $V_{AG}$  if not used. The average level must be the same as  $V_{AG}$  to maintain proper operation. (See *Applications Information*.)

# DSI Driver Summing Input (Pin 1)

The driver summing input may be used to connect an external signal, such as a DTMF dialer, to the phone line. A series resistor, RDSI, is needed to define the voltage gain AV (see *Applications Information* and Figure 6). When applying a signal to the DSI pin, the modulator should be squelched by bringing SQT (pin 14) to a logic high level. The voltage gain, AV, is calculated by the formula AV =  $-R_f/RDSI$  (where  $R_f \approx 20~k\Omega$ ). For example, a 20  $k\Omega$  resistor for RDSI will provide unity gain (AV =  $-20~k\Omega/20~k\Omega = -1$ ). This pin must be left open if not used.

# RxD Receive Data (Pin 6)

The receive data output pin presents the digital binary data resulting from the demodulation of the receive carrier. If no carrier is present,  $\overline{\text{CD}}$  high, the receive data output (RxD) is clamped high.

#### RxA2, RxA1

#### Receive Carrier (Pins 15, 16)

The receive carrier is the FSK input to the demodulator through the receive band–pass filter. RxA1 is the non–inverting input and RxA2 is the inverting input of the receive hybrid (duplexer) operational amplifier.

#### LB

#### Analog Loopback (Pin 2)

When a high level is applied to this pin (SQT must be low), the analog loopback test is enabled. The analog loopback test connects the TxA pin to the RxA2 pin and the RxA1 to analog ground. In loopback, the demodulator frequencies are switched to the modulation frequencies for the selected mode. (See Tables 1 and 2 and Figures 4c and 4d.)

When  $\overline{\text{LB}}$  is connected to analog ground (VAG), the modulator generates an echo cancellation tone of 2100 Hz for MC145442B CCITT V.21 and 2225 Hz for MC145443B Bell 103 systems. For normal operation, this pin should be at a logic low level (VSS).

The power–down mode is enabled when both  $\overline{LB}$  and SQT are connected to a logic high level (see Table 2).

| MODE<br>Pin 13 | SQT<br>Pin 14 | LB<br>Pin 2                          | Operating Mode  |

|----------------|---------------|--------------------------------------|-----------------|

| 1              | 0             | 0                                    | Originate Mode  |

| 0              | 0             | 0                                    | Answer Mode     |

| Х              | 0             | V <sub>AG</sub> (V <sub>DD</sub> /2) | Echo Tone       |

| Х              | 0             | 1                                    | Analog Loopback |

| Х              | 1             | 0                                    | Squelch Mode    |

| Х              | 1             | V <sub>AG</sub> (V <sub>DD</sub> /2) | Squelch Mode    |

| Х              | 1             | 1                                    | Power Down      |

**Table 2. Functional Table**

# MODE Mode (Pin 13)

This input selects the pair of transmit and frequencies used during modulation and demodulation. When a logic high level is placed on this input, originate (Bell) or channel 1 (CCITT) is selected. When a low level is placed on this input, answer (Bell) or channel 2 (CCITT) is selected. (See Tables 1 and 2 and Figure 4.)

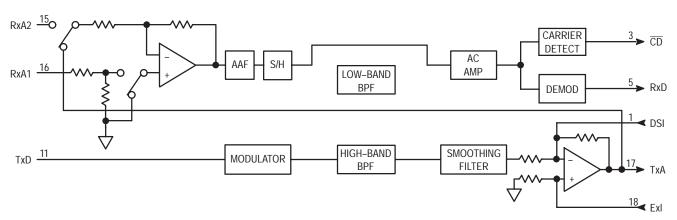

#### **CDT**

#### **Carrier Detect Timing (Pin 4)**

A capacitor on this pin to VSS sets the amount of time the carrier must be present before  $\overline{\text{CD}}$  goes low (see **Applications Information** for the capacitor values).

### CD

#### **Carrier Detect Output (Pin 3)**

This output is used to indicate when a carrier has been sensed by the carrier detect circuit. This output goes to a logic low level when a valid signal above the maximum threshold level (defined by CDA, pin 7) is maintained on the input to the hybrid circuit longer then the response (defined

by CDT, pin 4). This pin is held at the logic low level until the signal falls below the maximum threshold level for longer than the turn off time. (See *Applications Information* and Figure 5.)

#### CDA

#### Carrier Detect Adjust (Pin 7)

An external voltage may be applied to this pin to adjust the carrier detect threshold. The threshold hysteresis is internally fixed at 3 dB (see *Applications Information*).

#### X<sub>out</sub>, X<sub>in</sub> Crystal Oscillator (Pins 8, 9)

A crystal reference oscillator is formed when a 3.579 MHz crystal is connected between these two pins.  $X_{Out}$  (pin 8) is the output of the oscillator circuit, and  $X_{in}$  (pin 9) is the input to the oscillator circuit. When using an external clock, apply the clock to the  $X_{in}$  (pin 9) pin and leave  $X_{Out}$  (pin 8) open. An internal 10 M $\Omega$  resistor and internal capacitors, typically 10 pF on  $X_{in}$  and 16 pF on  $X_{Out}$ , allow the crystal to be connected without any other external components. Printed circuit board layout should keep external stray capacitance to a minimum.

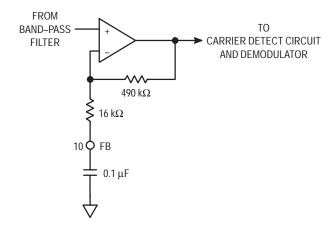

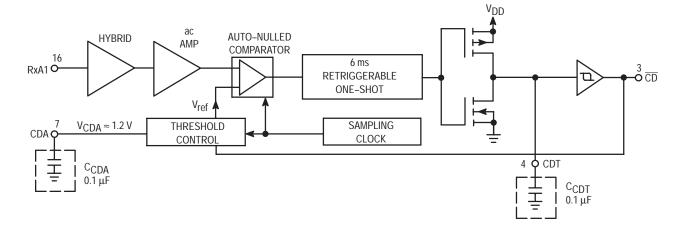

# FB Filter Bias (Pin 10)

This is the negative input to the ac amplifier. In normal operation, this pin is connected to analog ground through a 0.1  $\mu$ F bypass capacitor in order to cancel the input offset voltage of the limiter. It has a nominal input impedance of 16 k $\Omega$  (see Figure 3).

#### SQT

#### Transmit Squelch (Pin 14)

When this input pin is at a logic high level, the modulator is disabled. The line driver remains active if  $\overline{LB}$  is at a logic low level (see Table 2).

When both  $\overline{LB}$  and SQT are connected to a logic high level (see Table 2), the entire chip is in a power down state and all circuitry except the crystal oscillator is disabled. Total power supply current decreases from 10 mA (max) to 300  $\mu$ A (max).

Figure 3. AC Amplifier Circuit

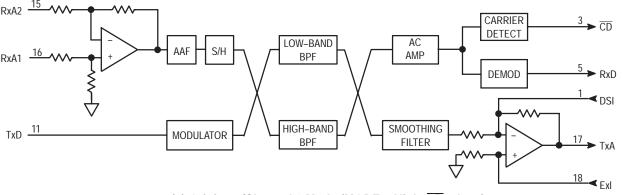

#### **GENERAL DESCRIPTION**

The MC145442B and MC145443B are full–duplex low–speed modems. They provide a 300–baud FSK signal for bidirectional data transmission over the telephone network. They can be operated in one of four basic configurations as determined by the state of MODE (pin 13) and  $\overline{\text{LB}}$  (pin 2). The normal (non–loopback) and self test (loopback) modes in both answer and originate modes will be discussed.

For an originate or channel 1 mode, a logic high level is placed on MODE (pin 13) and a logic low level is placed on LB (pin 2). In this mode, transmit data is input on TxD, where it is converted to a FSK signal and routed through a lowband band-pass filter. The filtered output signal is then buffered by the Tx op-amp line driver, which is capable of driving -9 dBm onto a 600  $\Omega$  line. The receive signal is connected through a hybrid duplexer circuit on pins 15 and 16, RxA2 and RxA1. The signal then passes through the anti-aliasing filter, the sample-and-hold circuit, is switched into the highband band-pass filter, and then switched into the ac amplifier circuit. The output of the ac amplifier circuit is routed to the demodulator circuit and demodulated. The resulting digital data is then output through RxD (pin 5). The carrier detect circuit receives its signal from the output of the ac amplifier circuit and goes low when the incoming signal is detected (see Figure 4a).

In the answer or channel 2 mode, a logic low level is placed on MODE (pin 13) and on  $\overline{\text{LB}}$  (pin 2). In this mode, the data follows the same path except the FSK signal is routed to the high–band band–pass filter and the sample–and–hold signal is routed through the low–band band–pass filter (see Figure 4b).

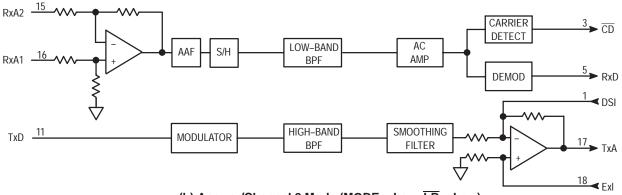

In the analog loopback originate or channel 1 mode, a logic high level is placed on MODE (pin 13) and on  $\overline{LB}$  (pin 2). This mode is used for a self check of the modulator, demodulator, and low–band pass–band filter circuit. The modulator side is configured exactly like the originate mode above except the line driver output (TxA, pin 17) is switched to the negative input of the hybrid op–amp. The RxA2 input pin is open in this mode and the non–inverting input of the hybrid circuit is connected to  $V_{\mbox{AG}}$ . The sample–and–hold output bypasses the filter so that the demodulator receives the modulated Tx data (see Figure 4c). This test checks all internal device components except the high–band band–pass filter, which can be checked in the answer or channel 2 mode test.

In the analog loopback or channel 2 mode, a logic low level is placed on MODE (pin 13) and a logic high level on LB (pin 2). This mode is used for a self check of the modulator, demodulator, and high-band pass-band filter circuit. This configuration is exactly like the originate loopback mode above, except the signal is routed through the high-band pass-band filter (see Figure 4d).

# (a) Originate/Channel 1 Mode (MODE = High, $\overline{LB}$ = Low)

# (b) Answer/Channel 2 Mode (MODE = Low, $\overline{LB}$ = Low)

# (c) Originate/Channel 1 Mode and Analog Loopback State (MODE = High, $\overline{LB}$ = Low)

(d) Answer/Channel 2 Mode and Analog Loopback State (MODE = Low,  $\overline{LB}$  = Low)

Figure 4. Basic Operating Modes

MOTOROLA MC145442B•MC145443B

#### **APPLICATIONS INFORMATION**

### **CARRIER DETECT TIMING ADJUSTMENT**

The value of a capacitor, CCDT at CDT (pin 4) determines how long a received modem signal must be present above the minimum threshold level before  $\overline{CD}$  (pin 3) goes low. The CCDT capacitor also determines how long the  $\overline{CD}$  pin stays low after the received modem signal goes below the minimum threshold. The  $\overline{CD}$  pin is used to distinguish a strong modem signal from random noise. The following equations show the relationship between tCDL, the time in seconds required for  $\overline{CD}$  to go low; tCDH, the time in seconds required for  $\overline{CD}$  to go high; and CCDT, the capacitor value in  $\mu F$ .

Valid signal to  $\overline{CD}$  response time:  $t_{CDL} \approx 6.4 \times C_{CDT}$ Invalid signal to  $\overline{CD}$  off time:  $t_{CDH} \approx 0.54 \times C_{CDT}$ Example:  $t_{CDL} \approx 6.4 \times 0.1 \ \mu\text{F} \approx 0.64 \ \text{seconds}$  $t_{CDH} \approx 0.54 \times 0.1 \ \mu\text{F} \approx 0.054 \ \text{seconds}$

### CARRIER DETECT THRESHOLD ADJUSTMENT

The carrier detect threshold is set by internal resistors to activate  $\overline{\text{CD}}$  with a typical –44 dBm (into 600  $\Omega$ ) signal and deactivate  $\overline{\text{CD}}$  with a typical –47 dBm signal applied to the input of the hybrid circuit. The carrier detect threshold level can be adjusted by applying an external voltage on CDA (pin 7). The following equations may be used to find the CDA voltage required for a given threshold voltage. (Von and Voff are in Vrms.)

$$V_{CDA} = 244 \times V_{on}$$

$V_{CDA} = 345 \times V_{off}$

#### **Example (Internally Set)**

$$V_{OR}$$

= 4.9 mV  $\approx$  -44 dBm:  $V_{CDA}$  = 244  $\times$  4.9 mV = 1.2 V  $V_{OFF}$  = 3.5 mV  $\approx$  -47 dBm:  $V_{CDA}$  = 345  $\times$  3.5 mV = 1.2 V

# **Example (Externally Set)**

$$V_{on}$$

= 7.7 mV  $\approx$  -40 dBm:  $V_{CDA}$  = 244  $\times$  7.7 mV = 1.9 V  $V_{off}$  = 5.4 mV  $\approx$  -43 dBm:  $V_{CDA}$  = 345  $\times$  5.4 mV = 1.9 V

The CDA pin has an approximate Thevenin equivalent voltage of 1.2 V and an output impedance of 100 k $\Omega$ . When using the internal 1.2 V reference, a 0.1  $\mu$ F capacitor should be connected between this pin and VSS (see Figure 5).

#### TRANSMIT LEVEL ADJUSTMENT

The power output at TxA (pin 17) is determined by the value of resistor R<sub>TLA</sub> that is connected between TLA

(pin 20) to VDD (pin 6). Table 3 shows the RTLA values and the corresponding power output for a 600  $\Omega$  load. The voltage at TxA is twice the value of that at ring and tip because TxA feeds the signal through a 600  $\Omega$  resistor RTx to a 600  $\Omega$  line transformer (see Figure 7). When choosing resistor RTLA, keep in mind that –9 dBm is the maximum output level allowed from a modem onto the telephone line (in the U.S.). In addition, keep in mind that maximizing the power output from the modem optimizes the signal–to–noise ratio, improving accurate data transmission.

**Table 3. Transmit Level Adjust**

| Output Transmit Level (Typical into 600 $\Omega$ ) | R <sub>TLA</sub> |

|----------------------------------------------------|------------------|

| −12 dBm                                            | 8                |

| -11 dBm                                            | 19.8 kΩ          |

| −10 dBm                                            | 9.2 kΩ           |

| −9 dBm                                             | 5.5 kΩ           |

#### THE LINE DRIVER

The line driver is a power amplifier used for driving a telephone line. Both the inverting and noninverting input to the line driver are available for transmitting externally generated tones.

ExI (pin 18) is the noninverting input to the line driver and gives a fixed gain of 2 (R<sub>i</sub> = 50 k $\Omega$ ). The average signal level must be the same as VAG to maintain proper operation. This pin should be connected to VAG if not used.

The driver summing input (DSI, pin 1) may be used to connect an external signal, such as a DTMF dialer, to the phone line. When applying a signal to the DSI pin, the modulator should be squelched by bringing SQT (pin 14) to a logic high level. DSI must be left open if not used.

In addition, the DSI pin is the inverting side of the line driver and allows adjustable gain with a series resistor  $R_{DSI}$  (see Figure 6). The voltage gain,  $A_V$ , is determined by the equation:

$$A_V = -\frac{R_f}{RDSI}$$

where  $R_f\approx 20~k\Omega.$

Example: A resistor value of 20  $\mbox{k}\Omega$  for RDSI will provide unity gain.

$$A_{V} = -(20 \text{ k}\Omega/20 \text{ k}\Omega) = -1$$

.

Figure 5. Carrier Detect Circuit

Figure 6. Line Driver Using the DSI Input

Figure 7. Typical MC145442B/MC145443B Applications Circuit

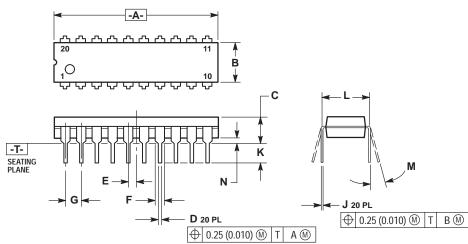

# **PACKAGE DIMENSIONS**

#### **P SUFFIX** PLASTIC DIP CASE 738-03

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- MIMENSIONING AND TOLERANCING PER AI Y14.5M, 1982.

CONTROLLING DIMENSION: INCH.

DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

- 4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | INCHES    |       | MILLIN   | IETERS |

|-----|-----------|-------|----------|--------|

| DIM | MIN       | MAX   | MIN      | MAX    |

| Α   | 1.010     | 1.070 | 25.66    | 27.17  |

| В   | 0.240     | 0.260 | 6.10     | 6.60   |

| С   | 0.150     | 0.180 | 3.81     | 4.57   |

| D   | 0.015     | 0.022 | 0.39     | 0.55   |

| E   | 0.050 BSC |       | 1.27 BSC |        |

| F   | 0.050     | 0.070 | 1.27     | 1.77   |

| G   | 0.100 BSC |       | 2.54     | BSC    |

| J   | 0.008     | 0.015 | 0.21     | 0.38   |

| K   | 0.110     | 0.140 | 2.80     | 3.55   |

| L   | 0.300 BSC |       | 7.62     | BSC    |

| M   | 0°        | 15°   | 0°       | 15°    |

| N   | 0.020     | 0.040 | 0.51     | 1.01   |

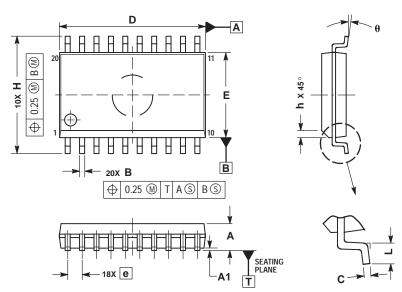

### **DW SUFFIX** SOG PACKAGE CASE 751D-05

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTUSION.

- DIMENSIONS DAING E DO NOT INCLUDE MIGLED PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE PROTRUSION SHALL

BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT

MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 2.35        | 2.65  |  |  |

| A1  | 0.10        | 0.25  |  |  |

| В   | 0.35        | 0.49  |  |  |

| С   | 0.23        | 0.32  |  |  |

| D   | 12.65       | 12.95 |  |  |

| Ε   | 7.40        | 7.60  |  |  |

| е   | 1.27 BSC    |       |  |  |

| Η   | 10.05       | 10.55 |  |  |

| h   | 0.25        | 0.75  |  |  |

| L   | 0.50        | 0.90  |  |  |

| θ   | 0 °         | 7 °   |  |  |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado, 80217. 1-303-675-2140 or 1-800-441-2447

TECHNICAL INFORMATION CENTER: 1-800-521-6274

HOME PAGE: http://motorola.com/semiconductors/

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu. Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tao Po, N.T., Hong Kong. 852-26668334

MC145442B/D