## **Programmable Delay Chip**

The MC10E/100E195 is a programmable delay chip (PDC) designed primarily for clock de-skewing and timing adjustment. It provides variable delay of a differential ECL input transition.

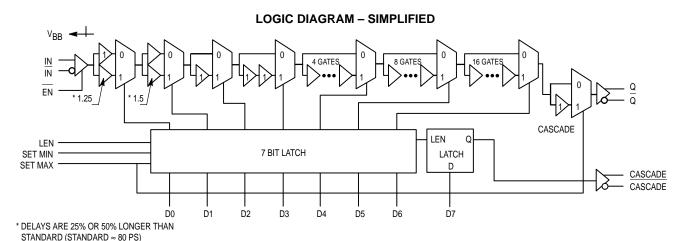

The delay section consists of a chain of gates organized as shown in the logic symbol. The first two delay elements feature gates that have been modified to have delays 1.25 and 1.5 times the basic gate delay of approximately 80 ps. These two elements provide the E195 with a digitally-selectable resolution of approximately 20 ps. The required device delay is selected by the seven address inputs D[0:6], which are latched on chip by a high signal on the latch enable (LEN) control.

Because the delay programmability of the E195 is achieved by purely differential ECL gate delays the device will operate at frequencies of >1.0 GHz while maintaining over 600 mV of output swing.

The E195 thus offers very fine resolution, at very high frequencies, that is selectable entirely from a digital input allowing for very accurate system clock timing.

An eighth latched input, D7, is provided for cascading multiple PDC's for increased programmable range. The cascade logic allows full control of multiple PDC's, at the expense of only a single added line to the data bus for each additional PDC, without the need for any external gating.

- 2.0ns Worst Case Delay Range

- ≈20ps/Delay Step Resolution

- >1.0GHz Bandwidth

- On Chip Cascade Circuitry

- Extended 100E V<sub>EE</sub> Range of -4.2 to -5.46V

- 75KΩ Input Pulldown Resistors

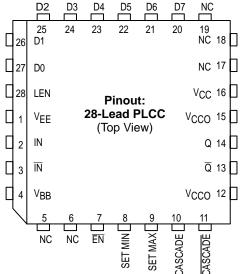

#### **PIN NAMES**

| Pin                                             | Function                                                                                                          |  |  |  |  |  |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| IN/IN EN D[0:7] Q/Q LEN SET MIN SET MAX CASCADE | Signal Input Input Enable Mux Select Inputs Signal Output Latch Enable Min Delay Set Max Delay Set Cascade Signal |  |  |  |  |  |  |

### MC10E195 MC100E195

# PROGRAMMABLE DELAY CHIP

**04/99**© Motorola, Inc. 1999

MOTOROLA

#### DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|        |                                     | 0°C |            |            | 25°C |            |            | 85°C |            |            |      |           |

|--------|-------------------------------------|-----|------------|------------|------|------------|------------|------|------------|------------|------|-----------|

| Symbol | Characteristic                      | Min | Тур        | Max        | Min  | Тур        | Max        | Min  | Тур        | Max        | Unit | Condition |

| lіН    | Input HIGH Current                  |     |            | 150        |      |            | 150        |      |            | 150        | μΑ   |           |

| IEE    | Power Supply Current<br>10E<br>100E |     | 130<br>130 | 156<br>156 |      | 130<br>130 | 156<br>156 |      | 130<br>150 | 156<br>179 | mA   | _         |

#### AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|                                      |                                                                                      | 0°C                             |                                             |                                  | 25°C                            |                                               |                                  |                                 | 85°C                                        |                                  |      |        |

|--------------------------------------|--------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------|----------------------------------|---------------------------------|-----------------------------------------------|----------------------------------|---------------------------------|---------------------------------------------|----------------------------------|------|--------|

| Symbol                               | Characteristic                                                                       | Min                             | Тур                                         | Max                              | Min                             | Тур                                           | Max                              | Min                             | Тур                                         | Max                              | Unit | Notes  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay IN to Q; Tap = 0 IN to Q; Tap = 127 EN to Q; Tap = 0 D7 to CASCADE | 1210<br>3200<br>1250<br>300     | 1360<br>3570<br>1450<br>450                 | 1510<br>3970<br>1650<br>700      | 1240<br>3270<br>1275<br>300     | 1390<br>3630<br>1475<br>450                   | 1540<br>4030<br>1675<br>700      | 1440<br>3885<br>1350<br>300     | 1590<br>4270<br>1650<br>450                 | 1765<br>4710<br>1950<br>700      | ps   |        |

| <sup>t</sup> RANGE                   | Programmable Range<br>tpD (max) – tpD (min)                                          | 2000                            | 2175                                        |                                  | 2050                            | 2240                                          |                                  | 2375                            | 2580                                        |                                  | ps   |        |

| Δt                                   | Step Delay D0 High D1 High D2 High D3 High D4 High D5 High D6 High                   | 55<br>115<br>250<br>505<br>1000 | 17<br>34<br>68<br>136<br>272<br>544<br>1088 | 105<br>180<br>325<br>620<br>1190 | 55<br>115<br>250<br>515<br>1030 | 17.5<br>35<br>70<br>140<br>280<br>560<br>1120 | 105<br>180<br>325<br>620<br>1220 | 65<br>140<br>305<br>620<br>1240 | 21<br>42<br>84<br>168<br>336<br>672<br>1344 | 120<br>205<br>380<br>740<br>1450 | ps   | 6      |

| Lin                                  | Linearity                                                                            | D1                              | D0                                          |                                  | D1                              | D0                                            |                                  | D1                              | D0                                          |                                  |      | 7      |

| tSKEW                                | Duty Cycle Skew<br><sup>t</sup> PHL <sup>-t</sup> PLH                                |                                 | ±30                                         |                                  |                                 | ±30                                           |                                  |                                 | ±30                                         |                                  | ps   | 1      |

| t <sub>S</sub>                       | Setup Time D to LEN D to IN EN to IN                                                 | 200<br>800<br>200               | 0                                           |                                  | 200<br>800<br>200               | 0                                             |                                  | 200<br>800<br>200               | 0                                           |                                  | ps   | 2<br>3 |

| t <sub>h</sub>                       | Hold Time<br>LEN to D<br>IN to EN                                                    | 500<br>0                        | 250                                         |                                  | 500<br>0                        | 250                                           |                                  | 500<br>0                        | 250                                         |                                  | ps   | 4      |

| t <sub>R</sub>                       | Release Time EN to IN SET MAX to LEN SET MIN to LEN                                  | 300<br>800<br>800               |                                             |                                  | 300<br>800<br>800               |                                               |                                  | 300<br>800<br>800               |                                             |                                  | ps   | 5      |

| <sup>t</sup> jit                     | Jitter                                                                               |                                 | <5.0                                        |                                  |                                 | <5.0                                          |                                  |                                 | <5.0                                        |                                  | ps   | 8      |

| t <sub>r</sub> t <sub>f</sub>        | Output Rise/Fall Time<br>20–80% (Q)<br>20–80% (CASCADE)                              | 125<br>300                      | 225<br>450                                  | 325<br>650                       | 125<br>300                      | 225<br>450                                    | 325<br>650                       | 125<br>300                      | 225<br>450                                  | 325<br>650                       | ps   |        |

- 1. Duty cycle skew guaranteed only for differential operation measured from the cross point of the input to the cross point of the output.

- 2. This setup time defines the amount of time prior to the input signal the delay tap of the device must be set.

- 3. This setup time is the minimum time that  $\overline{\text{EN}}$  must be asserted prior to the next transition of  $\overline{\text{IN/IN}}$  to prevent an output response greater than  $\pm 75$  mV to that  $\overline{\text{IN/IN}}$  transition.

- 4. This hold time is the minimum time that  $\overline{EN}$  must remain asserted after a negative going IN or positive going  $\overline{IN}$  to prevent an output response greater than  $\pm 75$  mV to that IN/IN transition.

- 5. This release time is the minimum time that EN must be deasserted prior to the next IN/IN transition to ensure an output response that meets the specified IN to Q propagation delay and transition times.

- 6. Specification limits represent the amount of delay added with the assertion of each individual delay control pin. The various combinations of asserted delay control inputs will typically realize D0 resolution steps across the specified programmable range.

- 7. The linearity specification guarantees to which delay control input the programmable steps will be monotonic (i.e. increasing delay steps for increasing binary counts on the control inputs Dn). Typically the device will be monotonic to the D0 input, however under worst case conditions and process variation, delays could decrease slightly with increasing binary counts when the D0 input is the LSB. With the D1 input as the LSB the device is guaranteed to be monotonic over all specified environmental conditions and process variation.

- 8. The jitter of the device is less than what can be measured without resorting to very tedious and specialized measurement techniques.

MOTOROLA 2–2

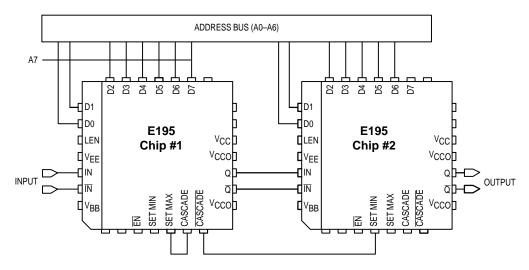

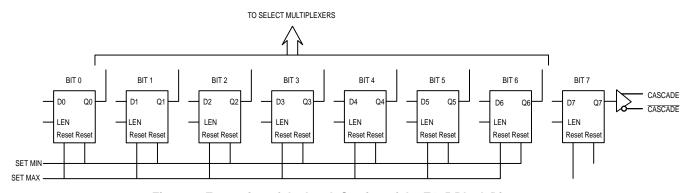

Figure 1. Cascading Interconnect Architecture

#### Cascading Multiple E195's

To increase the programmable range of the E195 internal cascade circuitry has been included. This circuitry allows for the cascading of multiple E195's without the need for any external gating. Furthermore this capability requires only one more address line per added E195. Obviously cascading multiple PDC's will result in a larger programmable range however this increase is at the expense of a longer minimum delay.

Figure 1 illustrates the interconnect scheme for cascading two E195's. As can be seen, this scheme can easily be expanded for larger E195 chains. The D7 input of the E195 is the cascade control pin. With the interconnect scheme of Figure 1 when D7 is asserted it signals the need for a larger programmable range than is achievable with a single device.

An expansion of the latch section of the block diagram is pictured below. Use of this diagram will simplify the explanation of how the cascade circuitry works. When D7 of chip #1 above is low the cascade output will also be low while the cascade bar output will be a logical high. In this condition the SET MIN pin of chip #2 will be asserted and thus all of the latches of chip #2 will be reset and the device will be set at its minimum delay. Since the RESET and SET inputs of the latches are overriding any changes on the A0–A6 address bus will not affect the operation of chip #2.

Chip #1 on the other hand will have both SET MIN and SET MAX de-asserted so that its delay will be controlled entirely by the address bus A0–A6. If the delay needed is greater than can be achieved with 31.75 gate delays (11111111 on the A0–A6 address bus) D7 will be asserted to signal the need to cascade the delay to the next E195 device. When D7 is asserted the SET MIN pin of chip #2 will be de-asserted and the delay will be controlled by the A0–A6 address bus. Chip #1 on the other hand will have its SET MAX pin asserted resulting in the device delay to be independent of the A0–A6 address bus.

When the SET MAX pin of chip #1 is asserted the D0 and D1 latches will be reset while the rest of the latches will be set. In addition, to maintain monotonicity an additional gate delay is selected in the cascade circuitry. As a result when D7 of chip #1 is asserted the delay increases from 31.75 gates to 32 gates. A 32 gate delay is the maximum delay setting for the E195.

To expand this cascading scheme to more devices one simply needs to connect the D7 input and CASCADE outputs of the current most significant E195 to the new most significant E195 in the same manner as pictured in Figure 1. The only addition to the logic is the increase of one line to the address bus for cascade control of the second PDC.

Figure 2. Expansion of the Latch Section of the E195 Block Diagram

2-3

MOTOROLA

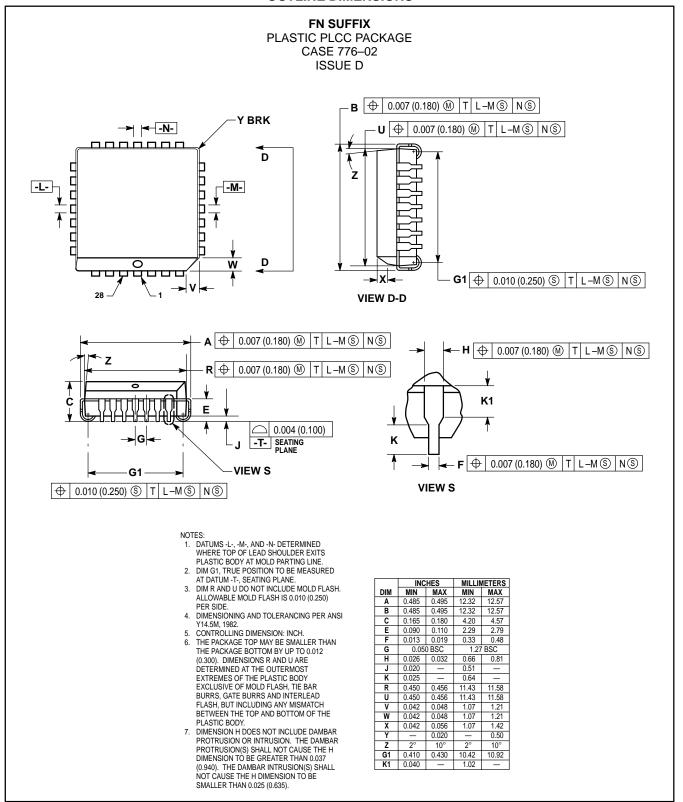

#### **OUTLINE DIMENSIONS**

MOTOROLA 2-4

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Mfax is a trademark of Motorola, Inc.

#### How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

JAPAN: Motorola Japan Ltd.; SPD, Strategic Planning Office, 141, 4–32–1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan. 81–3–5487–8488

#### Customer Focus Center: 1-800-521-6274

Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE 1-602-244-6609

Motorola Fax Back System - US & Canada ONLY 1-800-774-1848

- http://sps.motorola.com/mfax/

**ASIA/PACIFIC:** Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26629298

HOME PAGE: http://motorola.com/sps/

$\Diamond$  MC10E195/D