# **HP PA-8000 CLOCK SOURCE**

## **FEATURES**

- 3.3V, -1.9V power supples

- Differential LVPECL clock input

- **■** Differential HSTL/LVPECL outputs

- Compatible with HP PA-8000 microprocessors

- Low-jitter source for all PA-8000 required timing signals

- Available in 44-pin MQUAD package

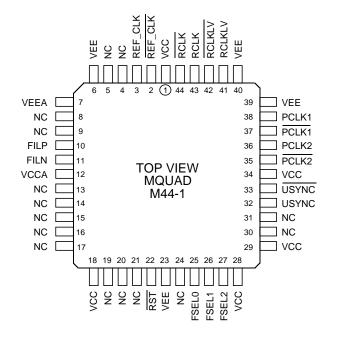

## PIN CONFIGURATION

## DESCRIPTION

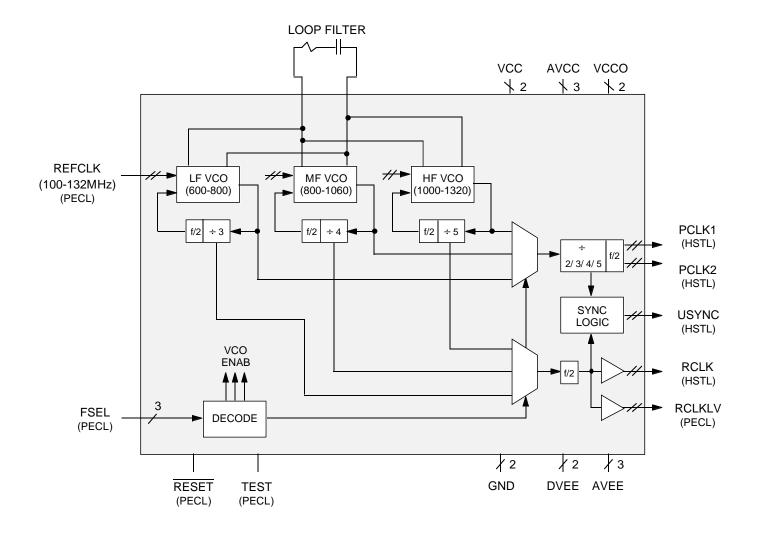

Micrel-Synergy's SY89801A PLL based clock generator provides, in a single chip, all the necessary clocks for Hewlett-Packard's PA-8000 Microprocessor.

Utilizing Micrel-Synergy's advanced PLL technology, the SY89801A accepts a Positive-ECL (PECL) reference clock input at 100MHz-132MHz, and provides precisely aligned, ultra-low-jitter ratios of frequencies necessary for the operation of the processor. In addition, the SY89801A provides the "USYNC" synchronizing signals as required by the PA-8000. The frequency ratios are 1:1, 4:3, 3:2, 5:3 and 2:1.

To facilitate direct interfacing to the PA-8000, the SY89801A operates across +3.3 volt and -1.9 volt supplies. The processor clock (PCLK), runway clock (RCLK), and USYNC outputs are HSTL-compatible. Additionally, there is a PECL-compatible runway clock output (RCLKLV). The SY89801A requires only a simple external series-RC loop filter.

Coupling Micrel-Synergy's advanced PLL technology with our proprietary ASSET bipolar process has produced a Timing Generator IC which meets the stringent requirements of the PA-8000 μP, while setting a new standard for performance and flexibility.

### PIN NAMES

| Pin              | Function                           |

|------------------|------------------------------------|

| REF_CLK, REF_CLK | Differential Input Ref. Clock      |

| FILP, FILN       | Filter Pins (Positive & Negative)  |

| VCCA, VEEA       | Analog Vcc, VEE                    |

| RST              | Master Reset                       |

| FSEL2-0          | LVPECL Frequency Select Pins       |

| USYNC, USYNC     | Diff. HSTL Sync Signal for PA-8000 |

| PCLK1-2, PCLK1-2 | Diff. HSTL Processor Clock Signal  |

| RCLK, RCLK       | Diff. HSTL Runway Clock Signal     |

| RCLKLV, RCLKLV   | Diff. LVPECL Clock Signal          |

# **BLOCK DIAGRAM**

# 3.3V DC ELECTRICAL CHARACTERISTICS

$VCC = VCCA = 3.3V \pm 10\%$ ; VEEA = VEE = -1.9V

| Symbol | Parameter                  | Min. | Тур. | Max. | Unit | Condition   |

|--------|----------------------------|------|------|------|------|-------------|

| Vcc    | Power Supply Voltage       | 3.0  |      | 3.6  | ٧    | VEE = −1.9V |

| Icc    | Power Supply Current (Vcc) | _    | 250  | 321  | mA   |             |

# PECL DC ELECTRICAL CHARACTERISTICS

$VCC = 3.3V \pm 10\%$ ; VEE = -1.9V

| Symbol | Parameter           | Min.        | Тур.       | Max.        | Unit | Condition |

|--------|---------------------|-------------|------------|-------------|------|-----------|

| Voн    | Output HIGH Voltage | Vcc - 1.075 |            | Vcc - 0.830 | >    |           |

| Vol    | Output LOW Voltage  | Vcc - 1.860 | _          | Vcc - 1.570 | ٧    |           |

| VIH    | Input HIGH Voltage  | Vcc - 1.165 | _          | Vcc - 0.880 | V    |           |

| VIL    | Input LOW Voltage   | Vcc - 1.810 |            | Vcc – 1.475 | V    |           |

| Vвв    | PECL Threshold      | _           | Vcc - 1.35 | _           | V    |           |

## HSTL DC ELECTRICAL CHARACTERISTICS

$VCC = 3.3V \pm 10\%$ ; VEE = -1.9V

| Symbol | Parameter           | Min.      | Тур. | Max.      | Unit | Condition |

|--------|---------------------|-----------|------|-----------|------|-----------|

| Vон    | Output HIGH Voltage | Vcc - 2.3 |      | Vcc - 2.1 | V    |           |

| Vol    | Output LOW Voltage  | Vcc - 3.1 | _    | Vcc - 2.9 | V    |           |

## AC ELECTRICAL CHARACTERISTICS(1)

$VCC = 3.3V \pm 10\%$ ; VEE = -1.9V

|                      |                                                               | TA = 0°C    |             | TA = +25°C                  |             | TA = +70°C  |                             |                  |             |                             |                      |                                    |

|----------------------|---------------------------------------------------------------|-------------|-------------|-----------------------------|-------------|-------------|-----------------------------|------------------|-------------|-----------------------------|----------------------|------------------------------------|

| Symbol               | Parameter                                                     | Min.        | Тур.        | Max.                        | Min.        | Тур.        | Max.                        | Min.             | Тур.        | Max.                        | Unit                 | Condition                          |

| fvco                 | Maximum VCO Frequency                                         | 1320        |             | _                           | 1320        | _           | _                           | 1320             | _           | _                           | MHz                  |                                    |

| fMAX                 | Maximum PCLK Output Frequency Maximum RCLK Output Frequency   | 264<br>132  | _           | _                           | 264<br>132  | _           | _                           | 264<br>132       | _           | _                           | MHz<br>MHz           |                                    |

| tskew <sup>(2)</sup> | PCLK to PCLK RCLK to RCLKLV PCLK to RCLK PCLK (neg.) to USYNC | _<br>_<br>_ | _<br>_<br>_ | ±50<br>±100<br>±100<br>±500 | _<br>_<br>_ | _<br>_<br>_ | ±50<br>±100<br>±100<br>±500 | _<br>_<br>_<br>_ | _<br>_<br>_ | ±50<br>±100<br>±100<br>±500 | ps<br>ps<br>ps<br>ps | Measured at differential crossover |

| tpe                  | Phase Error<br>RCLK to REF_CLK                                | _           | _           | ±250                        | _           | _           | ±250                        | _                | _           | ±250                        | ps                   |                                    |

| tj <sup>(2)</sup>    | Output Jitter                                                 | -50         | _           | +50                         | -50         | _           | +50                         | -50              | _           | +50                         | ps                   | Peak to Peak,<br>Cycle to Cycle    |

| tdc <sup>(2)</sup>   | Output Duty Cycle                                             | 49          | _           | 51                          | 49          | _           | 51                          | 49               | _           | 51                          | %                    |                                    |

| tr (2)               | Rise/Fall Times<br>(20% to 80%)                               | 100         | _           | 800                         | 100         | _           | 800                         | 100              | _           | 800                         | ps                   |                                    |

#### **NOTES**

- 1. All HSTL outputs terminated into 50 ohms in parallel with 3pf to GND.

- 2. tskew, tj, tdc, tr and tf are specified by HP for the PA-8000. This is our best information as of the date of this document.

# **APPLICATIONS INFORMATION**

The following table lists the various PCLK and RCLK ratios supported by the SY89801A and the corresponding PCLK, RCLK, FB and VCO frequencies. The table is arranged in order of increasing PCLK:RCLK ratio. The table was designed to balance several constraints:

- 2.5:1 VCO frequency range

- Maximum system frequency of 120MHz plus 10% margin

- Maximum output frequency of 264MHz

| FSEL <2:0> | PCLK:RCLK | fPCLK (MHz) | fRCLK (MHz) | VCO ÷ ratios<br>VCO/P:VCO/R | fVCO (MHz) |

|------------|-----------|-------------|-------------|-----------------------------|------------|

| 000        | 1:1       | 100-132     | 100-132     | 8:8                         | 800-1056   |

| 001        | 4:3       | 133.3-176   | 100-132     | 6:8                         | 800-1056   |

| 010        | 3:2       | 150-198     | 100-132     | 4:6                         | 600-792    |

| 011        | 5:3       | 166.7-220   | 100-132     | 6:10                        | 1000-1320  |

| 100        | 2:1       | 200-264     | 100-132     | 4:8                         | 800-1056   |

| 101        | 1:1       | 100-132     | 100-132     | 6:6                         | 600-792    |

| 110        | 1:1       | 100-132     | 100-132     | 10:10                       | 1000-1320  |

| 111        | n/a       | n/a         | n/a         | n/a                         | n/a        |

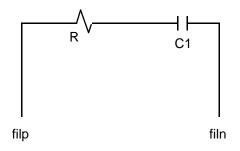

## LOOP FILTER COMPONENT SELECTION

$R = 500\Omega \pm 10\%$

$C1 = 1000pF \pm 10\%$

## PRODUCT ORDERING CODE

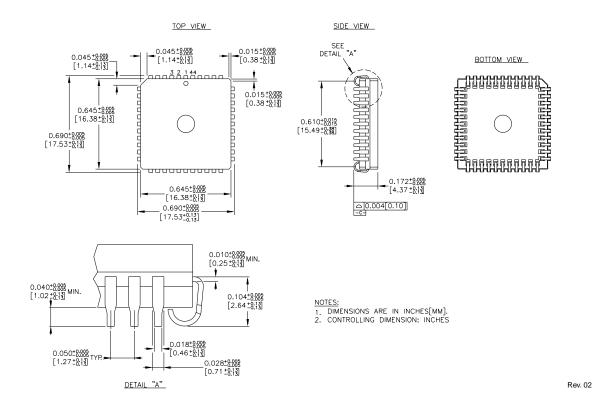

| Ordering<br>Code | Package<br>Type | Operating<br>Range |

|------------------|-----------------|--------------------|

| SY89801AMC       | M44-1           | Commercial         |

| SY89801AMCA(1)   | M44-1           | Commercial         |

#### NOTES:

1. "A" denotes enhanced 200MHz testing.

## 44 LEAD MLCC (M44-1)

### MICREL-SYNERGY 3250 SCOTT BOULEVARD SANTA CLARA CA 95054 USA

TEL + 1 (408) 980-9191 FAX + 1 (408) 914-7878 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 2000 Micrel Incorporated