### Features

- LIN-Bus transceiver according to LIN specification 1.3

- o PNP-bipolar driver with slew rate control and wave shaping for good EME behaviour

- $\circ$  BUS input voltage -24V to 30V (independently of V<sub>SUP</sub>)

- Current limitation

- Possibility of BUS wake up

- o Baud rate up to 20 kBaud

- □ Operating voltage V<sub>SUP</sub> = 5.5 ... 18 V

- $\Box$  Very low standby current consumption < 110  $\mu$ A in normal mode (< 50  $\mu$ A in sleep mode)

- Linear low drop voltage regulator

- Output voltage 5V± 1%

- o Output current max. 100mA

- o Output current limitation

- Overtemperature shutdown

- □ Configurable reset time (15ms/100ms) and reset threshold voltage (3.15V / 4.65V)

- □ Low voltage detection at VSUP

- U Wake-up by LIN BUS traffic and start-up capable independent of EN voltage level

- □ Universal comparator with an input voltage range –24V to 30V and digital output

- □ Load dump protected (40V)

- □ SOIC16 Package with 4 GND connection for better thermal dissipation

| Ordering Information |  |

|----------------------|--|

|----------------------|--|

| Part No. | Temperature Range | Package             |

|----------|-------------------|---------------------|

| TH8060   | J (-40 to 125 °C) | DF (SOIC16, 300mil) |

# **General Description**

The RELIN TH8060 consist a low drop voltage regulator 5V/100mA and a LIN Bus transceiver. The LINtransceiver is suitable for LIN-Bus systems conform to "LIN-Protocol Specification" Rev.1.3. The combination of voltage regulator and bus transceiver in combination with the monitoring functions make it possible to develop simple, but powerful and cheap slave nodes in LIN Bus systems.

The wide output current area and the configurable reset time and reset voltage works together with many different microcontrollers.

# Contents

| 1.                                                                                                                                      | Functional Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 2.                                                                                                                                      | Electrical Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                               |

| 2.                                                                                                                                      | 2.1 Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                               |

|                                                                                                                                         | 2.2 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                 |

|                                                                                                                                         | 2.3 Static Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                 |

|                                                                                                                                         | 2.4 Dynamic Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |

|                                                                                                                                         | 2.5 Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |

| 2.                                                                                                                                      | 2.6 Test Circuit for Dynamic and Static Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                 |

| 3.                                                                                                                                      | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                              |

| 3.                                                                                                                                      | 3.1 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |

| 3.                                                                                                                                      | 3.2 LIN BUS Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                 |

|                                                                                                                                         | 3.3 Linear Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                 |

|                                                                                                                                         | 3.4 RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                 |

|                                                                                                                                         | 3.5 Reset Programmming on VTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |

|                                                                                                                                         | 3.6 Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                 |

|                                                                                                                                         | 3.7 Mode Input EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

|                                                                                                                                         | 3.8 Wake-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |

|                                                                                                                                         | <ul> <li>3.9 Overtemperature Shut Down</li> <li>3.10 Low Voltage Detection at VSUP</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |

|                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

| .5                                                                                                                                      | 3.11 Universal Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                                                              |

| 3.<br><b>4.</b>                                                                                                                         | 3.11 Universal Comparator Application Hints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |

| 4.                                                                                                                                      | Application Hints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                                                                              |

| 4.                                                                                                                                      | Application Hints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>18</b><br>                                                                                                   |

| 4.                                                                                                                                      | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>18</b><br>                                                                                                   |

| <b>4.</b><br>4.<br>4.                                                                                                                   | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>18</b><br>                                                                                                   |

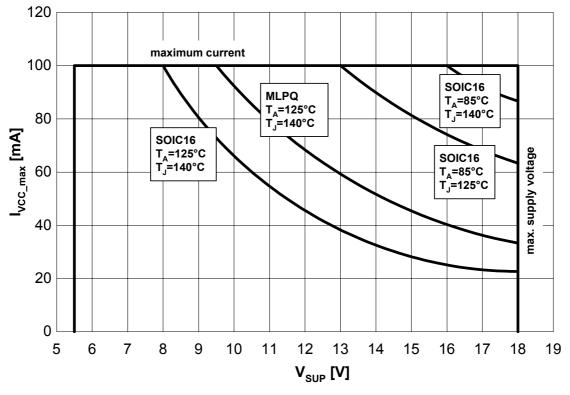

| <b>4.</b><br>4.<br>4.<br>4.                                                                                                             | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>18</b><br>                                                                                                   |

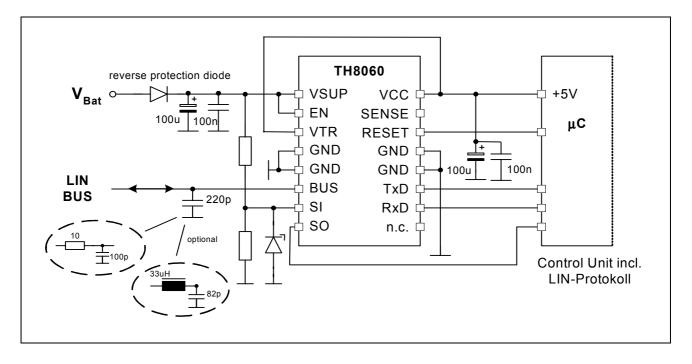

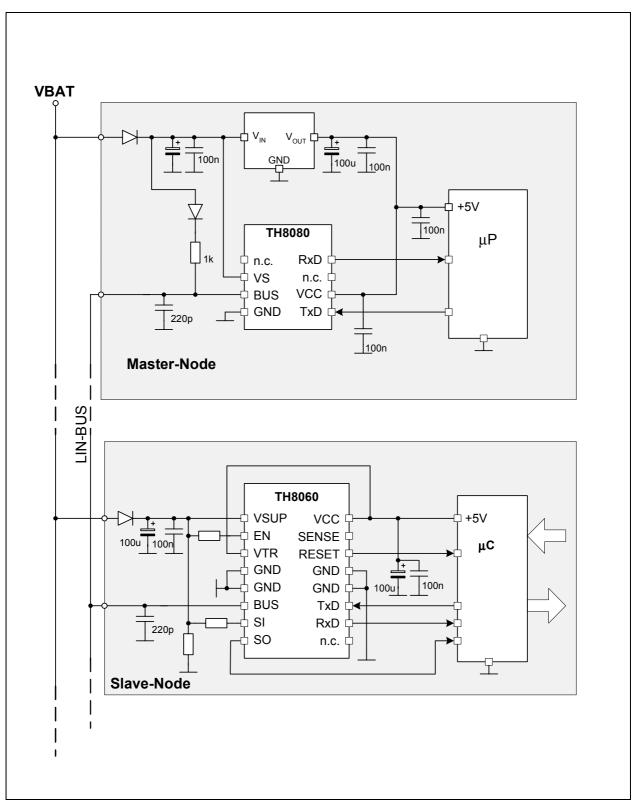

| <b>4.</b><br>4.<br>4.<br>4.<br>4.                                                                                                       | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>18</b><br>18<br>18<br>19<br>20<br>21<br>22                                                                   |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.                                                                                           | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>18</b><br>18<br>18<br>19<br>20<br>21<br>22<br>22                                                             |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.                                                                                     | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>18</b><br>18<br>18<br>19<br>20<br>21<br>22<br>22<br>22<br>22                                                 |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.                                                                                     | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>18</b><br>18<br>18<br>19<br>20<br>21<br>22<br>22<br>22<br>22                                                 |

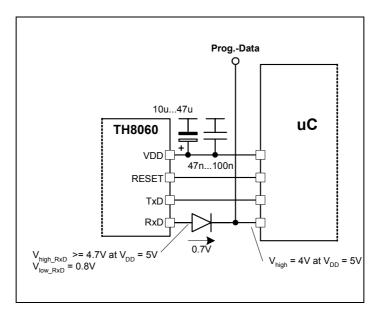

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.                                                                                     | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>18</b><br>18<br>18<br>19<br>20<br>21<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22 |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>5.                                                                                     | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU         Description of the system of the | <b>18</b> 18 18 19 20 21 22 22 22 22 22 24 <b>25</b> 25                                                         |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>5.<br>5.<br>5.                                                                         | Application Hints         4.1       LIN System Parameter         4.1.1       Bus loading requirements         4.1.2       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU         5.1       Operating without VSUP or GND         5.2       Short Circuit BUS against VBAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>18</b> 18 18 19 20 21 22 22 22 22 22 24 <b>25</b> 25                                                         |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>5.<br>5.<br>5.<br>5.<br>5.                                                             | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design.         4.2       Min/max slope time calculation.         4.3       Power Dissipation and operating range.         4.4       Regulator circuitry.         4.5       Application circuitry.         4.6       EMI Supressing         4.7       Connection to Flash-MCU <b>Operating during Disturbance</b> 5.1       Operating without VSUP or GND         5.2       Short Circuit BUS against VBAT         5.3       Short Circuit BUS against GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>18</b> 18 18 19 20 21 22 22 22 22 22 24 <b>25</b> 25 25                                                      |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.                                                             | Application Hints         4.1       LIN System Parameter         4.1.1       Bus loading requirements         4.1.2       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU <b>Operating during Disturbance</b> 5.1       Operating without VSUP or GND         5.2       Short Circuit BUS against VBAT         5.3       Short Circuit TxD against GND         5.4       Short Circuit TxD against GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>18</b> 18 18 19 20 21 22 22 22 22 22 24 <b>25</b> 25 25 25                                                   |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.                                                 | Application Hints         4.1       LIN System Parameter         4.1.1       Bus loading requirements         4.1.2       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU         5.1       Operating during Disturbance         5.2       Short Circuit BUS against VBAT         5.3       Short Circuit BUS against GND         5.4       Short Circuit TxD against GND         5.5       TxD open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>18</b> 18 18 19 20 21 22 22 22 22 22 24 <b>25</b> 25 25 25 25 25 25 25 25 25 25 25 25 25                     |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.                                     | Application Hints         4.1       LIN System Parameter         4.1.1       Bus loading requirements         4.1.2       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU         5.1       Operating during Disturbance         5.2       Short Circuit BUS against VBAT         5.3       Short Circuit BUS against GND         5.4       Short Circuit TxD against GND         5.5       TxD open         5.6       Short Circuit VCC against GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>18</b> 18 18 19 20 21 22 22 22 22 22 22 22 22 22 22 24 24 25 25 25 25 25 25 25 25 25 25 25 25 25             |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.                   | Application Hints         4.1       LIN System Parameter         4.1.1.       Bus loading requirements         4.1.2.       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU         Operating during Disturbance         5.1       Operating without VSUP or GND         5.2       Short Circuit BUS against VBAT         5.3       Short Circuit BUS against GND         5.4       Short Circuit TxD against GND         5.5       TxD open         5.6       Short Circuit VCC against GND         5.7       Overload of VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>18</b> 18 18 19 20 21 22 22 22 22 22 22 22 22 22 24 <b>25</b> 25 25 25 25 25 25 25 25 25 25 25 25 25         |

| <b>4.</b><br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5.<br>5. | Application Hints         4.1       LIN System Parameter         4.1.1       Bus loading requirements         4.1.2       Recommendations for system design         4.2       Min/max slope time calculation         4.3       Power Dissipation and operating range         4.4       Regulator circuitry         4.5       Application circuitry         4.6       EMI Supressing         4.7       Connection to Flash-MCU         5.1       Operating during Disturbance         5.2       Short Circuit BUS against VBAT         5.3       Short Circuit BUS against GND         5.4       Short Circuit TxD against GND         5.5       TxD open         5.6       Short Circuit VCC against GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>18</b> 18 18 19 20 21 22 22 22 22 22 22 22 22 22 22 24 24 25 25 25 25 25 25 25 25 25 25 25 25 25             |

# TH8060

Voltage Regulator with integrated LIN Transceiver

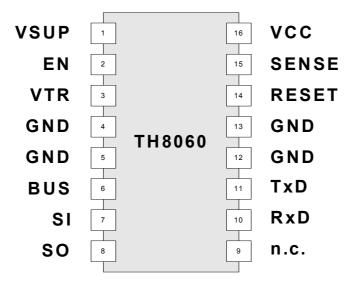

| 6.  | PIN Description SOIC16WB | 26 |

|-----|--------------------------|----|

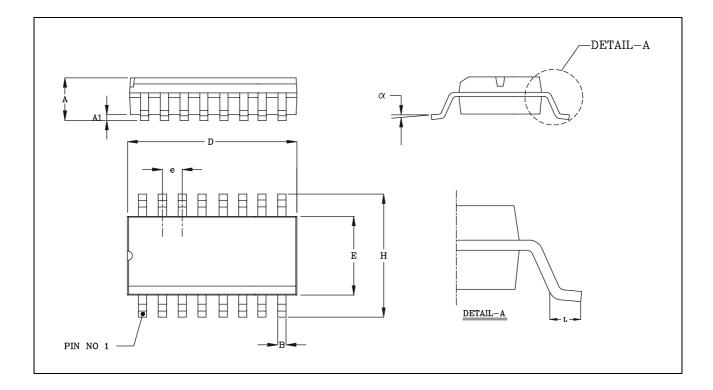

| 7.  | Mechanical Specification | 27 |

| 8.  | ESD/EMC Remarks          |    |

| 8.  | .1 General Remarks       |    |

| 8.  | .2 ESD-Test              |    |

| 8.  | .3 EMC                   |    |

| 9.  | Reliability Information  | 29 |

| 10. | Disclaimer               | 29 |

# **List of Figures**

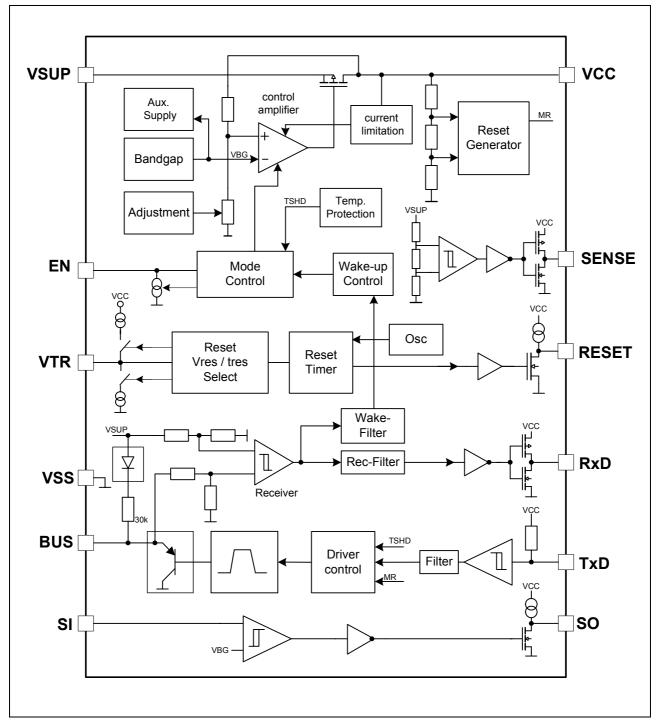

| Figure 1- Block diagram                                                          | 4    |

|----------------------------------------------------------------------------------|------|

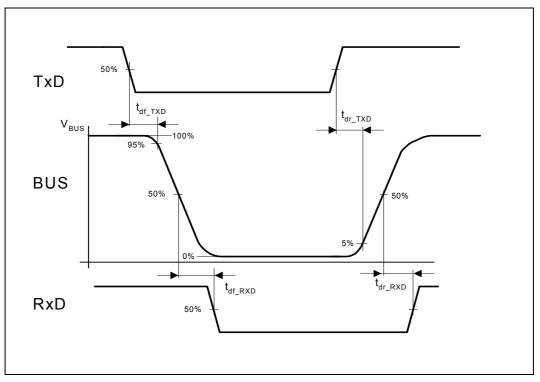

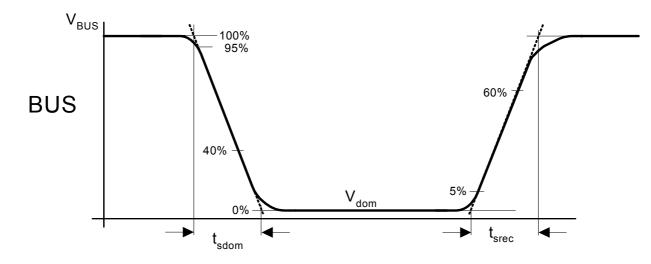

| Figure 2 - Timing diagram for propagation delay                                  | 10   |

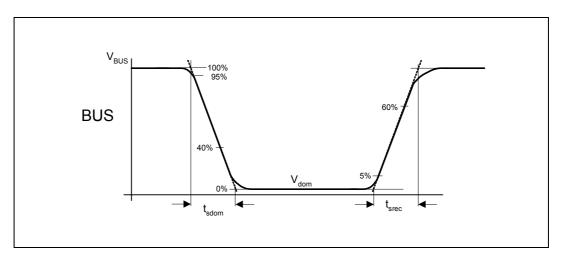

| Figure 3 - Timing diagram for slope times                                        | . 10 |

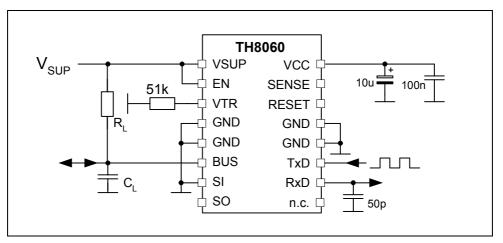

| Figure 4 - Test circuit for delay time and slope control                         | . 11 |

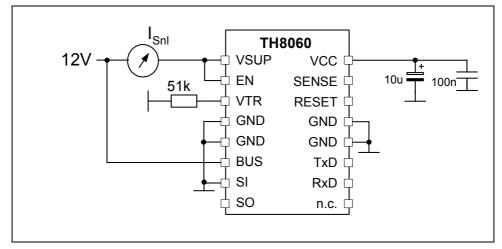

| Figure 5 - Test circuit for supply current I <sub>SnI</sub>                      | . 11 |

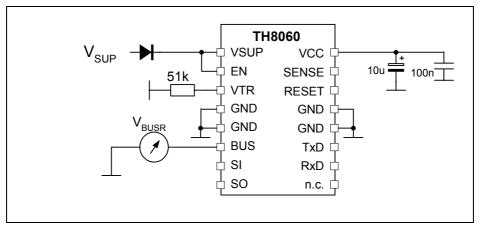

| Figure 6 - Test circuit for bus voltage "recessiv" V <sub>BUSR</sub>             | . 12 |

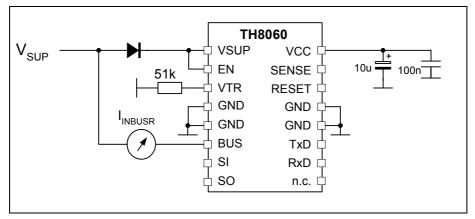

| Figure 7 - Test circuit for bus current "recessiv" I <sub>BUSR</sub>             | . 12 |

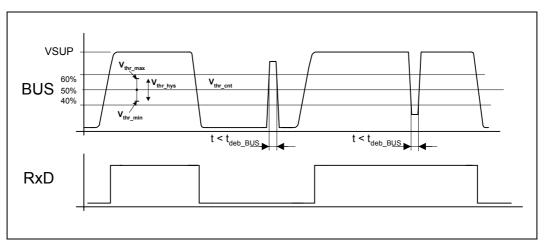

| Figure 8 - Receive mode impulse diagram                                          | .14  |

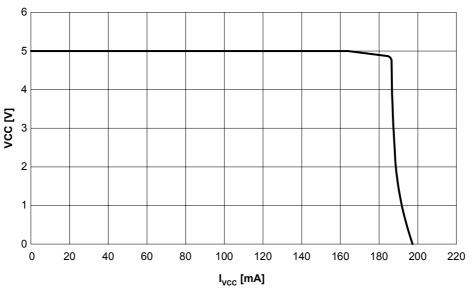

| Figure 9 - Characteristic of current limitation VCC = f(I <sub>VCC</sub> )       | . 15 |

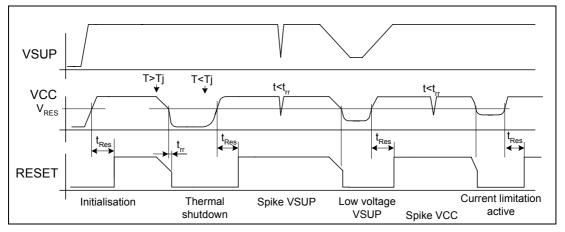

| Figure 10 - Reset behaviour                                                      | . 15 |

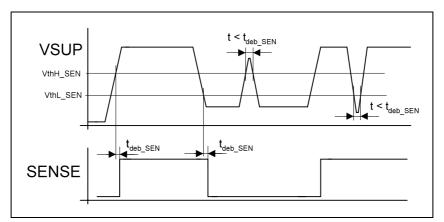

| Figure 11 - Low Voltage Detection                                                | . 17 |

| Figure 12 - Slope time calculation                                               | 20   |