19-0379; Rev 0; 3/95

##

### 155Mbps/622Mbps Clock Recovery and Data Retiming IC with Fully Integrated Phase/Frequency Detector

#### General Description

The MAX3270 is a complete Clock Recovery and Data Retiming IC for 155Mbps and 622Mbps SDH/SONET and ATM applications. The MAX3270 meets Bellcore and CCITT jitter tolerance specifications ensuring errorfree data recovery. Recovered clock and data are phase aligned using a fully integrated phase-locked loop (PLL). An output frequency monitor (FM) is included to detect loss of PLL acquisition or a loss of input data.

The MAX3270 has differential ECL input and output interfaces, so it is less susceptible to noise in a high-frequency environment. The fully integrated PLL includes an integrated phase-frequency detector that eliminates the need for external references.

#### Applications

155Mbps (STM-1/OC-3)/622Mbps (STM-4/ OC-12) SDH/SONET Transmission Systems 155Mbps/622Mbps ATM/SONET Access Nodes Add/Drop Multiplexers Cross-Connects

#### \_\_Features

- Supports Both 155Mbps and 622Mbps Clock Recovery and Data Retiming

- Fully Integrated Phase/Frequency Detector

- Capable of Switching to an External Clock

- Differential 100K ECL Data and Clock I/Os

- Output Monitor Provides Lock Detection

- No External Reference Clock Required

#### Ordering Information

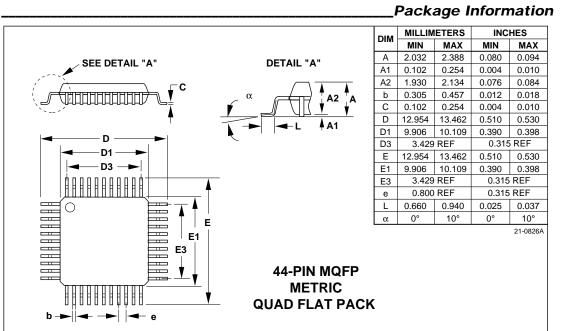

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX3270EMH | -40°C to +85°C | 44 MQFP     |

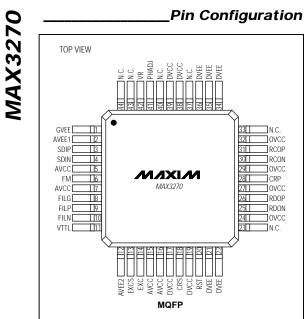

Pin Configuration appears at end of data sheet.

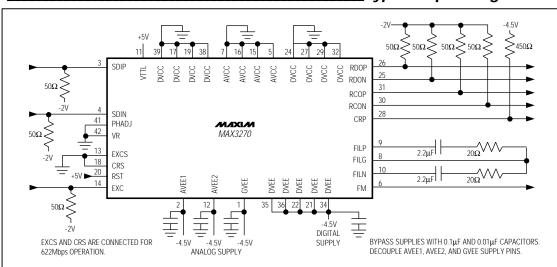

#### Typical Operating Circuit

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

<sup>///</sup>XI//I

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltages             |               |

|-----------------------------|---------------|

| VTTL to GND                 | 0.5V to +8.0V |

| V <sub>CC</sub> to GND      | 0.5V to +8.0V |

| V <sub>EE</sub> to GND      | 8.0V to +0.5V |

| SDIP, SDIN, EXC             | 8.0V to +0.5V |

| RDOP, RDON, RCOP, RCON, CRP | 8.0V to +0.5V |

| EXCS, RST, CRS              | 0.5V to +8.0V |

| FILP, FILG, FILN            | 8.0V to +0.5V |

| PHADJ, VR8.0V to +8.0V                                    |

|-----------------------------------------------------------|

| FM8.0V to +8.0V                                           |

| Input Differential Voltage Level, SDIP, SDIN+3.0V         |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C)1.3W |

| Operating Temperature Range40°C to +85°C                  |

| Storage Temperature Range                                 |

| Lead Temperature (soldering, 10sec)+300°C                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VEE = -4.5V  $\pm$ 5%, VTTL = 5V  $\pm$ 5%, TA = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                                           | SYMBOL           | CONDITIONS                                  | MIN    | TYP   | MAX    | UNITS |

|-----------------------------------------------------|------------------|---------------------------------------------|--------|-------|--------|-------|

| Positive Voltage Supply<br>(with respect to ground) | V <sub>TTL</sub> |                                             | 4.75   | 5.00  | 5.25   | V     |

| Negative Voltage Supply<br>(with respect to ground) | V <sub>EE</sub>  |                                             | -4.725 | -4.50 | -4.275 | V     |

| Static Supply Current from VTTL                     | ITTL             |                                             |        | 2.4   | 5      | mA    |

| Static Supply Current from VEE                      | IVEE             |                                             |        | 150   | 210    | mA    |

| ECL INPUTS: EXC, SDIP, SDIN                         |                  |                                             |        |       |        |       |

| Input High Voltage                                  | VIH              |                                             | -1165  |       | -870   | mV    |

| Input Low Voltage                                   | VIL              |                                             | -1830  |       | -1475  | mV    |

| Input High Current                                  | Ιн               | V <sub>IN</sub> = V <sub>OH</sub> (typ)     | 0      |       | 100    | μΑ    |

| Input Low Current                                   | l <sub>IL</sub>  | $V_{IN} = V_{OL}$ (typ)                     | -100   |       | 100    | nA    |

| ECL OUTPUTS: RCOP, RCON, RDO                        | OP, RDON         |                                             |        |       |        |       |

| Output High Voltage                                 | Voh              | Loaded with 50 $\Omega$ to -2V              | -1025  | -955  | -870   | mV    |

| Output Low Voltage                                  | Vol              | Loaded with 50 $\Omega$ to -2V              | -1830  | -1705 | -1550  | mV    |

| LOW-POWER ECL OUTPUT: CRP                           |                  |                                             |        |       |        |       |

| Output High Voltage                                 | Voh              | Loaded with 470 $\Omega$ to V <sub>EE</sub> | -1025  | -955  | -870   | mV    |

| Output Low Voltage                                  | Vol              | Loaded with 470 $\Omega$ to V <sub>EE</sub> | -1830  | -1705 | -1620  | mV    |

| TTL INPUTS: CRS, RST, EXCS                          | 1                |                                             | -      |       |        |       |

| Input High Voltage                                  | VIH              |                                             | 2      |       |        | V     |

| Input Low Voltage                                   | VIL              |                                             |        |       | 0.8    | V     |

| Input High Current                                  | lін              | VTTL = 5.00V, VIN = 2V                      | 0      |       | 40     | μΑ    |

| Input Low Current                                   | l <sub>IL</sub>  | VTTL = 5.00V, VIN = 0.8V                    | 0      |       | 40     | μΑ    |

| PHASE ADJUST INPUTS: PHADJ,                         | VR               | 1                                           |        |       |        |       |

| Input Bias Current                                  | IBIAS            | $VR = PHADJ = 0, T_A = +25^{\circ}C$        | 0      |       | 10     | μA    |

#### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{EE} = -4.5V, VTTL = 5V, T_A = 25^{\circ}C, unless otherwise noted.)$

| PARAMETER                                                                    | SYMBOL                          | CONDITIONS                                    | MIN   | TYP    | MAX   | UNITS  |

|------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------|-------|--------|-------|--------|

| ECL OUTPUTS: RDOP, RDON, RCOP,                                               | RCON                            |                                               | 1     |        |       | 1      |

| Transition Time 20% to 80%                                                   | t <sub>r</sub> , t <sub>f</sub> | Loaded with 50 $\Omega$ to -2V and 5pF to GND |       | 600    |       | ps     |

| Time Difference between RDO and RCO                                          | TD                              | Loaded with 50 $\Omega$ to -2V and 5pF to GND |       | 100    |       | ps     |

| PFD AND FILTER AMPLIFIER TEST LE                                             | VELS                            |                                               |       |        |       |        |

| Output Offset Voltage of the<br>Monitor Amplifier                            | Vo                              | PHADJ = 0, FILP and FILN shorted              | -35   |        | 35    | mV     |

| Gain of the Monitor Amplifier                                                | GFM                             | PHADJ = 0                                     | 0.95  |        | 1.05  | V/V    |

| Filter Amplifier Open-Loop Voltage Gain                                      | GOL                             | FILP and FILN open                            | 21    | 26     |       | dB     |

| VCO TEST PARAMETERS; CPR OUTP                                                | UT                              |                                               | 1     |        |       |        |

| Center Frequency                                                             | Fo                              | FILP and FILN shorted,<br>PFD = neutral state | 38.00 |        | 39.50 | MHz    |

| Frequency Range                                                              | DFo                             | FILP - FILN = 1.6V                            | 6     |        | 10    | MHz    |

| Mean Frequency Sensitivity                                                   | Ko                              | FILP - FILN = 1.6V                            | 3.75  |        | 6     | MHz/V  |

| Frequency Sensitivity to<br>Power-Supply Voltage                             | Kov                             | FILP and FILN shorted                         |       |        | 550   | kHz/V  |

| PLL ELECTRICAL SPECIFICATIONS                                                |                                 |                                               |       |        |       |        |

| Frequency of VCO                                                             | Fo                              |                                               |       | 622.08 |       | MHz    |

| Incremental Tuning Sensitivity (Incremental Slope, $\Delta f / \Delta V t$ ) | Ko                              | f <sub>t</sub> = 622.08MHz                    |       | 75     |       | MHz/V  |

| Phase-Detector Gain                                                          | KD                              |                                               |       | 192    |       | mV/rac |

| Transconduction Gain of Filter Amplifier                                     | Gm                              |                                               |       | 1.25   |       | mA/V   |

| Phase Offset Sensitivity, $\Delta \Phi / \Delta P HADJ$                      | Kphadj                          |                                               |       | 2      |       | rad/V  |

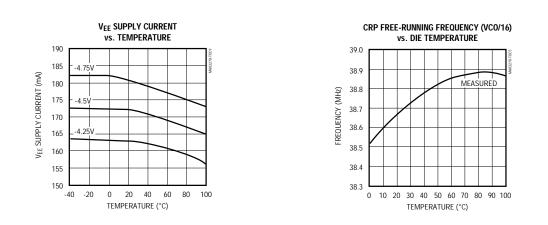

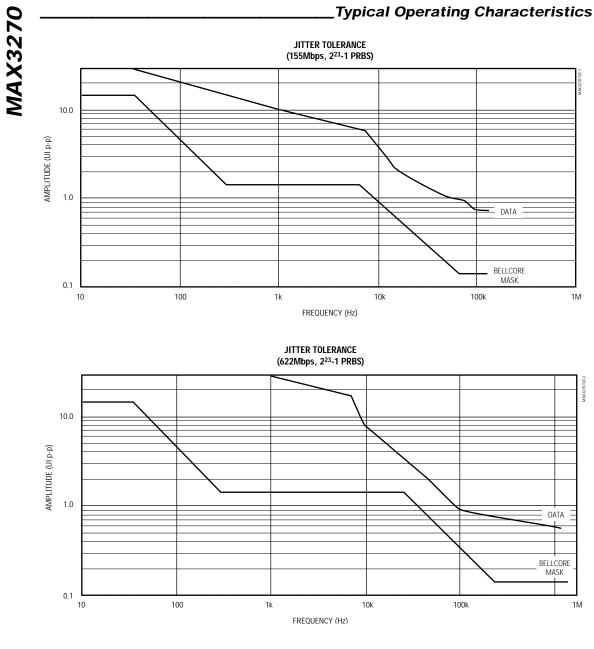

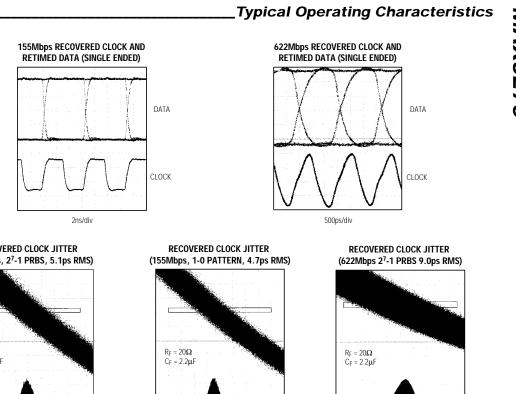

## Typical Operating Characteristics

**M/IXI/M**

MAX3270

M/XI/M

**RECOVERED CLOCK JITTER** (155Mbps, 27-1 PRBS, 5.1ps RMS)

10ps/div  $\mu \pm 1\sigma$  68.961% Mean 40.61ns μ±2**σ** 95.844% RMSA 5.13ps μ±3σ 99.717% PkPk 45.6ps

10ps/div μ±1σ 69.674% Mean 40.65ns . μ±2σ 95.558% RMS $\Delta$  4.7ps PkPk 38.4ps μ±3σ 99.698%

| 3/01/        |

|--------------|

| μ±1σ 69.747% |

| μ±2σ 95.453% |

| μ±3σ 99.582% |

|              |

MAX3270

|                           |       | Pin Description                                                                                                                                                                                  |

|---------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                       | NAME  | FUNCTION                                                                                                                                                                                         |

| 1                         | GVEE  | Guard-Ring Negative Supply to Substrate: -4.5V                                                                                                                                                   |

| 2                         | AVEE1 | Negative Supply for Input Buffers: -4.5V                                                                                                                                                         |

| 3                         | SDIP  | Serial Data Input: 155Mbps or 622Mbps. Differential ECL Positive.                                                                                                                                |

| 4                         | SDIN  | Serial Data Input: 155Mbps or 622Mbps. Differential ECL Negative.                                                                                                                                |

| 5                         | AVCC  | Ground for Input Buffers: 0V                                                                                                                                                                     |

| 6                         | FM    | Frequency Monitor Output. This pin monitors the input voltage to the VCO. When the PLL is locked, the pin will be $\cong$ 0V.                                                                    |

| 7                         | AVCC  | Guard-Ring Positive Supply to Epi: 0V                                                                                                                                                            |

| 8                         | FILG  | Loop Filter Ground. This pin connects to an external filter.                                                                                                                                     |

| 9                         | FILP  | Loop Filter Positive. This pin connects to an external filter.                                                                                                                                   |

| 10                        | FILN  | Loop Filter Negative. This pin connects to an external filter.                                                                                                                                   |

| 11                        | VTTL  | TTL Positive Supply: +5.0V                                                                                                                                                                       |

| 12                        | AVEE2 | Negative Supply for VCO: -4.5V                                                                                                                                                                   |

| 13                        | EXCS  | External Clock-Select TTL Input. A logical high selects the external clock.                                                                                                                      |

| 14                        | EXC   | External Clock. Single-ended ECL input.                                                                                                                                                          |

| 15, 16                    | AVCC  | Ground for VCO: 0V                                                                                                                                                                               |

| 17, 19, 38,<br>39         | DVCC  | Digital Ground for Mux: 0V                                                                                                                                                                       |

| 18                        | CRS   | Clock-Rate Select TTL Input. This selects the clock rate to be either 155Mbps or 622Mbps. A logic-<br>high level selects the 622Mbps mode.                                                       |

| 20                        | RST   | Resets all digital flip-flops, TTL input. Reset is assert when low.                                                                                                                              |

| 21, 22, 34,<br>35, 36     | DVEE  | Digital Negative Supply: -4.5V                                                                                                                                                                   |

| 23, 33, 37,<br>40, 43, 44 | N.C.  | No Connection                                                                                                                                                                                    |

| 24, 27, 29,<br>32         | OVCC  | Output Driver Ground: 0V                                                                                                                                                                         |

| 25                        | RDON  | Negative Recovered Data Output, differential ECL output: 155Mbps or 622Mbps.                                                                                                                     |

| 26                        | RDOP  | Positive Recovered Data Output, differential ECL output: 155Mbps or 622Mbps.                                                                                                                     |

| 28                        | CRP   | Clock-Reference Output Divide-by-4. ECL low-power single-ended: 38Mbps or 155Mbps.                                                                                                               |

| 30                        | RCON  | Negative Recovered Clock Output, differential ECL output: 155Mbps or 622Mbps.                                                                                                                    |

| 31                        | RCOP  | Positive Recovered Clock Output, differential ECL output: 155Mbps or 622Mbps.                                                                                                                    |

| 41                        | PHADJ | Phase Adjust. This is an analog adjustment that varies the static phase between the input data and the recovered clock. If not used, this input should be grounded. The range is from -1V to 1V. |

| 42                        | VR    | Phase Reference Voltage: 0V. The PHADJ pin compares to this voltage. Set to ground.                                                                                                              |

6 \_

#### Detailed Description

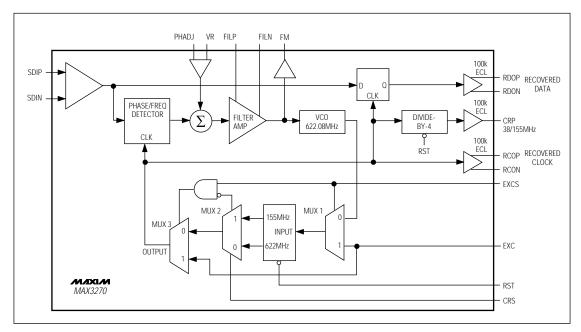

The block diagram of Figure 1 shows the MAX3270's architecture. The phase-locked loop (PLL) consists of a phase/frequency detector (PFD), a loop filter amplifier, and a voltage-controlled oscillator (VCO).

#### Phase Detector

The phase detector produces a voltage proportional to the phase difference of the incoming data and the output of the recovered clock. Because of its feedback nature, the PLL will drive the error voltage to zero, making the phase difference zero and aligning the recovered clock to the incoming data. An external phase-adjustment pin (PHADJ) allows the user to vary phase alignment.

#### Frequency Detector

A frequency detector is also incorporated into the PLL. Frequency detection aids in the acquisition of the input data; this frequency-aided acquisition is necessary during start-up conditions, since the input data stream and VCO difference frequency may be outside the PLL bandwidth. The input data stream is sampled by quadrature components of the VCO clock, generating a difference frequency. Depending on the rotation of the difference frequency, the PFD will drive the VCO so that the difference frequency is driven to zero. Once frequency acquisition is obtained, the frequency detector will return to a neutral state.

#### Loop Filter and VCO

The PLL is a second-order transfer function whose bandwidth is set by the loop filter. The VCO is integrated into the PLL and always operates at 622MHz. The center frequency is tightly controlled by laser trimming, limiting frequency drift when lock is lost. 155Mbps or 622Mbps mode is selected by the clock-rate select (CRS) pin. CRS selects the inputs to multiplexer MUX2.

The internal VCO can be bypassed with an external clock applied to the EXC input. The external clock select (EXCS) controls the input selections to multiplexers MUX1 and MUX2.

Figure 1. Block Diagram

M/IXI/N

MAX3270

#### \_\_\_Design Procedure

Phase/Frequency Detector

#### Selecting the Data Rate

155Mbps/622Mbps Clock Recovery and Data Retiming IC with Fully Integrated

The MAX3270 is intended for use in SDH/SONET systems operating at 155.52Mbps or 622.08Mbps data rates. TTL inputs (CRS and EXCS) are provided for selecting the recovered clock rate (Table 1). It is also possible to switch to an externally supplied clock by enabling the EXC input. The EXC input is a high-speed single-ended ECL interface capable of handling serial clock rates of 155MHz and 622MHz.

|  | Table | 1. | <b>MAX3270</b> | Loaic | Table |

|--|-------|----|----------------|-------|-------|

|--|-------|----|----------------|-------|-------|

| EXCS | CRS | RCOP/RCON  | CRP        |

|------|-----|------------|------------|

| 0    | 1   | 155.52Mbps | 38.88Mbps  |

| 0    | 0   | 622.08Mbps | 155.52Mbps |

| 1    | 0   | EXC        | EXC/4      |

| 1    | 1   | EXC/4      | EXC/16     |

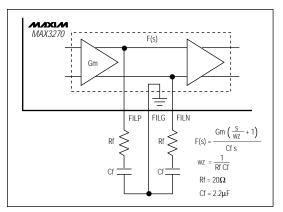

#### Setting the Loop Filter

The loop filter within the PLL consist of a transconductance amplifier and the external filter elements Rf and Cf (Figure 2). The closed-loop bandwidth of a PLL can be approximated by:

#### K<sub>D</sub> K<sub>O</sub> Gm Rf

where  $K_D$  is the gain of the phase detector, KO is the gain of the VCO, and Gm is the transconductance of the filter amplifier. Because this filter is an integrator, a zero in the open-loop gain is required for stability. This zero is set by the following equation:

#### $w_z = 1 / (Rf Cf)$

where the recommended external values are Rf =  $20\Omega$  and Cf =  $2.2\mu$ F. To decrease the PLL's closed-loop bandwidth, reduce the value of Rf. Decreasing this bandwidth will improve the MAX3270's jitter transfer performance but reduce jitter tolerance. The MAX3270 has been designed (using the recommended values of Rf and Cf) to meet the Bellcore and CCITT specifications for jitter tolerance of a Network Element. Carefully consider the application if a reduction in loop bandwidth is desired. By reducing Rf an order of magnitude, the PLL's bandwidth becomes more sensitive to the internal tolerances of the IC. As a result, the loop bandwidth may have a wider variation. If Rf is reduced, then Cf should also be increased to maintain loop stability and minimize jitter peaking.

Figure 2. Loop Filter

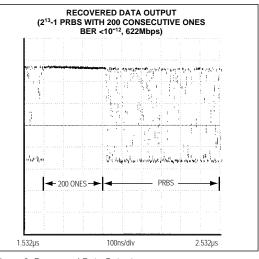

Figure 3. Recovered Data Output

The MAX3270 is optimally designed to acquire lock and to provide a bit-error rate (BER) of less than  $10^{-12}$  for long strings of consecutive zeros or ones. Using the recommended external values for Rf =  $20\Omega$  and Cf =  $2.2\mu$ F, measured results show that the MAX3270 can tolerate more than 200 consecutive ones or zeros. Figure 3 shows a bit stream of  $2^{13}$  - 1 PRBS with 200 consecutive ones.

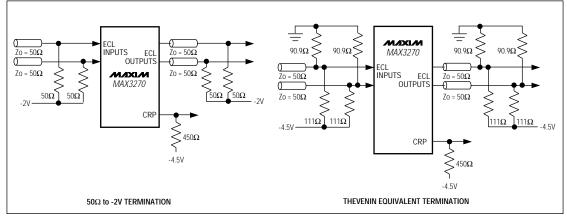

#### Input and Output Termination

The MAX3270 data and clock I/Os (SDIP, SDIN, RDOP, RDON, RCOP, RCON, and EXC) are open emitters, designed to interface with ECL signal levels. It is important to bias these ports appropriately. A circuit that provides a Thevenin equivalent of  $50\Omega$  to -2V should be used with fixed-impedance transmission lines for proper termination. Figure 4 shows some typical input and output termination methods.

The serial data input signals (SDIP and SDIN) are the differential inputs to an emitter coupled pair. As a result, the MAX3270 can accept differential input signal levels as low as 250mV. The serial input (SDIP) can also be driven single-ended by externally biasing SDIN to the center of the voltage swing (approximately -1.3V). Make sure that the differential inputs and outputs each see the same termination impedance for balanced operation.

CRP is also an open-emitter ECL output, but it requires a termination resistor of 450 $\Omega$  to -4.5V. If this output is not used, reduce power by connecting CRP to V<sub>EE</sub> through a resistor valued at 10k $\Omega$  or more.

The MAX3270's performance can be greatly affected by circuit board layout and design. Use good high-frequency design techniques, including minimizing ground inductances and using fixed-impedance transmission lines on the data and clock signals. Powersupply decoupling should be placed as close to the VEE and VTTL pins as possible. AVEE1, AVEE2 and GVEE should each have their own bypass/decoupling elements, independent of each other and any other - 4.5V supply. Make sure to isolate the inputs from the outputs to reduce feedthrough.

#### \_Applications Information

#### Lock Detection

MAX3270

The MAX3270 has an output (FM) that monitors the input voltage to the VCO. FM is an analog output that can be used as a flag to indicate that the PLL is locked. Under normal operation, the loop is locked and the FM output is approximately equal to 0V. When the PLL is unlocked, the VCO will drift. The FM output monitors this drift and will equal approximately  $\pm 1V$  in the limit.

#### Phase Adjust

In some applications, the optimum alignment point between the recovered clock and the serial data is not at the center of the eye diagram. The MAX3270 has a PHADJ input that can be used in these applications to introduce a phase difference between the recovered clock and the serial data. When no phase difference is desired, this input should be set to 0V. The VR pin is the reference input for PHADJ and is normally tied to GND.

Figure 4. Typical Input and Output Terminations

M/IXI/N

**MAX3270**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1995 Maxim Integrated Products

12

Printed USA

is a registered trademark of Maxim Integrated Products.