# GT-96100A

Datasheet Revision 1.0 3 October. 2000

#### **Advanced Communication Controller**

Please contact Galileo Technology for possible updates before finalizing a design.

### **FEATURES**

- Integrated communication controller and system controller with PCI interface for highperformance embedded control applications.

- Eight Multi-Protocol Serial Controllers (MPSCs):

- Support HDLC, BISYNC, UART and Transparent protocols.

- Bit rate of up to 55Mbit/s on multiple channels simultaneously.

- Can drive dedicated pins or use TDMs.

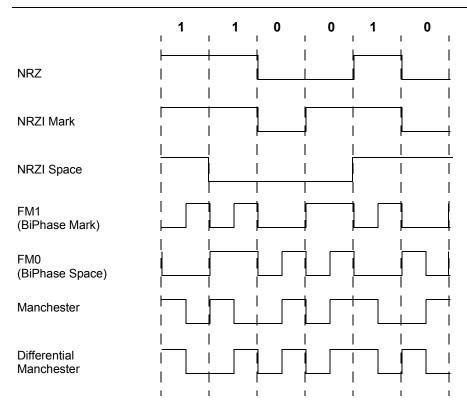

- Dedicated DPLL for clock recovery and data encoding/decoding.

- Supports NRZ, NRZI, FM0, FM1, Manchester and Differential Manchester.

- Hardware support for HDLC over asynchronous channel in UART mode.

- Four FlexTDM channels:

- Time slot assigner for serial and control channels.

- Supports up to four Basic Rate ISDN interfaces (2B+D) in GCI mode.

- Fully programmable via dual-port memory.

- Two 10/100Mbps Fast Ethernet MAC controllers:

- MII/RMII interface.

- Full duplex and flow-control support.

- Programmable perfect filtering of 1/2K or 8K MAC addresses (both physical and multicast).

- 2 Queues for Tx Priority queueing

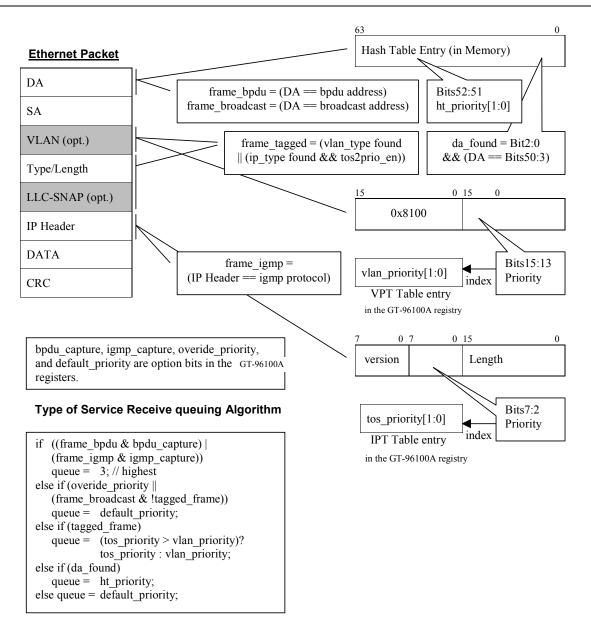

- 4 Queues for Priority queuing based on IP DSCP field or 802.1q tag or MAC address.

- IGMP and BPDU packet trapping.

- Twenty Serial DMA (SDMA) channels to support the communications and Ethernet controllers.

- Moves data between communications controllers and SDRAM/PCI.

- Buffer chaining via a linked list of descriptors.

- Eight baud rate generators with multiple clock sources.

- 64-bit CPU bus interface:

- Supports all 64-bit bus MIPS CPUs: RM5260, RM5270/1 and RM7000 from QED, RV4600 through RV5000 from IDT and R5000 compatibles from various vendors.

- 100MHz bus frequency.

- 3.3V bus interface.

- Support for multiple GT-96100A devices on the same SysAD bus (up to 4).

- 8x64-bit (64 byte) CPU write posting buffer accepts CPU writes with zero wait-states.

- CPU address remapping to resources.

- Zero wait state secondary cache support (L2 of R4xxx and R5000, L3 of R7000).

- Backward Software Compatibility with GT-64010A, GT-64011 and GT-64120.

- SDRAM controller:

- 3.3V (5V tolerant).

- 4GB address space.

- Supports 16/64/128/256/512Mbit SDRAM devices.

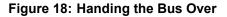

- Supports 64-bit registered SDRAM.

- Supports 2-way & 4-way SDRAM bank interleaving.

- Up to 4GB bank address space, 1MB granularity.

- 1 to 4 banks supported.

- 64-bit data width.

- ECC support for 64-bit SDRAM.

- Zero wait-state interleaved burst accesses at 100MHz.

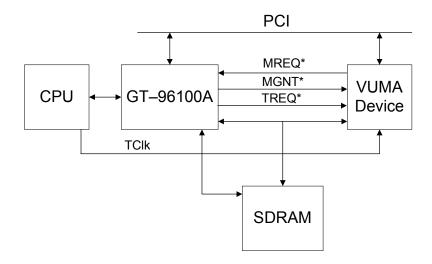

- Supports the VESA Unified Memory Architecture (VUMA) Standard allows for external masters access to SDRAM directly.

- · Device controller:

- 5 chip selects.

- Programmable timing for each chip select.

- Supports many types of standard memory and I/O devices.

- Up to 4GB address space.

- Optional external wait-state support.

- 8-,16-,32- and 64-bit width device support.

- Support for boot ROMs.

- Four Independent DMA (IDMA) channels:

- Chaining via linked-lists of records.

- Byte address boundary for source and destination.

- Moves data between PCI, memory, and devices.

- Two 64-byte internal FIFOs.

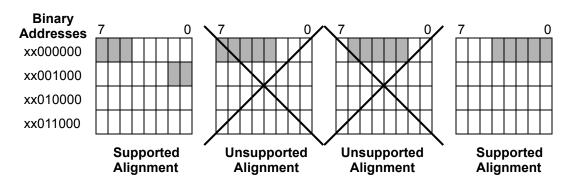

- Alignment of source and destination addresses.

- DMAs can be initiated by the CPU writing to a register, external request via DMAReq\* pin, or an internal timer/ counter.

- Termination of DMA transfer on each channel.

- Descriptor ownership transfer to CPU.

- Fly-By support for local data bus.

- Override capability of source/ destination/record address mapping.

- Two 32-bit or one 64-bit high-performance PCI 2.1 compliant devices:

- Dual mode PCI interface can be used as two independent 32-bit interfaces (synchronous or asynchronous to each other) or as a single 64-bit interface.

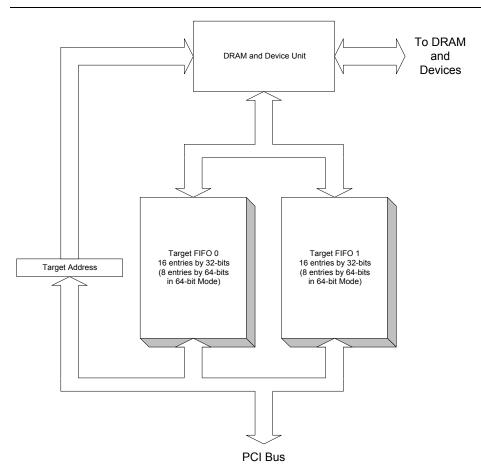

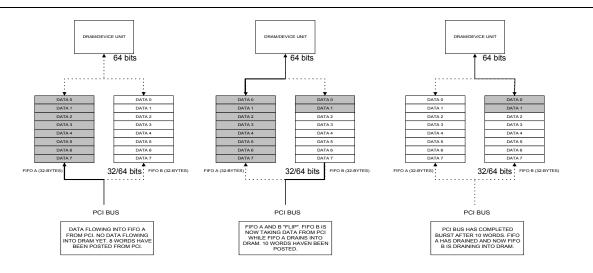

- 192-bytes of posted write and read prefetch buffers for each PCI interface.

- 32/64-bit PCI master and target operations.

- PCI bus speed of up to 66MHz with zero wait states.

- Universal PCI buffers (each 32-bit PCI use a different voltage).

- Operates either synchronous or asynchronous to the CPU clock.

- Burst transfers used for efficient data movement.

- Doorbell interrupts provided between CPU and PCI.

- Supports flexible byte swapping through PCI interface.

- Synchronization barrier support for PCI side.

- PCI address remapping to resources.

- Host to PCI bridge:

- Translates CPU cycles into PCI I/O or Memory cycles.

- Generates PCI Configuration, Interrupt Acknowledge, and Special cycles on PCI bus.

- PCI to Main Memory bridge:

- Supports fast back-to-back transactions.

- Supports memory and I/O transactions to internal configuration registers.

- Supports locked operations.

- I<sub>2</sub>O and Plug and Play Support:

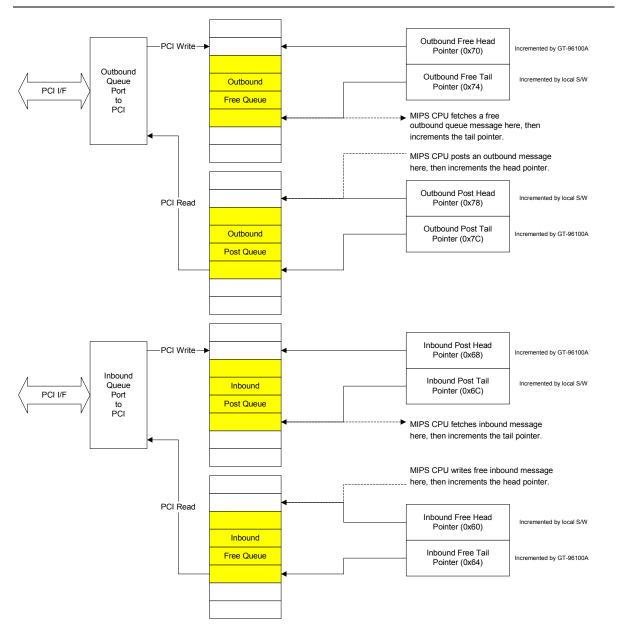

- Industry Standard I<sub>2</sub>O messaging unit on primary 32-bit PCI interface (also available in 64-bit mode).

- Plug and Play compatible configuration registers.

- PCI configuration header can be loaded from boot PROM.

- PCI configuration registers are accessible from both CPU and PCI bus.

- Expansion ROM support.

- PCI Hot-Plug and CompactPCI Hot-Swap capable compliant.

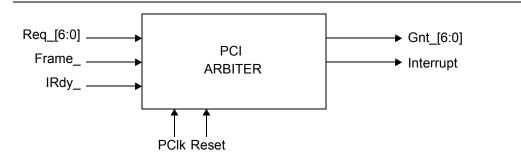

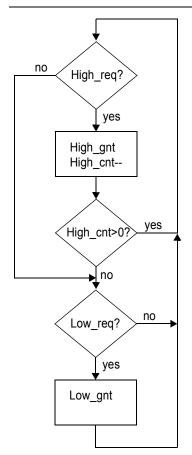

- Two programmable PCI Arbiter functions:

- Supports up to 9 external agents in addition to PCI\_0 and PCI\_1 internal devices.

- Two level priority arbitration capability

each request can be assigned either high or low priority.

- Two-stage watchdog timer (NMI, Reset).

- One 32-bit wide timer/counter, Three 24-bit wide timer/counters.

- Eighty-eight pins dedicated for peripheral functions and general purpose I/Os.

- Each pin can be configured independently as peripheral or General Purpose I/O.

- Supports simple I/O and LED control.

- Inputs can generate a maskable interrupt.

- 2.5V Core Supply Voltage, 3.3V I/O Supply Voltage (PCI and Peripherals).

- All inputs are 5V tolerant.

- JTAG Boundary Scan.

- 492 pin PBGA package.

- Advanced 0.25 micron CMOS process.

Part Number: GT-96100A Publication Revision: 1.0

©Galileo Technology, Inc.

No part of this datasheet may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the express written permission of Galileo Technology, Inc.

Galileo Technology, Inc. retains the right to make changes to these specifications at any time, without notice.

Galileo Technology, Inc. makes no warranty of any kind, expressed or implied, with regard to this material, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Galileo Technology, Inc. further does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within these materials. Galileo Technology, Inc. makes no commitment to update nor to keep current the information contained in this document.

Galileo Technology, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in Galileo Technology, Inc. products. No other circuit patent licenses are implied.

Galileo Technology, Inc. products are not designed for use in life support equipment or applications in which if the product failed it would cause a life threatening situation. Do not use Galileo Technology, Inc. products in these types of equipment or applications.

Contact your local sales office to obtain the latest specifications before finalizing your product.

Galileo Technology, Inc. 142 Charcot Avenue San Jose, California 95131 Phone: 1 408 367-1400 Fax: 1 (408) 367-1401 E-mail: info@galileot.com www.galileoT.com

Other brands and names are the property of their respective owners.

## TABLE OF CONTENTS

| 1. | Over        | view                                                      | 19 |

|----|-------------|-----------------------------------------------------------|----|

|    | 1.1         | Communication Unit Description                            | 19 |

|    | 1.2         | CPU Interface                                             | 21 |

|    | 1.3         | SDRAM and Device Interface                                | 21 |

|    | 1.4         | PCI Interface                                             | 21 |

|    | 1.5         | Independent DMA (IDMA) Engines                            | 22 |

|    | 1.6         | Peripheral Configurations                                 |    |

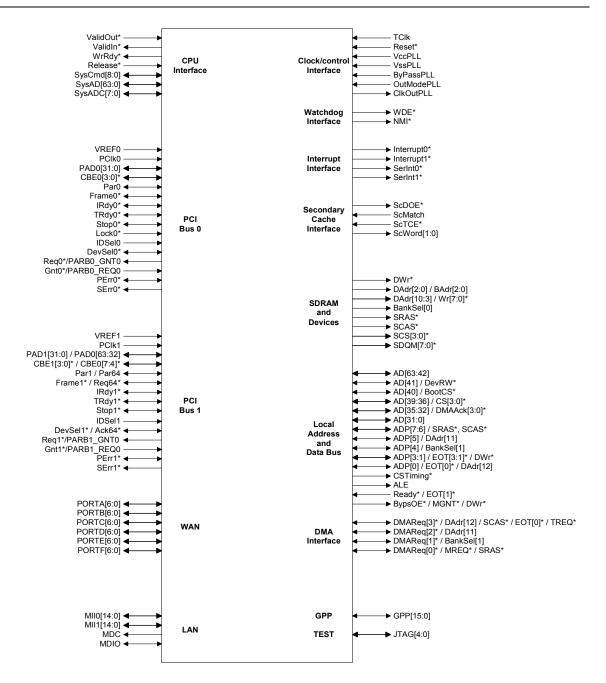

| 2. | Pin I       | nformation                                                | 25 |

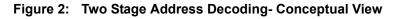

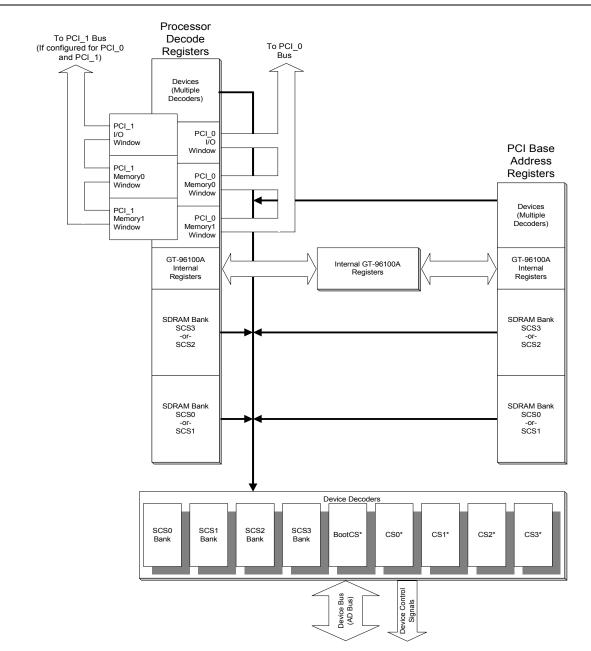

| 3. | ۸dd         | ress Space Decoding                                       | 56 |

| J. | 3.1         | Two Stage Decoding Process                                |    |

|    | 3.1         | Disabling Address Decoders                                |    |

|    | 3.2<br>3.3  | DMA Unit Address Decoding                                 |    |

|    | 3.3<br>3.4  |                                                           |    |

|    |             | Address Space Decoding Errors                             |    |

|    | 3.5         | Default Memory Map                                        |    |

|    | 3.6         | Address Remapping                                         |    |

|    | 3.7         | Using the CPU PCI Override.                               |    |

|    | 3.8         | Using the DMA to PCI Bypass.                              | 71 |

| 4. | CPU         | Interface Description                                     |    |

|    | 4.1         | CPU Interface Signals                                     | 72 |

|    | 4.2         | SysAD, SysADC, and SysCmd Buses                           |    |

|    | 4.3         | Operation of WrRdy* and the Internal Write Posting Queues | 79 |

|    | 4.4         | CPU Write Modes and Write Patterns Supported              | 79 |

|    | 4.5         | CPU Interface Endianess                                   | 80 |

|    | 4.6         | Burst Order                                               | 80 |

|    | 4.7         | MIPS L2 Cache Support                                     | 80 |

|    | 4.8         | Multiple GT-96100A Support.                               | 81 |

|    | 4.9         | CPU Interface Restrictions                                | 84 |

|    | 4.10        | CPU Interface Control Registers                           | 84 |

| 5. | Mem         | ory Controller                                            | 95 |

| •  | 5.1         | SDRAM Controller                                          |    |

|    | 5.2         | Connecting the Address Bus to the SDRAM.                  |    |

|    | 5.3         | Programmable SDRAM Parameters                             |    |

|    | 5.4         | SDRAM Performance                                         |    |

|    | 5.5         | SDRAM Bank Interleaving.                                  |    |

|    | 5.6         | Unified Memory Architecture (UMA) Support                 |    |

|    | 5.7         | Device Controller                                         |    |

|    | 5.8         | Programming the ADP lines for other Functions             |    |

|    | 5.8<br>5.9  | Memory Controller Restrictions                            |    |

|    | 5.9<br>5.10 | Registered SDRAM Interface Restrictions                   |    |

|    | 5.10        | Memory Interface Control Registers                        |    |

|    |             |                                                           |    |

| 6. |             | Integrity 1                                               |    |

|    | 6.1         | SDRAM ECC                                                 |    |

|    | 6.2         | PCI Parity Support                                        | 47 |

|     | <ul> <li>6.3 Parity Support for Devices</li> <li>6.4 CPU Parity Support</li> <li>6.5 Data Integrity Flow</li> <li>6.6 Register Information</li> <li>6.7 CPU Errors Report Registers</li> </ul>                                                                                                                                                                                                                                                                                                                                     | 147<br>148<br>150                                                                                                  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 7.  | PCI Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 152<br>157<br>161<br>162<br>163<br>166<br>167<br>167<br>167<br>168<br>168<br>169                                   |

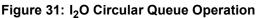

| 8.  | Intelligent I/O (I2O) Standard Support       2         8.1       Overview         8.2       I2O Registers         8.3       Enabling I2O Support         8.4       Register Map Compatibility with the i960Rx Family         8.5       Message Registers         8.6       Doorbell Registers         8.7       Circular Queues         8.8       I2O Support Registers                                                                                                                                                            | 201<br>203<br>203<br>203<br>203<br>204<br>204                                                                      |

| 9.  | Independent DMA Controllers (IDMA Controllers)       2         9.1       DMA Channel Registers.         9.2       DMA Channel Control Register (0x840 - 0x84c)         9.3       Restarting a Disabled Channel.         9.4       Reprogramming an Active Channel         9.5       Arbitration.         9.6       Current Descriptor Pointer Registers         9.7       Design Information         9.8       Initiating a DMA from a Timer/Counter.         9.9       DMA Restrictions         9.10       DMA Control Registers. | <ul> <li>219</li> <li>221</li> <li>224</li> <li>225</li> <li>225</li> <li>225</li> <li>230</li> <li>230</li> </ul> |

| 10. | PCI Arbiter       10.1         10.1       Interface         10.2       Arbitration Scheme         10.3       Arbitration Parking         10.4       PCI Arbiter Configuration Register                                                                                                                                                                                                                                                                                                                                             | 241<br>242<br>243                                                                                                  |

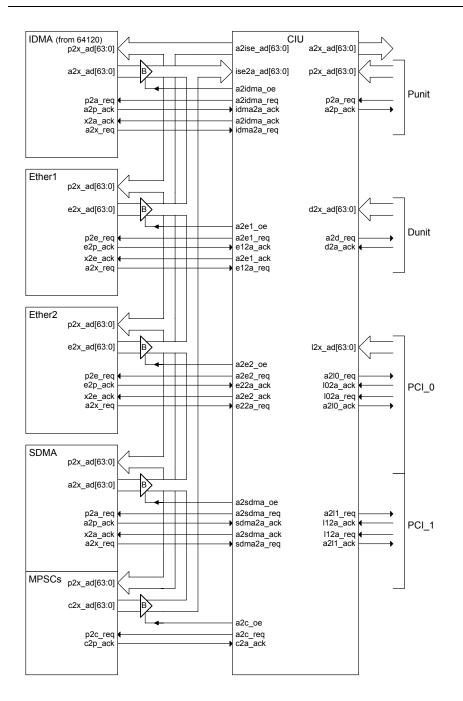

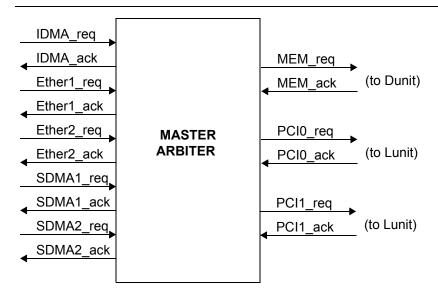

|     | Communication Interface Unit (CIU)                     | 246                                                                       |

|-----|--------------------------------------------------------|---------------------------------------------------------------------------|

|     | 11.1 CIU Connectivity                                  |                                                                           |

|     | 11.2 Address Decoding and PCI Override (MASTER)        |                                                                           |

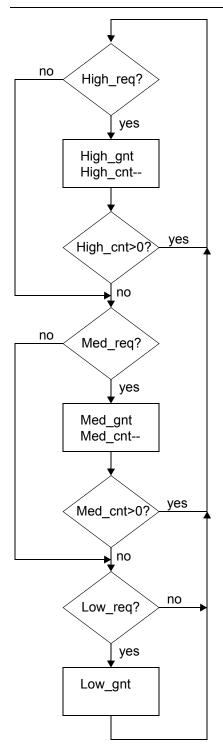

|     | 11.3 Arbitration Scheme                                |                                                                           |

|     | 11.4 CIU Arbiter Configuration Register                | 201                                                                       |

| 12. | 10/100Mb Ethernet Unit                                 |                                                                           |

|     | 12.1 Functional Overview                               |                                                                           |

|     | 12.2 Port Features                                     |                                                                           |

|     | 12.3 Operational Description                           |                                                                           |

|     | 12.4 Ethernet Port    12.5 Internal Control Registers  |                                                                           |

|     | 12.6 Ethernet MIB Counters                             |                                                                           |

|     |                                                        |                                                                           |

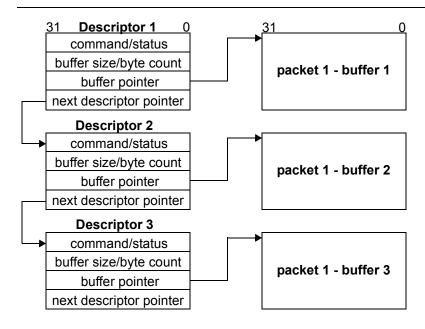

| 13. | Serial DMA (SDMA)                                      |                                                                           |

|     | 13.1 Overview                                          |                                                                           |

|     | <ul><li>13.2 SDMA Descriptors</li></ul>                |                                                                           |

|     | 13.4 SDMA Command Register (SDC)                       |                                                                           |

|     | 13.5 SDMA Group Configuration Register                 |                                                                           |

|     | 13.6 SDMA Descriptor Pointer Registers                 |                                                                           |

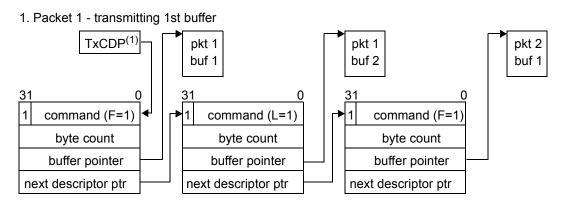

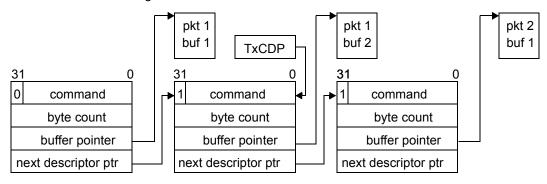

|     | 13.7 Transmit SDMA                                     |                                                                           |

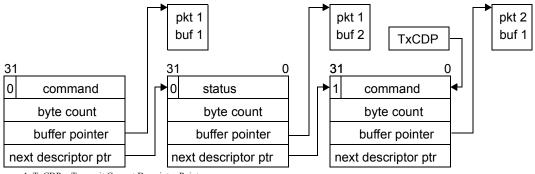

|     | 13.8 Receive SDMA                                      |                                                                           |

|     | 13.9 SDMA Interrupt and Mask register (SDI and SDM)    |                                                                           |

|     | 13.10 SDMA in Auto Mode                                | 319                                                                       |

|     | 13.11 SDMA Registers                                   | 320                                                                       |

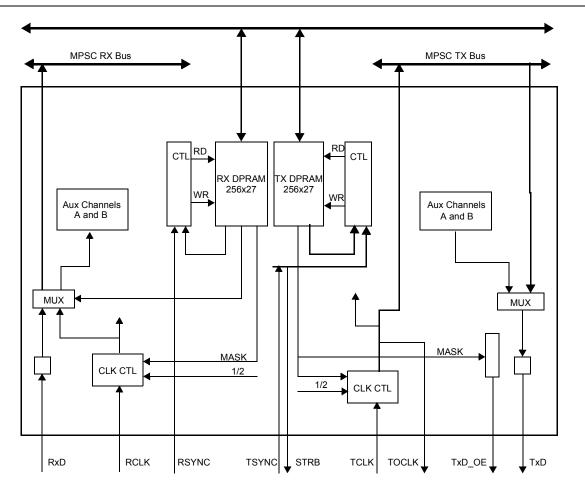

| 14. | Multi Protocol Serial Controller (MPSC)                | 326                                                                       |

|     | 14.1 DPLL                                              |                                                                           |

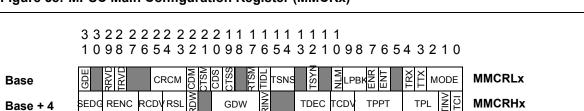

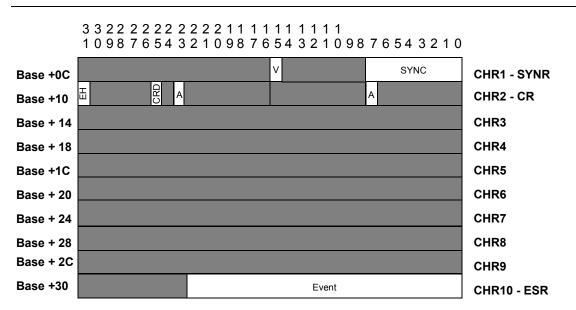

|     | 14.2 MPSCx Main Configuration Register (MMCRx)         | 328                                                                       |

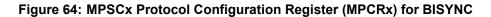

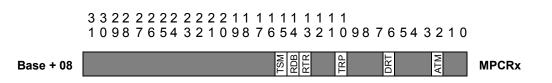

|     | 14.3 MPSCx Protocol Configuration Registers (MPCRx)    |                                                                           |

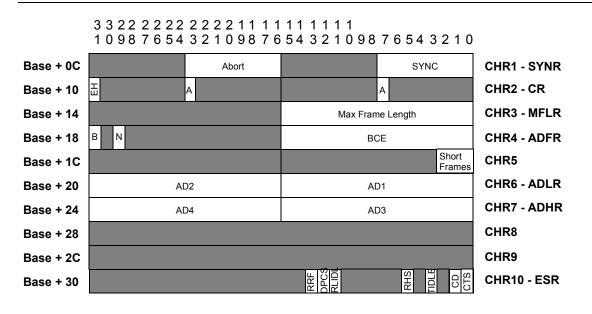

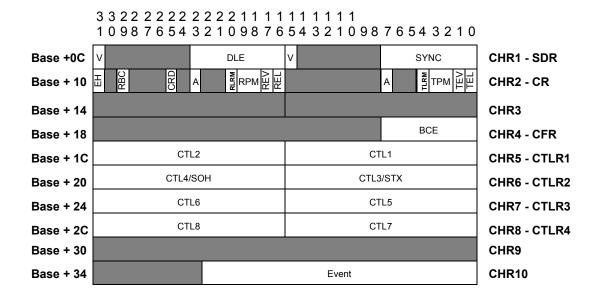

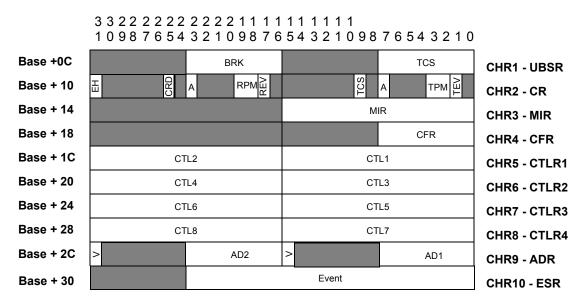

|     | 14.4 Channel Registers (CHxRx)                         |                                                                           |

|     | 14.5 HDLC Mode                                         |                                                                           |

|     | 14.6 BISYNC Mode                                       |                                                                           |

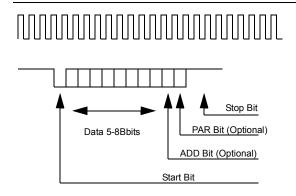

|     | 14.7 UART Mode                                         |                                                                           |

|     | 14.9 Transport Drotocol                                |                                                                           |

|     | 14.8 Transparent Protocol                              |                                                                           |

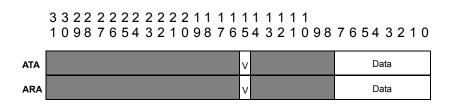

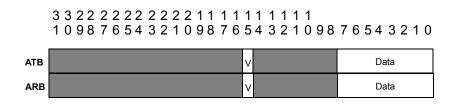

| 15. | FlexTDM Units (FTDM)                                   | 372<br><b>379</b>                                                         |

| 15. | FlexTDM Units (FTDM)                                   | 372<br><b>379</b><br>380                                                  |

| 15. | FlexTDM Units (FTDM)         15.1 FlexTDM Architecture | 372<br><b>379</b><br>380<br>380                                           |

| 15. | FlexTDM Units (FTDM)         15.1 FlexTDM Architecture | 372<br>379<br>380<br>380<br>383                                           |

| 15. | FlexTDM Units (FTDM)                                   | 372<br>379<br>380<br>380<br>383<br>383                                    |

| 15. | FlexTDM Units (FTDM)                                   | 372<br>379<br>380<br>380<br>383<br>384<br>386                             |

| 15. | FlexTDM Units (FTDM)                                   | 372<br>380<br>380<br>383<br>383<br>384<br>386<br>387                      |

| 15. | FlexTDM Units (FTDM)                                   | 372<br>380<br>380<br>383<br>384<br>386<br>387<br>388                      |

| 15. | FlexTDM Units (FTDM)                                   | 372<br>380<br>380<br>383<br>384<br>386<br>387<br>388<br>388               |

| 15. | FlexTDM Units (FTDM)                                   | 372<br>380<br>380<br>383<br>384<br>386<br>387<br>388<br>388<br>388<br>388 |

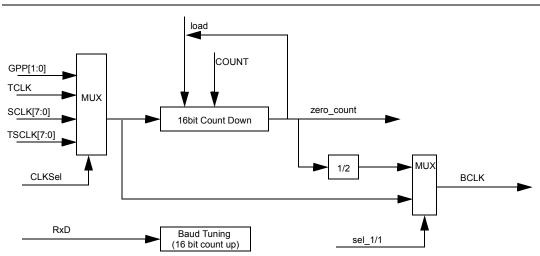

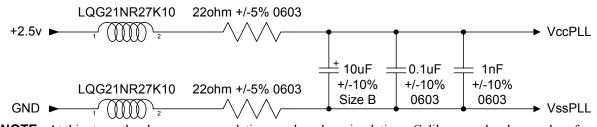

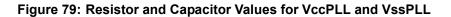

| 16.               | Baud Rate Generators (BRGs)         16.1 BRG Inputs and Outputs         16.2 BRG Baud Tuning         16.3 BRG Registers                                                                                                                                                                                                                                                                                                                   | . 397<br>. 397                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 17.               | Watchdog Timer         17.1 Watchdog Registers         17.2 Watchdog Operation                                                                                                                                                                                                                                                                                                                                                            | 401                                                                                                          |

| 18.               | Timers/Counters         18.1 Timer / Counter Registers                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| 19.               | General Purpose Ports         19.1 Overview         19.2 General Purpose Control Registers                                                                                                                                                                                                                                                                                                                                                | 405                                                                                                          |

| 20.               | Physical Signal Routing         20.1 Signal Routing         20.2 Clock Routing                                                                                                                                                                                                                                                                                                                                                            | 414                                                                                                          |

| 21.               | Interrupt Controller         21.1       Interrupt Cause Registers         21.2       Interrupt Mask Registers         21.3       Interrupt Summaries         21.4       Interrupt Select Registers         21.5       Interrupt Registers Tables                                                                                                                                                                                          | 424<br>425<br>426<br>426                                                                                     |

| 22.               | Reset Configuration                                                                                                                                                                                                                                                                                                                                                                                                                       | 452                                                                                                          |

| <b>LL</b> .       |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |

| 23.               | Connecting the Memory Controller to SDRAM and Devices                                                                                                                                                                                                                                                                                                                                                                                     | <b>455</b><br>455                                                                                            |

|                   | Connecting the Memory Controller to SDRAM and Devices                                                                                                                                                                                                                                                                                                                                                                                     | <b>455</b><br>455<br>456<br><b>460</b><br>460<br>461<br>461<br>461                                           |

| 23.               | Connecting the Memory Controller to SDRAM and Devices                                                                                                                                                                                                                                                                                                                                                                                     | <b>455</b><br>456<br><b>460</b><br>460<br>461<br>461<br>461<br>461<br>462<br><b>463</b>                      |

| 23.<br>24.        | Connecting the Memory Controller to SDRAM and Devices                                                                                                                                                                                                                                                                                                                                                                                     | <b>455</b><br>456<br><b>460</b><br>460<br>461<br>461<br>461<br>461<br>462<br><b>463</b><br>463<br>465        |

| 23.<br>24.<br>25. | Connecting the Memory Controller to SDRAM and Devices.         23.1 SDRAM         23.2 Devices.         JTAG Interface.         24.1 IEEE Standard 1149.1         24.2 TAP Controller         24.3 Instruction Register (IR).         24.4 Bypass Register (BR).         24.5 JTAG Scan Chain.         24.6 ID Register         Big and Little Endian         25.1 Background         25.2 Configuring a System for Big and Little Endian | <b>455</b><br>456<br>460<br>460<br>461<br>461<br>461<br>461<br>462<br><b>463</b><br>463<br>465<br><b>466</b> |

| 29. | System Configurations                                      | 475   |

|-----|------------------------------------------------------------|-------|

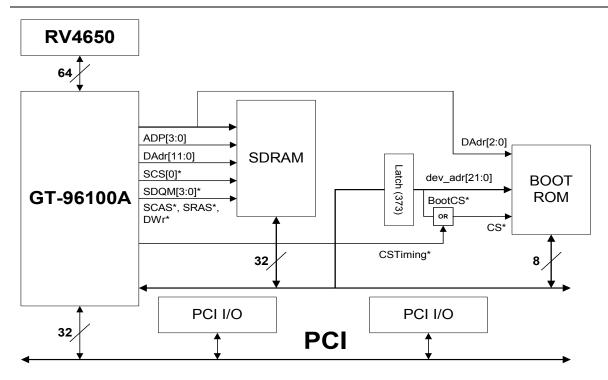

|     | 29.1 Minimal System Configuration                          |       |

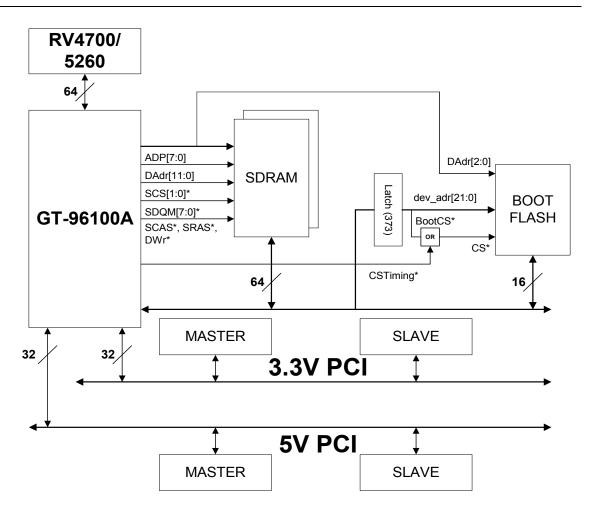

|     | 29.2 Typical System Configuration                          |       |

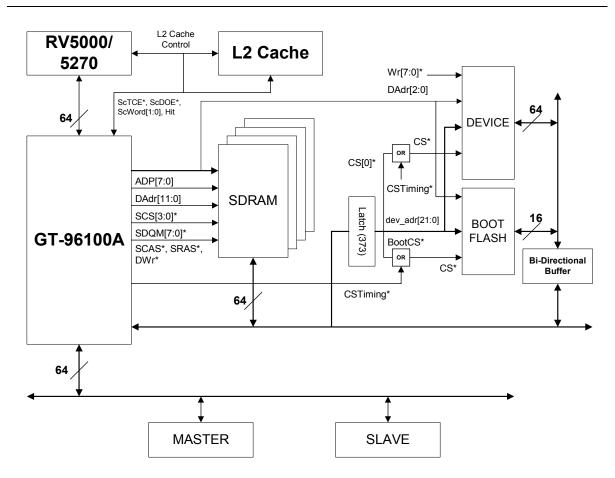

|     | 29.3 High Performance System.                              | . 477 |

| 30. | Register Tables                                            | 478   |

|     | 30.1 Access to On-Chip PCI Configuration Space Registers   | . 478 |

|     | 30.2 Register Maps                                         | . 479 |

| 31. | DC Characteristics                                         | 508   |

|     | 31.1 DC Electrical Characteristics Over Operating Range    | . 509 |

|     | 31.2 Thermal Data                                          | 512   |

| 32. | AC Timing                                                  | 513   |

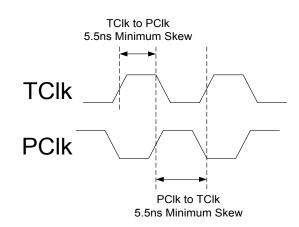

|     | 32.1 TClk/PClk Restrictions                                |       |

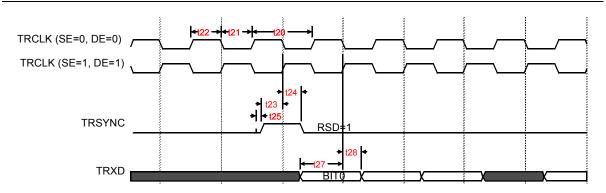

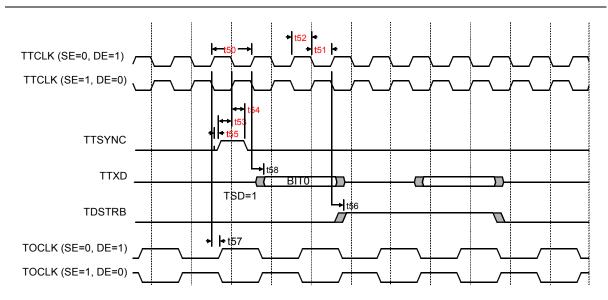

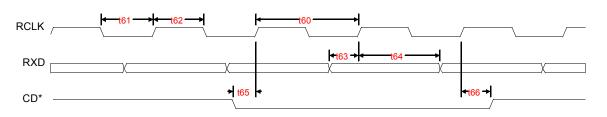

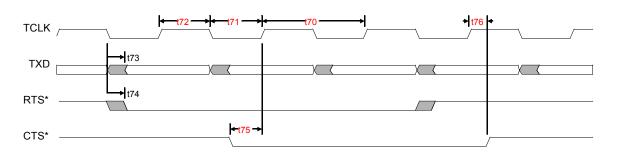

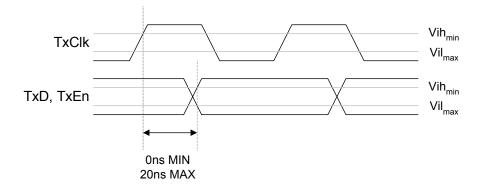

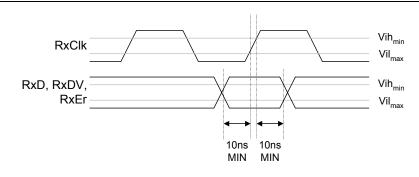

|     | 32.2 Serial (Communication) Clock Domain AC Characteristic | . 518 |

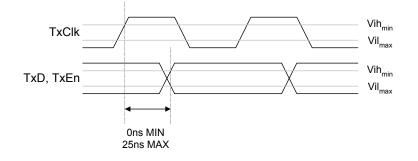

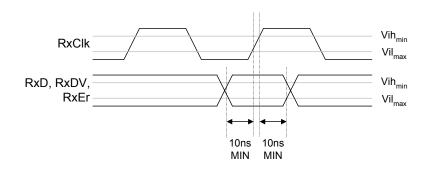

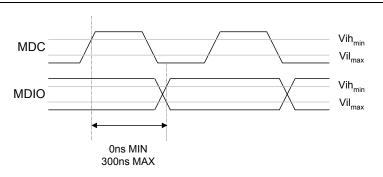

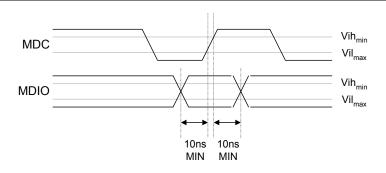

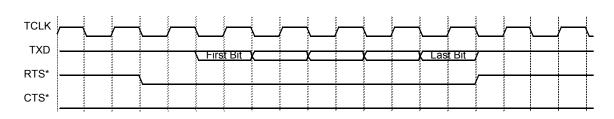

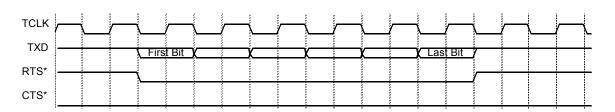

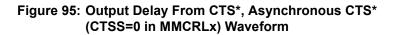

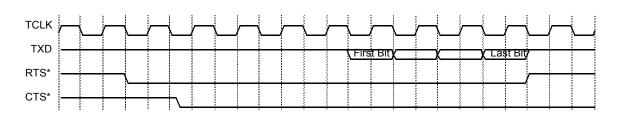

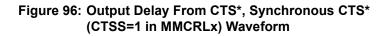

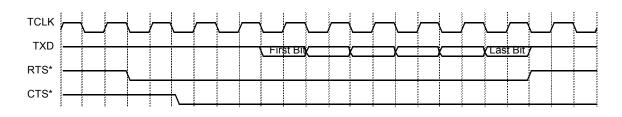

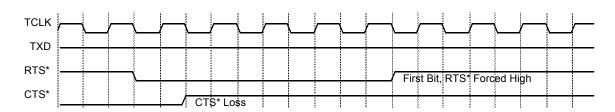

|     | 32.3 MPSC Waveforms                                        |       |

|     | 32.4 MII Waveforms                                         |       |

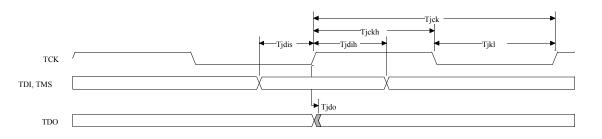

|     | 32.5 JTAG AC Characteristics.                              |       |

|     | 32.6 Additional Delay Due to Capacitive Loading            | . 531 |

| 33. | Pinout Table, 492 Pin BGA                                  | 533   |

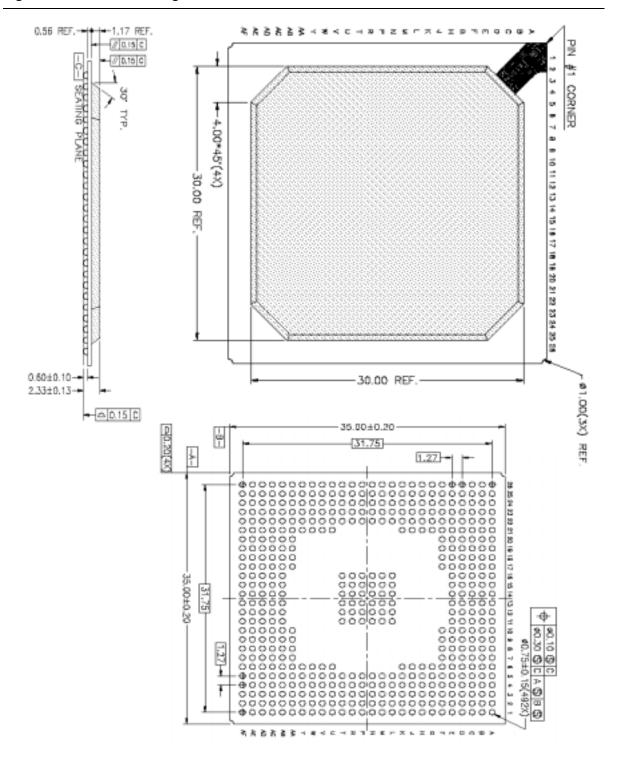

| 34. | 492 BGA Package Mechanical Information                     | 542   |

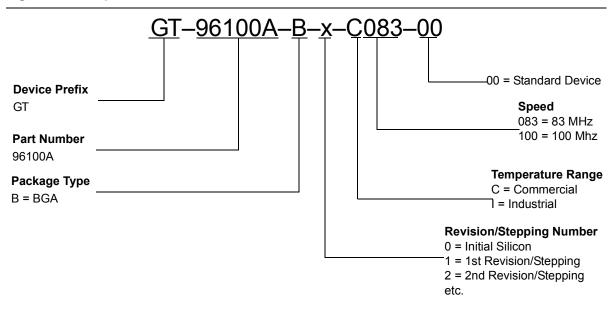

| 35. | GT–96100A Part Numbering                                   | 543   |

|     | 35.1 Standard Part Number                                  |       |

|     | 35.2 Valid Part Numbers                                    | . 543 |

| 36. | Abbreviations                                              | 544   |

| 37. | Revision History                                           | 515   |

| 57. |                                                            | J+J   |

## List of Tables

| 1. | Overview               |                                                                                | 19   |

|----|------------------------|--------------------------------------------------------------------------------|------|

|    | Table 1:               | GT–96100A Serial Performance                                                   | . 20 |

|    | Table 2:               | GT–96100A Port Configurations                                                  | . 23 |

|    | Table 3:               | GT–96100A Peripheral Configurations                                            | . 24 |

| 2. | Pin Information        | on                                                                             | 25   |

|    | Table 4:               | CPU Interface Pin Assignments                                                  |      |

|    | Table 5:               | Secondary Cache Interface Pin Assignments                                      | . 26 |

|    | Table 6:               | PCI Bus 0 Pin Assignments.                                                     | . 27 |

|    | Table 7:               | PCI Bus 1 Pin Assignments.                                                     | . 29 |

|    | Table 8:               | SDRAM and Devices Pin Assignments                                              | . 31 |

|    | Table 9:               | Local Address and Data Bus Pin Assignments                                     | . 32 |

|    | Table 10:              | DMA Pin Assignments                                                            | . 35 |

|    | Table 11:              | WAN Pin Assignments                                                            | . 36 |

|    | Table 12:              | LAN Pin Assignments                                                            |      |

|    | Table 13:              | GPP Pin Assignments                                                            |      |

|    | Table 14:              | Interrupt Interface Pin Assignments                                            |      |

|    | Table 15:              | Watchdog Interface Pin Assignments                                             |      |

|    | Table 16:              | Test Interface Pin Assignments.                                                |      |

|    | Table 17:              | Clock/Control Interface Pin Assignments                                        |      |

| 3. | Address Spa            | ce Decoding                                                                    | 56   |

|    | Table 18:              | CPU and Device Decoder Mappings.                                               | . 57 |

|    |                        | PCI_0 Base Address Register and Device Decoder Mappings                        |      |

|    |                        | PCI_1 Base Address Register and Device Decoder Mappings                        |      |

|    | Table 21:              | CPU and Device Decoder Default Address Mapping                                 |      |

|    | Table 22:              | PCI Function 0 and Device Decoder Default Address Mapping                      | . 65 |

|    | Table 23:              | PCI Function 1 (Byte Order Swap) and<br>Device Decoder Default Address Mapping | 66   |

|    | Table 24 <sup>.</sup>  | PCI Address Remapping Example                                                  |      |

|    |                        |                                                                                |      |

| 4. |                        | Description                                                                    |      |

|    | Table 25.<br>Table 26: | CPU Interface Signals                                                          |      |

|    |                        | Address Phase SysCmd[8:0] Encodings (driven by CPU)                            |      |

|    |                        | Read Response SysCmd[8:0] Encodings (driven by the GT-96100A)                  |      |

|    | Table 28.              | CPU Write SysCmd[8:0] Encodings (driven by local master)                       |      |

|    | Table 30:              | SysAD Read Phases                                                              |      |

|    | Table 31:              | SysAD Write Phases                                                             |      |

|    | Table 31:              | Pin Strapping the GT-96100A ID.                                                |      |

|    | Table 33:              | WrRdy*, ValidIn*, and ScDOE* Signal Multiple GT-96100A Functionality           |      |

|    | Table 34:              | Initializing a Multiple GT-96100A System                                       |      |

|    | Table 35:              | CPU Interface Register Map                                                     |      |

| F  |                        |                                                                                |      |

| 5. |                        | roller<br>DMAReq*, Ready* and BypsOE* Functionality                            |      |

|    |                        | Divinited, ready and bypoor rundlinding                                        | 101  |

|                  | Table 72:<br>Table 73:<br>Table 74:<br>Table 75:<br>Table 76:                                                                                                                                                                                                                                    | SysAD/PCI Address Decoding for 32-bit SDRAM, 16 Mbit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 104<br>. 105<br>. 105<br>. 106                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Table 77:<br>Table 78:                                                                                                                                                                                                                                                                           | Programmable SDRAM Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |

|                  | Table 70:                                                                                                                                                                                                                                                                                        | Events Determining PCI Read Performance from SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                  |

|                  | Table 80:                                                                                                                                                                                                                                                                                        | GT–96100A Sync. Modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |

|                  | Table 81:                                                                                                                                                                                                                                                                                        | SDRAM Performance Summary PCI Read Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

|                  | Table 82:                                                                                                                                                                                                                                                                                        | UMA AC Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |

|                  | Table 83:                                                                                                                                                                                                                                                                                        | ADP[7:0] Pin Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 125                                                                                                                                                                            |

|                  | Table 84:                                                                                                                                                                                                                                                                                        | 32-bit Device Limitations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 127                                                                                                                                                                            |

|                  | Table 85:                                                                                                                                                                                                                                                                                        | Memory Interface Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 128                                                                                                                                                                            |

| 6.               | Data Integrity                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 143                                                                                                                                                                              |

|                  |                                                                                                                                                                                                                                                                                                  | ECC Code Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                  |

|                  | Table 124:                                                                                                                                                                                                                                                                                       | Registers for Implementing Parity and ECC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 150                                                                                                                                                                            |

| 7.               | PCI Interfaces                                                                                                                                                                                                                                                                                   | \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 152                                                                                                                                                                              |

|                  |                                                                                                                                                                                                                                                                                                  | DevNum to IdSel Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |

|                  | Table 131:                                                                                                                                                                                                                                                                                       | PCI_0 Registers Loaded at RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 165                                                                                                                                                                            |

|                  | Table 132:                                                                                                                                                                                                                                                                                       | PCI_1 Registers Loaded at RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 165                                                                                                                                                                            |

|                  | Table 133:                                                                                                                                                                                                                                                                                       | PCI Control and Configuration Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 169                                                                                                                                                                            |

|                  |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                  |

| 8.               | Intelligent I/O                                                                                                                                                                                                                                                                                  | (I2O) Standard Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |

| 8.               | Intelligent I/O<br>Table 209:                                                                                                                                                                                                                                                                    | I2O PCI and CPU Offsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 202                                                                                                                                                                            |

| 8.               | Intelligent I/O<br>Table 209:<br>Table 210:                                                                                                                                                                                                                                                      | I2O PCI and CPU Offsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 202<br>. 203                                                                                                                                                                   |

| 8.               | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:                                                                                                                                                                                                                                        | I2O PCI and CPU Offsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 202<br>. 203<br>. 205                                                                                                                                                          |

| 8.               | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:                                                                                                                                                                                                                          | I2O PCI and CPU Offsets       Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses       I2O Circular Queue Functional Summary.                                                                                                                                                                                                                                                                                                                                                                                    | . 202<br>. 203<br>. 205<br>. 209                                                                                                                                                 |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:                                                                                                                                                                                                            | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map                                                                                                                                                                                                                                                                                                                                               | . 202<br>. 203<br>. 205<br>. 209<br>. 210                                                                                                                                        |

| 8.<br>9.         | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent                                                                                                                                                                                             | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).                                                                                                                                                                                                                                                                                                   | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. <b>219</b>                                                                                                                        |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:                                                                                                                                                                             | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.                                                                                                                                                                                                                                                          | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br><b>. 219</b><br>. 223                                                                                                               |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:                                                                                                                                                               | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP                                                                                                                                                                                                             | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br><b>. 219</b><br>. 223<br>. 223                                                                                                      |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:<br>Table 239:                                                                                                                                                 | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP                                                                                                                                                                     | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 219<br>. 223<br>. 223<br>. 223<br>. 223                                                                                           |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:<br>Table 239:<br>Table 240:                                                                                                                                   | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions                                                                                                    | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 219<br>. 223<br>. 223<br>. 223<br>. 223<br>. 225                                                                                  |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:<br>Table 239:<br>Table 240:<br>Table 241:                                                                                                                     | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions         Source and Data Transfer Examples                                                          | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 210<br>. 223<br>. 223<br>. 223<br>. 225<br>. 227                                                                                  |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:<br>Table 239:<br>Table 240:<br>Table 241:<br>Table 242:                                                                                                       | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions         Source and Data Transfer Examples         Fly-By Bits.                                     | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 210<br>. 223<br>. 223<br>. 223<br>. 223<br>. 225<br>. 227<br>. 229                                                                |

| 9.               | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:<br>Table 239:<br>Table 240:<br>Table 241:<br>Table 242:<br>Table 243:                                                                                         | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions         Source and Data Transfer Examples         Fly-By Bits.         DMA Control Register Map    | 202<br>203<br>205<br>209<br>210<br>223<br>223<br>223<br>225<br>225<br>227<br>229<br>231                                                                                          |

|                  | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:<br>Table 239:<br>Table 240:<br>Table 240:<br>Table 241:<br>Table 242:<br>Table 243:<br>PCI Arbiter                                                            | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions         Source and Data Transfer Examples         Fly-By Bits.                                     | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 210<br>. 223<br>. 223<br>. 223<br>. 225<br>. 227<br>. 229<br>. 231<br>. 231<br>. 241                                              |

| 9.               | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 239:<br>Table 239:<br>Table 240:<br>Table 241:<br>Table 242:<br>Table 243:<br>PCI Arbiter<br>Table 269:                                                                          | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions         Source and Data Transfer Examples         Fly-By Bits.         DMA Control Register Map    | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 210<br>. 223<br>. 223<br>. 223<br>. 225<br>. 227<br>. 229<br>. 231<br>. 221<br>. 241                                              |

| 9.<br>10.<br>11. | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 239:<br>Table 239:<br>Table 240:<br>Table 240:<br>Table 241:<br>Table 242:<br>Table 243:<br>PCI Arbiter<br>Table 269:                                                            | I2O PCI and CPU Offsets.         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions.         Source and Data Transfer Examples         Fly-By Bits.         DMA Control Register Map. | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 210<br>. 223<br>. 223<br>. 223<br>. 225<br>. 227<br>. 229<br>. 231<br>. 229<br>. 231<br>. 241<br>. 241<br>. 246                   |

| 9.<br>10.        | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 237:<br>Table 238:<br>Table 239:<br>Table 240:<br>Table 241:<br>Table 241:<br>Table 242:<br>Table 243:<br>PCI Arbiter<br>Table 269:<br>Communicati<br>10/100Mb Eth               | I2O PCI and CPU Offsets         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions         Source and Data Transfer Examples         Fly-By Bits.         DMA Control Register Map.   | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 210<br>. 223<br>. 223<br>. 223<br>. 223<br>. 225<br>. 227<br>. 229<br>. 231<br>. 241<br>. 241<br>. 241<br>. 241<br>. 246<br>. 253 |

| 9.<br>10.<br>11. | Intelligent I/O<br>Table 209:<br>Table 210:<br>Table 211:<br>Table 212:<br>Table 213:<br>Independent I<br>Table 238:<br>Table 239:<br>Table 239:<br>Table 240:<br>Table 240:<br>Table 241:<br>Table 242:<br>Table 243:<br>PCI Arbiter<br>Table 269:<br>Communicati<br>10/100Mb Eth<br>Table 273: | I2O PCI and CPU Offsets.         Register Differences Between the GT–96100A and i960Rx.         Circular Queue Starting Addresses         I2O Circular Queue Functional Summary.         I2O Support Register Map         DMA Controllers (IDMA Controllers).         Location of Source Address, SLP.         Location of Destination Address, DLP         Location of Record Address, RLP         IDMA Controller Design Information Terms and Definitions.         Source and Data Transfer Examples         Fly-By Bits.         DMA Control Register Map. | . 202<br>. 203<br>. 205<br>. 209<br>. 210<br>. 219<br>. 223<br>. 223<br>. 223<br>. 223<br>. 225<br>. 227<br>. 229<br>. 231<br>. 241<br>. 241<br>. 241<br>. 246<br>. 253<br>. 260 |

|     | Table 275: Ethernet TX Descriptor - Buffer Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | er                                                                                                                                                                     | 261                                                                                                                                                                                              |