## 32-bit Cascadable Barrel Shifter

### **FEATURES**

- 32-bit Input, 32-bit Output Multiplexed to 16 Lines

- ☐ Full 0-31 Position Barrel Shift Capability

- ☐ Integral Priority Encoder for 32-bit Floating Point Normalization

- ☐ Sign-Magnitude or Two's Complement Mantissa Representation

- ☐ 32-bit Linear Shifts with Sign or Zero Fill

- ☐ Independent Priority Encoder Outputs for Block Floating Point

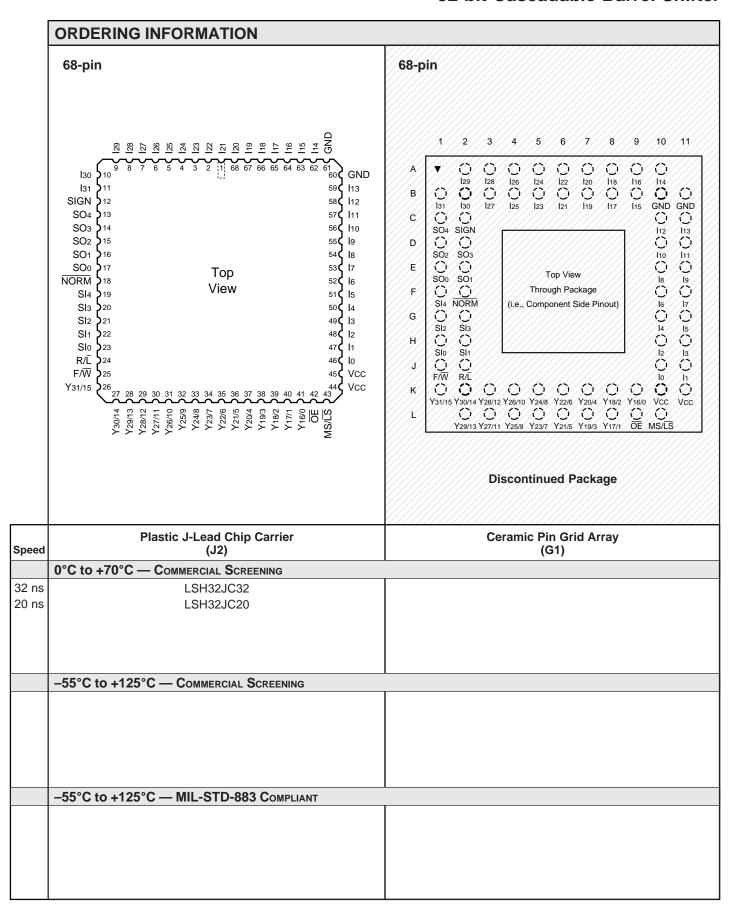

- ☐ 68-pin PLCC, J-Lead

### **DESCRIPTION**

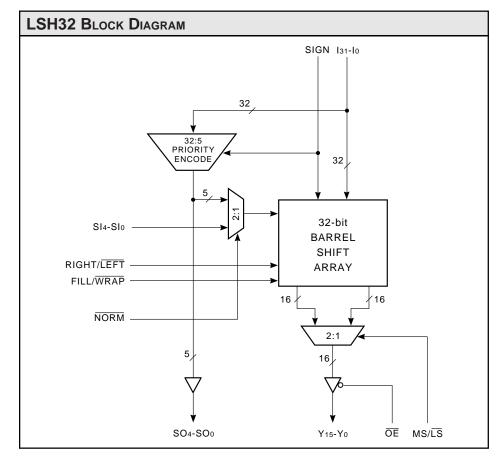

The LSH32 is a 32-bit high speed shifter designed for use in floating point normalization, word pack/unpack, field extraction, and similar applications. It has 32 data inputs, and 16 output lines. Any shift configuration of the 32 inputs, including circular (barrel) shifting, left shifts with zero fill, and right shift with sign extend are possible. In addition, a built-in priority encoder is provided to aid floating point normalization.

### **SHIFT ARRAY**

The 32 inputs to the LSH32 are applied to a 32-bit shift array. The 32 outputs of this array are multiplexed down to 16 lines for presentation at the device outputs. The array may be

1

configured such that any contiguous 16-bit field (including wraparound of the 32 inputs) may be presented to the output pins under control of the shift code field (wrap mode). Alternatively, the wrap feature may be disabled, resulting in zero or sign bit fill, as appropriate (fill mode). The shift code control assignments and the resulting input to output mapping for the wrap mode are shown in Table 1.

Essentially the LSH32 is configured as a left shift device. That is, a shift code of 000002 results in no shift of the input field. A code of 000012 provides an effective left shift of 1 position, etc. When viewed as a right shift, the shift code corresponds to the two's complement of the shift distance, i.e., a shift code of 111112 (-110) results in a right shift of one position, etc.

When not in the wrap mode, the LSH32 fills bit positions for which there is no corresponding input bit. The fill value and the positions filled depend on the RIGHT/ $\overline{LEFT}$  (R/ $\overline{L}$ ) direction pin. This pin is a don't care input when in wrap mode. For left shifts in fill mode, lower bits are filled with zero as shown in Table 2. For right shifts, however, the SIGN input is used as the fill value. Table 3 depicts the bits to be filled as a function of shift code for the right shift case. Note that the  $R/\overline{L}$  input changes only the fill convention, and does not affect the definition of the shift code.

In fill mode, as in wrap mode, the shift code input represents the number of shift positions directly for left shifts, but the two's complement of the shift code results in the equivalent right shift. However, for fill mode the  $R/\bar{L}$  input can be viewed as the most

## 32-bit Cascadable Barrel Shifter

| TABLE 1.   | <b>W</b> RAP   | Mode        | SHIFT           | Code | DEFI        | NITIONS         | 3   |              |              |              |

|------------|----------------|-------------|-----------------|------|-------------|-----------------|-----|--------------|--------------|--------------|

| Shift Code | Y 31           | <b>Y</b> 30 | Y 29            | •••  | Y16         | Y 15            | ••• | Y2           | <b>Y</b> 1   | Y0           |

| 00000      | <b>I</b> 31    | <b>I</b> 30 | <b>1</b> 29     | •••  | 116         | 115             | ••• | 12           | n            | ID           |

| 00001      | <b>I</b> 30    | <b>I</b> 29 | <b>1</b> 28     | •••  | 115         | 114             | ••• | n            | ID           | <b>I</b> 31  |

| 00010      | 129            | 128         | <b>1</b> 27     | •••  | 114         | 113             | ••• | ID           | <b>I</b> 31  | <b>I</b> 30  |

| 00011      | 128            | 127         | <b>I</b> 26     | •••  | 113         | 112             | ••• | <b>B</b> 1   | <b>I</b> 30  | <b>1</b> 29  |

|            | •              | •           | •               | •••  | •           | •               | ••• | •            | •            | •            |

|            | •              | •           | •               | •••  | •           | •               | ••• | •            | •            | •            |

|            | •              | •           | •               | •••  | •           | •               | ••• | •            | •            | •            |

| 01111      | 116            | 115         | 114             | •••  | 11          | ${\rm I\!\! D}$ | ••• | 119          | 118          | 117          |

| 10000      | 115            | 114         | 113             | •••  | ID          | <b>I</b> 31     | ••• | 118          | 117          | 116          |

| 10001      | 114            | 113         | 112             | •••  | <b>I</b> 31 | <b>I</b> 30     | ••• | 117          | 116          | 115          |

| 10010      | 113            | 112         | 111             | •••  | <b>I</b> 30 | <b>1</b> 29     | ••• | 116          | 115          | 114          |

| •          | •              | •           | •               | •••  | •           | •               | ••• | •            | •            | •            |

| •          | •              | •           | •               | •••  | •           | •               | ••• | •            | •            | •            |

| •          | •              | •           | •               | •••  | •           | •               | ••• | •            | •            | •            |

| 11100      | $\mathbb{I}_3$ | 12          | ı               | •••  | 120         | 119             | ••• | <b>I</b> 6   | 15           | 14           |

| 11101      | 12             | ı           | ${\rm I\!\! D}$ | •••  | 119         | 118             | ••• | <b>I</b> 5   | 14           | $\mathbb{B}$ |

| 11110      | 11             | ID          | <b>I</b> 31     | •••  | 118         | 117             | ••• | 14           | $\mathbb{B}$ | 12           |

| 11111      | 10             | <b>I</b> 31 | <b>I</b> 30     | •••  | 117         | 116             | ••• | $\mathbb{B}$ | 12           | ı            |

| TABLE 2.   | 2. FILL MODE SHIFT CODE DEFINITIONS — LEFT SHIFT |             |             |     |             |              |     |            |    |     |  |

|------------|--------------------------------------------------|-------------|-------------|-----|-------------|--------------|-----|------------|----|-----|--|

| Shift Code | Y 31                                             | Y30         | Y 29        | ••• | <b>Y</b> 16 | Y 15         | ••• | <b>Y</b> 2 | Y1 | Y0  |  |

| 00000      | <b>I</b> 31                                      | <b>I</b> 30 | <b>1</b> 29 | ••• | 116         | 115          | ••• | 12         | n  | IIO |  |

| 00001      | <b>I</b> 30                                      | <b>I</b> 29 | 128         | ••• | 115         | 114          | ••• | n          | ID | 0   |  |

| 00010      | <b>1</b> 29                                      | 128         | 127         | ••• | 114         | 113          | ••• | ID         | 0  | 0   |  |

| 00011      | 128                                              | <b>1</b> 27 | 126         | ••• | 113         | 112          | ••• | 0          | 0  | 0   |  |

|            | •                                                | •           | •           | ••• | •           | •            | ••• | •          | •  | •   |  |

|            | •                                                | •           | •           | ••• | •           | •            | ••• | •          | •  | •   |  |

| •          | •                                                | •           | •           | ••• | •           | •            | ••• | •          | •  | •   |  |

| 01111      | 116                                              | 115         | 114         | ••• | ı           | ${\rm I\!D}$ | ••• | 0          | 0  | 0   |  |

| 10000      | 115                                              | 114         | 113         | ••• | ID          | 0            | ••• | 0          | 0  | 0   |  |

| 10001      | 114                                              | 113         | 112         | ••• | 0           | 0            | ••• | 0          | 0  | 0   |  |

| 10010      | 113                                              | 112         | 111         | ••• | 0           | 0            | ••• | 0          | 0  | 0   |  |

| •          | •                                                | •           | •           | ••• | •           | •            | ••• | •          | •  | •   |  |

| •          | •                                                | •           | •           | ••• | •           | •            | ••• | •          | •  | •   |  |

|            | •                                                | •           | •           | ••• | •           | •            | ••• | •          | •  | •   |  |

| 11100      | $\mathbb{B}$                                     | 12          | l           | ••• | 0           | 0            | ••• | 0          | 0  | 0   |  |

| 11101      | 12                                               | ī           | ĪD          | ••• | 0           | 0            | ••• | 0          | 0  | 0   |  |

| 11110      | n                                                | ID          | 0           | ••• | 0           | 0            | ••• | 0          | 0  | 0   |  |

| 11111      | ID                                               | 0           | 0           | ••• | 0           | 0            | ••• | 0          | 0  | 0   |  |

significant bit of a 6-bit two's complement shift code, comprised of  $R/\bar{L}$  concatenated with the SI4–SI0 lines. Thus a positive shift code  $(R/\bar{L}=0)$  results in a left shift of 0–31 positions, and a negative code  $(R/\bar{L}=1)$  a right shift of up to 32 positions. The LSH32 can thus effectively select any contiguous 32-bit field out of a (sign extended and zero filled) 96-bit "input."

### **OUTPUT MULTIPLEXER**

The shift array outputs are applied to a 2:1 multiplexer controlled by the MS/ $\overline{LS}$  select line. This multiplexer makes available at the output pins either the most significant or least significant 16 outputs of the shift array.

### PRIORITY ENCODER

The 32-bit input bus drives a priority encoder which is used to determine the first significant position for purposes of normalization. The priority encoder produces a five-bit code representing the location of the first non-zero bit in the input word. Code assignment is such that the priority encoder output represents the number of shift positions required to left align the first non-zero bit of the input word. Prior to the priority encoder, the input bits are individually exclusive OR'ed with the SIGN input. This allows normalization in floating point systems using two's complement mantissa representation. A negative value in two's complement representation will cause the exclusive OR gates to invert the input data to the encoder. As a result the leading significant digit will always be "1." This affects only the encoder inputs; the shift array always operates on the raw input data. The priority encoder function table is shown in Table 4.

## 32-bit Cascadable Barrel Shifter

| TABLE 3. I | BLE 3. FILL MODE SHIFT CODE DEFINITIONS — RIGHT SHIFT |             |             |     |             |             |     |             |              |             |  |

|------------|-------------------------------------------------------|-------------|-------------|-----|-------------|-------------|-----|-------------|--------------|-------------|--|

| Shift Code | Y 31                                                  | <b>Y</b> 30 | Y 29        | ••• | <b>Y</b> 16 | Y 15        | ••• | Y2          | <b>Y</b> 1   | Y0          |  |

| 00000      | S                                                     | S           | S           | ••• | S           | S           | ••• | S           | S            | S           |  |

| 00001      | S                                                     | S           | S           | ••• | S           | S           | ••• | S           | S            | <b>B</b> 1  |  |

| 00010      | S                                                     | S           | S           | ••• | S           | S           | ••• | S           | <b>I</b> 31  | <b>I</b> 30 |  |

| 00011      | S                                                     | S           | S           | ••• | S           | S           | ••• | <b>I</b> 31 | <b>I</b> 30  | <b>1</b> 29 |  |

| •          | •                                                     | •           | •           | ••• | •           | •           | ••• | •           | •            | •           |  |

| •          | •                                                     | •           | •           | ••• | •           | •           | ••• | •           | •            | •           |  |

| •          | •                                                     | •           | •           | ••• | •           | •           | ••• | •           | •            | •           |  |

| 01111      | S                                                     | S           | S           | ••• | S           | S           | ••• | 119         | 118          | <b>1</b> 17 |  |

| 10000      | S                                                     | S           | S           | ••• | S           | <b>I</b> 31 | ••• | 118         | 117          | 116         |  |

| 10001      | S                                                     | S           | S           | ••• | <b>I</b> 31 | <b>I</b> 30 | ••• | 117         | 116          | 115         |  |

| 10010      | S                                                     | S           | S           | ••• | <b>I</b> 30 | 129         | ••• | 116         | 115          | 114         |  |

| •          | •                                                     | •           | •           | ••• | •           | •           | ••• | •           | •            | •           |  |

| •          | •                                                     | •           | •           | ••• | •           | •           | ••• | •           | •            | •           |  |

| •          | •                                                     | •           | •           | ••• | •           | •           | ••• | •           | •            | •           |  |

| 11100      | S                                                     | S           | S           | ••• | <b>I</b> 20 | 119         | ••• | <b>I</b> 6  | 15           | 14          |  |

| 11101      | S                                                     | S           | S           | ••• | 119         | 118         | ••• | 15          | 14           | B           |  |

| 11110      | S                                                     | S           | <b>I</b> 31 | ••• | 118         | 117         | ••• | <b>1</b> 4  | $\mathbb{B}$ | 12          |  |

| 11111      | S                                                     | <b>I</b> 31 | <b>I</b> 30 | ••• | 117         | 116         | ••• | B           | 12           | l           |  |

| TABLE      | TABLE 4. PRIORITY ENCODER FUNCTION TABLE |             |     |     |     |     |    |   |    |            |  |  |

|------------|------------------------------------------|-------------|-----|-----|-----|-----|----|---|----|------------|--|--|

| <b>B</b> 1 | <b>I</b> 30                              | <b>1</b> 29 | ••• | 116 | 115 | ••• | 12 | n | 10 | Shift Code |  |  |

| 1          | Х                                        | Х           | ••• | Х   | Х   | ••• | Х  | Х | Х  | 00000      |  |  |

| 0          | 1                                        | X           | ••• | Х   | X   | ••• | X  | X | Х  | 00001      |  |  |

| 0          | 0                                        | 1           | ••• | Х   | X   | ••• | X  | X | Х  | 00010      |  |  |

|            | •                                        | •           | ••• | •   | •   | ••• | •  | • | •  |            |  |  |

|            | •                                        | •           | ••• | •   | •   | ••• | •  | • | •  |            |  |  |

| 0          | 0                                        | 0           | ••• | 1   | X   | ••• | X  | X | Х  | 01111      |  |  |

| 0          | 0                                        | 0           | ••• | 0   | 1   | ••• | X  | X | X  | 10000      |  |  |

| 0          | 0                                        | 0           | ••• | 0   | 0   | ••• | X  | X | X  | 10001      |  |  |

|            | •                                        | •           | ••• | •   | •   | ••• | •  | • | •  |            |  |  |

|            | •                                        | •           | ••• | •   | •   | ••• | •  | • | •  |            |  |  |

| 0          | 0                                        | 0           | ••• | 0   | 0   | ••• | 0  | 1 | X  | 11110      |  |  |

| 0          | 0                                        | 0           | ••• | 0   | 0   | ••• | 0  | 0 | 1  | 11111      |  |  |

| 0          | 0                                        | 0           | ••• | 0   | 0   | ••• | 0  | 0 | 0  | 11111      |  |  |

### NORMALIZE MULTIPLXER

The  $\overline{NORM}$  input, when asserted results in the priority encoder output driving the internal shift code inputs directly. It is exactly equivalent to routing the SO4–SO0 outputs back to the SI4–SI0 inputs. The  $\overline{NORM}$  input provides faster normalization of 32-bit data by avoiding the delay associated with routing the shift code off chip. When using the  $\overline{NORM}$  function, the LSH32 should be placed in fill mode, with the  $R/\overline{L}$  input low.

#### APPLICATIONS EXAMPLES

Normalization of mantissas up to 32 bits can be accomplished directly by a single LSH32. The  $\overline{\text{NORM}}$  input is asserted, and fill mode and left shift are selected. The normalized mantissa is then available at the device output in two 16-bit segments, under the control of the output data multiplexer select, the MS/ $\overline{\text{LS}}$ .

If it is desirable to avoid the necessity of multiplexing output data in 16-bit segments, two LSH32 devices can be used in parallel. Both devices receive the same input word, with the MS/LS select line of one wired high, and the other low. Each device will then independently determine the shift distance required for normalization, and the full 32 bits of output data will be available simultaneously.

## 32-bit Cascadable Barrel Shifter

# LONG-WORD NORMALIZATION (MULTIPLE CYCLES)

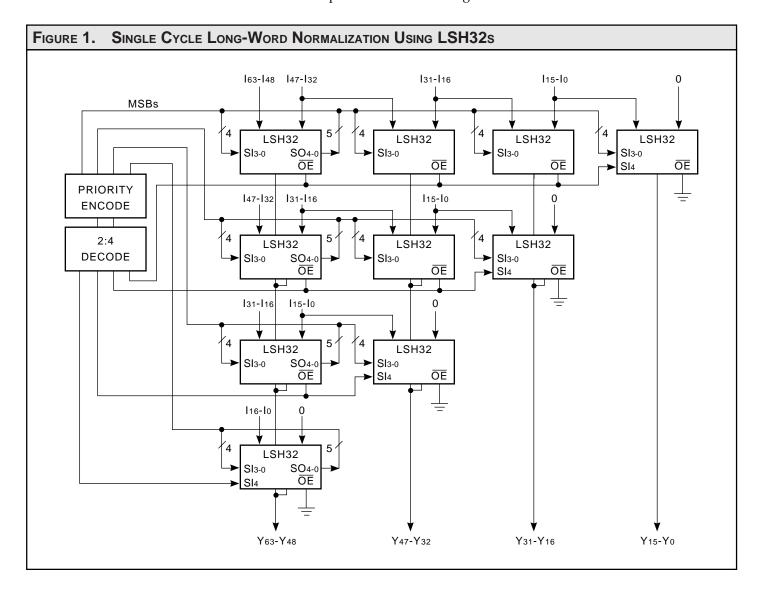

Normalization of floating point mantissas longer than 32 bits can be accomplished by cascading LSH32 units. When cascading for normalization, the device inputs are overlapped such that each device lower in priority than the first shares 16 inputs with its more significant neighbor. Fill mode and left shift are selected, however, internal normalization (NORM) is not used. The most significant result half of each device is enabled to the output. The shift out (SO4–SO0) lines of the most significant slice are connected to the shift in lines of all

slices, including the first. The exception is that all SI4 lines are grounded, limiting the shift distance to 16 positions. The shift distance required for normalization is produced by the priority encoder in the most significant slice. The priority encoder will produce the shift code necessary to normalize the input word if the leading non-zero digit is found in the upper 16 bits. If this is the case, the number of shift positions necessary to accomplish normalization is placed on the SO4-SO0 outputs for use by all slices, and the appropriate 0-15 bit shift is accomplished. If the upper 16 bits are all zero, then the maximum shift of 15 places is executed. Single

clock normalization requiring shifts longer than 16 bits can be accomplished by a bank-select technique described below.

# SINGLE CYCLE LONG-WORD NORMALIZATION

An extension of the above concept is a single clock normalization of long words (potentially requiring shifts of more than 15 places). The arrangement of LSH32s required is shown in Figure 1. Cascading of LSH32 units is accomplished by connecting the SI3–SI0 input lines of each unit to the SO3–SO0 outputs of the most significant device in the row as before. Essen-

## 32-bit Cascadable Barrel Shifter

tially the LSH32s are arranged in multiple rows or banks such that the inputs to successive rows are leftshifted by 16 positions. The outputs of each row are multiplexed onto a three-state bus. The normalization problem then reduces to selecting from among the several banks that one which has the first non-zero bit of the input value among its 16 most significant positions. If the most significant one in the input file was within the upper 16 locations of a given bank, the SO4 output of the most significant slice in that bank will be low. Single clock normalization can thus be accomplished simply by enabling onto the three-state output bus the highest priority bank in which this condition is met. In this way the input word will be normalized regardless of the number of shift positions required to accomplish this.

The number of shift positions can be determined simply by concatenation of the SO3-SO0 outputs of the most significant slice in the selected row with the encoded Output Enable-bits determining the row number. Note that lower rows need not be fully populated. This is because they represent left shifts in multiples of 16 positions, and the lower bits of the output word will be zero filled. In order to accomplish this zero fill, the least significant device in each row is always enabled, and the row select is instead connected to the SI4 input. This will force the shift length of the least significant device to a value greater than 15 whenever the row containing that device is not selected. This results in zero fill being accomplished by the equivalently positioned slice in a higher bank, as shown in the diagram.

#### **BLOCK FLOATING POINT**

With a small amount of external logic, block floating point operations are easily accomplished by the LSH32. Data resulting from a vector operation are applied to the LSH32 with the NORM-input deasserted. The SO4-SO<sub>0</sub> outputs fill then represent the normalization shift distance for each vector element in turn. By use of an external latch and comparator, the maximum shift distance encountered across all elements in the vector is saved for use in the next block operation (or block normalization). During this subsequent pass through the data, the shift code saved from the previous pass is applied uniformly across all elements of the vector. Since the LSH32 is not used in the internal normalize mode, this operation can be pipelined, thereby obtaining the desired shift distance for the next pass while simultaneously applying the normalization required from the previous pass.

## 32-bit Cascadable Barrel Shifter

| AXIMUM RATINGS Above which useful life may be impaired (Notes 1, 2, 3, 8) |                 |  |  |  |  |  |  |

|---------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

| Storage temperature                                                       | 65°C to +150°C  |  |  |  |  |  |  |

| Operating ambient temperature                                             | –55°C to +125°C |  |  |  |  |  |  |

| Vcc supply voltage with respect to ground                                 | 0.5 V to +7.0 V |  |  |  |  |  |  |

| Input signal with respect to ground                                       | 3.0 V to +7.0 V |  |  |  |  |  |  |

| Signal applied to high impedance output                                   | 3.0 V to +7.0 V |  |  |  |  |  |  |

| Output current into low outputs                                           | 25 mA           |  |  |  |  |  |  |

| Latchup current                                                           | > 400 mA        |  |  |  |  |  |  |

| OPERATING CONDITIONS To meet specified electrical and switching characteristics |                             |                               |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------|-----------------------------|-------------------------------|--|--|--|--|--|--|--|--|

| Mode                                                                            | Temperature Range (Ambient) | Supply Voltage                |  |  |  |  |  |  |  |  |

| Active Operation, Commercial                                                    | 0°C to +70°C                | 4.75 V ≤ <b>V</b> CC ≤ 5.25 V |  |  |  |  |  |  |  |  |

| Active Operation, Military                                                      | –55°C to +125°C             | 4.50 V ≤ <b>V</b> CC ≤ 5.50 V |  |  |  |  |  |  |  |  |

| ELECTRI     | ELECTRICAL CHARACTERISTICS Over Operating Conditions (Note 4) |                                                         |     |     |             |      |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------|---------------------------------------------------------|-----|-----|-------------|------|--|--|--|--|--|--|

| Symbol      | Parameter                                                     | ameter Test Condition                                   |     | Тур | Max         | Unit |  |  |  |  |  |  |

| <b>V</b> OH | Output High Voltage                                           | <b>V</b> CC = Min., <b>I</b> OH = -2.0 mA               | 2.4 |     |             | V    |  |  |  |  |  |  |

| <b>V</b> OL | Output Low Voltage                                            | <b>V</b> CC = Min., <b>I</b> OL = 8.0 mA                |     |     | 0.4         | V    |  |  |  |  |  |  |

| <b>V</b> IH | Input High Voltage                                            |                                                         | 2.0 |     | <b>V</b> CC | V    |  |  |  |  |  |  |

| <b>V</b> IL | Input Low Voltage                                             | (Note 3)                                                | 0.0 |     | 0.8         | V    |  |  |  |  |  |  |

| lix         | Input Current                                                 | Ground $\leq$ <b>V</b> IN $\leq$ <b>V</b> CC (Note 12)  |     |     | ±20         | μA   |  |  |  |  |  |  |

| loz         | Output Leakage Current                                        | Ground $\leq$ <b>V</b> OUT $\leq$ <b>V</b> CC (Note 12) |     |     | ±20         | μA   |  |  |  |  |  |  |

| ICC1        | Vcc Current, Dynamic                                          | (Notes 5, 6)                                            |     | 10  | 30          | mA   |  |  |  |  |  |  |

| ICC2        | Vcc Current, Quiescent                                        | (Note 7)                                                |     |     | 1.5         | mA   |  |  |  |  |  |  |

## 32-bit Cascadable Barrel Shifter

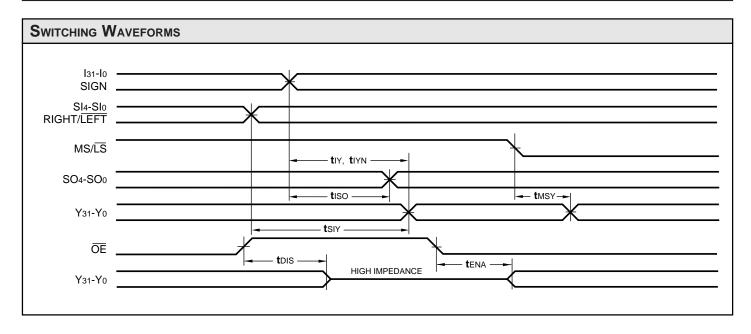

## **SWITCHING CHARACTERISTICS**

| Commercial Operating Range (0°C to +70°C) Notes 9, 10 (ns) |                                             |        |     |     |     |     |     |  |  |  |  |  |

|------------------------------------------------------------|---------------------------------------------|--------|-----|-----|-----|-----|-----|--|--|--|--|--|

|                                                            |                                             | LSH32- |     |     |     |     |     |  |  |  |  |  |

|                                                            |                                             | 4      | 2*  | 3   | 32  | 20  |     |  |  |  |  |  |

| Symbol                                                     | Parameter                                   | Min    | Max | Min | Max | Min | Max |  |  |  |  |  |

| tıY                                                        | I, SIGN Inputs to Y Outputs                 |        | 42  |     | 32  |     | 20  |  |  |  |  |  |

| tiyn                                                       | I, SIGN Inputs to Y Outputs, Normalize Mode |        | 75  |     | 60  |     | 20  |  |  |  |  |  |

| tiso                                                       | I, SIGN Inputs to SO Outputs                |        | 55  |     | 42  |     | 20  |  |  |  |  |  |

| tsiy                                                       | SI, RIGHT/LEFT to Y Outputs                 |        | 52  |     | 40  |     | 20  |  |  |  |  |  |

| tMSY                                                       | MS/LS Select to Y Outputs                   |        | 28  |     | 24  |     | 15  |  |  |  |  |  |

| tDIS                                                       | Three-State Output Disable Delay (Note 11)  |        | 20  |     | 20  |     | 15  |  |  |  |  |  |

| <b>t</b> ENA                                               | Three-State Output Enable Delay (Note 11)   |        | 20  |     | 20  |     | 15  |  |  |  |  |  |

| MILITAR      | MILITARY OPERATING RANGE (-55°C to +125°C) Notes 9, 10 (ns) |        |        |     |     |     |       |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------|--------|--------|-----|-----|-----|-------|--|--|--|--|--|--|

|              |                                                             | LSH32- |        |     |     |     |       |  |  |  |  |  |  |

|              |                                                             | 5      | 0*//// | 4   | 0*  | 3   | 0*/// |  |  |  |  |  |  |

| Symbol       | Parameter                                                   | Min    | Max    | Min | Max | Min | Max   |  |  |  |  |  |  |

| tiY          | I, SIGN Inputs to Y Outputs                                 |        | 50     |     | 40  |     | 30    |  |  |  |  |  |  |

| tiyn         | I, SIGN Inputs to Y Outputs, Normalize Mode                 |        | 85     |     | 75  |     | 58    |  |  |  |  |  |  |

| tiso         | I, SIGN Inputs to SO Outputs                                |        | 65     |     | 52  |     | 42    |  |  |  |  |  |  |

| tsiy         | SI, RIGHT/LEFT to Y Outputs                                 |        | 62     |     | 52  |     | 40    |  |  |  |  |  |  |

| tMSY         | MS/LS Select to Y Outputs                                   |        | 32     |     | 26  |     | 24    |  |  |  |  |  |  |

| <b>t</b> DIS | Three-State Output Disable Delay (Note 11)                  |        | 22     |     | 20  |     | 17    |  |  |  |  |  |  |

| <b>t</b> ENA | Three-State Output Enable Delay (Note 11)                   |        | 22     |     | 20  |     | 17    |  |  |  |  |  |  |

\*DISCONTINUED SPEED GRADE

## 32-bit Cascadable Barrel Shifter

### **NOTES**

- 1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.

- 2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

- 3. This device provides hard clamping of transient undershoot and overshoot. Input levels below ground or above VCC will be clamped beginning at -0.6 V and VCC + 0.6 V. The device can withstand indefinite operation with inputs in the range of -0.5 V to +7.0 V. Device operation will not be adversely affected, however, input current levels will be well in excess of 100 mA.

- 4. Actual test conditions may vary from those designated but operation is guaranteed as specified.

- 5. Supply current for a given application can be accurately approximated by:

$\frac{NCV^2F}{4}$

where

N = total number of device outputs

C = capacitive load per output

V = supply voltage

F = clock frequency

- 6. Tested with all outputs changing every cycle and no load, at a 5 MHz clock rate.

- 7. Tested with all inputs within 0.1 V of **V**CC or Ground, no load.

- 8. These parameters are guaranteed but not 100% tested.

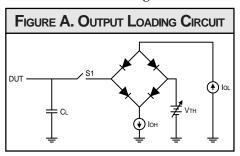

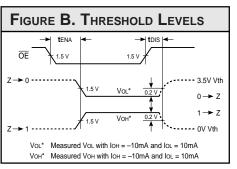

9. AC specifications are tested with input transition times less than 3 ns, output reference levels of 1.5 V (except tDIS test), and input levels of nominally 0 to 3.0 V. Output loading may be a resistive divider which provides for specified IOH and IOL at an output voltage of VOH min and VOL max respectively. Alternatively, a diode bridge with upper and lower current sources of IOH and IOL respectively, and a balancing voltage of 1.5 V may be used. Parasitic capacitance is 30 pF minimum, and may be distributed.

This device has high-speed outputs capable of large instantaneous current pulses and fast turn-on/turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

- a. A  $0.1~\mu F$  ceramic capacitor should be installed between VCC and Ground leads as close to the Device Under Test (DUT) as possible. Similar capacitors should be installed between device VCC and the tester common, and device ground and tester common.

- b. Ground and VCC supply planes must be brought directly to the DUT socket or contactor fingers.

- c. Input voltages should be adjusted to compensate for inductive ground and  $\mathbf{V}$ CC noise to maintain required DUT input levels relative to the DUT ground pin.

- 10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

- 11. For the tena test, the transition is measured to the 1.5 V crossing point with datasheet loads. For the tDIS test, the transition is measured to the  $\pm 200 \,\mathrm{mV}$  level from the measured steady-state output voltage with  $\pm 10 \,\mathrm{mA}$  loads. The balancing voltage, VTH, is set at 3.5 V for Z-to-0 and 0-to-Z tests, and set at 0 V for Z-to-1 and 1-to-Z tests.

- 12. These parameters are only tested at the high temperature extreme, which is the worst case for leakage current.

## 32-bit Cascadable Barrel Shifter