# LTC2970/LTC2970-1

# Dual I<sup>2</sup>C Power Supply Monitor and Margining Controller

### DESCRIPTION

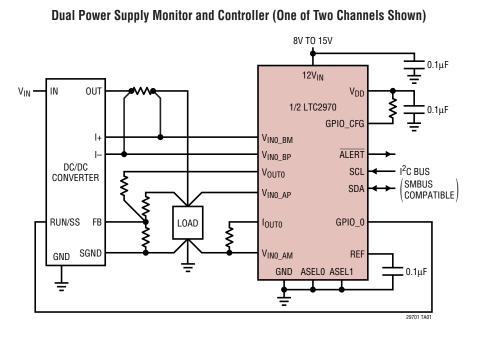

The LTC<sup>®</sup>2970 is a dual power supply monitor and margining controller with an SMBus compatible I<sup>2</sup>C bus interface. A low-drift, on-chip reference and 14-bit  $\Delta \Sigma$  A/D converter allow precise measurements of supply voltages, load currents or internal die temperature. Fault management allows ALERT to be asserted for configurable over and under voltage fault conditions. Two voltage buffered, 8-bit IDACs allow highly accurate programming of DC/DC converter output voltages. The IDACs can be configured to automatically servo the power supplies to the desired voltages using the ADC. The LTC2970-1 adds a tracking feature that can be used to turn multiple power supplies on or off in a controlled manner.

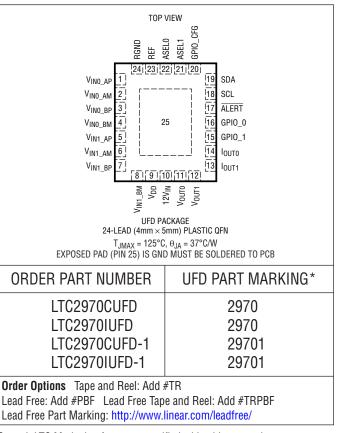

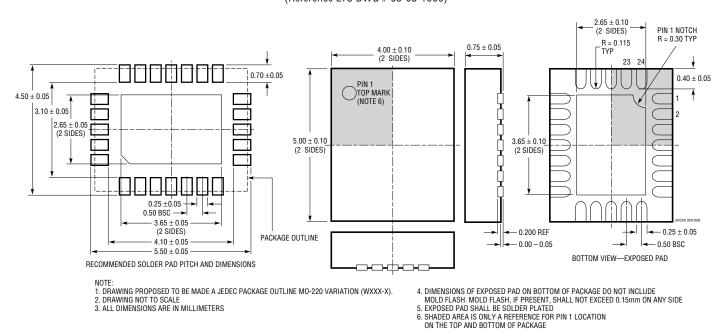

The bus address is set to 1 of 9 possible combinations by pin strapping the ASEL0 and ASEL1 pins. The LTC2970/ LTC2970-1 are packaged in the 24-lead,  $4mm \times 5mm$  QFN package.

T, LTC and LT are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## FEATURES

- Less Than ±0.5% Total Unadjusted Error 14-Bit  $\Delta \Sigma$ ADC with On-Chip Reference

- Dual, 8-Bit IDACs with 1x Voltage Buffers

- Linear, Voltage Servo Adjusts Supply Voltages by Ramping IDAC Outputs Up/Down

- I<sup>2</sup>C<sup>TM</sup> Bus Interface (SMBus Compatible)

- Extensive, User Configurable Fault Monitoring

- On-Chip Temperature Sensor

- Available in 24-Lead 4mm × 5mm QFN Package

### **APPLICATIONS**

- Dual Power Supply Voltage Servo

- Monitoring Supply Voltage and Current

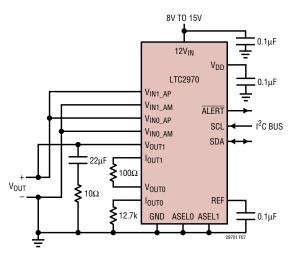

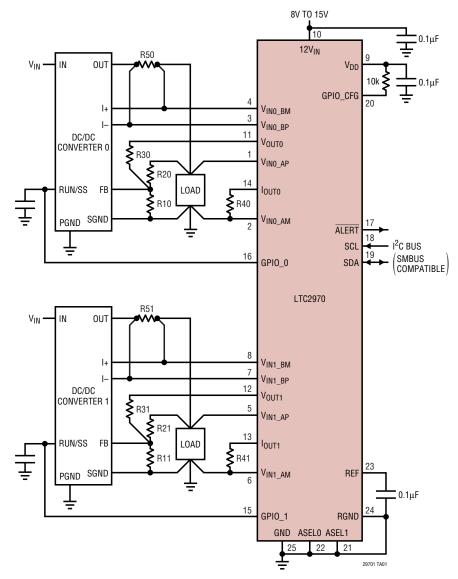

- Programmable Power Supplies

- Programmable Reference

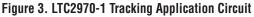

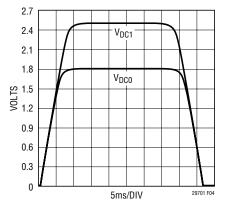

# TYPICAL APPLICATION

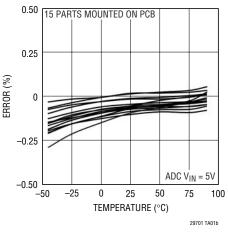

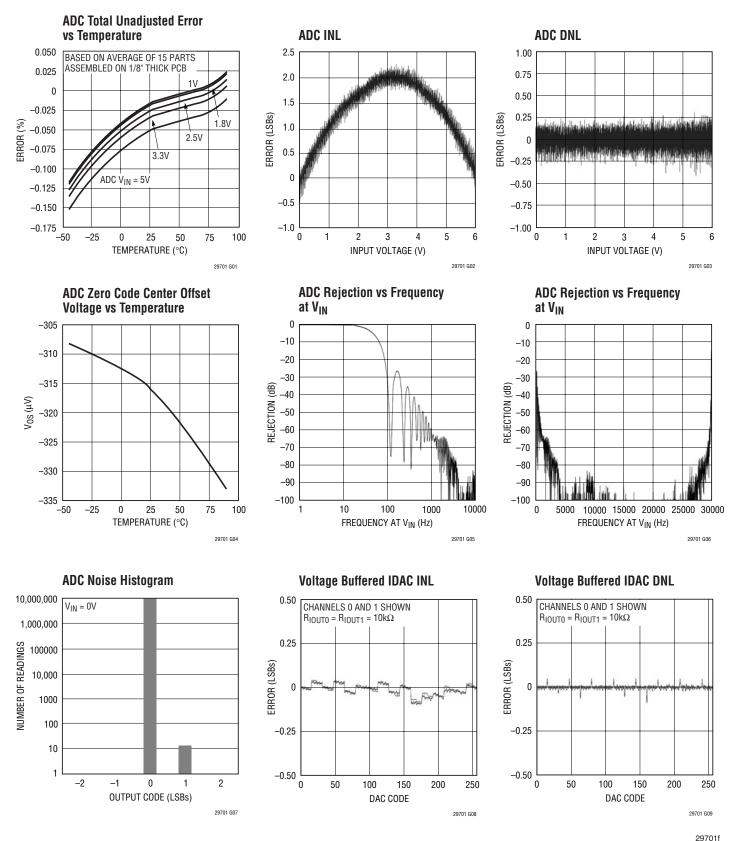

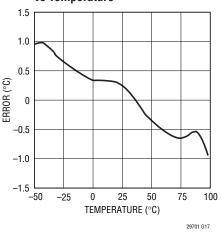

# ADC Total Unadjusted Error vs Temperature

# **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1 and 2)

| Supply Voltages:                                                                             |

|----------------------------------------------------------------------------------------------|

| V <sub>DD</sub> –0.3V to 6V                                                                  |

| 12V <sub>IN</sub> –0.3V to 15V                                                               |

| Digital Input/Output Voltages:                                                               |

| ASEL0, ASEL1 –0.3V to V <sub>DD</sub> + 0.3V                                                 |

| SDA, SCL, GPIO_CFG,                                                                          |

| ALERT, GPIO_0, GPIO_10.3V to 6V                                                              |

| Analog Voltages:                                                                             |

| V <sub>INO_AP</sub> , V <sub>INO_AM</sub> , V <sub>INO_BP</sub> ,                            |

| V <sub>INO BM</sub> , V <sub>IN1 AP</sub> , V <sub>IN1 AM</sub> ,                            |

| V <sub>IN1_BP</sub> , V <sub>IN1_BM</sub> , V <sub>OUT0</sub> , V <sub>OUT1</sub> 0.3V to 6V |

| $I_{OUTO}$ , $I_{OUT1}$ , REF –0.3V to $V_{DD}$ + 0.3V                                       |

| RGND–0.3V to 0.3V                                                                            |

| Operating Temperature Range:                                                                 |

| LTC2970C                                                                                     |

| LTC2970I40°C to 85°C                                                                         |

| Storage Temperature Range–65°C to 125°C                                                      |

| Lead Temperature (Soldering, 10 sec)                                                         |

|                                                                                              |

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>12VIN</sub> = 12V, V<sub>DD</sub> and REF pins floating unless otherwise indicated,

temperature range, otherwise specifications are at  $T_A = 25$  °C.  $V_{12VIN} = 12V$ ,  $V_{DD}$  and REF pins floating unless otherwise indicated,  $C_{VDD} = 100$ nF and  $C_{REF} = 100$ nF.

| SYMBOL             | PARAMETER                                           | CONDITIONS                                                         |   | MIN  | ТҮР  | MAX  | UNITS    |

|--------------------|-----------------------------------------------------|--------------------------------------------------------------------|---|------|------|------|----------|

| Power-Sup          | ply Characteristics                                 | 1                                                                  |   |      |      |      | <u> </u> |

| I <sub>V12</sub>   | 12V <sub>IN</sub> Supply Current                    | V <sub>12VIN</sub> = 12V, V <sub>DD</sub> Floating                 |   |      | 4.24 | 7.5  | mA       |

| I <sub>DD</sub>    | V <sub>DD</sub> Supply Current                      | $V_{DD} = 5V, V_{12VIN} = V_{DD}$                                  | • |      | 3.7  | 5    | mA       |

| V <sub>LKO</sub>   | V <sub>DD</sub> Undervoltage Lockout                | V <sub>DD</sub> Ramping-Down, V <sub>12VIN</sub> = V <sub>DD</sub> | • | 3.7  | 4.14 | 4.4  | V        |

|                    | V <sub>DD</sub> Undervoltage Lockout Hysteresis     |                                                                    |   |      | 118  |      | mV       |

| V <sub>DD</sub>    | Supply Input Operating Range                        |                                                                    | • | 4.5  |      | 5.75 | V        |

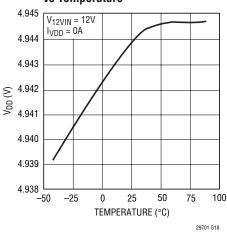

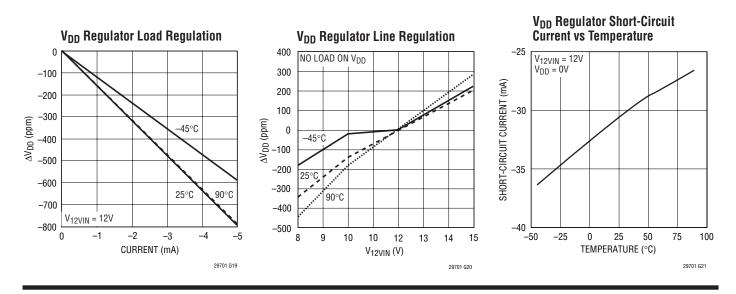

|                    | Regulator Output Voltage                            | $8V \le V_{12VIN} \le 15V$ , $-1mA \le I_{VDD} \le 0$              | • | 4.75 | 4.95 | 5.25 | V        |

|                    | Regulator Output Voltage<br>Temperature Coefficient |                                                                    |   |      | 10   |      | ppm/°C   |

|                    | Regulator Output Voltage Load<br>Regulation         | $-1mA \le I_{VDD} \le 0$                                           |   |      | 160  |      | ppm/mA   |

|                    | Regulator Line Regulation                           | $8V \le V_{12VIN} \le 15V$ , $I_{VDD} = 0mA$                       |   |      | 80   |      | ppm/V    |

|                    | Regulator Output Short-Circuit Current              | $V_{12VIN} = 12V, V_{DD} = 0V$                                     | • | -5   | -34  | -63  | mA       |

| V <sub>12VIN</sub> | 12V <sub>IN</sub> Supply Operating Range            |                                                                    | • | 8    |      | 15   | V        |

|                    | -                                                   | 1                                                                  |   |      |      |      | 29701f   |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C.  $V_{12VIN} = 12V$ ,  $V_{DD}$  and REF pins floating unless otherwise indicated,  $C_{VDD} = 100$ nF and  $C_{REF} = 100$ nF.

| SYMBOL                            | PARAMETER                                    | CONDITIONS                                                   |   | MIN   | ТҮР   | MAX  | UNITS  |

|-----------------------------------|----------------------------------------------|--------------------------------------------------------------|---|-------|-------|------|--------|

| Voltage Refe                      | erence Characteristics                       |                                                              |   |       |       |      |        |

| V <sub>REF</sub>                  | Reference Output Voltage                     |                                                              |   |       | 1.229 |      | V      |

|                                   | Reference Voltage Temperature<br>Coefficient |                                                              |   |       | 2     |      | ppm/°C |

|                                   | Reference Overdrive Voltage Input<br>Range   |                                                              | • | 1     |       | 1.5  | V      |

| ADC Charact                       | teristics                                    |                                                              |   |       |       |      |        |

| N_ADC                             | Resolution                                   | N_ADC = 8.192V/16384                                         |   |       | 500   |      | μV/LSB |

| TUE_ADC                           | Total Unadjusted Error                       | $V_{IN} = 3V, V_{IN} = V_{INn_XP} - V_{INn_XM}$ (Note 3)     | ٠ |       |       | ±0.5 | %      |

| INL_ADC                           | Integral Nonlinearity                        | (Note 4)                                                     | ٠ | -1    | 2     | 4.5  | LSB    |

| DNL_ADC                           | Differential Nonlinearity                    | (Note 7)                                                     | ٠ |       |       | ±0.5 | LSB    |

| V <sub>IN_ADC</sub>               | Input Voltage Range                          |                                                              | • | 0     |       | 6    | V      |

| V <sub>OS_ADC</sub>               | Offset Error                                 |                                                              | ٠ | -1000 | -316  | 1000 | μV     |

|                                   | Offset Error Drift                           |                                                              |   |       | 0.19  |      | μV/°C  |

| GAIN_ADC                          | Gain Error                                   | Full-Scale V <sub>IN</sub> = 6V                              | ٠ |       |       | ±0.4 | %      |

|                                   | Gain Error Drift                             |                                                              |   |       | 3     |      | ppm/°C |

| T <sub>CONV_ADC</sub>             | Conversion Time                              |                                                              |   |       | 33.3  |      | ms     |

| C <sub>IN_ADC</sub>               | Input Sampling Capacitance                   |                                                              |   |       | 3     |      | pF     |

| FIN_ADC                           | Input Sampling Frequency                     |                                                              |   |       | 61.4  |      | kHz    |

| I <sub>LEAK_ADC</sub>             | Input Leakage Current                        | $0V < V_{IN} < 6V$                                           | ٠ |       |       | ±0.1 | μA     |

| IDAC Output                       | Current Characteristics                      |                                                              |   |       |       |      |        |

| N_I <sub>OUT</sub>                | Resolution (Guaranteed Monotonic)            |                                                              |   | 8     |       |      | Bits   |

| INL_I <sub>OUT</sub>              | Integral Nonlinearity                        | V <sub>IOUT<i>n</i></sub> < V <sub>DD</sub> - 1.5V           | • |       |       | ±1   | LSB    |

| DNL_I <sub>OUT</sub>              | Differential Nonlinearity                    | $V_{\text{IOUT}n} < V_{\text{DD}} - 1.5V$                    | • |       |       | ±1   | LSB    |

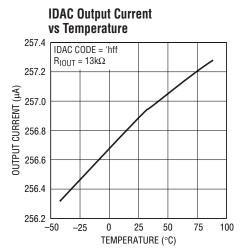

| I <sub>FS-</sub> I <sub>OUT</sub> | Full-Scale Output Current                    | V <sub>IOUTn</sub> < V <sub>DD</sub> – 1.5V, DAC Code = 'hff | ٠ | -236  | -255  | -276 | μA     |

| I <sub>DRIFT-</sub> IOUT          | Output Current Drift                         | DAC Code = 'hff                                              |   |       | 32    |      | ppm/°C |

| I <sub>OS-</sub> I <sub>OUT</sub> | Offset Current                               | DAC Code = 'h00                                              | ٠ |       |       | ±0.1 | μA     |

| Voltage Buff                      | ered IDAC Output Characteristics             |                                                              | 1 |       |       |      | 1      |

| INL_V <sub>OUT</sub>              | Integral Nonlinearity                        | $R_{IOUTn} = 10k\Omega$ , No Load on $V_{OUTn}$ (Note 5)     |   |       |       | ±0.5 | LSB    |

| DNL_V <sub>OUT</sub>              | Differential Nonlinearity                    | $R_{IOUTn} = 10k\Omega$ , No Load on $V_{OUTn}$ (Note 5)     | • |       |       | ±0.5 | LSB    |

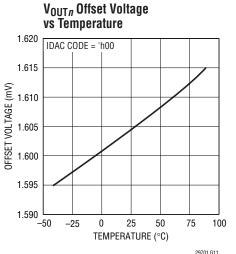

| V <sub>OS-</sub> V <sub>OUT</sub> | Offset Voltage                               | $V_{OS} = V_{OUTn} - V_{IOUTn}$ , No Load on $V_{OUTn}$      | • |       | 1.6   | ±10  | mV     |

|                                   | Output Voltage Drift                         | No Load on V <sub>OUT</sub>                                  |   |       | 0.17  |      | μV/°C  |

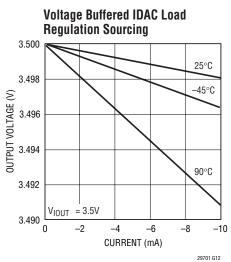

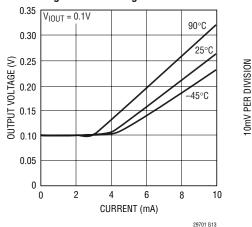

| V <sub>OUT</sub>                  | Load Regulation                              | $0.1V < V_{OUTn} < V_{DD} - 1.5V$ , $I_{VOUTn}$ Source = 1mA |   |       | -57   |      | ppm/mA |

|                                   |                                              | $0.1V < V_{OUTn} < V_{DD} - 1.5V$ , $I_{VOUTn}$ Sink = 1mA   |   |       | 100   |      | ppm/mA |

|                                   | Leakage Current                              | $V_{OUTn}$ High-Z, $0V \le V_{OUTn} \le V_{DD}$              | • |       | 1     | ±100 | nA     |

|                                   | Short-Circuit Current Low                    | V <sub>OUT<i>n</i></sub> Shorted to GND                      | ٠ |       |       | -50  | mA     |

|                                   | Short-Circuit Current High                   | V <sub>OUT</sub> Shorted to V <sub>DD</sub>                  | ٠ |       |       | 50   | mA     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{12VIN} = 12V$ ,  $V_{DD}$  and REF pins floating unless otherwise indicated,  $C_{VDD} = 100$ nF and  $C_{REF} = 100$ nF.

| SYMBOL                  | PARAMETER                           | CONDI               | TIONS                         |                | MIN        | ТҮР       | MAX                  | UNITS  |

|-------------------------|-------------------------------------|---------------------|-------------------------------|----------------|------------|-----------|----------------------|--------|

| Soft Conne              | ct Comparator Characteristics (CMPO | , CMP1)             |                               |                | I          |           |                      |        |

| V <sub>OS</sub>         | Offset Voltage                      |                     |                               |                |            | ±3        |                      | mV     |

| Temperatur              | re Sensor Characteristics           | I                   |                               |                |            |           |                      |        |

| TMP                     | Gain                                |                     |                               |                |            | 0.25      |                      | °C/LSB |

| 12V <sub>IN</sub> Volta | ge Divider Characteristics          | I                   |                               |                |            |           |                      |        |

| GAIN_12VII              | N Gain                              |                     |                               | •              | 0.329      | 0.333     | 0.335                | V/V    |

| Digital Inpu            | uts SCL, SDA, GPIO_CFG, GPIO_O, GF  | PIO_1               |                               |                |            |           |                      |        |

| V <sub>IH</sub>         | Input High Threshold Voltage        | SDA, S              | CL                            | •              |            |           | 2.1                  | V      |

|                         |                                     | GPIO_0              | CFG, GPIO_0, GIPO_1           | •              |            |           | 1.6                  | V      |

| V <sub>IL</sub>         | Input Low Threshold Voltage         | SDA, S              | CL                            | •              | 1.5        |           |                      | V      |

|                         |                                     | GPIO_0              | CFG, GPIO_0, GIPO_1           | •              | 1.0        |           |                      | V      |

| V <sub>HYST</sub>       | Input Hysteresis                    |                     |                               |                |            | 0.08      |                      | V      |

| I <sub>LEAK</sub>       | Input Leakage Current               | $0V \le V_{I}$      | $N \le 6V$                    | •              |            |           | ±1                   | μA     |

| C <sub>IN</sub>         | Input Capacitance                   |                     |                               |                |            | 10        |                      | pF     |

| Three State             | e Inputs ASEL[1:0]                  | I                   |                               | I              | I          |           |                      |        |

| V <sub>IH_ASEL</sub>    | Input High Threshold Voltage        |                     |                               | •              |            |           | V <sub>DD</sub> -0.5 | V      |

| V <sub>IL_ASEL</sub>    | Input Low Threshold Voltage         |                     |                               | •              | 0.5        |           |                      | V      |

| I <sub>IN,HL</sub>      | High, Low Input Current             | ASEL[1              | :0] = 0, V <sub>DD</sub>      | •              |            |           | ±20                  | μA     |

| I <sub>IN,Z</sub>       | High Z Input Current                |                     |                               | •              | ±2         |           |                      | μA     |

| Open Drain              | Outputs SDA, GPIO_CFG, GPIO_O, G    | PIO_1, ALER         | T                             |                |            |           |                      |        |

| V <sub>OL</sub>         | Output Low Voltage                  | I <sub>SINK</sub> = | 3mA                           | •              |            |           | 0.4                  | V      |

| I <sub>OH</sub>         | Input Leakage Current               | $0V \le V_{I}$      | $N \le 6V$                    | •              |            |           | ±1                   | μA     |

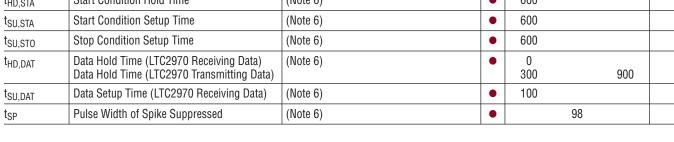

| The <b>e</b> den        | otes the specifications which app   | ly over the i       | full onerating temperature ra | nne otherwis   | e snecifir | ations ar | e at T₄ = 2          | 5°C    |

| SYMBOL                  | PARAMETER                           | -                   | CONDITIONS                    | inge, etternie | MIN        | ТҮР       |                      | UNITS  |

|                         | e Timing Characteristics            |                     |                               |                |            |           |                      |        |

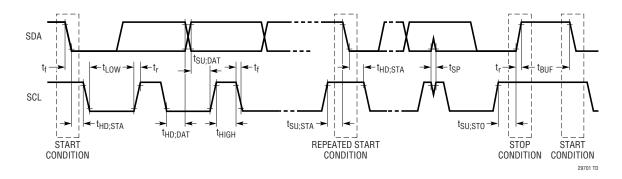

| f <sub>SCL</sub>        | Serial Clock Frequency              |                     | (Note 6)                      |                | 10         |           | 400                  | kHz    |

| tLOW                    | Serial Clock Low Period             |                     | (Note 6)                      | •              | 1.3        |           |                      | μs     |

| t <sub>HIGH</sub>       | Serial Clock High Period            |                     | (Note 6)                      |                | 0.6        |           |                      | μs     |

| t <sub>BUF</sub>        | Bus Free Time Between Stop and S    |                     | (Note 6)                      |                | 1.3        |           |                      | μs     |

| t <sub>HD,STA</sub>     | Start Condition Hold Time           |                     | (Note 6)                      | •              | 600        |           |                      | ns     |

| t <sub>SU,STA</sub>     | Start Condition Setup Time          |                     | (Note 6)                      | •              | 600        |           |                      | ns     |

| t <sub>SU,STA</sub>     | Stop Condition Setup Time           |                     | (Note 6)                      | •              | 600        |           |                      | ns     |

ns

ns

ns

ns

### ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25$ °C.

| SYMBOL                        | PARAMETER                      | CONDITIONS                                                                                                                                                                                                                             |   | MIN | ТҮР | MAX | UNITS  |

|-------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|--------|

| t <sub>SETUP_GPIO</sub>       | GPIO_0 and GPIO_1 Setup Time   | GPIO_0 and GPIO_1 input setup time<br>prior to the 26th rising SCL of an IO()<br>I <sup>2</sup> C read. These inputs must be valid and<br>stable by this time to be returned in the<br>IO() read result. (Note 6)                      | • | 2.5 |     |     | μs     |

| t <sub>HOLD_GPIO</sub>        | GPIO_0 and GPIO_1 Hold Time    | GPIO_0 and GPIO_1 input hold time<br>after the 26th rising SCL of an IO() I <sup>2</sup> C<br>read. These inputs must be held until<br>this amount of time has elapsed to be<br>returned in the IO() read result. (Note 6)             | • | 2.5 |     |     | μs     |

| tout_gpio                     | GPIO_0 and GPIO_1 Output Time  | GPIO_0 and GPIO_1 output delay after<br>the 35th rising SCL of an I <sup>2</sup> C write. These<br>outputs will become high impedance or<br>begin driving low by this time. (Note 6)                                                   | • |     |     | 2.5 | μs     |

| Internal Time                 | rs                             |                                                                                                                                                                                                                                        |   |     |     |     |        |

| t <sub>timeout_smb</sub>      | Stuck BUS Timer                | The LTC2970 will release the I <sup>2</sup> C bus and terminate the current command if the command is not completed before this amount of time has elapsed.                                                                            |   | 24  | 32  | 39  | ms     |

| tsetup_adc                    | ADC Channel Setup Time         | After selecting a new ADC channel, the LTC2970 will wait this amount of time to allow the analog input to settle before beginning an ADC conversion.                                                                                   |   |     | 304 |     | μs     |

| t <sub>timeout_</sub><br>sync | Tracking SYNC Failure Timer    | LTC2970-1 Only: The LTC2970-1 will<br>abort a pending SYNC() command if a<br>tracking command is not received before<br>this amount of time has elapsed.                                                                               |   | 255 |     | ms  |        |

| thold_track                   | Tracking IDAC Disconnect Delay | LTC2970-1 Only: After the tracking<br>algorithm asserts CPIO_CFG low, the<br>LTC2970-1 will delay disconnecting the<br>IDACs from the power supply feedback<br>nodes by this amount of time. Used while<br>tracking power supplies on. |   | 32  |     | ms  |        |

| tsetup_track                  | Tracking IDAC Disconnect Delay | LTC2970-1 Only: After the tracking<br>algorithm asserts CPIO_CFG high, the<br>LTC2970-1 will wait this amount of time<br>before starting to decrement Ch <i>n</i> _a_<br>delay_track[9:0]. Used while tracking<br>power supplies off.  |   |     | 32  |     | ms     |

| t <sub>dec_track</sub>        | Tracking IDAC Decrement Rate   | LTC2970-1 Only: The LTC2970-1 changes Ch <i>n</i> _a_delay_track[9:0] at this rate.                                                                                                                                                    |   |     | 88  |     | µs/LSB |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.  $V_{IN}$

**Note 3:** TUE (%) is defined as % Gain Error +  $\frac{v_{IN}}{(INL \bullet 500 \mu V/LSB + V_{OS})} \bullet 100$ **Note 4:** Integral nonlinearity (INL) is defined as the deviation of a code from a straight line passing through the actual endpoints (0V and 6V) of the transfer curve. The deviation is measured from the center of the quantization band.

**Note 5:** Nonlinearity is defined from the first code that is greater than or equal to the maximum offset specification to code 255 (full-scale).

**Note 6:** Maximum capacitive load,  $C_B$ , for SCL and SDA is 400pF. Data and clock risetime  $(t_r)$  and falltime  $(t_f)$  are:  $(20 + 0.1 \bullet C_B)(ns) < t_r < 300ns$  and  $(20 + 0.1 \bullet C_B)(ns) < t_f < 300ns$ .  $C_B =$  capacitance of one bus line in pF. SCL and SDA external pull-up voltage,  $V_{IO}$ , is  $3V < V_{IO} < 5.5V$ .

Note 7: This specification is guaranteed by design.

# TIMING DIAGRAM

The I<sup>2</sup>C Bus Specification

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

#### Voltage Buffered IDAC Load Regulation Sinking

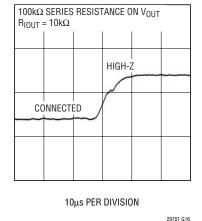

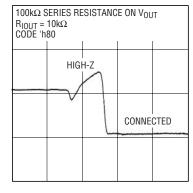

#### Voltage Buffered IDAC Transient Response During Transition from On State to High-Z State

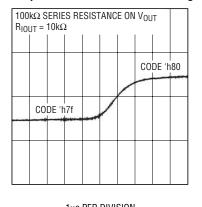

Voltage Buffered IDAC Transient Response to 1LSB DAC Code Change

$1\mu s$  PER DIVISION

# Temperature Sensor Error vs Temperature

#### Voltage Buffered IDAC Soft-Connect Transient Response

**0mV PER DIVISION**

29701 G14

5µs PER DIVISION

29701 G15

#### V<sub>DD</sub> Regulator Output Voltage vs Temperature

29701f

**10mV PER DIVISION**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# PIN FUNCTIONS

$V_{IN0\_AP}$  (Pin 1): Positive CH0\_A ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CH0\_A can be configured to servo IDAC0.

$V_{IN0\_AM}$  (Pin 2): Negative CH0\_A ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CH0\_A can be configured to servo IDAC0.

**V**<sub>INO\_BP</sub> (**Pin 3**): Positive CHO\_B ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CHO\_B is a voltage monitor input only.

$V_{IN0\_BM}$  (Pin 4): Negative CH0\_B ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CH0\_B is a voltage monitor input only.

$V_{IN1\_AP}$  (Pin 5): Positive CH1\_A ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CH1\_A can be configured to servo IDAC1.

$V_{IN1\_AM}$  (Pin 6): Negative CH1\_A ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CH1\_A can be configured to servo IDAC1. **V**<sub>IN1\_BP</sub>(**Pin 7**): Positive CH1\_B ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CH1\_B is a voltage monitor input only.

**V**<sub>IN1\_BM</sub> (**Pin 8**): Negative CH1\_B ADC Multiplexer Input. The output of the differential, 7:1 multiplexer connects to the input of the ADC. CH1\_B is a voltage monitor input only.

$V_{DD}$  (Pin 9):  $V_{DD}$  Power Supply, Voltage Monitor Input, and Internal 5V Regulator Output. The supply input range is 4.5V to 5.75V. The  $V_{DD}$  pin voltage can be connected to the ADC through an internal mux. Bypass the  $V_{DD}$  pin to device ground with a 100nF capacitor ( $C_{VDD}$ ). If no 5V input voltage supply is available, float the  $V_{DD}$  pin and power the LTC2970 from the  $12V_{\rm IN}$  pin.

**12V**<sub>IN</sub> (Pin 10): 12V Power Supply and Voltage Monitor Input. An internal regulator generates 5V from  $12V_{IN}$ . The input range for  $12V_{IN}$  is 8V to 15V. Bypass this pin with a 100nF capacitor. The regulator's output is connected to the V<sub>DD</sub> pin. The  $12V_{IN}$  pin voltage can also be monitored by the ADC through a 3:1 attenuator and the internal mux. If no 12V supply input is available, tie the  $12V_{IN}$  to the V<sub>DD</sub> pin and operate from 4.5V to 5.75V.

**V<sub>OUT0</sub> (Pin 11):** CH0 Voltage Output. Buffered version of IDAC0 output voltage.

# PIN FUNCTIONS

**V<sub>OUT1</sub> (Pin 12):** CH1 Voltage Output. Buffered version of IDAC1 output voltage.

**I**<sub>OUT1</sub> (**Pin 13**): IDAC1 Current Output. Connect a resistor between this pin and the point-of-load ground for channel 1. The IDAC sources between 0 and 255µA.

**I**<sub>OUTO</sub> (**Pin 14**): IDACO Current Output. Connect a resistor between this pin and the point-of-load ground for channel 0. The IDAC sources between 0 and 255µA.

**GPIO\_1 (Pin 15):** General Purpose Input or Open Drain Digital Output. GPIO\_1 can be configured as the IDAC Fault or Faults output, a digital input, or an open-drain digital output.

**GPIO\_0 (Pin 16):** General Purpose Input or Open Drain Digital Output. GPIO\_0 can be configured as the voltage monitor power-good or power-good bar output, a digital input, or a programmable open-drain output. Power good is the NOR of all instantaneous OV and UV faults; it does not include IDAC faults.

**ALERT** (Pin 17): Open Drain Digital Output. Connect the SMBALERT signal to this pin. ALERT is asserted low when either IDAC0 or IDAC1 rails out (optional), or when one of the monitored voltages ventures outside its UV and OV thresholds (also optional).

SCL (Pin 18): Serial Bus Clock Input.

SDA (Pin 19): Serial Bus Data Input and Output.

**GPIO\_CFG (Pin 20):** GPIO Configuration Digital Input and Open Drain Output. Pulling GPIO\_CFG high will cause the GPIO\_0 and GPIO\_1 open-drain outputs to automatically assert low after a power-on reset. If GPIO\_CFG is pulled low, then GPIO\_0 and GPIO\_1 do not assert low after power-up.

**ASEL1 (Pin 21):** Slave Address Select Bit 1. Tie this pin to the  $V_{DD}$  pin, ground, or float in order to select the address location (see Table 2).

**ASELO (Pin 22):** Slave Address Select Bit 0. Tie this pin to the  $V_{DD}$  pin, ground, or float in order to select the address location (see Table 2).

**REF (Pin 23):** Internal Reference Output or ADC Reference Overdrive Input. The voltage at this pin determines the full-scale input voltage of the delta-sigma ADC (V<sub>FULL-SCALE</sub> =  $6.65 \cdot V_{REF}$ , typically). An internal 3.5k resistor decouples the reference output from this pin. Bypass this pin to RGND with a 100nF capacitor (C<sub>REF</sub>).

**RGND (Pin 24):** Reference Ground. Connect to device ground.

**GND (Pin 25):** Device Ground. Must be soldered to ground.

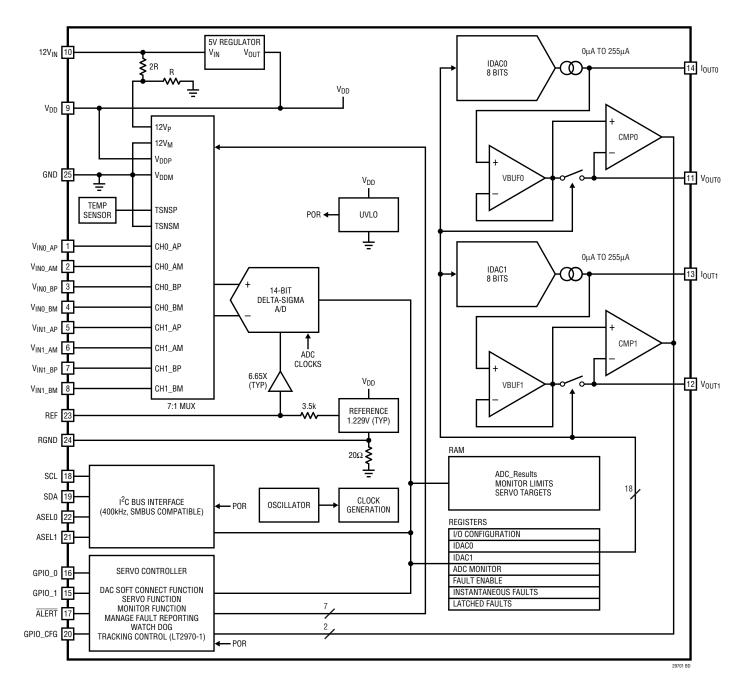

# **BLOCK DIAGRAM**

# LTC2970/LTC2970-1

# TABLE OF CONTENTS (For Operations Sections)

| 1.  | LTC2970 Operation Overview                                                  | 14 |

|-----|-----------------------------------------------------------------------------|----|

| 2.  | I <sup>2</sup> C Serial Digital Interface                                   | 15 |

| 3.  | Register Command Set                                                        | 16 |

| 4.  | Detailed I <sup>2</sup> C Command Register Descriptions                     | 17 |

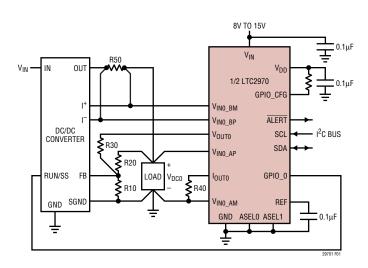

| 5.  | Soft Connecting the LTC2970 to the Power Supply Feedback Node               | 21 |

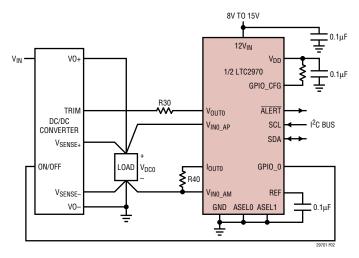

| 6.  | Hard Connecting the LTC2970 to the Power Supply Trim Pin                    | 21 |

| 7.  | Programming a Previously Connected IDAC                                     | 22 |

| 8.  | Disconnecting the LTC2970 from the Power Supply Trim Pin                    | 22 |

| 9.  | Tracking Power Supplies Overview (LTC2970-1 Only)                           | 22 |

| 10. | . Tracking Power Supplies On (LTC2970-1 Only)                               | 22 |

| 11. | . Tracking Power Supplies Off (LTC2970-1 Only)                              | 23 |

| 12. | . Continuous Power Supply Voltage Servo                                     | 24 |

| 13. | . One Time Power Supply Voltage Servo                                       | 25 |

| 14. | . One Time Power Supply Voltage Servo with Repeat On Fault                  | 25 |

| 15. | . Configuring ADC to Monitor Input Channels and Internal Temperature Sensor | 25 |

| 16. | . Generating and Monitoring Instantaneous Faults                            | 26 |

| 17. | . Generating and Monitoring Latched Faults                                  | 27 |

| 18. | . General Purpose Input/Output Pins                                         | 28 |

| 19. | . Advanced Development Features                                             | 28 |

|     |                                                                             |    |

#### 1. LTC2970 Operation Overview

The LTC2970 is designed to control and monitor two power supplies. The LTC2970's superior accuracy allows it to precisely servo each supply's output voltage over a wide range of operating conditions; increasing accuracy, reducing power requirements and component costs. Margining may be performed with equal ease and precision. The monitoring functions allow for increased reliability by alerting a system host about incipient failures before they occur. The seven channel ADC may also be used to monitor current, temperature, and the 5V or optional 12V supply.

The LTC2970's unique architecture and control algorithm have been especially tailored for power supply management. The soft connect feature allows the LTC2970 to begin controlling a power supply without perturbing its initial value. The delta-sigma ADC architecture was specifically chosen to average out power-supply noise and allow the LTC2970 to ignore fast transients. Unlike discrete time DACs, the LTC2970's continuous time, voltage buffered IDAC is ideal for noise sensitive applications. The servo algorithm limits the IDAC step size to one LSB per iteration in order to minimize power supply transients. The point of load ground reference for the IDAC outputs minimize errors that would otherwise occur in a power system that experiences ground bounce. By selecting two resistor values, the user can choose the appropriate resolution while providing an important hardware range limit beyond which the supply may not be driven. The servo on fault option allows the LTC2970 to further reduce output voltage disturbances by only stepping the IDAC when the output voltage drifts outside of a user programmable window. The LTC2970 powers up in a high impedance state and will not interfere with default power supply operation. Similarly, powering down the LTC2970 will restore its high impedance state.

All communication with the LTC2970 is performed over an industry standard I<sup>2</sup>C bus. The LTC2970 I<sup>2</sup>C interface also meets all SMB<u>us setup</u> times, hold times, and timeout requirements. The ALERT pin may be used to signal that one or more of the fourteen configurable fault limits have been reached. Each fault may be individually masked. The I<sup>2</sup>C interface supports word reads, word writes and the SMBus Alert Response Address protocol. Two general purpose IO pins may be used to provide additional fault information or user defined system control. Powering down the LTC2970 will not interfere with I<sup>2</sup>C operation.

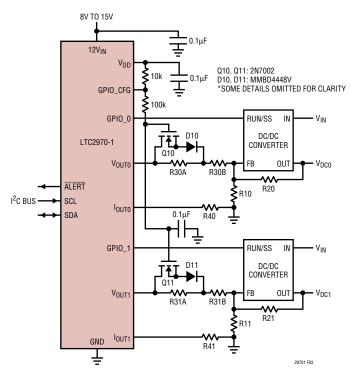

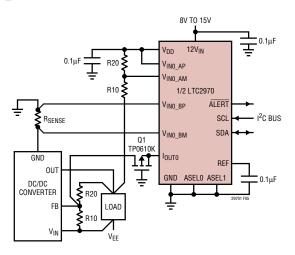

The LTC2970-1 enables power supply tracking and sequencing with the addition of a few external components. A special global address and synchronization command allow multiple LTC2970-1's to track and sequence multiple pairs of power supplies.

The LTC2970 can perform the following operations:

- Accept all programming commands and report status over the I<sup>2</sup>C or SMBus bus.

- Command each voltage buffered IDAC to connect to the corresponding power supply's feedback node through an external resistor using the IDAC code that most closely approximates the feedback node's regulation voltage (Soft Connect).

- Command each voltage buffered IDAC output to connect to the corresponding power supply's feedback node through an external resistor with a user-selected IDAC code (Hard Connect).

- Change the code of a previously connected IDAC.

- Disconnect each voltage buffered IDAC output from the power supply's feedback node.

- *LTC2970-1 Only:* Track two power supplies up or down. Multiple LTC2970-1's can be configured to track simultaneously or in a sequence.

- Continuously servo one or both supplies to a programmed voltage.

- Perform a one-time servo of one or both supplies to a programmed voltage and hold the servo codes in the controlling IDAC.

- Perform a one time servo of one or both supplies to a programmed voltage and hold the code(s) in the controlling IDAC(s) until over/under voltage monitoring detects a fault, at which point a control bit may be used to allow the LTC2970 to servo back to the initial voltage target.

- Select any combination of seven possible ADC channels to be monitored by the ADC.

- Generate instantaneous faults based on user programmable over-voltage and under-voltage limits and fixed IDAC limits. The status of OR'd voltage limit faults and IDAC faults may be output over GPIO\_0 and GPIO\_1, respectively.

- Enable instantaneous faults to set associated latched faults using the FAULT\_EN register. The status of OR'd latched faults may be signalled using ALERT.

- Configure the GPIO\_0 and GPIO\_1 pins to act as inputs or outputs.

#### 2. I<sup>2</sup>C Serial Digital Interface

The LTC2970 communicates with a host (master) using the 2-wire,  $I^2C$  serial bus interface. The Timing Diagram shows the timing relationship of the signals on the bus.

The two bus lines, SDA and SCL, must be high when the bus is not in use. External pull-up resistors or current sources are required on these lines.

The LTC2970 I<sup>2</sup>C interface is SMBus compatible; it meets all SMBus setup times, hold times and timeout requirements.

The LTC2970 is a receive-only (slave) device. The LTC2970 can signal the host through the SMBALERT protocol that it wants to talk by asserting  $\overline{\text{ALERT}}$  low. The LTC2970 supports the three I<sup>2</sup>C protocols summarized in Table 1.

#### **Slave Address**

The LTC2970 can respond to one of nine 7-bit addresses. The two slave address select pins (ASEL1 and ASEL0) are programmed by the user and determine the slave address, as shown in Table 2.

The LTC2970 also supports the ARA address and a global address that allows multiple LTC2970s to be programmed with the same data simultaneously, as shown in Table 3.

#### Table 1. Supported I<sup>2</sup>C Command Types

READ DATA WORD: S:ADR:W:A:CMD:A:Sr:ADR:R:A:DATA:A:DATA:NACK:P WRITE DATA WORD:

S:ADR:W:A:CMD:A:W:A:DATA:A:DATA:A:P

#### ALERT RESPONSE

S:ARA:R:A:ADR:NACK:P:

#### Table 2. LTC2970 Address Table

| ADDRESS[7:0]<br>(R/W = 0) | ADDRESS[7:1] | ASEL1 | ASELO |

|---------------------------|--------------|-------|-------|

| 8'hB8                     | 7'h5C        | L     | L     |

| 8'hBA                     | 7'h5D        | L     | F     |

| 8'hBC                     | 7'h5E        | L     | Н     |

| 8'hBE                     | 7'h5F        | F     | L     |

| 8'hD6                     | 7'h6B        | F     | F     |

| 8'hD8                     | 7'h6C        | F     | Н     |

| 8'hDA                     | 7'h6D        | Н     | L     |

| 8'hDC                     | 7'h6E        | Н     | F     |

| 8'hDE                     | 7'h6F        | Н     | Н     |

#### Table 3. Special LTC2970 Addresses

|        | ADDRESS[7:0]<br>(R/W = 0) | ADDRESS[7:1] | FUNCTION                                                                                                                                             |

|--------|---------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARA    | 8'h18                     | 7'hOC        | This is the standard Alert<br>Response Address for all<br>SMBus devices. This address is<br>independent of the value of the<br>ASEL1 and ASEL0 pins. |

| Global | 8'hB6                     | 7'h5B        | This a global address to which<br>all LTC2970s will respond. This<br>address is independent of the<br>value of the ASEL1 and ASEL0<br>pins.          |

L:  $V_{ASELn} < V_{IL}_{ASEL}$  F: ASEL*n* Floating H:  $V_{ASELn} > V_{IH}_{ASEL}$

#### 3. Registered Command Set

| COMMAND FUNCTION     | DESCRIPTION                                                         | R/W        | DATA<br>Length | COMMAND<br>Byte value |

|----------------------|---------------------------------------------------------------------|------------|----------------|-----------------------|

| FAULT()              | Instantaneous Fault Status For All Channels                         | Read Only  | 16 Bits        | 'h00                  |

| FAULT_EN()           | Enable For All Latched Faults and Servo On Fault                    | Read/Write | 16 Bits        | 'h08                  |

| FAULT_LA_INDEX()     | Index to All Latched Faults                                         | Read Only  | 16 Bits        | ʻh10                  |

| FAULT_LA()           | Latched Fault Status For All Channels                               | Read Only  | 16 Bits        | ʻh11                  |

| 10()                 | IO Control and Status Register                                      | Read/Write | 16 Bits        | ʻh17                  |

| ADC_MON()            | Control Register For Selecting ADC Channels to Monitor              | Read/Write | 16 Bits        | ʻh18                  |

| *SYNC()              | Control Register For Synchronizing Tracking Across Multiple Devices | Read/Write | 16 Bits        | ʻh1F                  |

| VDD_ADC()            | V <sub>DDIN</sub> ADC Conversion Result Register                    | Read Only  | 16 Bits        | ʻh28                  |

| VDD_OV()             | V <sub>DDIN</sub> Over-Voltage Monitor Control Register             | Read/Write | 16 Bits        | ʻh29                  |

| VDD_UV()             | V <sub>DDIN</sub> Under-Voltage Monitor Control Register            | Read/Write | 16 Bits        | ʻh2A                  |

| V12_ADC()            | 12V <sub>IN</sub> ADC Conversion Result Register                    | Read Only  | 16 Bits        | ʻh38                  |

| V12_0V()             | 12V <sub>IN</sub> Over-Voltage Monitor Control Register             | Read/Write | 16 Bits        | ʻh39                  |

| V12_UV()             | 12V <sub>IN</sub> Under-Voltage Monitor Control Register            | Read/Write | 16 Bits        | ʻh3A                  |

| CH0_A_ADC()          | CH0_A ADC Conversion Result Register                                | Read Only  | 16 Bits        | 'h40                  |

| CH0_A_OV()           | CH0_A Over-Voltage Monitor Control Register                         | Read/Write | 16 Bits        | ʻh41                  |

| CH0_A_UV()           | CH0_A Under-Voltage Monitor Control Register                        | Read/Write | 16 Bits        | ʻh42                  |

| CH0_A_SERVO()        | CH0_A Voltage Servo Control Register                                | Read/Write | 16 Bits        | ʻh43                  |

| CH0_A_IDAC()         | CH0_A IDAC Control Register                                         | Read/Write | 16 Bits        | ʻh44                  |

| *CH0_A_IDAC_TRACK()  | CH0_A IDAC Track Final Value Register                               | Read/Write | 16 Bits        | ʻh45                  |

| *CH0_A_DELAY_TRACK() | CH0_A IDAC Track Delay Register                                     | Read/Write | 16 Bits        | ʻh46                  |

| CH0_B_ADC()          | CH0_B ADC Conversion Result Register                                | Read Only  | 16 Bits        | ʻh48                  |

| CH0_B_OV()           | CH0_B Over-Voltage Monitor Control Register                         | Read/Write | 16 Bits        | ʻh49                  |

| CH0_B_UV()           | CH0_B Under-Voltage Monitor Control Register                        | Read/Write | 16 Bits        | ʻh4A                  |

| CH1_A_ADC()          | CH1_A ADC Conversion Result Register                                | Read Only  | 16 Bits        | ʻh50                  |

| CH1_A_OV()           | CH1_A Over-Voltage Monitor Control Register                         | Read/Write | 16 Bits        | ʻh51                  |

| CH1_A_UV()           | CH1_A Under-Voltage Monitor Control Register                        | Read/Write | 16 Bits        | 'h52                  |

#### 3. Registered Command Set (Cont.)

| COMMAND FUNCTION     | DESCRIPTION                                                                             | R/W        | DATA<br>Length | COMMAND<br>Byte value |

|----------------------|-----------------------------------------------------------------------------------------|------------|----------------|-----------------------|

| CH1_A_SERVO()        | CH1_A Voltage Servo Control Register                                                    | Read/Write | 16 Bits        | ʻh53                  |

| CH1_A_IDAC()         | CH1_A IDAC Control Register                                                             | Read/Write | 16 Bits        | ʻh54                  |

| *CH1_A_IDAC_TRACK()  | CH1_A IDAC Track Control Register                                                       | Read/Write | 16 Bits        | ʻh55                  |

| *CH1_A_DELAY_TRACK() | CH1_A IDAC Track Delay Register                                                         | Read/Write | 16 Bits        | ʻh56                  |

| CH1_B_ADC()          | CH1_B ADC Conversion Result Register                                                    | Read Only  | 16 Bits        | ʻh58                  |

| CH1_B_OV()           | CH1_B Over-Voltage Monitor Control Register                                             | Read/Write | 16 Bits        | ʻh59                  |

| CH1_B_UV()           | CH1_B Under-Voltage Monitor Control Register                                            | Read/Write | 16 Bits        | ʻh5A                  |

| TEMP_ADC()           | Temperature ADC Conversion Result Register                                              | Read/Write | 16 Bits        | ʻh68                  |

| RESERVED()           | All other commands are reserved for future expansion and should not be written or read. | Read/Write | 16 Bits        | 'hXX                  |

\*LTC2970-1 Only. LTC2970 will not acknowledge these commands.

### 4. Detailed I<sup>2</sup>C Command Register Descriptions

#### FAULT: Instantaneous Fault Register – Read

| BIT(s)   | SYMBOL           | OPERATION                                                           |

|----------|------------------|---------------------------------------------------------------------|

| b[0]     | Fault_ch0_a_ov   | 0 = The associated channel is clear of                              |

| b[1]     | Fault_ch0_a_uv   | instantaneous faults.                                               |

| b[2]     | Fault_ch0_a_idac | 1 = The associated channel has an<br>instantaneous fault.           |

| b[3]     | Fault_ch0_b_ov   |                                                                     |

| b[4]     | Fault_ch0_b_uv   | The reported faults are instantaneous and not latched. When used in |

| b[5]     | Fault_ch1_a_ov   | conjunction with latched faults they                                |

| b[6]     | Fault_ch1_a_uv   | may indicate faults that are transient in nature.                   |

| b[7]     | Fault_ch1_a_idac |                                                                     |

| b[8]     | Fault_ch1_b_ov   |                                                                     |

| b[9]     | Fault_ch1_b_uv   |                                                                     |

| b[10]    | Fault_vdd_ov     |                                                                     |

| b[11]    | Fault_vdd_uv     |                                                                     |

| b[12]    | Fault_v12_ov     |                                                                     |

| b[13]    | Fault_v12_uv     |                                                                     |

| b[15:14] | Reserved         | Always Returns 0                                                    |

#### FAULT\_EN: Fault Enabling Register - Read/Write

| FAULI_E | FAULI_EN: Fault Eliability Register – Reau/Write |                                                                                                                                                                                                              |  |  |  |

|---------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BIT(s)  | SYMBOL                                           | OPERATION                                                                                                                                                                                                    |  |  |  |

| b[0]    | Fault_en_ch0_a_ov                                | 0 = The associated bit in the                                                                                                                                                                                |  |  |  |

| b[1]    | Fault_en_ch0_a_uv                                | FAULT_LA register will always be 0. (default)                                                                                                                                                                |  |  |  |

| b[2]    | Fault_en_ch0_a_idac                              | 1 = Instantaneous faults reported in                                                                                                                                                                         |  |  |  |

| b[3]    | Fault_en_ch0_b_ov                                | the FAULT register will set associated                                                                                                                                                                       |  |  |  |

| b[4]    | Fault_en_ch0_b_uv                                | bit in the FAULT_LA register.                                                                                                                                                                                |  |  |  |

| b[5]    | Fault_en_ch1_a_ov                                |                                                                                                                                                                                                              |  |  |  |

| b[6]    | Fault_en_ch1_a_uv                                |                                                                                                                                                                                                              |  |  |  |

| b[7]    | Fault_en_ch1_a_idac                              |                                                                                                                                                                                                              |  |  |  |

| b[8]    | Fault_en_ch1_b_ov                                |                                                                                                                                                                                                              |  |  |  |

| b[9]    | Fault_en_ch1_b_uv                                |                                                                                                                                                                                                              |  |  |  |

| b[10]   | Fault_en_vdd_ov                                  |                                                                                                                                                                                                              |  |  |  |

| b[11]   | Fault_en_vdd_uv                                  |                                                                                                                                                                                                              |  |  |  |

| b[12]   | Fault_en_v12_ov                                  |                                                                                                                                                                                                              |  |  |  |

| b[13]   | Fault_en_v12_uv                                  |                                                                                                                                                                                                              |  |  |  |

| b[14]   | Fault_en_ch0_a_servo                             | 0 = Do not re-servo CH0_A in<br>response to instantaneous OV or UV<br>fault.                                                                                                                                 |  |  |  |

|         |                                                  | 1 = Repeat a one time servo of CH0_A<br>in response to instantaneous OV or<br>UV fault. CH0_A must have servo<br>operation enabled with Ch0_a_idac_<br>servo_repeat set low, and Adc_mon_<br>ch0_a set high. |  |  |  |

| b[15]   | Fault_en_ch1_a_servo                             | 0 = Do not re-servo CH1_A in<br>response to instantaneous OV or UV<br>fault.                                                                                                                                 |  |  |  |

|         |                                                  | 1 = Repeat a one time servo of CH1_A<br>in response to instantaneous OV or<br>UV fault. CH1_A must have servo<br>operation enabled with Idac_ch1_a_<br>servo_repeat set low, and Adc_mon_<br>ch1_a set high. |  |  |  |

4. Detailed I<sup>2</sup>C Command Register Descriptions (Cont.)

#### FAULT\_INDEX: Latched Fault Index Register - Read

| BIT(s)  | SYMBOL         | OPERATION                                                                                                            |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------|

| b[0]    | Fault_la_index | 0 = All faults indicated by FAULT_LA are clear.                                                                      |

|         |                | 1 = One or more faults indicated by<br>FAULT_LA are set.                                                             |

|         |                | This register allows a summary of all latched faults to be viewed in a single read without resetting latched faults. |

| b[15:1] | Reserved       | Always Returns 0                                                                                                     |

#### FAULT\_LA: Latched Fault Register - Read

| BIT(s)   | SYMBOL              | OPERATION                                                                    |

|----------|---------------------|------------------------------------------------------------------------------|

| b[0]     | Fault_la_ch0_a_ov   | 0 = The associated channel is clear of                                       |

| b[1]     | Fault_la_ch0_a_uv   | faults.                                                                      |

| b[2]     | Fault_la_ch0_a_idac | 1 = The associated channel has faulted<br>and is enabled.                    |

| b[3]     | Fault_la_ch0_b_ov   | The latched faults are set and held                                          |

| b[4]     | Fault_la_ch0_b_uv   | when the associated instantaneous                                            |

| b[5]     | Fault_la_ch1_a_ov   | fault channel has faulted with faults                                        |

| b[6]     | Fault_la_ch1_a_uv   | enabled. Clearing the enable bit for the associated channel in FAULT_EN will |

| b[7]     | Fault_la_ch1_a_idac | immediately clear its corresponding                                          |

| b[8]     | Fault_la_ch1_b_ov   | latched fault bit.                                                           |

| b[9]     | Fault_la_ch1_b_uv   | All latched channel faults are cleared                                       |

| b[10]    | Fault_la_vdd_ov     | when this register is read. They may be set again if the instantaneous       |

| b[11]    | Fault_la_vdd_uv     | fault condition and fault_en have not                                        |

| b[12]    | Fault_la_v12_ov     | changed.                                                                     |

| b[13]    | Fault_la_v12_uv     |                                                                              |

| b[15:14] | Reserved            | Always Returns 0                                                             |

# IO: Input/Output Data and General Purpose Control Register – Read/Write unless specified otherwise.

| BIT(s)   | SYMBOL             | OPERATION                                                                                                                                                              |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[1:0]   | lo_cfg_0[1:0]      | Io_cfg_0[1:0] is used to configure the function of the GPI0_0 pin and IO(Io_gpio_0).                                                                                   |

|          |                    | 00: lo_gpio_0 = GPIO_0 = Power_good. Power_<br>good asserts high if there are no instantaneous<br>over-voltage or under-voltage faults.                                |

|          |                    | 01: lo_gpio_0 = GPIO_0 = Power_good_bar.<br>Power_good_bar is the complement of<br>Power_good.                                                                         |

|          |                    | 10: GPIO_0 is a general-purpose open-drain output and mirrors the value written to lo_gpio_0 (default).                                                                |

| _        |                    | 11: GPIO_0 is a general-purpose digital input with lo_gpio_0 = GPIO_0                                                                                                  |

| b[3:2]   | lo_cfg_1[1:0]      | lo_cfg_1[1:0] is used to configure the function of the GPIO_1 pin and IO(Io_gpio_1).                                                                                   |

|          |                    | 00: $lo_gpio_1 = GPIO_1 = Idac_fault$ .<br>$Idac_fault$ asserts if either IDAC value is faulted<br>$(Chn_idac[7:0] = 8'h00 \text{ or } 8'hff)$                         |

|          |                    | 01: lo_gpio_1 = GPIO_1 = Idac_fault_bar.<br>Idac_fault_bar is the complement of Idac_fault.                                                                            |

|          |                    | 10 = GPIO_1 is a general-purpose open-<br>drain output and mirrors the value written to<br>lo_gpio_1 (default).                                                        |

|          |                    | 11 = GPIO_1 is a general-purpose digital input<br>with lo_gpio_1 = GPIO_1                                                                                              |

| b[4]     | lo_gpio_0          | See Io_cfg_0.<br>If the GPIO_CFG pin is pulled-high during a<br>power on reset, Io_gpio_0 is cleared and the<br>GPIO_0 open-drain output will assert low.              |

| b[5]     | lo_gpio_1          | See lo_cfg_1.<br>If the GPIO_CFG pin is pulled-high during a<br>power on reset, lo_gpio_1 is cleared and the<br>GPIO_1 open-drain output will assert low.              |

| b[6]     | lo_alertb          | Mirrors the value of the ALERT pin.<br>Read only.                                                                                                                      |

| b[7]     | lo_alertb_enb      | 1 = ALERT pin never asserts (default).<br>0 = ALERT pin asserts low when one or more<br>FAULT_LA bits are set.                                                         |

| b[8]     | lo_i2c_adc_<br>wen | 1 = Special test mode that inhibits ADC from<br>writing to ADC result register and allows user<br>to update registers over the $I^2C$ serial interface.                |

|          |                    | 0 = Normal operation (default).                                                                                                                                        |

| b[9]     | lo_gpio_cfg        | Read only. GPIO_CFG digital input and open-<br>drain output. Reading this bit returns the<br>current state of the GPIO_CFG pin voltage.                                |

| b[10]    | lo_track_start     | Writing a 1 to this bit will start tracking all<br>enabled channels. Returns a 1 when tracking<br>is pending (LTC2970-1). Reserved on LTC2970<br>and always returns 0. |

| b[15:11] | Reserved           | Always Returns 0                                                                                                                                                       |

|          |                    |                                                                                                                                                                        |

4. Detailed I<sup>2</sup>C Command Register Descriptions (Cont.)

#### ADC\_MON: ADC Monitoring Mux Control Register – Read/Write

| BIT(s)  | SYMBOL        | OPERATION                                                |

|---------|---------------|----------------------------------------------------------|

| b[0]    | Adc_mon_vdd   | 0 = ADC will not convert associated                      |

| b[1]    | Adc_mon_v12   | channel. (Default)                                       |

| b[2]    | Adc_mon_ch0_a | 1 = ADC will continuously convert<br>associated channel. |

| b[3]    | Adc_mon_ch0_b |                                                          |

| b[4]    | Adc_mon_ch1_a |                                                          |

| b[5]    | Adc_mon_ch1_b |                                                          |

| b[6]    | Adc_mon_temp  |                                                          |

| b[15:7] | Reserved      | Always Returns 0                                         |

# SYNC: Tracking Synchronization Control Register – Read/Write LTC2970-1 Only

| BIT(s)  | SYMBOL     | OPERATION                                                                                                                                                                                                                                                                                                                                           |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[0]    | Sync_track | Write<br>0 = Do not synchronize.                                                                                                                                                                                                                                                                                                                    |

|         |            | 1 = Synchronize all tracking enabled registers to the same starting point.                                                                                                                                                                                                                                                                          |

|         |            | Read<br>0 = The LTC2970-1 is not synchronized<br>for tracking (default).                                                                                                                                                                                                                                                                            |

|         |            | 1 = The LTC2970-1 is synchronized for tracking.                                                                                                                                                                                                                                                                                                     |

|         |            | Use of the global address will allow<br>the synchronization status of multiple<br>LTC2970-1s to be verified in a single<br>read; since a one can only be returned<br>if all LTC2970-1s are synchronized. The<br>IO_track_start command may then be<br>issued with the same global address<br>to begin synchronized tracking across<br>multiple ICs. |

| b[15:1] | Reserved   | Always Returns 0                                                                                                                                                                                                                                                                                                                                    |

# VDD\_ADC, V12\_ADC, CH0\_A\_ADC, CH0\_B\_ADC, CH1\_A\_ADC, CH1\_B\_ADC, and TEMP\_ADC: ADC Conversion Result Registers – Read Only Unless Specified Otherwise

| BIT(s)  | SYMBOL                                                                                                         | OPERATION                                                                                                                                                                |

|---------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[14:0] | Vdd_adc[14:0]<br>V12_adc[14:0]<br>Ch0_a_adc[14:0]<br>Ch0_b_adc[14:0]                                           | Measured data from ADC conversion<br>'h4000 corresponds to negative full-<br>scale input voltage.<br>'h0000 corresponds to 0V.<br>'h3fff corresponds to full-scale input |

|         | Ch1_a_adc[14:0]<br>Ch1_b_adc[14:0]<br>Temp_adc[14:0]                                                           | voltage.<br>2's complement format, b[14] = sign.<br>Read/Write when lo_i2c_adc_wen = 1.<br>Default value is undefined.                                                   |

| b[15]   | Vdd_adc_new<br>V12_adc_new<br>Ch0_a_adc_new<br>Ch0_b_adc_new<br>Ch1_a_adc_new<br>Ch1_b_adc_new<br>Temp_adc_new | <ul> <li>1 = The ADC has updated the associated result register since the last time the data was read.</li> <li>0 = Previously read data. (Default)</li> </ul>           |

#### VDD\_OV, V12\_OV, CH0\_A\_OV, CH0\_B\_OV, CH1\_A\_OV, CH1\_B\_ OV: Over Voltage Limit Registers – Read/Write

| BIT(s)  | SYMBOL         | OPERATION                                                                         |

|---------|----------------|-----------------------------------------------------------------------------------|

| b[14:0] | Vdd_ov[14:0]   | ADC over-voltage threshold limit.                                                 |

|         | V12_ov[14:0]   | The associated instantaneous over                                                 |

|         | Ch0_a_ov[14:0] | voltage fault is asserted if the channel's ADC result is greater than this limit. |

|         | Ch0_b_ov[14:0] | Code 'h3fff disables OV threshold                                                 |

|         | Ch1_a_ov[14:0] | detect feature for that channel.                                                  |

|         | Ch1_b_ov[14:0] | 2's complement format, b[14] = sign.                                              |

|         |                | Default value is undefined.                                                       |

| b[15]   | Reserved       | Always Returns 0                                                                  |

#### VDD\_UV, V12\_UV, CH0\_A\_UV, CH0\_B\_UV, CH1\_A\_UV, CH1\_B\_ UV: Under Voltage Limit Registers – Read/Write

| BIT(s)  | SYMBOL         | OPERATION                                                                         |

|---------|----------------|-----------------------------------------------------------------------------------|

| b[14:0] | Vdd_uv[14:0]   | ADC under-voltage threshold limit.                                                |

|         | V12_uv[14:0]   | The associated instantaneous under                                                |

|         | Ch0_a_uv[14:0] | voltage fault is asserted if the channel's ADC result is greater than this limit. |

|         | Ch0_b_uv[14:0] | Code 'h4000 disables UV threshold                                                 |

|         | Ch1_a_uv[14:0] | detect feature for that channel.                                                  |

|         | Ch1_b_uv[14:0] | 2's complement format, b[14] = sign.                                              |

|         |                | Default value is undefined.                                                       |

| b[15]   | Reserved       | Always Returns 0                                                                  |

4. Detailed I<sup>2</sup>C Command Register Descriptions (Cont.)

# CH0\_A\_SERVO, CH1\_A\_SERVO: Voltage Servo Control Registers – Read/Write

| BIT(s)  | SYMBOL            | OPERATION                                                                                                                                                     |

|---------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[14:0] | Ch0_a_servo[14:0] | During servo operation                                                                                                                                        |

|         | Ch1_a_servo[14:0] | Ch <i>n</i> _a_idac[7:0] output current is<br>stepped to force Ch <i>n</i> _a_adc[14:0]<br>code to equal target code stored in<br>Ch <i>n</i> _a_servo[14:0]. |

|         |                   | 2's complement format, b[14] = sign                                                                                                                           |

|         |                   | Default value is undefined.                                                                                                                                   |

| b[15]   | Ch0_a_servo_en    | 0 = Ch <i>n</i> _a servo disabled (default).                                                                                                                  |

|         | Ch1_a_servo_en    | 1 = Ch <i>n</i> _a servo enabled.                                                                                                                             |

# CH0\_A\_IDAC, CH1\_A\_IDAC: IDAC Control/Data Registers - Read/Write

| BIT(s) | SYMBOL                                            | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[7:0] | Ch0_a_idac[7:0]                                   | Chn_a IDAC data value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| b[8]   | Ch1_a_idac[7:0]<br>Ch0_a_idac_en<br>Ch1_a_idac_en | <ul> <li>0 = V<sub>OUTn</sub> output tri-stated.</li> <li>1 = V<sub>OUTn</sub> output enabled.</li> <li>There are two ways to enable V<sub>OUTn</sub>.</li> <li>1) When Chn_a_idac_en is set high with Chn_a_idac_con low, the LTC2970 will perform a soft connect. During a soft connect, the V<sub>OUTn</sub> voltage buffer output will not be connected to the V<sub>OUTn</sub> pin until the internal algorithm has servo'd the voltage at the IDACn pin to match the V<sub>OUTn</sub> pin voltage. Resolution is one Chn_a_idac_En is</li> <li>2) When Chn_a_idac_en is</li> </ul> |

|        |                                                   | enabled with $Ch_a_i dac_con$<br>high, the LTC2970 will perform<br>a hard connect. The $V_{OUTn}$<br>voltage buffer will be immediately<br>connected to the $V_{OUTn}$ pin.                                                                                                                                                                                                                                                                                                                                                                                                              |

| b[9]   | Ch0_a_idac_con<br>Ch1_a_idac_con                  | $0 = V_{OUTn}$ is not enabled or<br>has been enabled but is not yet<br>connected to the output of the<br>CHn voltage buffer. (Default)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |