# Dual 12-Bit Rail-to-Rail Micropower DACs

#### **FEATURES**

- 12-Bit Resolution

- Buffered True Rail-to-Rail Voltage Output

- 5V Operation, I<sub>CC</sub>: 700µA Typ (LTC1454)

- 3V Operation, I<sub>CC</sub>: 450µA Typ (LTC1454L)

- Built-In Reference: 2.048V (LTC1454)

- 1.220V (LTC1454L)

- CLR Pin

- Power-On Reset

- 16-Lead SO Package

- 3-Wire Cascadable Serial Interface

- Maximum DNL Error: 0.5LSB

- Low Cost

#### **APPLICATIONS**

- Digital Calibration

- Industrial Process Control

- Automatic Test Equipment

- Cellular Telephones

#### DESCRIPTION

The LTC®1454/LTC1454L are complete single supply, dual rail-to-rail voltage output, 12-bit digital-to-analog converters (DACs) in a 16-lead SO package. They include an output buffer amplifier with variable gain ( $\times 1$  or  $\times 2$ ) and an easy-to-use 3-wire cascadable serial interface.

The LTC1454 has an onboard reference of 2.048V and a full-scale output of 4.095V in a  $\times 2$  gain configuration. It operates from a single 4.5V to 5.5V supply.

The LTC1454L has an onboard 1.22V reference and a full-scale output of 2.5V in a  $\times$  2 gain configuration. It operates from a single 2.7V to 5.5V supply.

Low power supply current, excellent DNL and small size allow these parts to be used in a host of applications where size, DNL and single supply operation are important.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

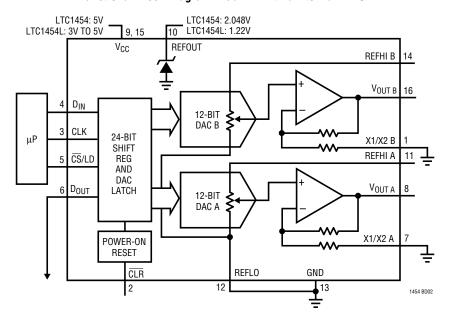

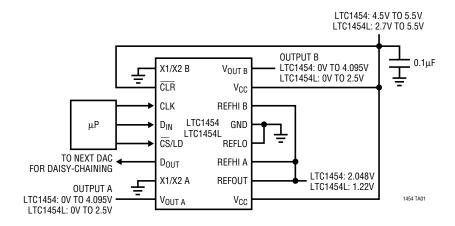

#### TYPICAL APPLICATION

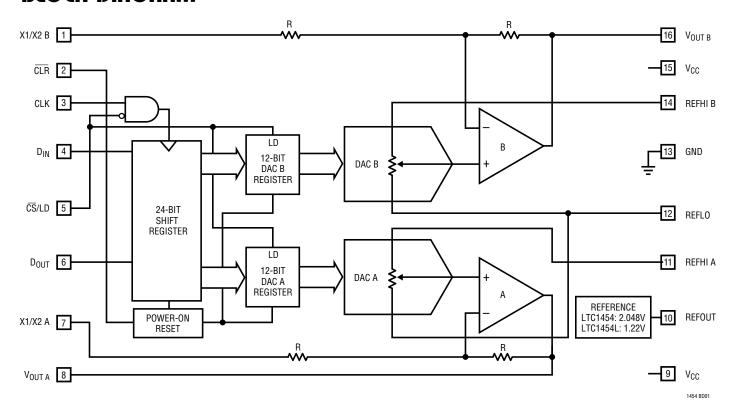

#### Functional Block Diagram: Dual 12-Bit Rail-to-Rail DAC

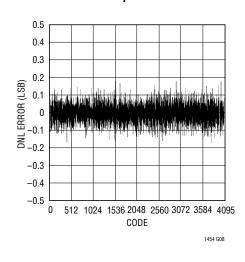

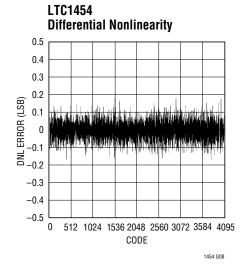

# Differential Nonlinearity vs Input Code

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.5V to 7.5V                 |

|----------------------------------------------------|

| Logic Inputs to GND −0.5V to 7.5V                  |

| $V_{OUT A}$ , $V_{OUT B}$ , $X1/X2 A$ ,            |

| $X1/X2 B$ $-0.5V$ to $V_{CC} + 0.5V$               |

| REFHI A, REFHI B, REFLO $-0.5V$ to $V_{CC} + 0.5V$ |

| Maximum Junction Temperature 125°C                 |

| Operating Temperature Range                        |

| LTC1454C/LTC1454LC0°C to 70°C                      |

| LTC1454I/LTC1454LI40°C to 85°C                     |

| Storage Temperature Range65°C to 150°C             |

| Lead Temperature (Soldering, 10 sec) 300°C         |

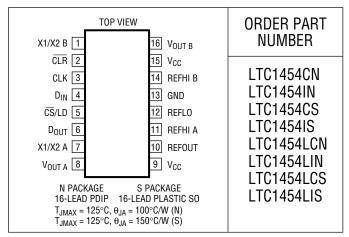

#### PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 4.5V to 5.5V (LTC1454), 2.7V to 5.5V (LTC1454L), X1/X2 = REFLO = GND, REFHI = REFOUT,  $V_{OUT}$  and REFOUT unloaded,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL              | PARAMETER                                   | CONDITIONS                                                     |   | MIN   | TYP                | MAX   | UNITS  |

|---------------------|---------------------------------------------|----------------------------------------------------------------|---|-------|--------------------|-------|--------|

| DAC                 |                                             |                                                                |   |       |                    |       |        |

|                     | Resolution                                  |                                                                | • | 12    |                    |       | Bits   |

| DNL                 | Differential Nonlinearity                   | Guaranteed Monotonic (Note 1)                                  | • |       |                    | ± 0.5 | LSB    |

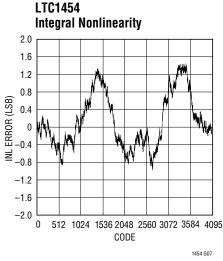

| INL                 | Integral Nonlinearity                       | T <sub>A</sub> = 25°C                                          |   |       | ±2.0               | ±4.0  | LSB    |

|                     |                                             | (Note 1)                                                       | • |       | ±2.5               | ±4.5  | LSB    |

| V <sub>OS</sub>     | Offset Error                                | T <sub>A</sub> = 25°C                                          |   |       | ±2.0               | ±12   | mV     |

|                     |                                             |                                                                | • |       | ±4.0               | ±18   | mV     |

| V <sub>OS</sub> TC  | Offset Error Temperature<br>Coefficient     |                                                                |   |       | ±15                |       | μV/°C  |

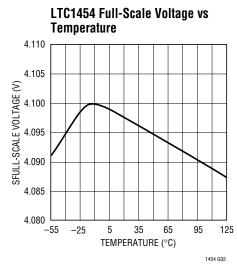

| $\overline{V_{FS}}$ | Full-Scale Voltage                          | When Using Internal Reference, LTC1454, T <sub>A</sub> = 25°C  |   | 4.065 | 4.095              | 4.125 | V      |

|                     |                                             | LTC1454                                                        | • | 4.045 | 4.095              | 4.145 | V      |

|                     |                                             | When Using Internal Reference, LTC1454L, T <sub>A</sub> = 25°C |   | 2.470 | 2.500              | 2.530 | V      |

|                     |                                             | LTC1454L                                                       | • | 2.460 | 2.500              | 2.540 | V      |

| V <sub>FS</sub> TC  | Full-Scale Voltage Temperature Coefficient  | When Using Internal Reference                                  |   |       | ± 24               |       | ppm/°C |

| Reference           | e                                           |                                                                |   |       |                    |       |        |

|                     | Reference Output Voltage                    | LTC1454                                                        | • | 2.008 | 2.048              | 2.088 | V      |

|                     |                                             | LTC1454L                                                       | • | 1.195 | 1.220              | 1.245 | V      |

|                     | Reference Output<br>Temperature Coefficient |                                                                |   |       | ±20                |       | ppm/°C |

|                     | Reference Line Regulation                   |                                                                | • |       | 0.7                | ±2.0  | LSB/V  |

|                     | Reference Load Regulation                   | 0 ≤ I <sub>OUT</sub> ≤ 100μA, LTC1454                          | • |       | 0.2                | 1.5   | LSB    |

|                     |                                             | LTC1454L                                                       |   |       | 0.6                | 3.0   | LSB    |

|                     | Reference Input Range                       | $V_{REFHI} \le V_{CC} - 1.5V$                                  |   |       | V <sub>CC</sub> /2 |       | V      |

|                     | Reference Input Resistance                  |                                                                | • | 15    | 24                 | 40    | kΩ     |

|                     | Reference Input Capacitance                 |                                                                |   |       | 15                 |       | pF     |

| -                   | Short-Circuit Current                       | REFOUT Shorted to GND                                          | • |       | 40                 | 120   | mA     |

## **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 4.5V to 5.5V (LTC1454), 2.7V to 5.5V (LTC1454L), X1/X2 = REFLO = GND, REFHI = REFOUT,  $V_{OUT}$  and REFOUT unloaded,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL          | PARAMETER                    | CONDITIONS                                                                                          |   | MIN        | TYP        | MAX          | UNITS    |

|-----------------|------------------------------|-----------------------------------------------------------------------------------------------------|---|------------|------------|--------------|----------|

| Power Su        | pply                         |                                                                                                     | • |            |            |              |          |

| V <sub>CC</sub> | Positive Supply Voltage      | For Specified Performance, LTC1454<br>LTC1454L                                                      | • | 4.5<br>2.7 |            | 5.5<br>5.5   | V        |

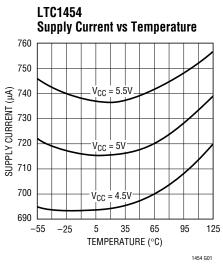

| I <sub>CC</sub> | Supply Current               | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V (Note 4), LTC1454<br>2.7V ≤ V <sub>CC</sub> ≤ 5.5V (Note 4), LTC1454L | • |            | 700<br>450 | 1250<br>1100 | μA<br>μA |

| Op Amp D        | C Performance                |                                                                                                     |   |            |            |              |          |

|                 | Short-Circuit Current Low    | V <sub>OUT</sub> Shorted to GND                                                                     | • |            | 70         | 120          | mA       |

|                 | Short-Circuit Current High   | V <sub>OUT</sub> Shorted to V <sub>CC</sub>                                                         | • |            | 80         | 120          | mA       |

|                 | Output Impedance to GND      | Input Code = 0                                                                                      | • |            | 40         |              | Ω        |

| AC Perfor       | mance                        |                                                                                                     |   |            |            |              |          |

|                 | Voltage Output Slew Rate     | (Note 2)                                                                                            | • | 0.5        | 1.0        |              | V/µs     |

|                 | Voltage Output Settling Time | (Notes 2, 3) to ±0.5LSB                                                                             |   |            | 14         |              | μS       |

|                 | Digital Feedthrough          |                                                                                                     |   |            | 0.3        |              | nV∙s     |

|                 | AC Feedthrough               | REFHI = 1kHz, 2V <sub>P-P</sub> , (Code: All 0s)                                                    |   |            | -95        |              | dB       |

| SINAD           | Signal-to-Noise + Distortion | REFHI = 1kHz, 2V <sub>P-P</sub> , (Code: All 1s)                                                    |   |            | 85         |              | dB       |

$V_{CC} = 5V$  (LTC1454), 3V (LTC1454L),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

|                            |                                    |                                   |   | LTC1454               |     |     | L                     |     |     |       |

|----------------------------|------------------------------------|-----------------------------------|---|-----------------------|-----|-----|-----------------------|-----|-----|-------|

| SYMBOL                     | PARAMETER                          | CONDITIONS                        |   | MIN                   | TYP | MAX | MIN                   | TYP | MAX | UNITS |

| Digital I/O                | 1                                  |                                   |   |                       |     |     |                       |     |     |       |

| $\overline{V_{\text{IH}}}$ | Digital Input High Voltage         |                                   | • | 2.4                   |     |     | 2.0                   |     |     | V     |

| $\overline{V_{IL}}$        | Digital Input Low Voltage          |                                   | • |                       |     | 0.8 |                       |     | 0.6 | V     |

| $\overline{V_{OH}}$        | Digital Output High Voltage        | I <sub>OUT</sub> = -1mA           | • | V <sub>CC</sub> - 1.0 |     |     | V <sub>CC</sub> - 0.7 |     |     | V     |

| $\overline{V_{0L}}$        | Digital Output Low Voltage         | I <sub>OUT</sub> = 1mA            | • |                       |     | 0.4 |                       |     | 0.4 | V     |

| I <sub>LEAK</sub>          | Digital Input Leakage              | $V_{IN} = GND \text{ to } V_{CC}$ | • |                       |     | ±10 |                       |     | ±10 | μА    |

| C <sub>IN</sub>            | Digital Input Capacitance          | Guaranteed by Design              | • |                       |     | 10  |                       |     | 10  | pF    |

| Switching                  |                                    |                                   | ' |                       |     |     | '                     |     |     |       |

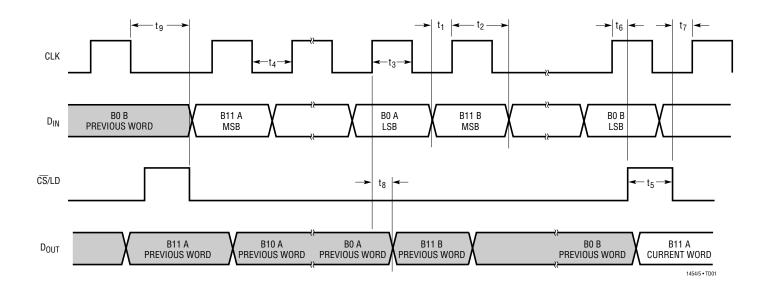

| t <sub>1</sub>             | D <sub>IN</sub> Valid to CLK Setup |                                   | • | 40                    |     |     | 60                    |     |     | ns    |

| $\overline{t_2}$           | D <sub>IN</sub> Valid to CLK Hold  |                                   | • | 0                     |     |     | 0                     |     |     | ns    |

| $\overline{t_3}$           | CLK High Time                      |                                   | • | 40                    |     |     | 60                    |     |     | ns    |

| $\overline{t_4}$           | CLK Low Time                       |                                   | • | 40                    |     |     | 60                    |     |     | ns    |

| t <sub>5</sub>             | CS/LD Pulse Width                  |                                   | • | 50                    |     |     | 80                    |     |     | ns    |

| $\overline{t_6}$           | LSB CLK to CS/LD                   |                                   | • | 40                    |     |     | 60                    |     |     | ns    |

| t7                         | CS/LD Low to CLK                   |                                   | • | 20                    |     |     | 30                    |     |     | ns    |

| t <sub>8</sub>             | D <sub>OUT</sub> Output Delay      | C <sub>LOAD</sub> = 15pF          | • |                       |     | 150 |                       |     | 220 | ns    |

| t <sub>9</sub>             | CLK Low to CS/LD Low               |                                   | • | 20                    |     |     | 30                    |     |     | ns    |

The ullet denotes specifications which apply over the full operating temperature range.

**Note 1:** Nonlinearity is defined from the first code that is greater than or equal to the maximum offset specification to code 4095 (full scale).

Note 2: Load is  $5k\Omega$  in parallel with 100pF.

Note 3: DAC switched between all 1s and the code corresponding to  $V_{OS}$  for the part.

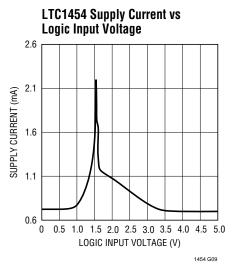

**Note 4:** Digital inputs at OV or  $V_{CC}$ .

## TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

**X1/X2 B, X1/X2 A (Pins 1, 7):** The Input Pin that Sets the Gain for DAC A/B. When grounded the gain will be 2, i.e., output full scale will be  $\times 2$  REFHI. When connected to  $V_{OUT}$  the gain will be 1, i.e., output full scale will be equal to REFHI.

$\overline{\text{CLR}}$  (Pin 2): The Clear Pin for the DAC. Clears both DACs to zero scale when pulled low. This pin should be tied to  $V_{CC}$  for normal operation.

**CLK (Pin 3):** The Serial Interface Clock Input.

$D_{IN}$  (Pin 4): The Serial Data Input. Data on the  $D_{IN}$  pin is latched into the shift register on the rising edge of the serial clock. Data is loaded as one 24-bit word. The first 12 bits are for DAC A, MSB-first and the second 12 bits are for DAC B, MSB-first.

**CS/LD** (**Pin 5**): The Serial Interface Enable and Load Control Input. When  $\overline{CS}/LD$  is low the CLK signal is enabled so the data can be clocked in. When  $\overline{CS}/LD$  is

pulled high, data is loaded from the shift register into the DAC register, updating the DAC output.

**D**<sub>OUT</sub> (**Pin 6**): The Output of the Shift Register which Becomes Valid on the Rising Edge of the Serial Clock.

V<sub>OUT A.</sub> V<sub>OUT B</sub> (Pins 8, 16): The Buffered DAC Outputs.

**V<sub>CC</sub>** (**Pins 9, 15**): The Positive Supply Input.  $4.5 \le V_{CC} \le 5.5V$  (LTC1454),  $2.7V \le V_{CC} \le 5.5V$  (LTC1454L). Requires a bypass capacitor to ground.

**REFOUT (Pin 10):** The Output of the Internal Reference.

**REFHI A**, **REFHI B** (**Pins 11,14**): The Inputs to the DAC Resistor Ladder for DAC A/B.

**REFLO (Pin 12):** The Bottom of the DAC Resistor Ladder for Both DACs. This can be used to offset zero-scale above ground. REFLO should be connected to ground when no offset is required.

GND (Pin 13): Ground.

## **BLOCK DIAGRAM**

## TIMING DIAGRAM

#### **DEFINITIONS**

**Resolution (n):** Resolution is defined as the number of digital input bits, n. It defines the number of DAC output states (2<sup>n</sup>) that divide the full-scale range. The resolution does not imply linearity.

**Full-Scale Voltage (V<sub>FS</sub>):** This is the output of the DAC when all bits are set to 1.

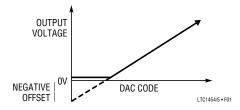

**Voltage Offset Error (V<sub>OS</sub>):** The theoretical voltage at the output when the DAC is loaded with all zeros. The output amplifier can have a true negative offset, but because the part is operated from a single supply, the output cannot go below zero. If the offset is negative, the output will remain near 0V resulting in the transfer curve shown in Figure 1.

Figure 1. Effect of Negative Offset

The offset of the part is measured at the code that corresponds to the maximum offset specification:

$$V_{OS} = V_{OUT} - (Code)(V_{FS})/(2^n - 1)$$

**Least Significant Bit (LSB):** One LSB is the ideal voltage difference between two successive codes.

LSB =

$$(V_{FS} - V_{OS})/(2^n - 1) = (V_{FS} - V_{OS})/4095$$

Nominal LSBs:

Integral Nonlinearity (INL): End-point INL is the maximum deviation from a straight line passing through the end-points of the DAC transfer curve. Because the part operates from a single supply and the output cannot go below zero, the linearity is measured between full scale and the code corresponding to the maximum offset specification. The INL error at a given input code is calculated as follows:

INL =

$$[V_{OUT} - V_{OS} - (V_{FS} - V_{OS})(Code/4095)]/LSB$$

$V_{OUT}$  = The output voltage of the DAC measured at the given input code

**Differential Nonlinearity (DNL):** DNL is the difference between the measured change and the ideal 1LSB change between any two adjacent codes. The DNL error between any two codes is calculated as follows:

DNL =

$$(\Delta V_{OUT} - LSB)/LSB$$

$\Delta V_{OUT}$  = The measured voltage difference between

two adjacent codes

**Digital Feedthrough:** The glitch that appears at the analog output caused by AC coupling from the digital inputs when they change state. The area of the glitch is specified in (nV)(sec).

#### **OPERATION**

#### **Serial Interface**

The data on the  $D_{IN}$  input is loaded into the shift register on the rising edge of the clock. Data is loaded as one 24-bit word, DAC A first, then DAC B. The MSB is loaded first for each DAC. The DAC registers load the data from the shift register when  $\overline{CS}/LD$  is pulled high. The CLK is disabled internally when  $\overline{CS}/LD$  is high. Note: CLK must be low before  $\overline{CS}/LD$  is pulled low to avoid an extra internal clock pulse.

The buffered output of the 24-bit shift register is available on the  $D_{OUT}$  pin which swings from ground to  $V_{CC}$ .

Multiple LTC1454/LTC1454Ls may be daisy-chained together by connecting the  $D_{OUT}$  pin to the  $D_{IN}$  pin of the next chip, while the CLK and  $\overline{\text{CS}}/\text{LD}$  signals remain common to all chips in the daisy-chain. The serial data is clocked to all of the chips, then the  $\overline{\text{CS}}/\text{LD}$  signal is pulled high to update all of them simultaneously.

#### Reference

The LTC1454L has an internal reference of 1.22V with a full scale of 2.5V (gain of 2 configuration). The LTC1454 includes an internal 2.048V reference, making 1LSB equal to 1mV (gain of 2 configuration). When the buffer gain is 2, the external reference must be less than  $V_{\rm CC}/2$  and be capable of driving the 15k minimum DAC resistor ladder. With a gain of 1 configuration the external reference must be less than  $V_{\rm CC}-1.5$ V.

#### **Voltage Output**

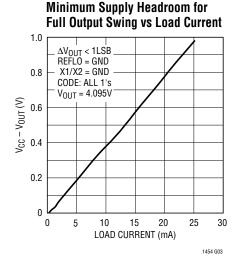

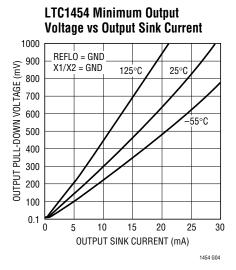

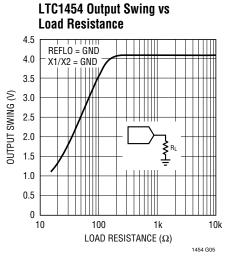

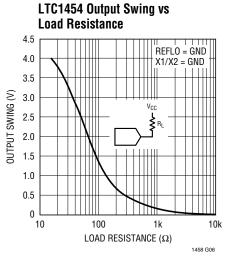

The rail-to-rail buffered output of the LTC1454 family can source or sink 5mA when operating with a 5V supply while pulling to within 300mV of the positive supply voltage or ground. The output swings to within a few millivolts of either supply rail when unloaded and has an equivalent output resistance of  $40\Omega$  when driving a load to the rails. The output can drive 1000pF without going into oscillation.

## APPLICATIONS INFORMATION

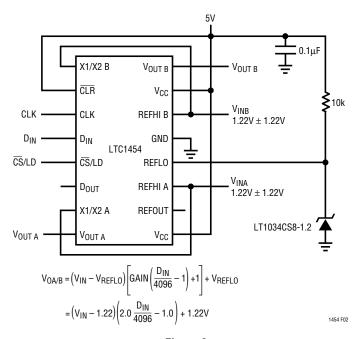

#### A Single Supply, 4-Quadrant Multiplying DAC

The LTC1454 can also be used for 4-quadrant multiplying with an offset signal ground of 1.22V. This application is shown in Figure 2. The inputs are connected to REFHI B or REFHI A and have a 1.22V amplitude around a signal

ground of 1.22V. The outputs will swing from 0V to 2.44V, as shown by the equation with the figure. Since the signal ground is around 1.22V, REFLO is offset above ground by using an LT1034CS8-1.2 as shown.

Figure 2

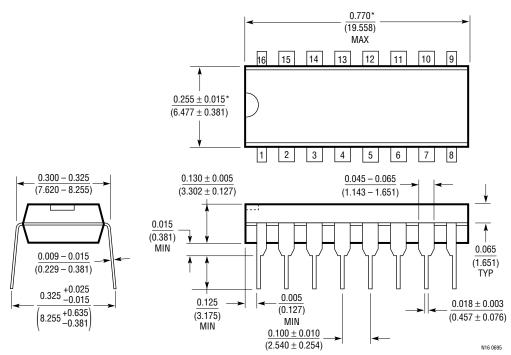

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

N Package 16-Lead PDIP (Narrow 0.300) (LTC DWG # 05-08-1510)

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

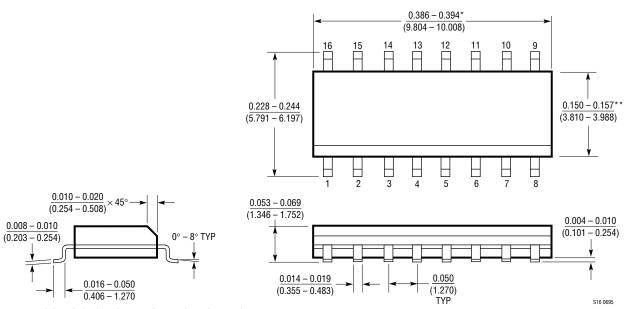

## PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

S Package 16-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

## TYPICAL APPLICATION

## RELATED PARTS

| PART NUMBER      | DESCRIPTION                                                                                                                                                     | COMMENTS                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC1257          | Single 12-Bit V <sub>OUT</sub> DAC, Full Scale: 2.048V, V <sub>CC</sub> : 4.75V to 15.75V, Reference Can Be Overdriven up to 12V, i.e., FS <sub>MAX</sub> = 12V | 5V to 15V Single Supply, Complete V <sub>OUT</sub> DAC in SO-8 Package                                                                              |

| LTC1446/LTC1446L | Dual 12-Bit Rail-to-Rail Output DACs in an SO-8 Package                                                                                                         | LTC1446: V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V to 4.095V<br>LTC1446L: V <sub>CC</sub> = 2.7V to 5.5V, V <sub>OUT</sub> = 0V to 2.5V |

| LTC1450/LTC1450L | Single 12-Bit Rail-to-Rail Output DACs with Parallel Interface                                                                                                  | LTC1450: V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V to 4.095V<br>LTC1450L: V <sub>CC</sub> = 2.7V to 5.5V, V <sub>OUT</sub> = 0V to 2.5V |

| LTC1451          | Single 12-Bit DAC, Full Scale: 4.095V, V <sub>CC</sub> : 4.5V to 5.5V                                                                                           | Low Power, Complete V <sub>OUT</sub> DAC in SO-8 Package                                                                                            |

| LTC1452          | Single 12-Bit Rail-to-Rail Output V <sub>OUT</sub> Multiplying DAC, V <sub>CC</sub> : 2.7V to 5.5V                                                              | Low Power, Multiplying V <sub>OUT</sub> DAC with Rail-to-Rail<br>Buffer Amplifier in SO-8 Package                                                   |

| LTC1453          | Single 12-Bit V <sub>OUT</sub> DAC, Full Scale: 2.5V, V <sub>CC</sub> : 2.7V to 5.5V                                                                            | 3V, Low Power, Complete V <sub>OUT</sub> DAC in SO-8 Package                                                                                        |

| LTC1456          | Single Rail-to-Rail Output 12-Bit DAC with Clear Pin, Full Scale: 4.095V, V <sub>CC</sub> : 4.5V to 5.5V                                                        | Low Power, Complete V <sub>OUT</sub> DAC in SO-8 Package, with Clear Pin                                                                            |

| LTC1458/LTC1458L | Quad 12-Bit Rail-to-Rail Output DACs                                                                                                                            | LTC1458: V <sub>CC</sub> = 4.5V to 5.5V, V <sub>OUT</sub> = 0V to 4.095V<br>LTC1458L: V <sub>CC</sub> = 2.7V to 5.5V, V <sub>OUT</sub> = 0V to 2.5V |