# Low Noise, Low Distortion Fully Differential Input/ Output Amplifier/Driver

### **FEATURES**

Fully Differential Input and OutputWide Supply Range: 2.375V to 12.6V

Rail-to-Rail Output Swing

Low Noise: 3nV/√Hz

■ Low Distortion, 2V<sub>P-P</sub>, 1MHz: −94dBc

Adjustable Output Common Mode Voltage

Unity Gain Stable

■ Gain-Bandwidth: 70MHz

Slew Rate: 65V/μs

Large Output Current: 85mA

DC Voltage Offset <2mV MAX</p>

Open-Loop Gain: 100V/mV

Low Power Shutdown

■ 8-Pin MSOP or 3mm × 3mm DFN Package

### **APPLICATIONS**

- Differential Input A/D Converter Driver

- Single-Ended to Differential Conversion

- Differential Amplification with Common Mode Translation

- Rail-to-Rail Differential Line Driver/Receiver

- Low Voltage, Low Noise, Differential Signal Processing

### DESCRIPTION

The LT®1994 is a high precision, very low noise, low distortion, fully differential input/output amplifier optimized for 3V, single supply operation. The LT1994's output common mode voltage is independent of the input common mode voltage, and is adjustable by applying a voltage on the  $V_{OCM}$  pin. A separate internal common mode feedback path provides accurate output phase balancing and reduced even-order harmonics. This makes the LT1994 ideal for level shifting ground referenced signals for driving differential input, single supply ADCs.

The LT1994 output can swing rail-to-rail and is capable of sourcing and sinking up to 85mA. In addition to the low distortion characteristics, the LT1994 has a low input referred voltage noise of  $3\text{nV}/\sqrt{\text{Hz}}$ . This part maintains its performance for supply voltages as low as 2.375V. It draws only 13.5mA of supply current and has a hardware shutdown feature that reduces current consumption to  $300\mu\text{A}$ .

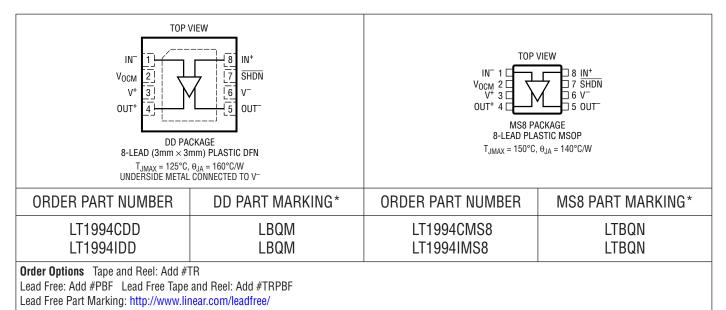

The LT1994 is available in an 8-pin MSOP or 8-pin DFN package.

7, LTC and LT are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

### TYPICAL APPLICATION

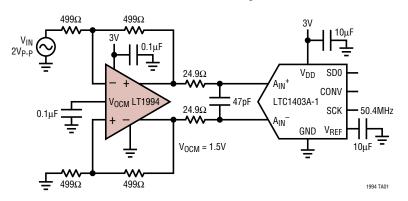

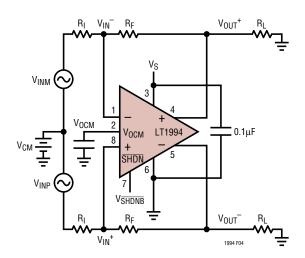

A/D Preamplifier: Single-Ended Input to Differential Output with Common Mode Level Shifting

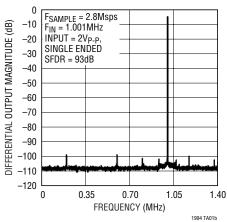

#### LT1994 Driving an LTC1403A-1 1MHz Sine Wave, 8192 Point FFT Plot

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> ) | 12.6V           |

|----------------------------------------------------------|-----------------|

| Input Voltage (Note 2)                                   | ±V <sub>S</sub> |

| Input Current (Note 2)                                   | ±10mÅ           |

| V <sub>OCM</sub> , SHDN                                  | ±V <sub>S</sub> |

| Output Short-Circuit Duration (Note 3)                   |                 |

| Operating Temperature Range (Note 4)                     | _40°C to 85°C   |

| Specified Temperature Range (Note 5)                     | 40°C to 85°C    |

|                                                          |                 |

| Junction Temperature                  |                |

|---------------------------------------|----------------|

| MS8                                   | 150°C          |

| DFN8                                  | 125°C          |

| Storage Temperature Range             |                |

| MS8                                   |                |

| DFN8                                  | –65°C to 125°C |

| Lead Temperature (Soldering, 10 sec). | 300°C          |

### PACKAGE/ORDER INFORMATION

<sup>\*</sup>The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 3V$ ,  $V^- = 0V$ ,  $V_{CM} = V_{OCM} = V_{ICM} = mid$ -supply,  $V_{\overline{SHDNBAR}} = 0$ PEN,  $R_1 = R_F = 499$ ,  $R_L = 800$  to a mid-supply voltage (See Figure 1) unless otherwise noted.  $V_S$  is defined  $(V^+ - V^-)$ .  $V_{OUTCM}$  is defined as  $(V_{OUT}^+ + V_{OUT}^-)/2$ .  $V_{ICM}$  is defined as  $(V_{IN}^+ + V_{IN}^-)/2$ .  $V_{OUTDIFF}$  is defined as  $(V_{OUT}^+ - V_{OUT}^-)$ .  $V_{INDIFF}$  is defined as  $(V_{IN}^+ - V_{IN}^-)/2$ .

| SYMBOL                  | PARAMETER                                             | CONDITIONS                                                                       |   | MIN                      | TYP                      | MAX                  | UNITS |

|-------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------|---|--------------------------|--------------------------|----------------------|-------|

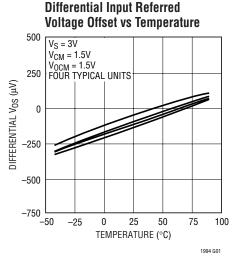

| V <sub>OSDIFF</sub>     | Differential Offset Voltage<br>(Input Referred)       | $V_S = 2.375V, V_{ICM} = V_S/4$<br>$V_S = 3V$<br>$V_S = 5V$<br>$V_S = \pm 5V$    | • |                          |                          | ±2<br>±2<br>±2<br>±3 | mV    |

| V <sub>OSDIFF</sub> / T | Differential Offset Voltage Drift<br>(Input Referred) | $V_S = 2.375V, V_{ICM} = V_S/4$<br>$V_S = 3V$<br>$V_S = 5V$<br>$V_S = \pm 5V$    |   |                          | 3<br>3<br>3<br>3         |                      | μV/°C |

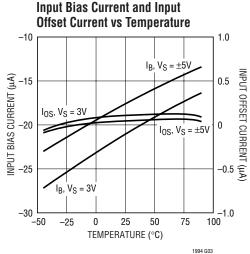

| I <sub>B</sub>          | Input Bias Current<br>(Note 6)                        | $V_S = 2.375V$ , $V_{ICM} = V_S/4$<br>$V_S = 3V$<br>$V_S = 5V$<br>$V_S = \pm 5V$ | • | -45<br>-45<br>-45<br>-45 | -18<br>-18<br>-18<br>-18 | -3<br>-3<br>-3<br>-3 | μА    |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 3V$ ,  $V^- = 0V$ ,  $V_{CM} = V_{OCM} = V_{ICM} = \text{mid-supply}$ ,  $V_{\overline{SHDNBAR}} = 0PEN$ ,  $R_I = R_F = 499$ ,  $R_L = 800$  to a mid-supply voltage (See Figure 1) unless otherwise noted.  $V_S$  is defined ( $V^+ - V^-$ ).  $V_{OUTCM}$  is defined as ( $V_{OUT}^+ + V_{OUT}^-$ )/2.  $V_{ICM}$  is defined as ( $V_{IN}^+ + V_{IN}^-$ )/2.  $V_{OUTDIFF}$  is defined as ( $V_{OUT}^+ - V_{OUT}^-$ ).  $V_{INDIFF}$  is defined as ( $V_{IN}^+ - V_{IN}^-$ ).

| SYMBOL                          | PARAMETER                                                                                  | CONDITIONS                                                                                                             |   | MIN                  | TYP                          | MAX                      | UNITS                            |

|---------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|----------------------|------------------------------|--------------------------|----------------------------------|

| I <sub>0S</sub>                 | Input Offset Current<br>(Note 6)                                                           | $V_S = 2.375V, V_{ICM} = V_S/4$<br>$V_S = 3V$<br>$V_S = 5V$<br>$V_S = \pm 5V$                                          | • |                      | ±0.2<br>±0.2<br>±0.2<br>±0.2 | ±2<br>±2<br>±3<br>±4     | μА                               |

| R <sub>IN</sub>                 | Input Resistance                                                                           | Common Mode<br>Differential Mode                                                                                       |   |                      | 700<br>4.5                   |                          | k<br>k                           |

| C <sub>IN</sub>                 | Input Capacitance                                                                          | Differential                                                                                                           |   |                      | 2                            |                          | pF                               |

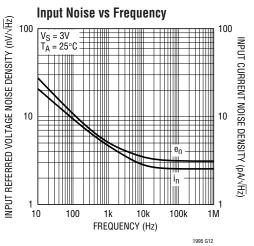

| e <sub>n</sub>                  | Differential Input Referred Noise Voltage<br>Density                                       | f = 50kHz                                                                                                              |   |                      | 3                            |                          | nV/√Hz                           |

| i <sub>n</sub>                  | Input Noise Current Density                                                                | f = 50kHz                                                                                                              |   |                      | 2.5                          |                          | pA/√Hz                           |

| e <sub>nVOCM</sub>              | Input Referred Common Mode Output<br>Noise Voltage Density                                 | f = 50kHz, V <sub>OCM</sub> Shorted to Ground                                                                          |   |                      | 15                           |                          | nV/√Hz                           |

| V <sub>ICMR</sub><br>(Note 7)   | Input Signal Common Mode Range                                                             | $V_S = 3V$<br>$V_S = \pm 5V$                                                                                           | • | 0<br>-5              |                              | 1.75<br>3.75             | V                                |

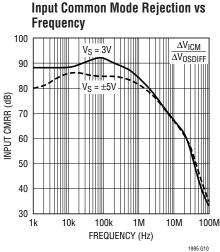

| CMRRI<br>(Note 8)               | Input Common Mode Rejection Ratio (Input Referred) V <sub>ICM</sub> / V <sub>OSDIFF</sub>  | $V_S = 3V$ , $V_{ICM} = 0.75V$                                                                                         | • | 55                   | 85                           |                          | dB                               |

| CMRRIO<br>(Note 8)              | Output Common Mode Rejection Ratio (Input Referred) V <sub>OCM</sub> / V <sub>OSDIFF</sub> | $V_S = 5V$ , $V_{OCM} = 2V$                                                                                            | • | 65                   | 85                           |                          | dB                               |

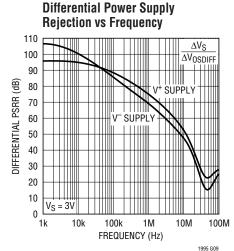

| PSRR<br>(Note 9)                | Differential Power Supply Rejection ( V <sub>S</sub> / V <sub>OSDIFF</sub> )               | $V_S = 3V \text{ to } \pm 5V$                                                                                          | • | 69                   | 105                          |                          | dB                               |

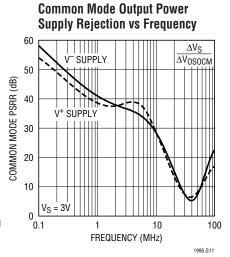

| PSRRCM<br>(Note 9)              | Output Common Mode Power Supply<br>Rejection (V <sub>S</sub> /V <sub>OSOCM</sub> )         | $V_S = 3V \text{ to } \pm 5V$                                                                                          | • | 45                   | 70                           |                          | dB                               |

| G <sub>CM</sub>                 | Common Mode Gain (ΔV <sub>OUTCM</sub> / V <sub>OCM</sub> )                                 | V <sub>S</sub> = ±2.5V                                                                                                 | • |                      | 1                            |                          | V/V                              |

|                                 | Common Mode Gain Error<br>100 • (G <sub>CM</sub> – 1)                                      | V <sub>S</sub> = ±2.5V                                                                                                 | • |                      | -0.15                        | ±1                       | %                                |

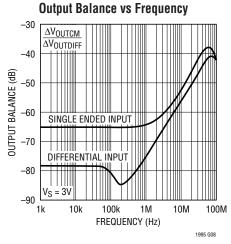

| BAL                             | Output Balance ( V <sub>OUTCM</sub> / V <sub>OUTDIFF</sub> )                               | V <sub>OUTDIFF</sub> = 2V<br>Single-Ended Input<br>Differential Input                                                  | • |                      | -65<br>-71                   | -46<br>-50               | dB<br>dB                         |

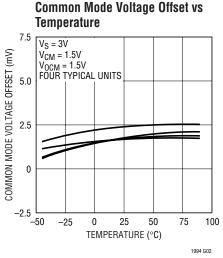

| V <sub>OSCM</sub>               | Common Mode Offset Voltage<br>(V <sub>OUTCM</sub> – V <sub>OCM</sub> )                     | $V_S = 2.375V$ , $V_{ICM} = V_S/4$<br>$V_S = 3V$<br>$V_S = 5V$<br>$V_S = \pm 5V$                                       | • |                      | ±2.5<br>±2.5<br>±2.5<br>±2.5 | ±25<br>±25<br>±30<br>±40 | mV<br>mV<br>mV                   |

| V <sub>OSCM</sub> / T           | Common Mode Offset Voltage Drift                                                           | $V_S = 2.375V, V_{ICM} = V_S/4$<br>$V_S = 3V$<br>$V_S = 5V$<br>$V_S = \pm 5V$                                          |   |                      | 5<br>5<br>5<br>5             |                          | μV/°C<br>μV/°C<br>μV/°C<br>μV/°C |

| V <sub>OUTCMR</sub><br>(Note 7) | Output Signal Common Mode Range<br>(Voltage Range for the V <sub>OCM</sub> Pin)            | V <sub>S</sub> = 3V, ±5V                                                                                               | • | V <sup>-</sup> + 1.1 |                              | V <sup>+</sup> – 0.8     | V                                |

| R <sub>INVOCM</sub>             | Input Resistance, V <sub>OCM</sub> Pin                                                     |                                                                                                                        | • | 30                   | 40                           | 60                       | k                                |

| $V_{MID}$                       | Voltage at the V <sub>OCM</sub> Pin                                                        | V <sub>S</sub> = 5V                                                                                                    | • | 2.45                 | 2.5                          | 2.55                     | V                                |

| V <sub>OUT</sub>                | Output Voltage, High, Either Output Pin<br>(Note 10)                                       | V <sub>S</sub> = 3V, No Load<br>V <sub>S</sub> = 3V, R <sub>L</sub> = 800<br>V <sub>S</sub> = 3V, R <sub>L</sub> = 100 | • |                      | 70<br>90<br>200              | 140<br>175<br>400        | mV<br>mV<br>mV                   |

|                                 |                                                                                            | $V_S = \pm 5V$ , No Load<br>$V_S = \pm 5V$ , $R_L = 800$<br>$V_S = \pm 5V$ , $R_L = 100$                               | • |                      | 150<br>200<br>900            | 325<br>450<br>2400       | mV<br>mV<br>mV                   |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 3V$ ,  $V^- = 0V$ ,  $V_{CM} = V_{OCM} = V_{ICM} = \text{mid-supply}$ ,  $V_{\overline{SHDNBAR}} = 0PEN$ ,  $R_1 = R_F = 499$ ,  $R_L = 800$  to a mid-supply voltage (See Figure 1) unless otherwise noted.  $V_S$  is defined ( $V^+ - V^-$ ).  $V_{OUTCM}$  is defined as ( $V_{IN}^+ + V_{IN}^-$ )/2.  $V_{OUTDIFF}$  is defined as ( $V_{OUT}^+ - V_{OUT}^-$ ).  $V_{INDIFF}$  is defined as ( $V_{IN}^+ - V_{IN}^-$ ).

| SYMBOL            | PARAMETER                                                    | CONDITIONS                                                                                                                                                                                                                                                           |   | MIN                      | TYP                       | MAX                  | UNITS                    |

|-------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------|---------------------------|----------------------|--------------------------|

|                   | Output Voltage, Low, Either Output Pin (Note 10)             | $V_S = 3V$ , No Load $V_S = 3V$ , $R_L = 800$ $V_S = 3V$ , $R_L = 100$                                                                                                                                                                                               | • |                          | 30<br>50<br>125           | 70<br>90<br>250      | mV<br>mV<br>mV           |

|                   |                                                              | $V_S = \pm 5V$ , No Load $V_S = \pm 5V$ , $R_L = 800$ $V_S = \pm 5V$ , $R_L = 100$                                                                                                                                                                                   | • |                          | 80<br>125<br>900          | 180<br>250<br>2400   | mV<br>mV<br>mV           |

| I <sub>SC</sub>   | Output Short-Circuit Current, Either<br>Output Pin (Note 11) | $\begin{split} V_S &= 2.375 V,  R_L = 10 \\ V_S &= 3 V,  R_L = 10 \\ V_S &= 5 V,  R_L = 10 \\ V_S &= \pm 5 V,  V_{CM} = 0 V,  R_L = 10 \end{split}$                                                                                                                  | • | ±25<br>±30<br>±40<br>±45 | ±35<br>±40<br>±65<br>±85  |                      | mA<br>mA<br>mA           |

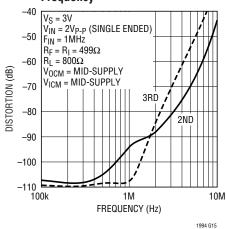

| SR                | Slew Rate                                                    | $V_S = 5V$<br>$V_S = \pm 5V$ , $V_{CM} = 0V$                                                                                                                                                                                                                         | • | 50<br>50                 | 65<br>65                  | 85<br>85             | V/µS                     |

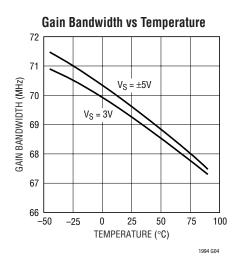

| GBW               | Gain-Bandwidth Product<br>(f <sub>TEST</sub> = 1MHz)         | V <sub>S</sub> = 3V, T <sub>A</sub> = 25°C<br>V <sub>S</sub> = ±5V, V <sub>CM</sub> = 0V, T <sub>A</sub> = 25°C                                                                                                                                                      | • | 58<br>58                 | 70<br>70                  |                      | MHz                      |

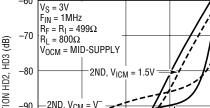

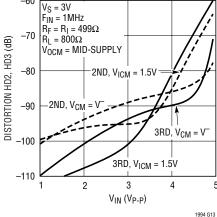

|                   | Distortion                                                   | V <sub>S</sub> = 3V, R <sub>L</sub> = 800 , f <sub>IN</sub> = 1MHz,<br>V <sub>OUT</sub> <sup>+</sup> - V <sub>OUT</sub> <sup>-</sup> = 2V <sub>P-P</sub><br>Differential Input<br>2nd Harmonic<br>3rd Harmonic<br>Single-Ended Input<br>2nd Harmonic<br>3rd Harmonic |   |                          | -99<br>-96<br>-94<br>-108 |                      | dBc<br>dBc<br>dBc<br>dBc |

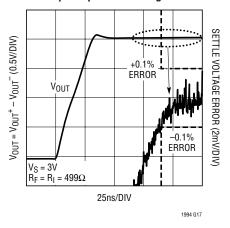

| $\overline{t_S}$  | Settling Time                                                | V <sub>S</sub> = 3V, 0.01%, 2V Step<br>V <sub>S</sub> = 3V, 0.1%, 2V Step                                                                                                                                                                                            |   |                          | 120<br>90                 |                      | ns<br>ns                 |

| A <sub>VOL</sub>  | Large-Signal Voltage Gain                                    | V <sub>S</sub> = 3V                                                                                                                                                                                                                                                  |   |                          | 100                       |                      | dB                       |

| $V_S$             | Supply Voltage Range                                         |                                                                                                                                                                                                                                                                      | • | 2.375                    |                           | 12.6                 | V                        |

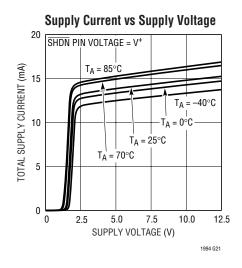

| I <sub>S</sub>    | Supply Current                                               | $V_S = 3V$ $V_S = 5V$ $V_S = \pm 5V$                                                                                                                                                                                                                                 | • |                          | 13.3<br>13.9<br>14.8      | 18.5<br>19.5<br>20.5 | mA<br>mA<br>mA           |

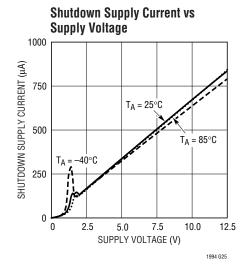

| I <sub>SHDN</sub> | Supply Current in Shutdown                                   | $V_S = 3V$<br>$V_S = 5V$<br>$V_S = \pm 5V$                                                                                                                                                                                                                           | • |                          | 0.225<br>0.375<br>0.7     | 0.8<br>1.75<br>2.5   | mA<br>mA<br>mA           |

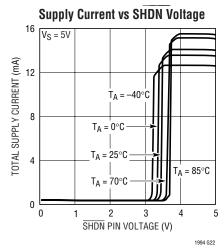

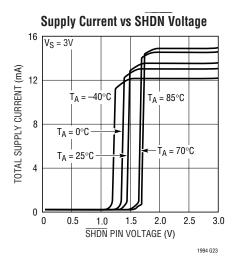

| $V_{IL}$          | SHDN Input Logic Low                                         | $V_S = 2.375V \text{ to } \pm 5V$                                                                                                                                                                                                                                    | • |                          |                           | V <sup>+</sup> – 2.1 | V                        |

| $V_{IH}$          | SHDN Input Logic High                                        | V <sub>S</sub> = 2.375V to ±5V                                                                                                                                                                                                                                       | • | V+ - 0.6                 |                           |                      | V                        |

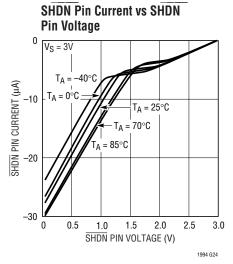

| R <sub>SHDN</sub> | SHDN Pull-Up Resistor                                        | V <sub>S</sub> = 2.375V to ±5V                                                                                                                                                                                                                                       |   | 40                       | 55                        | 75                   | k                        |

| t <sub>ON</sub>   | Turn-On Time                                                 | V <sub>SHDN</sub> 0.5V to 3V                                                                                                                                                                                                                                         |   |                          | 1                         |                      | μs                       |

| t <sub>OFF</sub>  | Turn-Off Time                                                | V <sub>SHDN</sub> 3V to 0.5V                                                                                                                                                                                                                                         |   |                          | 1                         |                      | μs                       |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The inputs are protected by a pair of back-to-back diodes. If the differential input voltage exceeds 1V, the input current should be limited to less than 10mA.

**Note 3:** A heat sink may be required to keep the junction temperature below the absolute maximum rating when the output is shorted indefinitely.

**Note 4:** The LT1994C/LT1994I are guaranteed functional over the operating temperature range –40°C to 85°C.

**Note 5:** The LT1994C is guaranteed to meet specified performance from 0°C to 70°C. The LT1994C is designed, characterized, and expected to meet specified performance from –40°C to 85°C but is not tested or QA sampled at these temperatures. The LT1994I is guaranteed to meet specified performance from –40°C to 85°C.

**Note 6:** Input bias current is defined as the average of the input currents flowing into Pin 1 and Pin 8 (IN $^-$  and IN $^+$ ). Input Offset current is defined as the difference of the input currents flowing into Pin 8 and Pin 1 ( $I_{OS} = I_B^+ - I_B^-$ ).

LINEAR

### **ELECTRICAL CHARACTERISTICS**

Note 7: Input Common Mode Range is tested using the Test Circuit of Figure 1 ( $R_F=R_I$ ) by applying a single ended  $2V_{P-P}$ , 1kHz signal to  $V_{INP}$  ( $V_{INM}=0$ ), and measuring the output distortion (THD) at the common mode Voltage Range limits listed in the Electrical Characteristics table, and confirming the output THD is better than -40 dBc. The voltage range for the output common mode range (Pin 2) is tested using the Test Circuit of Figure 1 ( $R_F=R_I$ ) by applying a 0.5V peak, 1kHz signal to the  $V_{OCM}$  Pin 2 (with  $V_{INP}=V_{INM}=0$ ) and measuring the output distortion (THD) at  $V_{OUTCM}$  with  $V_{OCM}$  biased 0.5V from the  $V_{OCM}$  pin range limits listed in the Electrical Characteristics Table, and confirming the THD is better than -40 dB

**Note 8:** Input CMRR is defined as the ratio of the change in the input common mode voltage at the pins IN<sup>+</sup> or IN<sup>-</sup> to the change in differential

input referred voltage offset. Output CMRR is defined as the ratio of the change in the voltage at the  $V_{\text{OCM}}$  pin to the change in differential input referred voltage offset.

**Note 9:** Differential Power Supply Rejection (PSRR) is defined as the ratio of the change in supply voltage to the change in differential input referred voltage offset. Common Mode Power Supply Rejection (PSRRCM) is defined as the ratio of the change in supply voltage to the change in the common mode offset,  $V_{OUTCM} - V_{OCM}$ .

**Note 10:** Output swings are measured as differences between the output and the respective power supply rail.

**Note 11:** Extended operation with the output shorted may cause junction temperatures to exceed the 150°C limit for the MSOP package (or 125°C for the DD package) and is not recommended.

### TYPICAL PERFORMANCE CHARACTERISTICS

### TYPICAL PERFORMANCE CHARACTERISTICS

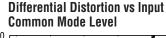

Differential Distortion vs Input

Amplitude (Single Ended Input)

### TYPICAL PERFORMANCE CHARACTERISTICS

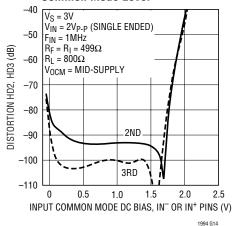

#### Differential Distortion vs Frequency

#### Slew Rate vs Temperature

#### 2V Step Response Settling

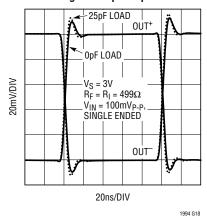

#### **Small Signal Step Response**

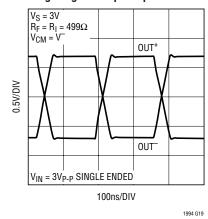

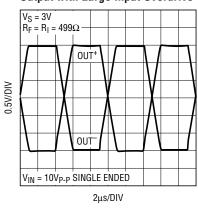

#### Large Signal Step Response

#### **Output with Large Input Overdrive**

1994 G20

# TYPICAL PERFORMANCE CHARACTERISTICS

### PIN FUNCTIONS

**IN+**, **IN-** (**Pins 1, 8**): Non-Inverting and Inverting Input Pins of the Amplifier, respectively. For best performance, it is highly recommended that stray capacitance be kept to an absolute minimum by keeping printed circuit connections as short as possible, and if necessary, stripping back nearby surrounding ground plane away from these pins.

$V_{OCM}$  (Pin 2): Output Common Mode Reference Voltage. The  $V_{OCM}$  pin is the midpoint of an internal resistive voltage divider between the supplies, developing a (default) mid-supply voltage potential to maximize output signal swing.  $V_{OCM}$  has a Thevenin equivalent resistance of approximately 40k and can be overdriven by an external voltage reference. The voltage on  $V_{OCM}$  sets the output common mode voltage level (which is defined as the average of the voltages on the OUT+ and OUT− pins).  $V_{OCM}$  should be bypassed with a high quality ceramic bypass capacitor of at least 0.1μF (unless connected directly to a low impedance, low noise ground plane) to minimize common mode noise from being converted to differential noise by impedance mismatches both externally and internally to the IC.

V<sup>+</sup>, V<sup>-</sup> (Pins 3, 6): Power Supply Pins. For single supply applications (pin 6 grounded) it is recommended that

high quality  $1\mu F$  and  $0.1\mu F$  ceramic bypass capacitors be placed from the positive supply pin (Pin 3) to the negative supply pin (Pin 6) with minimal routing. Pin 6 should be directly tied to a low impedance ground plane. For dual power supplies, it is recommended that high quality,  $0.1\mu F$  ceramic capacitors are used to bypass Pin 3 to ground and Pin 6 to ground. It is also highly recommended that high quality  $1\mu F$  and  $0.1\mu F$  ceramic bypass capacitors be placed across the power supply pins (Pins 3 and 6) with minimal routing.

**OUT+**, **OUT-** (**Pins 4, 5**): Output Pins. Each pin can drive approximately 100 to ground with a short circuit current limit of up to ±85mA. Each amplifier output is designed to drive a load capacitance of 25pF. This basically means the amplifier can drive 25pF from each output to ground or 12.5pF differentially. Larger capacitive loads should be decoupled with at least 25 resistors from each output.

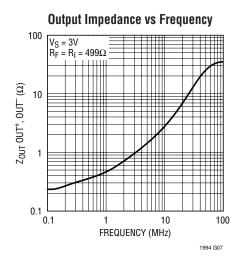

SHDN (Pin 7): When Pin 7 (SHDN) is floating or when Pin 7 is directly tied to V+, the LT1994 is in the normal operating mode. When Pin 7 is pulled a minimum of 2.1V below V+, the LT1994 enters into a low power shutdown state. Refer to the SHDN pin section under Applications Information for description of the LT1994 output impedance in the shutdown state.

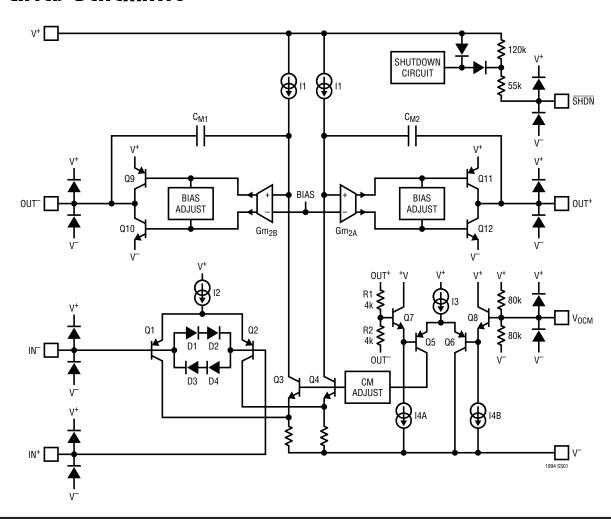

#### **Functional Description**

The LT1994 is a small outline, wide band, low noise, and low distortion fully-differential amplifier with accurate output phase balancing. The LT1994 is optimized to drive low voltage, single-supply, differential input analog-to-digital converters (ADCs). The LT1994's output is capable of swinging rail-to-rail on supplies as low as 2.5V, which makes the amplifier ideal for converting ground referenced, single-ended signals into V<sub>OCM</sub> referenced differential signals in preparation for driving low voltage, single-supply, differential input ADCs. Unlike traditional op amps which have a single output, the LT1994 has two outputs to process signals differentially. This allows for two times the signal swing in low voltage systems when compared to single-ended output amplifiers. The balanced differential nature of the amplifier also provides even-order harmonic distortion cancellation, and less susceptability to common mode noise (like power supply noise). The LT1994 can be used as a single ended input to differential output amplifier, or as a differential input to differential output amplifier.

The LT1994's output common mode voltage, defined as the average of the two output voltages, is independent of the input common mode voltage, and is adjusted by applying a voltage on the V<sub>OCM</sub> pin. If the pin is left open, there is an internal resistive voltage divider, which develops a potential halfway between the V<sup>+</sup> and V<sup>-</sup> pins. The V<sub>OCM</sub> pin will have an equivalent Thevenin equivalent resistance of 40k , and a Thevenin equivalent voltage of half-supply. Whenever this pin is not hard tied to a low impedance ground plane, it is recommended that a high quality ceramic cap is used to bypass the  $V_{OCM}$  pin to a low impedance ground plane (see Layout Considerations in this document). The LT1994's internal common mode feedback path forces accurate output phase balancing to reduce even order harmonics, and centers each individual output about the potential set by the V<sub>OCM</sub> pin.

$$V_{OUTCM} = V_{OCM} = \frac{V_{OUT}^+ + V_{OUT}^-}{2}$$

The outputs (OUT<sup>+</sup> and OUT<sup>-</sup>) of the LT1994 are capable of swinging rail-to-rail. They can source or sink up to approximately 85mA of current. Each output is rated to

drive approximately 25pF to ground (12.5pF differentially). Higher load capacitances should be decoupled with at least 25 of series resistance from each output.

#### **Input Pin Protection**

The LT1994's input stage protected against differential input voltages that exceed 1.4V by two pairs of back to back diodes that protect against emitter base breakdown of the input transistors. In addition, the input pins have steering diodes to either power supply. If the input pair is over-driven, the current should be limited to under 10mA to prevent damage to the IC. The LT1994 also has steering diodes to either power supply on the V<sub>OCM</sub>, and SHDN pins (Pins 2 and 7) and if exposed to voltages that exceed either supply, they too should be current limited to under 10mA.

#### **SHDN** Pin

If the SHDN pin (Pin 7) is pulled 2.1V below the positive supply, an internal current is generated that is used to power down the LT1994. The pin will have the Thevenin equivalent impedance of approximately 55k to V<sup>+</sup>. If the pin is left unconnected, an internal pull-up resistor of 120k will keep the part in normal active operation. Care should be taken to control leakage currents at this pin to under 1µA to prevent leakage currents from inadvertently putting the LT1994 into shutdown. In shutdown, all biasing current sources are shut off, and the output pins OUT+ and OUT will each appear as open collectors with a nonlinear capacitor in parallel, and steering diodes to either supply. Because of the non-linear capacitance, the outputs still have the ability to sink and source small amounts of transient current if exposed to significant voltage transients. The inputs (IN<sup>+</sup>, and IN<sup>-</sup>) have anti-parallel diodes that can conduct if voltage transients at the input exceed 1V. The inputs also have steering diodes to either supply. The turn-on and turn-off time between the shutdown and active states are on the order of 1µs but depends on the circuit configuration.

#### **General Amplifier Applications**

As levels of integration have increased and, correspondingly, system supply voltages decreased, there has been

LINEAR

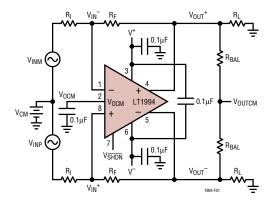

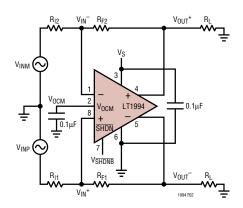

a need for ADCs to process signals differentially in order to maintain good signal to noise ratios. These ADCs are typically supplied from a single supply voltage that can be as low as 2.5V and will have an optimal common mode input range near mid-supply. The LT1994 makes interfacing to these ADCs trivial, by providing both single ended to differential conversion as well as common mode level shifting. Figure 1 shows a general single supply application with perfectly matched feedback networks from OUT $^+$  and OUT $^-$ . The gain to  $V_{OUTDIFF}$  from  $V_{INM}$  and  $V_{INP}$  is:

$$V_{OUTDIFF} = {V_{OUT}}^+ - {V_{OUT}}^- \approx \frac{R_F}{R_I} \bullet \left( V_{INP} - V_{INM} \right)$$

Note from the above equation that the differential output voltage ( $V_{OUT}^+ - V_{OUT}^-$ ) is completely independent of input and output common mode voltages, or the voltage at the common mode pin. This makes the LT1994 ideally suited pre-amplification, level shifting, and conversion of single ended signals to differential output signals in preparation for driving differential input ADCs.

#### **Effects of Resistor Pair Mismatch**

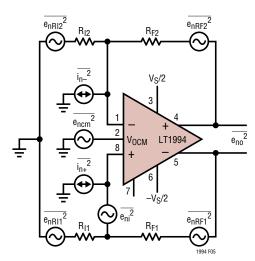

Figure 2 shows a circuit diagram that takes into consideration that real world resistors will not perfectly match. Assuming infinite open loop gain, the differential output relationship is given by the equation:

$$\begin{split} &V_{OUTDIFF} = {V_{OUT}}^+ - {V_{OUT}}^- \cong \frac{R_F}{R_I} \bullet V_{INDIFF} + \\ &\frac{\Delta \beta}{\beta_{AVG}} \bullet V_{ICM} - \frac{\Delta \beta}{\beta_{AVG}} \bullet V_{OCM}, \end{split}$$

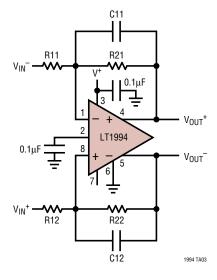

Figure 1. Test Circuit

where:  $R_F$  is the average of  $R_{F1}$  and  $R_{F2}$ , and  $R_I$  is the average of  $R_{I1}$  and  $R_{I2}$ .

$\beta_{AVG}$  is defined as the average feedback factor (or gain) from the outputs to their respective inputs:

$$\beta_{AVG} = \frac{1}{2} \bullet \left( \frac{R_{I2}}{R_{I2} + R_{F2}} + \frac{R_{I1}}{R_{I1} + R_{F1}} \right)$$

$\beta$  is defined as the difference in feedback factors:

$$\Delta \beta = \frac{R_{l2}}{R_{l2} + R_{F2}} - \frac{R_{l1}}{R_{l1} + R_{F1}}$$

$V_{ICM}$  is defined as the average of the two input voltages,  $V_{INP}$  and  $V_{INM}$  (also called the input common mode voltage):

$$V_{ICM} = \frac{1}{2} \bullet (V_{INP} + V_{INM})$$

and  $V_{\mbox{\scriptsize INDIFF}}$  is defined as the difference of the input voltages:

$$V_{\mathsf{INDIFF}} = V_{\mathsf{INP}} - V_{\mathsf{INM}}$$

When the feedback ratios mismatch ( $\beta$ ), common mode to differential conversion occurs.

Setting the differential input to zero ( $V_{INDIFF} = 0$ ), the degree of common mode to differential conversion is given

Figure 2. Real-World Application

by the equation:

$$\begin{aligned} & V_{OUTDIFF} = V_{OUT}^{}^{+} - V_{OUT}^{}^{-} \approx \\ & \left(V_{ICM} - V_{OCM}\right) \bullet \frac{\Delta \beta}{\beta_{AVG}} \\ & V_{INDIFF} = 0 \end{aligned}$$

In general, the degree of feedback pair mismatch is a source of common mode to differential conversion of both signals and noise. Using 1% resistors or better will provide about 28dB of common mode rejection. Using 0.1% resistors will provide about 48dB of common mode rejection. A low impedance ground plane should be used as a reference for both the input signal source and the  $V_{OCM}$  pin. A direct short of  $V_{OCM}$  to this ground plane or bypassing the  $V_{OCM}$  with a high quality  $0.1\mu F$  ceramic capacitor to this ground plane will further mitigate against common mode signals from being converted to differential.

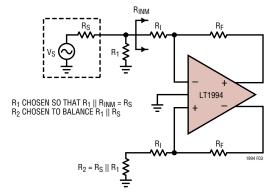

#### **Input Impedance and Loading Effects**

The input impedance looking into the  $V_{INP}$  or  $V_{INM}$  input of Figure 1 depends on whether or not the sources  $V_{INP}$  and  $V_{INM}$  are fully differential. For balanced input sources  $(V_{INP} = -V_{INM})$ , the input impedance seen at either input is simply:

$$R_{INP} = R_{INM} = R_{I}$$

For single ended inputs, because of the signal imbalance at the input, the input impedance actually increases over the balanced differential case. The input impedance looking into either input is:

$$R_{INP} = R_{INM} = \frac{R_I}{\left(1 - \frac{1}{2} \cdot \left\lceil \frac{R_F}{R_I + R_F} \right\rceil \right)}$$

Input signal sources with non-zero output impedances can also cause feedback imbalance between the pair of feedback networks. For the best performance, it is recommended that the source's output impedance be compensated for. If input impedance matching is required by the source,

R<sub>1</sub> should be chosen (see Figure 3):

$$R_1 = \frac{R_{INM} \cdot R_S}{R_{INM} - R_S}$$

According to Figure 3, the input impedance looking into the differential amp ( $R_{INM}$ ) reflects the single ended source case, thus:

$$R_{INM} = \frac{R_I}{\left(1 - \frac{1}{2} \bullet \left[\frac{R_F}{R_I + R_F}\right]\right)}$$

$R_2$  is chosen to balance  $R_1 \parallel R_S$ :

$$R_2 = \frac{R_1 \cdot R_S}{R_1 + R_S}$$

#### Input Common Mode Voltage Range

The LT1994's input common mode voltage ( $V_{ICM}$ ) is defined as the average of the two input voltages,  $V_{IN}^+$ , and  $V_{IN}^-$ . It extends from V<sup>-</sup> to approximately 1.25V below V<sup>+</sup>. The input common mode range depends on the circuit configuration (gain),  $V_{OCM}$  and  $V_{CM}$  (refer to Figure 4). For fully differential input applications, where  $V_{INP} = -V_{INM}$ , the common mode input is approximately:

$$\begin{split} V_{ICM} &= \frac{{V_{IN}}^{+} + {V_{IN}}^{-}}{2} \approx V_{OCM} \bullet \left(\frac{R_{I}}{R_{I} + R_{F}}\right) + \\ V_{CM} \bullet \left(\frac{R_{F}}{R_{F} + R_{I}}\right) \end{split}$$

Figure 3. Optimal Compensation for Signal Source Impedance

1994

Figure 4. Circuit for Common Mode Range

With singled ended inputs, there is an input signal component to the input common mode voltage. Applying only  $V_{INP}$  (setting  $V_{INM}$  to zero), the input common voltage is approximately:

$$\begin{split} &V_{ICM} = \frac{{V_{IN}}^{+} + {V_{IN}}^{-}}{2} \approx V_{OCM} \bullet \left(\frac{R_I}{R_I + R_F}\right) + \\ &V_{CM} \bullet \left(\frac{R_F}{R_F + R_I}\right) + \frac{V_{INP}}{2} \bullet \left(\frac{R_F}{R_F + R_I}\right) \end{split}$$

#### **Output Common Mode Voltage Range**

The output common mode voltage is defined as the average of the two outputs:

$$V_{OUTCM} = V_{OCM} = \frac{V_{OUT}^+ + V_{OUT}^-}{2}$$

The  $V_{OCM}$  sets this average by an internal common mode feedback loop which internally forces  $V_{OUT}^+ = -V_{OUT}^-$ . The output common mode range extends from approximately 1.1V above  $V^-$  to approximately 0.8V below  $V^+$ . The  $V_{OCM}$  pin sits in the middle of an 80k to 80k voltage divider that sets the default mid-supply open circuit potential.

In single supply applications, where the LT1994 is used to interface to an ADC, the optimal common mode input range to the ADC is often determined by the ADC's reference. If the ADC makes a reference available for setting

the input common mode voltage, it can be directly tied to the  $V_{OCM}$  pin, but must be capable of driving a 40k equivalent resistance that is tied to a mid-supply potential. If an external reference drives the  $V_{OCM}$  pin, it should still be bypassed with a high quality  $0.1\mu F$  capacitor to a low impedance ground plane to filter any thermal noise and to prevent common mode signals on this pin from being inadvertently converted to differential signals.

#### **Noise Considerations**

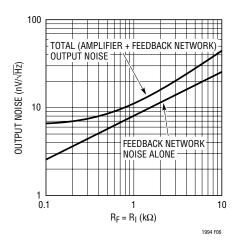

The LT1994's input referred voltage noise is on the order of  $3nV/\sqrt{Hz}$ . Its input referred current noise is on the order of  $2.5pA/\sqrt{Hz}$ . In addition to the noise generated by the amplifier, the surrounding feedback resistors also contribute noise. The output noise generated by both the amplifier and the feedback components is given by the equation:

$$e_{no} = \sqrt{\frac{\left(e_{ni} \bullet \left[1 + \frac{R_F}{R_I}\right]\right)^2 + 2 \bullet \left(I_n \bullet R_F\right)^2 + 2 \bullet \left(e_{nRI} \bullet \left[\frac{R_F}{R_I}\right]\right)^2 + 2 \bullet e_{nRF}^2}}$$

A plot of this equation and a plot of the noise generated by the feedback components are shown in Figure 6.

The LT1994's input referred voltage noise contributes the equivalent noise of a 560 resistor. When the feedback

Figure 5. Noise Analysis

network is comprised of resistors whose values are less than this, the LT1994's output noise is voltage noise dominant (See Figure 6):

$$e_{no} \approx e_{ni} \cdot \left(1 + \frac{R_F}{R_I}\right)$$

Feedback networks consisting of resistors with values greater than about 10k will result in output noise which is amplifier current noise dominant.

$$e_{no} \approx \sqrt{2} \cdot I_n \cdot R_F$$

Lower resistor values always result in lower noise at the penalty of increased distortion due to increased loading of the feedback network on the output. Higher resistor values will result in higher output noise, but improved distortion due to less loading on the output.

Figure 6. LT1994 Output Spot Noise vs Spot Noise Contributed by Feedback Network Alone

Figure 6 shows the noise voltage that will appear differentially between the outputs. The common mode output noise voltage does not add to this differential noise. For optimum noise and distortion performance, use a differential output configuration.

#### **Power Dissipation Considerations**

The LT1994 is housed in either an 8-lead MSOP package  $(\theta_{JA} = 140$ °C/W or an 8-lead DD package  $(\theta_{JA} = 160$ °C/ W). The LT1994 combines high speed and large output current with a small die and small package so there is a need to be sure the die temperature does not exceed 150°C if housed in the 8-lead MSOP package, and 125°C if housed in the 8-lead DD package. In the 8-lead MSOP, LT1994 has its V<sup>-</sup> lead fused to the frame so it is possible to lower the package thermal impedance by connecting the V<sup>-</sup> pin to a large ground plane or metal trace. Metal trace and plated through holes can be used to spread the heat generated by the device to the backside of the PC board. For example, an 8-lead MSOP on a 3/32" FR-4 board with 540mm<sup>2</sup> of 2oz. copper on both sides of the PC board tied to the V $^-$  pin can drop the  $\theta_{JA}$  from 140°C/W to 110°C/W (see Table 1).

The underside of the DD package has exposed metal (4mm²) from the lead frame where the die is attached. This provides for the direct transfer of heat from the die junction to the printed circuit board to help control the maximum operating junction temperature. The dual-inline pin arrangement allows for extended metal beyond the ends of the package on the topside (component side) of a circuit board. Table 1 summarizes for both the MSOP and DD packages, the thermal resistance from the die junction to ambient that can be obtained using various amounts of topside, and backside metal (2oz. copper). On multilayer boards, further reductions can be obtained using additional metal on inner PCB layers connected through vias beneath the package.

In general, the die temperature can be estimated from the ambient temperature  $T_A$ , and the device power dissipation  $P_D$ :

$$T_J = T_A^+ + P_D \bullet \theta_{JA}$$

The power dissipation in the IC is a function of the supply voltage, the output voltage, and the load resistance. For fully differential output amplifiers at a given supply voltage ( $\pm V_{CC}$ ), and a given differential load ( $R_{LOAD}$ ), the worst-case power dissipation  $P_{D(MAX)}$  occurs at the worst case quiescent current ( $I_{Q(MAX)} = 20.5$ mA) and when the load current is given by the expression:

$$I_{LOAD} = \frac{V_{CC}}{R_{LOAD}}$$

The worst case power dissipation in the LT1994 at

$$I_{LOAD} = \frac{V_{CC}}{R_{LOAD}}$$

is:

$$P_{D(MAX)} = 2 \cdot V_{CC} \cdot \left(I_{LOAD} + I_{Q(MAX)}\right) - I_{LOAD}^{2} \cdot$$

$$R_{LOAD} = \frac{V_{CC}^2}{R_{LOAD}} + 2 \bullet V_{CC} \bullet I_{Q(MAX)}$$

Example: A LT1994 is mounted on a circuit board in a MSOP-8 package ( $\theta_{JA} = 140^{\circ}\text{C/W}$ ), and is running off of  $\pm 5\text{V}$  supplies driving an equivalent load (external load plus feedback network) of 75 . The worst-case power that would be dissipated in the device occurs when:

$$P_{D(MAX)} = \frac{V_{CC}^2}{R_{I,OAD}} + 2 \bullet V_{CC} \bullet I_{Q(MAX)} =$$

$$\frac{5V^2}{75\Omega}$$

+ 2 • 5V • 17.5MA = 0.54W

The maximum ambient temperature the 8-lead MSOP is allowed to operate under these conditions is:

$$T_A = T_{JMAX} - P_D \bullet \theta_{JA} = 150^{\circ}C - (0.54W) \bullet (140^{\circ}C/W) = 75^{\circ}C$$

To operate the device at higher ambient temperature, connect more copper to the V $^-$  pin to reduce the thermal resistance of the package as indicated in Table 1. Note that  $T_{JMAX}$  for the 8-lead DD package is 125°C (as opposed to 150°C for the 8-lead MSOP), and the data for the equation above should be altered accordingly.

Table 1. LT1994 MSOP and DD Package Thermal Resistivity

| LT1994 8-LEA                    | D MSOP PACK                      | LT1994 8-LEAD DD PACKAGE                          |                                              |                                                   |  |

|---------------------------------|----------------------------------|---------------------------------------------------|----------------------------------------------|---------------------------------------------------|--|

| Copper Area<br>Topside<br>(mm²) | Copper Area<br>Backside<br>(mm²) | Thermal<br>Resistance<br>(Junction to<br>Ambient) | Copper Area<br>Topside<br>(mm <sup>2</sup> ) | Thermal<br>Resistance<br>(Junction to<br>Ambient) |  |

| 0                               | 0                                | 140                                               | 4                                            | 160                                               |  |

| 30                              | 0                                | 135                                               | 16                                           | 135                                               |  |

| 100                             | 0                                | 130                                               | 32                                           | 110                                               |  |

| 100                             | 100                              | 120                                               | 64                                           | 95                                                |  |

| 540                             | 540                              | 110                                               | 130                                          | 70                                                |  |

#### **Layout Considerations**

Because the LT1994 is a high speed amplifier, it is sensitive to both stray capacitance and stray inductance. Components connected to the LT1994 should be connected with as short and direct connections as possible. A low noise, low impedance ground plane is critical for the highest performance. In single supply applications, high quality surface mount  $1\mu F$  and  $0.1\mu F$  ceramic bypass capacitors with minimum PCB trace should be used directly across the power supplies V+ to V^-. In split supply applications, high quality surface mount  $1\mu F$  and  $0.1\mu F$  ceramic bypass capacitors should be placed across the power supplies V+ to V^-, and individual high quality surface mount  $0.1\mu F$  bypass caps should be used from each supply to ground with direct (short) connections.

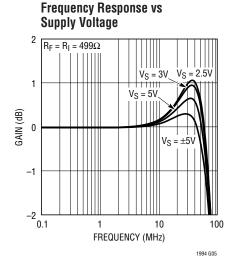

Any stray parasitic capacitance to ground at the summing junctions, IN+ and IN- should be kept to an absolute minimum even if it means stripping back the ground plane away from any trace attached to this node. This becomes especially true when the feedback resistor network uses resistor values >500  $\,$  in circuits with  $R_F=R_I$ . Excessive peaking in the frequency response can be mitigated by adding small amounts of feedback capacitance around RF (2pF to 5pF). Always keep in mind the differential nature of the LT1994, and that it is critical that the output impedances seen by both outputs (stray or intended) should be as balanced and symmetric as possible. This will help preserve the natural balance of the LT1994, which minimizes the generation of even order harmonics, and preserves the rejection of common mode signals and noise.

It is highly recommended that the  $V_{OCM}$  pin be either hard tied to a low impedance ground plane (in split supply applications) or bypassed to ground with a high quality 0.1µF ceramic capacitor in single supply applications. This will help prevent thermal noise from the internal 80k - 80k voltage divider (25nV/ $\sqrt{\text{Hz}}$ ) and other external sources of noise from being converted to differential noise due to mismatches in the feedback networks. It is also recommended that the resistive feedback networks be comprised of 1% resistors (or better) to enhance the output common mode rejection. This will also prevent  $V_{OCM}$  input referred common mode noise of the common mode amplifier path (which cannot be filtered) from being converted to differential noise, degrading the differential noise performance.

### SIMPLIFIED SCHEMATIC

T LINEAR

### TYPICAL APPLICATIONS

#### **Differential 1st Order Lowpass Filter**

Maximum –3dB frequency (f<sub>3dB</sub>) 5MHz

Stopband attenuation: -6dB at 2 • f<sub>3dB</sub> and 14dB at 5 • f<sub>3dB</sub>

Component Calculation:

$$f_{3dB} \le 5MHz$$

and  $Gain \le \frac{5MHz}{f_{3dB}}$

Calculate an absolute value for C11 (C11<sub>abs</sub>) using a specified –3dB frequency

$$C11_{abs} = \frac{4 \cdot 10^5}{f_{3dB}} (C11_{abs} in pF and f_{3dB} in kHz)$$

- 2. Select a standard 5% capacitor value nearest the absolute value for C11

- 3. Calculate R11 and R21 using the standard 5% C11 value,  $f_{3dB}$  and desired gain

R11 and R21 equations (C11 in pF and  $f_{3dB}$  in kHz)

$$R21 = \frac{159.2 \cdot 10^{6}}{C11 \cdot f_{3dB}}$$

$$R11 = \frac{R21}{Gain}$$

Example: The specified –3dB frequency is 1MHz Gain = 4

- 1. Using  $f_{3dB} = 1000kHz$ ,  $C11_{abs} = 400pF$

- 2. Nearest standard 5% value to 400pF is 390pF and C11 = C12 = 390pF

- 3. Using  $f_{3dB} = 1000 \text{kHz}$ , C11 = 390pF and Gain = 4, R21 = R22 = 412 and R11 = R12 = 102 (nearest 1% value)

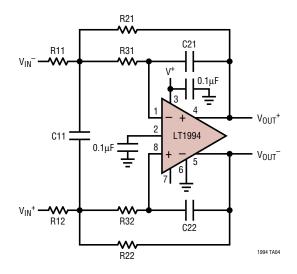

### **Differential 2nd Order Butterworth Lowpass Filter**

Maximum –3dB frequency (f<sub>3dB</sub>) 2.5MHz

Stopband attenuation: −12dB at 2 • f<sub>3dB</sub> and −28dB at 5 • f<sub>3dB</sub>

**Component Calculation:**

### TYPICAL APPLICATIONS

Calculate an absolute value for C2 (C2<sub>abs</sub>) using a specified –3dB frequency

$$C2_{abs} = \frac{4 \cdot 10^5}{f_{3dB}} (C2_{abs} in pF and f_{3dB} in kHz) (Note 2)$$

- 2. Select a standard 5% capacitor value nearest the absolute value for C2 (C1 = 10 C2)

- 3. Calculate R3, R2 and R1 using the standard 5% C2 value, the specified  $f_{3dB}$  and the specified passband gain (Gn)

$$f_{3dB} \le 2.5 MHz$$

and  $Gain \le 8.8$  or  $Gain \le \frac{2.5 MHz}{f_{3dB}}$

R1, R2 and R3 equations (C2 in pF and f<sub>3dB</sub> in kHz)

R3=

$$\frac{\left(1.121-\sqrt{\left(1.131-0.127\bullet Gn\right)}\right)\bullet10^{8}}{\left(Gn+1\right)\bullet C2\bullet f_{3dB}}$$

(Note 1)

$$R2 = \frac{1.266 \cdot 10^{15}}{R3 \cdot C2^2 \cdot f_{3dB}^2}$$

$$R1 = \frac{R2}{Gn}$$

Example: The specified –3dB frequency is 1MHz Gain = 1

- 1. Using  $f_{3dB} = 1000kHz$ ,  $C2_{abs} = 400pF$

- 2. Nearest standard 5% value to 400pF is 390pF and C21 = C22 = 390pF and C11 = 3900pF

- 3. Using  $f_{3dB}=1000$ kHz, C2=390pF and Gain=1, R1=549, R2=549 and R3=15.4 (nearest 1% values). R11=R21=549, R21=R22=549 and R31=R32=15.4.

Note 1: The equations for R1, R2, R3 are ideal and do not account for the finite gain bandwidth product (GBW) of the LT1994 (70MHz). The maximum gain is set by the C1/C2 ratio (which for convenience is set equal to ten).

Note 2: The calculated value of a capacitor is chosen to produce input resistors less than 600 . If a higher value input resistance is required then multiply all resistor values and divide all capacitor values by the same number.

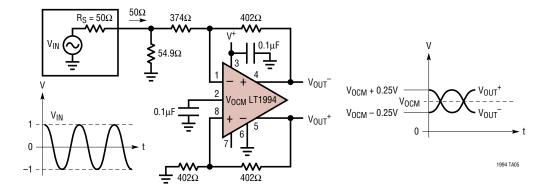

#### A Single Ended to Differential Voltage Conversion with Source Impedance Matching and Level Shifting

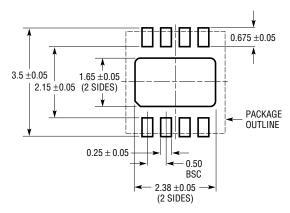

### PACKAGE DESCRIPTION

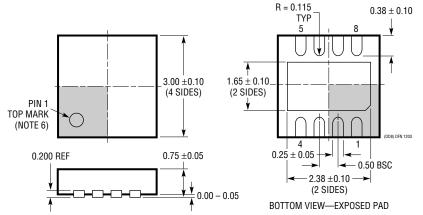

# DD Package 8-Lead Plastic DFN (3mm $\times$ 3mm)

(Reference LTC DWG # 05-08-1698)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

#### NOTE:

- 1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE MO-229 VARIATION OF (WEED-1)

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON TOP AND BOTTOM OF PACKAGE

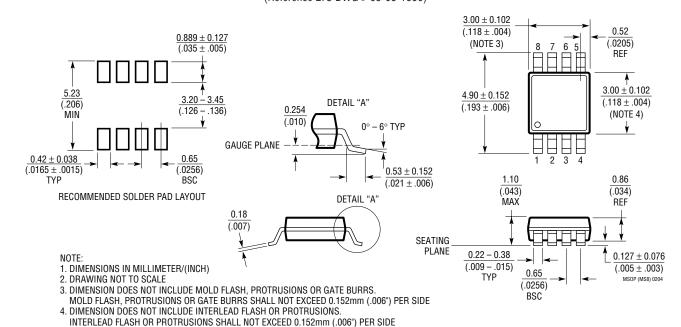

#### MS8 Package 8-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1660)

5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

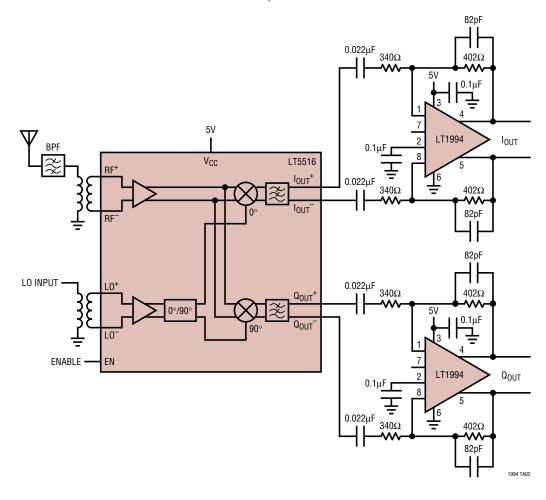

### TYPICAL APPLICATION

RFID Receiver Front-End, 20kHz < -3dB BW < 5MHz

# **RELATED PARTS**

| PART NUMBER               | DESCRIPTION                                        | COMMENTS                                            |  |

|---------------------------|----------------------------------------------------|-----------------------------------------------------|--|

| LT1167                    | Precision, Instrumentation Amp                     | Single Gain Set Resistor: G = 1 to 10,000           |  |

| LT1806/LT1807             | Single/Dual Low Distortion Rail-to-Rail Amp        | 325MHz, 140V/µs Slew Rate, 3.5nV/√Hz Noise          |  |

| LT1809/LT1810             | Single/Dual Low Distortion Rail-to-Rail Amp        | 180MHz, 350V/µs Slew Rate, Shutdown                 |  |

| LT1990                    | High Voltage Gain Selectable Differential Amp      | ±250V Common Mode, Micropower, Gain = 1, 10         |  |

| LT1991                    | Precision Gain Selectable Differential Amp         | Micropower, Pin Selectable Gain = -13 to 14         |  |

| LTC1992/LTC1992-x         | Fully Differential Input/Output Amplifiers         | Programmable Gain or Fixed Gain (G = 1, 2, 5, 10)   |  |

| LT1993-2/-4/-10           | Low Distortion and Noise, Differential In/Out      | Fixed Gain (G = 2, 4, 10)                           |  |

| LT1995                    | High Speed Gain Selectable Differential Amp        | 30MHz, 1000V/μs, Pin Selectable Gain = -7 to 8      |  |

| LT1996                    | Precision, 100μA, Gain Selectable Differential Amp | Pin Selectable Gain = 9 to 117                      |  |

| LT6600-2.5/-5/-10/-15/-20 | Differential Amp and Lowpass, Chebyshev Filter     | Filter Cutoff = 2.5MHz, 5MHz, 10MHz, 15MHz or 20MHz |  |

LT/TP 0605 500 • PRINTED IN USA

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2005