# WT6561F USB Embedded Controller with Hub (Flash Type)

Preliminary Specification v.099h

**USB Device Controller with Hub**

### **Table Of Contents**

| 1 FEATURES                                            | 7  |

|-------------------------------------------------------|----|

| GENERAL DESCRIPTION                                   | 7  |

| FEATURES                                              | 7  |

| ORDERING INFORMATION                                  | 8  |

| 2 PIN ASSIGNMENT AND PACKAGE TYPES                    | 9  |

| 2.1 Pin Description                                   | 10 |

| 2.2 Pin Configuration                                 | 13 |

| 3 FUNCTIONAL DESCRIPTION                              | 16 |

| 3.1 WT6561F USB Module                                | 16 |

| 3.2 Micro-controller                                  | 18 |

| 3.3 WT6561F Address Space Mapping                     | 19 |

| 3.3.1 WT6561F Special Function Register Address Space |    |

| 3.3.2 External Function Register Address Space        |    |

| 3.4 Clock Unit                                        | 21 |

| 3.5 Reset                                             | 22 |

| 3.6 Power-down Mode and Idle Mode                     | 23 |

| 3.7 Interrupt                                         | 24 |

| 3.8 Function Endpoint                                 | 24 |

| 3.9 Transmit FIFOs                                    | 25 |

| 3.9.1 Transmit FIFOs Features                         | 25 |

| 3.12.2 Transmit Data Set Management                   |    |

| 3.12.3 Transmit FIFO Registers                        |    |

| 3.13 Receive FIFOs                                    |    |

| 3.13.1 Receive FIFO Features                          |    |

| 3.13.2 Receive Data Set Management                    |    |

| 3.13.3 Receive FIFO Registers                         |    |

| 3.14 Setup Token Receive FIFO Handling                |    |

| 3.15 Suspend and Resume                               | 31 |

| 4 USB EXTERNAL FUNCTION REGISTERS                     |    |

**USB Device Controller with Hub**

| TARGET AC AND DC SPECIFICATION | 86                            |

|--------------------------------|-------------------------------|

| 1                              | ARGET AC AND DC SPECIFICATION |

# Figure List

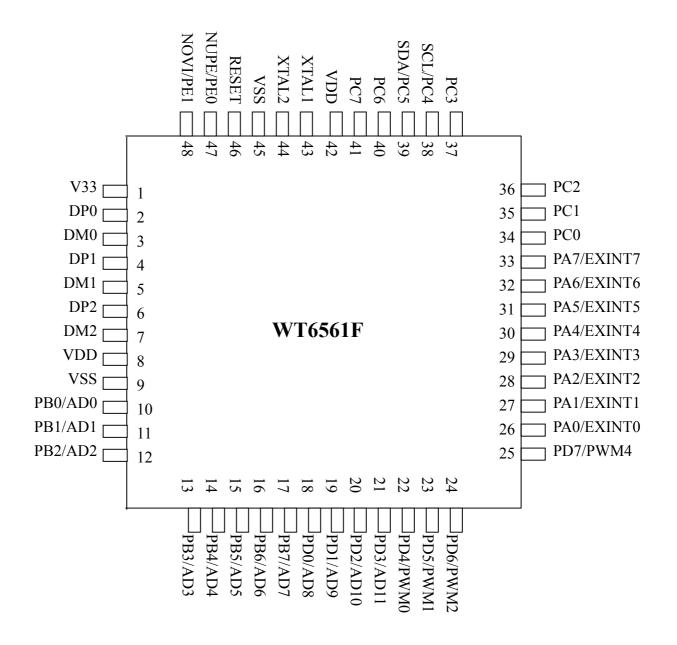

| Figure 1. WT6561F 48-Pin QFP Package                       | 13 |

|------------------------------------------------------------|----|

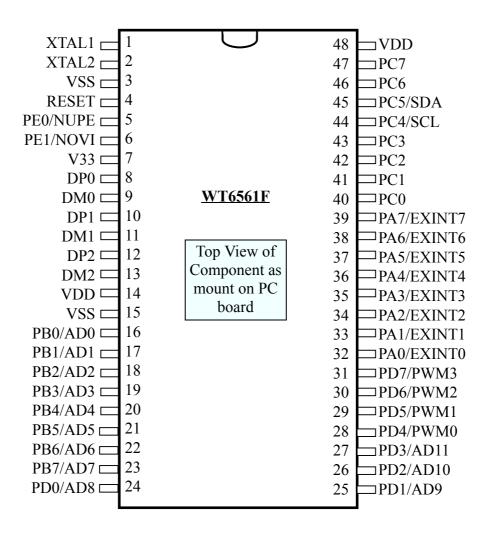

| Figure 2. WT6561F 48-Pin QFP Package                       | 14 |

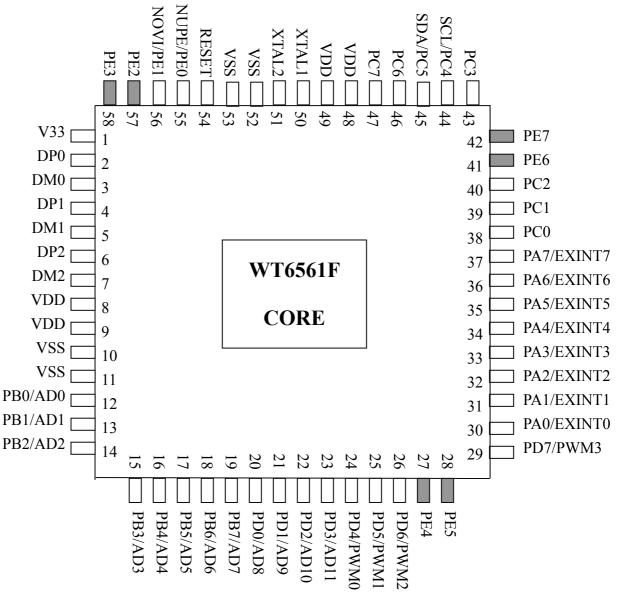

| Figure 3. WT6561F Core Pads Map                            | 15 |

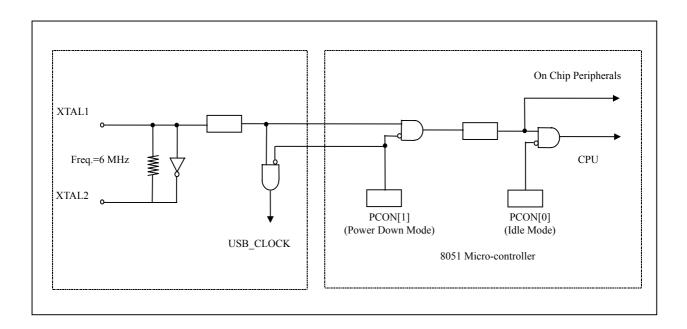

| Figure 4. Clock Circuit                                    | 22 |

| Figure 5. Transmit FIFO Outline (example for 8 bytes FIFO) | 25 |

| Figure 6. Receive FIFO Outline(example for 8 bytes FIFO)   | 28 |

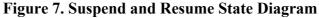

| Figure 7. Suspend and Resume State Diagram                 | 32 |

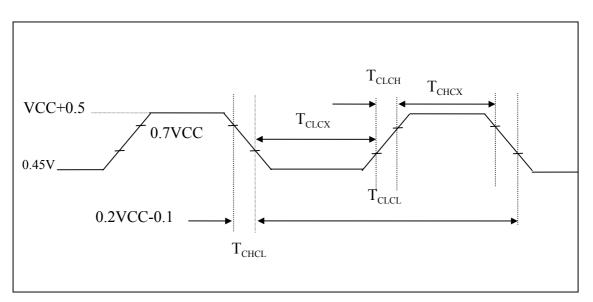

| Figure 8. External Clock Drive Waveform                    | 87 |

# Table List

| Table 1. WT6561F 48 Signals Arranged by Pin Number | 9  |

|----------------------------------------------------|----|

| Table 2. WT6561F Signal Description                | 12 |

| Table 3. Addressing Mapping                        | 19 |

| Table 4. WT6561F Special Function Register Layout  | 20 |

| Table 5. Writing to the Byte Count Register        | 26 |

| Table 6. Truth Table for Transmit FIFO Management  | 27 |

| Table 7. Status of the Receive FIFO Data Set       | 29 |

| Table 8. Truth Table for Receive FIFO Management   | 30 |

| Table 9. External Function Register Layout         | 34 |

| Table 10. Function Address Register                | 35 |

| Table 11. USB Function Interrupt Register          | 36 |

| Table 12. USB Function Interrupt Enable Register   | 37 |

| Table 13. USB SIE Interface Register               | 38 |

| Table 14. Endpoint Index Register                  | 39 |

| Table 15. Endpoint Control Register                | 40 |

| Table 16. Watchdog Timer Reset Register            | 41 |

| Table 17. Transmit FIFO Data Register              | 42 |

| Table 18. Transmit FIFO Control Register           | 43 |

| Table 19. Transmit FIFO Flag Register              | 44 |

| Table 20. Transmit FIFO Byte Count Register        |    |

| Table 21. Endpoint Transmit Status Register        | 46 |

| Table 22. Hub Port Bus Status Register             | 47 |

| Table 23. Hub Port Status Change Register          |    |

| Table 24. Notebook Register                        |    |

| Table 25. Hub Address Register                     | 50 |

| Table 26. USB Hub Interrupt Register               | 51 |

| Table 27. USB Hub Interrupt Enable Register        | 52 |

| Table 28. Hub Status and Configuration Register    | 53 |

| Table 29. Hub Endpoint 1 Status Change Register    | 54 |

| Table 30. Hub Port Index Register                  | 55 |

| Table 31. Hub Port Control Register                    | 56 |

|--------------------------------------------------------|----|

| Table 32. Hub Port Status Register                     | 57 |

| Table 33. Receive FIFO Data Register                   | 58 |

| Table 34. Receive FIFO Control Register                | 59 |

| Table 35. Receive FIFO Flag Register                   | 60 |

| Table 36. Receive FIFO Byte Count Register             | 61 |

| Table 37. Endpoint Receive Status Register             | 63 |

| Table 38. PA Register                                  | 64 |

| Table 39. PD Register                                  | 65 |

| Table 40. PE Register                                  | 66 |

| Table 41. External Interrupt Direction Register        | 67 |

| Table 42. External Interrupt Enable Register           | 68 |

| Table 43. Watch-Dog Timer Extension Register           | 69 |

| Table 44. Port Remote Wakeup Enable Register           | 70 |

| Table 45. PWM0 Duty Control Register                   | 71 |

| Table 46. PWM Enable Register                          | 72 |

| Table 47. ADC Lower Byte Register                      | 73 |

| Table 48. ADC Upper Byte Register                      | 73 |

| Table 49. ADC Lower Byte Register                      | 74 |

| Table 50. Enable/Disable of pull-up PUPCTRLA Register  | 75 |

| Table 51. Enable/Disable of pull-up PUPCTRLB Register  | 76 |

| Table 52. Enable/Disable AD low byte channel Register  | 77 |

| Table 53. Enable/Disable AD high byte channel Register | 78 |

| Table 54. Enable/Disable Power Switch Pins Register    | 79 |

| Table 55. PA,PD,PE output enable Register              | 80 |

| Table 56. I2C Control Register                         | 81 |

| Table 57. I2C Interface Status Register                | 82 |

| Table 58. I2C Interface Control Register               | 83 |

| Table 59. I2C Transmit/Receive Buffer Register         | 84 |

| Table 60. I2C Interface Address Register               | 85 |

| Table 61. DC Electrical Characteristics                | 86 |

| Table 62. Absolute Maximum Rating                      | 87 |

| Table 63. AC Electrical Characteristics                | 87 |

# 1 Features

### **GENERAL DESCRIPTION**

WT6561F is an embedded flash memory type and micro-controller based Full Speed USB device with 2 down stream Hub. It contains an 8051 CPU, 16K bytes Flash, 512 bytes SRAM, 12 channels of 12 bits AD converter, 4 PWMs, and I<sup>2</sup>C Interface. It is suitable for the combination of USB peripheral functions with Hub, such as X-Box game pad/joystick, USB game controller, and USB keyboard hub, etc.

### **FEATURES**

- 8-bit 8051 compatible CPU with 24 MHz operating frequency

- 16K bytes Flash, 512 bytes SRAM

- 6MHz crystal oscillator

- Universal Serial Bus (USB) hub with one upstream port, two external downstream ports, and one internal downstream port for embedded function.

- Complete Universal Serial Bus specification 1.1 compatible

### • USB hub

- Connectivity behavior

- Power management, including suspend / resume

- Device connect / disconnect detection

- Bus fault detection and recovery

- Full / Low speed device support

- Gang mode downstream port power enable

- Gang mode over-current detection

### • USB Embedded function:

- Support USB1.1 Full Speed Functions

- Compliant to USB Human Interface Devices (HID) specification 1.0 and XID specification.

- 1 control endpoint, IN/OUT each with 64 Bytes (8/16/32/64 bytes programmable) FIFO

- 1 Interrupt IN endpoint, with 64 Bytes(8/16/32/64 bytes programmable) FIFO

- 2 Generic endpoints (IN/OUT programmable) each with 64 Bytes(8/16/32/64

V0.99h

bytes programmable) FIFO

- 12 channels 12-bit AD converter

- 4 channels 8 bits PWM

- 14 GPIO(minimum), (Maximum 34 programmable I/O pin)

- Low VDD reset

- Fast mode master/slave I<sup>2</sup>C interface (support 50/100/200 up to 400KHz)

- One Watch-dog timer (programmable ranged from 10ms ~ 640ms)

- Two 16bit programmable timer

#### **ORDERING INFORMATION**

| Package Type | Part Number  |

|--------------|--------------|

| 48-pin LQFP  | WT6561F-LQ48 |

| 48-pin DIP   | WT6561F-N48  |

| Die          | WT6561F-Die  |

# 2 Pin Assignment and Package Types

| Pin | Name    | Pin | Name            | Pin | Name       |

|-----|---------|-----|-----------------|-----|------------|

| 1   | V33     | 17  | PB7/AD7         | 33  | PA7/EXINT7 |

| 2   | DP0     | 18  | PD0/AD8         | 34  | PC0        |

| 3   | DM0     | 19  | PD1/AD9         | 35  | PC1        |

| 4   | DP1     | 20  | PD2/AD10        | 36  | PC2        |

| 5   | DM1     | 21  | PD3/AD11/ADvref | 37  | PC3        |

| 6   | DP2     | 22  | PD4/PWM0        | 38  | PC4/SCL    |

| 7   | DM2     | 23  | PD5/PWM1        | 39  | PC5/SDA    |

| 8   | VDDA    | 24  | PD6/PWM2        | 40  | PC6        |

| 9   | VSSA    | 25  | PD7/PWM3        | 41  | PC7        |

| 10  | PB0/AD0 | 26  | PA0/EXINT0      | 42  | VDD        |

| 11  | PB1/AD1 | 27  | PA1/EXINT1      | 43  | XTAL1      |

| 12  | PB2/AD2 | 28  | PA2/EXINT2      | 44  | XTAL2      |

| 13  | PB3/AD3 | 29  | PA3/EXINT3      | 45  | VSS        |

| 14  | PB4/AD4 | 30  | PA4/EXINT4      | 46  | RESET      |

| 15  | PB5/AD5 | 31  | PA5/EXINT5      | 47  | PE0/NUPE   |

| 16  | PB6/AD6 | 32  | PA6/EXINT6      | 48  | PE1/NOVI   |

### Table 1. WT6561F 48 Signals Arranged by Pin Number

# 2.1 Pin Description

### Pin Description (48 PDIP & 48 LQFP Package)

| DIP | LQFP   | Signal      | Туре | Description                                                                                                                                                                                                                      |  |

|-----|--------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin | Pin    | Name        |      |                                                                                                                                                                                                                                  |  |

| 7   | 1      | V33         | PWR  | 3.3Volts output, Must be connected to a $1\mu$ F capacitor (or larger) to ensure proper operation of the differential line drivers. The other lead of the capacitor must be connected to GND.                                    |  |

| 8   | 2      | DP0         | I/O  | USB plus data line of USB upstream port. An internal $1.5K\Omega \pm 5\%$ pull-up resistor is connected between this lead and V33 to select full-speed USB operation. The internal $1.5 K\Omega$ resistor is controlled by DPEN. |  |

| 9   | 3      | DM0         | I/O  | USB minus data line of USB upstream port.                                                                                                                                                                                        |  |

| 10  | 4      | DM1         | I/O  | USB plus data lines of USB downstream ports. An external 15K $\Omega$ ± 5% pull-down resistor must be connected to each of these leads.                                                                                          |  |

| 11  | 5      | DP1         | I/O  | USB minus data lines of USB downstream ports. An external $15K\Omega \pm 5\%$ pull-down resistor must be connected to each of these leads.                                                                                       |  |

| 12  | 6      | DP2         | I/O  | USB plus data lines of USB downstream ports. An external $15K\Omega \pm 5\%$ pull-down resistor must be connected to each of these leads.                                                                                        |  |

| 13  | 7      | DM2         | I/O  | USB minus data lines of USB downstream ports. An external $15K\Omega \pm 5\%$ pull-down resistor must be connected to each of these leads.                                                                                       |  |

| 14  | 8      | VDDA        | PWR  | +5V supply voltage, for analog circuit                                                                                                                                                                                           |  |

| 15  | 9      | VSSA        | PWR  | Ground for analog circuit                                                                                                                                                                                                        |  |

| 16  | 10     | PB1/AD0     | I/O  | Option 1: GPIO Port, With Schmitt-trigger and $30K\Omega$                                                                                                                                                                        |  |

| 17  | 11     | PB1/AD1     | I/O  | programmable pull-up resistor in input mode.                                                                                                                                                                                     |  |

| 18  | 12     | PB2/AD2     | I/O  | Option 2: Input of AD converter.                                                                                                                                                                                                 |  |

| 19  | 13     | PB3/AD3     | I/O  |                                                                                                                                                                                                                                  |  |

| 20  | 14     | PB4/AD4     | I/O  |                                                                                                                                                                                                                                  |  |

| 21  | 15     | PB5/AD5     | I/O  |                                                                                                                                                                                                                                  |  |

| 22  | 16     | PB6/AD6     | I/O  |                                                                                                                                                                                                                                  |  |

| 23  | 17     | PB7/AD7     | I/O  |                                                                                                                                                                                                                                  |  |

|     | Techno | logy Co Ltd |      | V0.99h                                                                                                                                                                                                                           |  |

Suites 2202-7, 22/F Tower6, The Gateway, Tsimshatsui, Kowloon, Hong Kong TEL:852-2123 3289 FAX:852-2123 3393

# WT6561F

#### **USB Device Controller with Hub**

| 24 | 18 | PD0/AD8    | I/O |                                                                                                               |

|----|----|------------|-----|---------------------------------------------------------------------------------------------------------------|

| 25 | 19 | PD1/AD9    | I/O | Note: For Pin 19 (PD3/AD11/ADVref). If it is programmed as the                                                |

| 26 | 20 | PD2/AD10   | I/O | reference AD voltage (ADVref), then only 11 channels of AD can be used (i.e. AD[10:0]). Or otherwise, when 12 |

| 27 | 21 | PD3/AD11/  | I/O | channels will be used, the reference voltage is VDDA.                                                         |

|    |    | ADVref     |     |                                                                                                               |

| 28 | 22 | PD4 /PWM0  | I/O | Option 1: GPIO Port, With Schmitt-trigger and $30K\Omega$                                                     |

| 29 | 23 | PD5/PWM1   | I/O | <b>programmable</b> pull-up resistor in input mode.                                                           |

| 30 | 24 | PD6/PWM2   | I/O | Option 2: 8-bit PWM.                                                                                          |

| 31 | 25 | PD7/PWM3   | I/O |                                                                                                               |

| 32 | 26 | PA0/EXINT0 | I/O | Option 1: GPIO Port, With Schmitt-trigger and 30KΩ pull-up resistor in input mode.                            |

|    |    |            |     | Option 2: External interrupt.                                                                                 |

| 33 | 27 | PA1/EXINT1 | I/O |                                                                                                               |

| 34 | 28 | PA2/EXINT2 | I/O |                                                                                                               |

| 35 | 29 | PA3/EXINT3 | I/O |                                                                                                               |

| 36 | 30 | PA4/EXINT4 | I/O |                                                                                                               |

| 37 | 31 | PA5/EXINT5 | I/O |                                                                                                               |

| 38 | 32 | PA6/EXINT6 | I/O |                                                                                                               |

| 39 | 33 | PA7/EXINT7 | I/O |                                                                                                               |

| 40 | 34 | PC0        | I/O | GPIO Port, With Schmitt-trigger and $30K\Omega$ pull-up resistor in                                           |

| 41 | 35 | PC1        | I/O | input mode.                                                                                                   |

| 42 | 36 | PC2        | I/O |                                                                                                               |

| 43 | 37 | PC3        | I/O |                                                                                                               |

| 44 | 38 | PC4/SCL    | I/O | Option 1: GPIO Port, With Schmitt-trigger and $30K\Omega$ pull-up                                             |

| 45 | 39 | PC5/SDA    | I/O | resistor in input mode.<br>Option 2: Hardware I <sup>2</sup> C interface                                      |

| 46 | 40 | PC6        | I/O | GPIO Port, With Schmitt-trigger and $30K\Omega$ pull-up resistor in                                           |

| 47 | 41 | PC7        | I/O | input mode.                                                                                                   |

| 48 | 42 | VDD        | PWR | +5V power supply voltage.                                                                                     |

| 1  | 43 | XTAL1      | Ι   | Crystal oscillator input                                                                                      |

| 2  | 44 | XTAL2      | 0   | Crystal oscillator output.                                                                                    |

| 3  | 45 | VSS        | PWR | Ground                                                                                                        |

|    |    |            |     |                                                                                                               |

# WT6561F

#### **USB Device Controller with Hub**

| 4 | 46 | RESET    | Ι   | Reset input. Active high. This pin has an internal pull-down resister connected.   |  |

|---|----|----------|-----|------------------------------------------------------------------------------------|--|

| 5 | 47 | PE0/NUPE | I/O | Option 1: GPIO Port, With Schmitt-trigger and 30KΩ pull-up resistor in input mode. |  |

|   |    |          |     | Option 2: Downstream port power enable, low active and internal pull-up.           |  |

| 6 | 48 | PE1/NOVI | I/O | Option 1: GPIO Port, With Schmitt-trigger and 30KΩ pull-up resistor in input mode. |  |

|   |    |          |     | Option 2: Downstream port over-current detection, low active and internal pull-up. |  |

|   |    | VPP      | I/O | High Voltage pin used in test mode and operating in 0~15V (not bonded)             |  |

|   |    | TM[1:0]  | I/O | Analog pins used in test mode and operating in 0~VDD. (not bonded)                 |  |

Note:

1. For flash programming purpose, a total of 18 pins are used. They are PB[7:0], PC[2:0], PD[7], PE[1:0], XTAL1, RESET, VDD, VSS.

2. PE[7:2] shown in the core pad map are simply GPIO ports with Schmitt-trigger and 30KΩ pull-up resistor in input mode.

#### Table 2. WT6561F Signal Description

# 2.2 Pin Configuration

Figure 1. WT6561F 48-Pin QFP Package

Figure 2. WT6561F 48-Pin DIP Package

WT6561F USB Device Controller with Hub

Figure 3. WT6561F Core Pads Map

Note: Three pads, TM[0], TM[1] and VPP for foundry usage, is not shown in the figure.

# **3** Functional Description

The WT6561F is a physical entity that conjoins a device and 2 downstream USB interface to a compound device with USB interface. It functions as an USB device with an 2-port hub. Operations of the USB interface and device function are controlled through the use of external function registers (XFRs), special function registers (SFRs), SIE, HIU, SIL, FIFOs and 8051 micro-controller that are described in the following sections.

# 3.1 WT6561F USB Module

The USB function interface manages communications between the Host and the USB function. The WT6561F interface consists of the USB full / low speed transceiver, the serial bus engine (SIE), the hub interface unit (HIU), the system interface logic (SIL), and the transmit / receive FIFOs. The USB transceiver in WT6561F provides a physical interface to USB lines. The SIE handles communication protocol of USB. The HIU manages data transmission between upstream and downstream ports. The SIL handles data transfers and provides the interface among the SIE, the 8051 CPU and the function FIFOs.

The main blocks in the USB module are:

- 1. **Full / Low Speed USB Transceiver:** This is an on-chip transceiver having one differential driver to transmit the USB data onto the USB bus and single ended receivers on the D+ and D- lines as well as a differential receiver to receive the USB data signal on the USB bus.

- 2. Serial Bus Interface Engine (SIE): The SIE does all the front-end functions of USB protocol such as clock/data separation, sync-field identification, NRZI-NRZ conversion, token packet decoding, bit stripping, bit stuffing, NRZ-NRZI conversion, CRC5 checking and CRC16 generation and checking. Besides, it manages detecting of reset, suspend and resume signals on the upstream port of the WT6561F to wakeup the system from the suspend state. It also provides serial-to-parallel conversion for the serial packet from the full speed USB transceiver to 8 bit parallel data to the system interface logic

and for 8 bit parallel data from the system interface logic to serial packet to the full speed USB transceiver.

- 3. **Hub Interface Unit (HIU):** The HIU processes all the USB packets transmission, it detects SOP / EOP for each packet and enable / disable USB data line to send packets in both direction.

- 4. **System Interface Logic (SIL):** The SIL operates in conjunction with the 8051 CPU to provide the capabilities of controlling the operation of the FIFOs. The SIL also monitors the status of the data transactions, transfers event control to the 8051 CPU through interrupt requests at the appropriate moment, initiate resume signaling to USB bus while the WT6561F is in power-down mode. Operation of the SIL is controlled through the use of external function registers.

- 5. Device Function / Hub-Function FIFOs: The WT6561F device function interface has four endpoints that can support three types of USB data transfer: control, interrupt and bulk transfer. Transmit FIFOs are written by 8051 CPU, then read by SIL for transmission. Receive FIFO is written by the SIL following reception, then read by the 8051 CPU. Endpoint 0 supports control transfer for configuration / command / status type communication flows between client software and function. Endpoint 1/2/3 supports interrupt/bulk transfer. The hub function has 2 endpoints supporting two types of USB data transfer: control and interrupt. Endpoint 0 contains two FIFO for transmit and receive while endpoint 1 is used as hub status-change notification and only a byte register is used.

## 3.2 Micro-controller

The 8051 CPU is a high performance 8-bit on-chip micro-controller running the firmware associated with the operation of the function. As shown in Figure -(TBD), it features 16K-byte Flash, 512-byte RAM and two 16 bit timers. In addition, the 8051 has two power saving modes enabling further power reduction.

- 1. **16-bit Timer:** The WT6561F has two timers that can be clocked by oscillator. It can be programmed for applications such as periodically generating interrupt requests and serving as a firmware watchdog timer.

- 2. **8051 On-Chip Memory:** The 8051 provides on-chip program memory beginning at location 0000H where, following chip reset, the first instruction is fetched and executed from. The 8051 CPU also provides on-chip data RAM beginning at location 00H. Locations 00H-7FH can be accessed with direct, indirect addressing while locations 80H-FFH can only be accessed with indirect addressing. Locations 20H-2FH are bit addressable.

# 3.3 WT6561F Address Space Mapping

The WT6561F has five address spaces : a program memory space, an internal data memory space, a special function register space, an external function register space, and a register file. Table 3 shows the addressing mapping of the WT6561F.

| Memory Type       | Size      | Location    | Data Addressing  |

|-------------------|-----------|-------------|------------------|

| Code              | 8K bytes  | 0000H-1FFFH | Indirect using   |

|                   |           |             | MOVC instruction |

| External Function | 64 bytes  | 00H-3FH     | Indirect using   |

| Register          |           |             | MOVX instruction |

| Embedded External | 192bytes  | 40H-FFH     | Indirect using   |

| RAM               | -         |             | MOVX instruction |

| Internal Data     | 128 bytes | 00H-7FH     | Direct, Indirect |

|                   | 128 bytes | 80H-FFH     | Indirect         |

| SFRs              | 128 bytes | 80H-FFH     | Direct           |

| Register File (1) | 8 bytes   | R0-R7       | Register         |

Note:

Direct: Direct Byte Addressing

Indirect: Indirect Byte Addressing

#### Table 3. Addressing Mapping

### 3.3.1 WT6561F Special Function Register Address Space

The special function registers (SFRs) reside in this optimized 8051 micro-controller core. Table 4 lists the location of all the WT6561F SFRs. Please refer to the 8051 data sheet for bit definition of each SFR.

| Data Address | <b>Register Name</b> | Description                 |

|--------------|----------------------|-----------------------------|

| 80H          | PO                   | Port 0                      |

| 81H          | SP                   | Stack Point                 |

| 82H          | DPL                  | Data Point Low              |

| 83H          | DPH                  | Data Point High             |

| 87H          | PCON                 | Power Control Register      |

| 88H          | TCON                 | Timer Control Register      |

| 89H          | TMOD                 | Timer Mode Register         |

| 8AH          | TL0                  | Timer 0 Low Order           |

| 8CH          | TH0                  | Timer 0 High Order          |

| 90H          | P1                   | Port 1 (As PB)              |

| A0H          | P2                   | Port 2 (As PC)              |

| A8H          | IE                   | Interrupt Enable Register   |

| B0H          | P3                   | Port 3                      |

| B8H          | IP                   | Interrupt Priority Register |

| D0H          | PSW                  | Program Status Word         |

| E0H          | ACC                  | Accumulator                 |

| F0H          | В                    | B Register                  |

Table 4. WT6561F Special Function Register Layout

### **3.3.2 External Function Register Address Space**

The external function registers (XFRs) reside inside the USB module. The 8051 is connected to one of these registers when the register is addressed by the contents of registers R0 or R1 in the internal data memory. Two instructions, MOVX @Rr, A and MOVX A, @Rr can be used for data movement between the XFRs and accumulator of the 8051.Table 9 lists the location of all the XFRs. When the instruction, MOVX @Rr, A or MOVX A, @Rr, is executed, the address contained in R0 or R1 registers is latched by ALE signal and then the direction of data movement between the XFRs and the 8051 can be controlled by the signals  $\overline{WR}$  or  $\overline{RD}$  subsequently generated by the 8051.

### 3.4 Clock Unit

The WT6561F can use an external clock or an on-chip oscillator with crystal or ceramic resonator as its clock source. The timing waveform at XTAL1 can be provided by:

- an on-chip oscillator employing an external crystal / resonator connected across XTAL1 and XTAL2

- an external clock source connected to XTAL1

The frequency of clock is 6MHz in normal operation, and is used as the internal X8 PLL input, then the PLL output 48MHz clock (4 times of full-speed USB bit-rate and internal CPU clock).

As shown in Figure 4, the clock to CPU control section is stopped where "1" is set in bit 0 (IDL) of the power control register (PCON) in firmware, thereby the CPU operation is halted in idle mode. Idle mode freezes the clocks to the CPU at known states while the peripherals continue to be clocked. The CPU status before entering idle mode is preserved. The contents of the SFRs, XFRs and RAM are also retained. Idle mode can be used while the device is in un-enumerated state following chip reset. Activation of an enabled interrupt and a logic high on chip reset are the ways to exit the idle mode.

The clock to where the CPU controlled section and peripherals that including some portions of USB function is stopped at where bit 1 (PD) of the power control register (PCON) is set in firmware. Therefore both oscillator and CPU operation are halted in power-down mode. The CPU status before entering power-down mode is preserved. In addition, the contents of the SFRs, XFRs and RAM are also retained. For suspend, firmware must put the WT6561F into power-down mode to meet the USB limitation of 500  $\mu$ A. Activation of an enabled interrupt and a logic high on chip reset are the ways to exit the power-down mode.

### Figure 4. Clock Circuit

### 3.5 Reset

Chip reset can be initiated by the built-in power on reset (low voltage reset) or an USBinitiated reset, or a high level of signal on the RESET pin for at least 100us while the oscillator is running.

Built-in power on reset circuit can generate a pulse to reset the entire chip.

A "low" voltage (VCC  $\leq$  V<sub>LVR</sub>) causes a reset condition for entire chip to prevent the chip from being placed at unknown state.

## **3.6 Power-down Mode and Idle Mode**

The instruction that sets PCON.0 is the last instruction executed before the idle mode is activated. Once in the idle mode the CPU status is preserved in its entirety. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware and then the idle mode is terminated.

The instruction that sets PCON.1 is the last executed prior to entering power-down mode. Once in the power-down mode, the oscillator is stopped. The contents of the on-chip RAM, the Special Function Registers and USB External Function Registers are saved. Hardware reset and activation of any enabled interrupt is the ways of exiting the power-down mode. Power-down mode should be used for USB suspend operation. PCON.1 has to be set in the ISR of interrupt caused by active SUSPEND signal.

The WT6561F can initiate resume signaling to the USB host through remote wakeup of the USB function while it is in power-down mode. While in power-down mode, remote wakeup has to be initiated through assertion of an enabled interrupt. In the ISR for the interrupt activated by active SUSPEND signal, the interrupt should be enabled in firmware prior to entering power-down mode which can be terminated by activation of an enabled interrupt signal or an enabled USB resume interrupt signal (RESUME). In the ISR, interrupt signal should be disable before escaping from power-down mode. Upon completion of the ISR, program execution continues with the instruction immediately following the instruction that activated the power-down.

Note: Add two "NOP" instructions after set power-down instruction in F/W to avoid code execution error.

# 3.7 Interrupt

There are 13 interrupt sources share two external interrupt inputs of the 8051:

- Interrupt 0 This interrupt is connected to the external hardware interrupt input 0 of the 8051. In WT6561F, this interrupt is used by hub function interrupts (include suspend / resume processing), The interrupt vector is 03H.

- Interrupt 1 This interrupt is connected to the external hardware interrupt input 1 of the 8051. In WT6561F, The device function interrupts and port-3 bit interrupts use it to operate. In normal operation, interrupt is disabled. In power-down mode to support remote wakeup, interrupt is enabled to terminate the power-down mode (suspend state). and its interrupt vector is 13H.

### **3.8 Function Endpoint**

The WT6561F supports four device function endpoints. Endpoint 0 contains a FIFO each for transmit and receive. Endpoint 1, endpoint 2 and 3 can be programmed to transmit or receive. Endpoint 0 handles control data transfer. Endpoint 1, endpoint 2 and 3 can be interrupt or bulk transfer. The EPINDEX register selects the endpoint for any given data transaction.

The WT6561F supports two hub function endpoints. Endpoint 0 contains a FIFO each for transmit and receive control data while endpoint 1 is used as hub status-change and only a byte register is available.

## 3.9 Transmit FIFOs

### **3.9.1** Transmit FIFOs Features

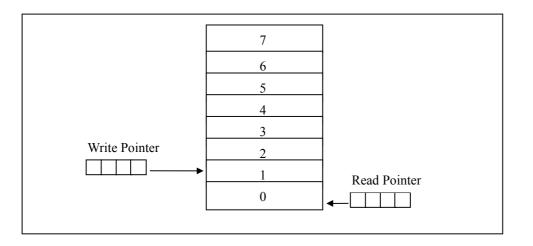

The transmit FIFOs are data buffers with the following features (See Figure 5):

- support for one data set of not greater than 8/16/32/64 bytes (programmable by counter setting)

- a byte count register to store the number of bytes in the data set

- protection against overwriting data in a full FIFO

- capable to retransmit the current data set

Figure 5. Transmit FIFO Outline (example for 8 bytes FIFO)

The 8051 CPU writes to the FIFO location specified by the write pointer also used as the byte-counter to indicate how many bytes have been written and not yet read by the SIL. The write pointer automatically increments by one after a write and decrements by one after a read. The read pointer points the next FIFO location to be read by the SIL. The read pointer automatically increments by one after a read. The transmit FIFO is inhibited to be read by the SIL when it is empty or before a data set has been successfully written into it.

V0.99h

### 3.12.2 Transmit Data Set Management

TXFULL = 1 in the TXFLG register, indicates data set has been written into the FIFO and is ready for transmission. Following reset, TXFULL = 0 and TXEMP = 1, signifying an empty FIFO. Only the first eight bytes of the data set which size is greater than eight are written into the FIFO. In this case, TXFULL is not set until a write to TXCNT. In the case of TXFULL = 1 farther writing to TXDAT or TXCNT are ignored. Please note that the content of TXCNT determines the number of bytes transmitted over the USB lines. Discrepancy between the byte number written to TXCNT and number of bytes actually written to the FIFO will cause an unexpected result. Read the FIFO is prohibited when the FIFO is empty or TXFULL = 0.

Two events cause the TXFULL to be updated:

- A new data set is written to the FIFO: The CPU writes bytes to the FIFO via TXDAT and writes the number of bytes to TXCNT. TXFULL is only set after the write to TXCNT. Set TXCNT=0 indicates a zero length transmission. In this case, TXFULL is set and TXEMP remains unchanged to indicate the FIFO is still empty. This process is illustrated in Table 5.

- A data set in the FIFO is successfully transmitted: The SIL reads the data set from the FIFO for transmission. When a good transmission is acknowledged, the TXFULL is cleared and TXEMP is set.

| TX   | TX  | Zero Length  | Write bytes to      | Data Set      | TX   | TX  |

|------|-----|--------------|---------------------|---------------|------|-----|

| FULL | EMP | Transmission | TXDATx              | Written       | FULL | EMP |

| 0    | 0   | No           |                     | Yes           | 1    | 0   |

| 0    | 1   | No           |                     | Yes           | 1    | 0   |

| 0    | 1   | Yes          | Write byte count to | No            | 1    | 1   |

| 1    | -   | -            | TXCNTx              | Write Ignored | 1    | _   |

#### Table 5. Writing to the Byte Count Register

When a good transmission is completed, both read pointer and write pointer is advanced to

the start point of the FIFO to set up for transmitting the next data set. When a bad transmission is encountered, the read pointer is reversed to the start point of the FIFO to enable the SIL to re-read the last data set for retransmission. The pointer reversal and advance are accomplished automatically by hardware. Table 6 summarizes how actions following a transmission depend on TXERR and TXACK.

| TXERR | TXACK | Action at End of Transfer Cycle                                        |  |

|-------|-------|------------------------------------------------------------------------|--|

| 0     | 0     | No operation                                                           |  |

| 0     | 1     | Read Pointer and Write Pointer both are set to the start point of FIFO |  |

| 1     | 0     | Read Pointer is set to the start point of FIFO                         |  |

#### Table 6. Truth Table for Transmit FIFO Management

### **3.12.3** Transmit FIFO Registers

TXDAT, the transmit FIFO data register (see Table 17)

TXCNT, the transmit FIFO byte count register (see Table 20)

TXCON, the transmit FIFO control register (see Table 18)

TXFLG, the transmit FIFO flag register (see Table 19)

These registers are endpoint indexed. They are used as a set to control the operation of the transmit FIFO, associated with the current endpoint specified by the EPINDEX register

# 3.13 Receive FIFOs

The WT6561F has two receive FIFO for Device / hub endpoint 0. This FIFO is shared with the transmit FIFO. Detail operating is described in section 5.15.

### 3.13.1 Receive FIFO Features

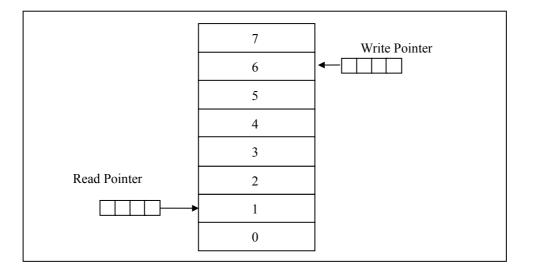

The receive FIFO is a data buffer with the following features (see Figure 6):

- support for one data set of not greater than eight bytes

- a byte count register accesses the number of bytes in the data set

- flag to signal a full FIFO and an empty FIFO

- capability to re-receive the last data set

#### Figure 6. Receive FIFO Outline(example for 8 bytes FIFO)

The SIL writes to the FIFO location specified by the write pointer also used as the bytecounter to indicate how many bytes have been written and not yet read by the 8051 CPU. The write pointer automatically increments by one after a write and decrements by one after a read. The read pointer points the next FIFO location to be read by the 8051 CPU. The read pointer automatically increments by one after a read. The receive FIFO is inhibited to be read by the 8051 CPU when it is empty or before a data set has been successfully written into it.

When a SETUP token is detected by the SIL, the SIL flushes the FIFO even if the FIFO is being read by the 8051 CPU.

### 3.13.2 Receive Data Set Management

RXFULL = 1 in the RXFLG register, indicates the data set has been written into the FIFO and is ready for reception. Following reset, RXFULL = 0 and RXEMP = 1, signifying an empty FIFO. Only the first eight bytes of the data set which size is greater than eight are written into FIFO. RXFULL is however not set until reception is done and successfully acknowledged. RXFULL is cleared by setting the FFRC bit of RXCON in firmware to indicate the data set has successfully read by CPU. In the case of RXFULL = 1 farther writes to FIFO are ignored. Please note that the content of RXCNT should be read by 8051 CPU to determine the numbers of bytes need to be read from FIFO by 8051 CPU. Further reading from an empty FIFO is ignored.

| RXFULL | RXEMP | Status                            |

|--------|-------|-----------------------------------|

| 0      | 0     | Data set is being written to FIFO |

| 0      | 1     | Empty                             |

| 1      | 0     | Data set already written to FIFO  |

| 1      | 1     | Zero length packet received       |

#### Table 7. Status of the Receive FIFO Data Set

When a good reception is completed and the data set has been successfully read by the 8051, firmware must set the FFRC bit of RXCON to advance the write pointer and read pointer to the start point of the FIFO to set up for receiving the next data set. When a bad reception is completed, the write pointer can be reversed to the position of the start point of the FIFO to enable the SIL to re-write the last data set for re-reception. The pointer advance and reversal are accomplished automatically by hardware. Table 8 summarizes how actions following a reception depend on RXERR and RXACK.

| RXERR | RXACK | Action at End of Transfer Cycle                                                                               |

|-------|-------|---------------------------------------------------------------------------------------------------------------|

| 0     | 0     | No operation                                                                                                  |

| 0     | 1     | Read Pointer and Write Pointer are set to the start point<br>of FIFO when firmware sets the FFRC bit of RXCON |

Table 8. Truth Table for Receive FIFO Management

### 3.13.3 Receive FIFO Registers

RXDAT, the receive FIFO data register (see Table 33) RXCNT, the receive FIFO byte count register (see Table 36) RXCON, the receive FIFO control register (see Table 34) RXFLG, the receive FIFO flag register (see Table 35)

These registers are endpoint indexed. They are used as a set to control the operation of the receive FIFO associated with the current endpoint specified by the EPINDEX register.

# 3.14 Setup Token Receive FIFO Handling

SETUP tokens received by the endpoint zero must be acknowledged, even if the receive FIFO is not empty. As described in section 5.14, when a SETUP token is detected by the SIL, the SIL flushes the FIFO and sets the STOVW bit of RXSTAT for reset and locking the read pointer. These prevent RXURF bit of RXFLG and the read pointer from being set if the receive FIFO flush occurs in the middle of an 8051 CPU data read cycle. The STOVW bit is cleared and the EDOVW bit is set when a SETUP packet has been successfully acknowledged. The read pointer will remain locked until both the STOVW and EDOVW bits are cleared. For SETUP packets only, firmware must clear EDOVW before reading data from the FIFO. If this is not done, data read from the FIFO will be invalid. After processing a SETUP packet, firmware should always check the STOVW and EDOVW flags before setting the RXFFRC bit. When a SETUP packet either has been or is being received, setting of RXFFRC has no effect if either STOVW or EDOVW is set.

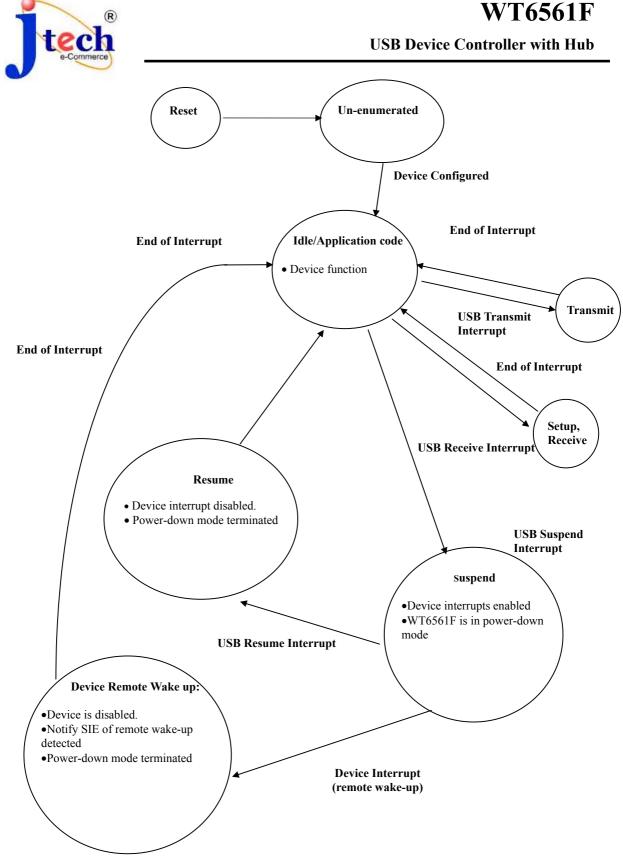

# 3.15 Suspend and Resume

In order to reduce the power consumption, WT6561F automatically enters the suspend state when it has observed no bus traffic for 3 ms. When in suspend, the 8051 CPU and its peripherals are in power down mode, an interrupt is enabled to support remote wakeup. The entire chip consumes less than 500  $\mu$ A in suspended state.

WT6561F exits suspend mode when there is bus activity. A USB device may also request the host exits from suspend or selective suspend by using electrical signaling to indicate remote wakeup. The ability of a device to signal remote wakeup is optional. WT6561F allows the host to enable or disable this capability. Device states are described in Figure 7.

V0.99h

# **4 USB External Function Registers**

| Data Address | Register Name | Description                            |  |

|--------------|---------------|----------------------------------------|--|

| 00H          | FADDR         | Function Address Register              |  |

| 01H          | USBFI         | USB Function Interrupt Register        |  |

| 02H          | USBFIE        | USB Function Interrupt Enable Register |  |

| 03H          | SIEI          | SIE Interface Register                 |  |

| 04H          | (TEST)        | Reserved for Testing                   |  |

| 05H          | EPINDEX       | Endpoint Index Register                |  |

| 06H          | EPCON         | Endpoint Data-flow Control Register    |  |

| 07H          | WDTRST        | Watchdog Timer Reset Register          |  |

| 08H          | TXDAT         | Transmit FIFO Data Register            |  |

| 09H          | TXCON         | Transmit FIFO Control Register         |  |

| 0AH          | TXFLG         | Transmit FIFO Flag Register            |  |

| 0BH          | TXCNT         | Transmit FIFO Byte Count Register      |  |

| 0CH          | TXSTAT        | Endpoint Transmit Status Register      |  |

| 0DH          | HPBSTAT       | Hub Port Bus Status Register           |  |

| 0EH          | HPSC          | Hub Port Status Change Register        |  |

| 0FH          | NOTEBOOK      | Notebook Register                      |  |

| 10H          | HADDR         | Hub Address Register                   |  |

| 11H          | USBHI         | USB Hub Interrupt Register             |  |

| 12H          | USBHIE        | USB Hub Interrupt Enable Register      |  |

| 13H          | HSTAT         | Hub Status and Configuration Register  |  |

| 14H          | HEPSC         | Hub Endpoint 1 Status Change Register  |  |

| 15H          | HPINDEX       | Hub Port Index Register                |  |

| 16H          | HPCON         | Hub Port Control Register              |  |

| 17H          | HPSTAT        | Hub Port Status Register               |  |

| 18H          | RXDAT         | Receive FIFO Data Register             |  |

| 19H          | RXCON         | Receive FIFO Control Register          |  |

| 1AH          | RXFLG         | Receive FIFO Flag Register             |  |

| 1BH          | RXCNT         | Receive FIFO Byte Count Register       |  |

| 1CH          | RXSTAT        | Endpoint Receive Status Register       |  |

| 1DH          | PA            | Port A (corresponding P0) data         |  |

| 1EH          | PD            | Port D (corresponding P3) data         |  |

| 1FH          | PE            | Port E (corresponding P4) data         |  |

**USB Device Controller with Hub**

| Data Address | Register Name | Description                                       |

|--------------|---------------|---------------------------------------------------|

| 20H          | EXINTD        | Rising/Falling Trigger Control for External Intr. |

| 21H          | EXINTEN       | Enable/Disable Control for External Interrupts    |

| 22H          | WDTEXT        | Extension of watch-dog timer                      |

| 23H          | RMPEN         | Enable/Disable port Remote wakeup                 |

| 24H          | PWM0          | PWM data 0                                        |

| 25H          | PWM1          | PWM data 1                                        |

| 26H          | PWM2          | PWM data 2                                        |

| 27H          | PWM3          | PWM data 3                                        |

| 28H          | PWMEN         | Enable of PWMs                                    |

| 29H          | ADL           | AD data lower 8 bits                              |

| 2AH          | ADH           | AD data upper 4 bits                              |

| 2BH          | AD_C          | AD control bits                                   |

| 2CH          | PUCTRLB       | PB programmable pull-up                           |

| 2DH          | PUCTRLD       | PD programmable pull-up                           |

| 2EH          | ADCHENL       | ADC Channel enable select, bit 7:0                |

| 2FH          | ADCHENH       | ADC Channel enable select, bit 11:8               |

| 30H          | PSWEN         | Power Switch Control                              |

| 31H          | PAOE          | PA Output Enable                                  |

| 32H          | PDOE          | PD Output Enable                                  |

| 33H          | PEOE          | PE Output Enable                                  |

| 34H          | I2CCON        | I2C Function Control (For Firmware I2C only)      |

| 35H (R)      | I2CSTA        | I2C Interface Status Register                     |

| 35H (W)      | I2CCON2       | I2C Interface Control Register                    |

| 36H (W)      | I2CTX         | I2C Interface Transmit Buffer Register            |

| 36H (R)      | I2CRX         | I2C Interface Receive Buffer Register             |

| 37H (W)      | I2CADR        | I2C Interface Address Register                    |

**Table 9. External Function Register Layout**

FADDR

Address: 00H Reset State: 0000 0000B

Function Address Register. This XFR holds the address for the USB function. During bus enumeration, it is written with a unique value assigned by the host.

| 7      |          | 0        |

|--------|----------|----------|

|        |          | FA6:0    |

|        |          |          |

| Bit    | Bit      | Function |

| Number | Mnemonic |          |

| Number | Mnemonic |                                                                                                                                                                                                                      |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      |          | Reserved:                                                                                                                                                                                                            |

|        |          | Write zero to this bit.                                                                                                                                                                                              |

| 6:0    | FA6:0    | 7-bit Programmable Function Address:                                                                                                                                                                                 |

|        |          | This register is programmed through the commands received via endpoint 0 on configuration, which should be the only time the firmware should change the value of this register. This register is hardware read-only. |

Table 10. Function Address Register

USBFI

Address: 01H Reset State: x000 0000B

USB Function Interrupt Register. A '1' indicates that an interrupt is actively pending. All bits are cleared after a read.

| 7      |       |       |      |      |      |       | 0     |

|--------|-------|-------|------|------|------|-------|-------|

| RMPINT | ADINT | EXINT | USBx | USBx | USBx | USBRx | USBTx |

|        |       |       | 3INT | 2INT | 1INT | 0INT  | 0INT  |

| Bit    | Bit       | Function                                                                                                                                                  |  |  |  |  |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Number | Mnemonic  |                                                                                                                                                           |  |  |  |  |

| 7      | RMPINT    | (Remote wake up interrupt enable) During suspend, if any of the enabled port (see RMPEN) detects "low", then RMPINT is set and remote-wakeup is processed |  |  |  |  |

| 6      | ADINT     | AD Converter Interrupt flag. This bit is set when the AD data was converted                                                                               |  |  |  |  |

| 5      | EXINT     | External Interrupt<br>1: Interrupt detected (Only occurs when any of EXINTEN is set to '1'<br>0: No interrupt                                             |  |  |  |  |

| 4      | USBx3INT  | Function Transmit/Receive Dong Flag for endpoint 3                                                                                                        |  |  |  |  |

| 3      | USBx2INT  | Function Transmit/Receive Dong Flag for endpoint 2                                                                                                        |  |  |  |  |

| 2      | USBx1INT  | Function Transmit/Receive Dong Flag for endpoint 1                                                                                                        |  |  |  |  |

| 1      | USBRx0INT | Function Receive Dong Flag for endpoint 0                                                                                                                 |  |  |  |  |

| 0      | USBTx0INT | Function Transmit Done Flag for endpoint 0.                                                                                                               |  |  |  |  |

#### Table 11. USB Function Interrupt Register

#### USBFIE

Address: 02H Reset State: x000 0000B

USB Function Interrupt Enable Register.

| 7 |          |          |         |         |         | 0       |

|---|----------|----------|---------|---------|---------|---------|

|   | ADINT_IE | <br>USBx | USBx    | USBx    | USBRx   | USBTx   |

|   |          | 3INT_IE  | 2INT_IE | 1INT_IE | 0INT_IE | 0INT_IE |

| Bit    | Bit          | Function                                                                                                                                                        |

|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic     |                                                                                                                                                                 |

| 7      | Reserved     |                                                                                                                                                                 |

| 6      | ADINT_IE     | ADINT Interrupt Enable                                                                                                                                          |

| 5      | Reserved     |                                                                                                                                                                 |

| 4      | USBx3INT_IE  | Function Transmit/Receive Dong Interrupt Enable 3:<br>Enable USBx3INT                                                                                           |

| 3      | USBx2INT_IE  | Function Transmit/Receive Done Interrupt Enable $\frac{1}{9}$ 2:<br>Enable function transmit/receive done interrupt for endpoint $\frac{1}{9}$ 2<br>(USBx2INT). |

| 2      | USBx1INT_IE  | Function Transmit/Receive Done Interrupt Enable $\ge 1$ :<br>Enable function transmit/receive done interrupt for endpoint $\ge 1$<br>(USBx1INT).                |

| 1      | USBRx0INT_IE | Function Transmit Receive Done Interrupt Enable $\pm 0$ :<br>Enable function transmit receive done interrupt for endpoint $\pm 0$<br>(USBRx0INT).               |

| 0      | USBTx0INT_IE | Function Transmit Done Interrupt Enable 0:<br>Enable function transmit done interrupt for endpoint 0<br>(USBTx0INT).                                            |

#### Table 12. USB Function Interrupt Enable Register

For all bits, a '1' means the interrupt is enabled and will cause an interrupt to be signaled to the micro-controller. A '0' means the associated interrupt source is disabled and cannot cause an interrupt.

SIEI

Address: 03H Reset State: xxxx x000B

USB SIE Interface Register.

| 7 |      |      |          |      | 0      |

|---|------|------|----------|------|--------|

|   | <br> | <br> | USBRSTEN | DPEN | WAKEUP |

| Bit    | Bit      | Function                                                                                 |

|--------|----------|------------------------------------------------------------------------------------------|

| Number | Mnemonic |                                                                                          |

| 7:3    |          | Reserved:                                                                                |

|        |          | Values read from these bits are indeterminate. Write zeros to these bits.                |

| 2      | USBRSTEN | USB Reset Enable:                                                                        |

|        |          | Set this bit to enable USB reset. This bit should be set at least 500µs after            |

|        |          | DPEN is set. This bit is not reset by USB reset.                                         |

| 1      | DPEN     | DP0 Enable:                                                                              |

|        |          | When this bit is cleared, CEXT does not provide 3.3V output and is in high               |

|        |          | impedance state. In this case, the $1.5$ K $\Omega$ resistor does not connect to the DPO |

|        |          | line and the upstream port of the device is disconnected. Set this bit for               |

|        |          | normal operation. This bit is not reset by USB reset.                                    |

| 0      | WAKEUP   | Wakeup:                                                                                  |

|        |          | This bit is used by the USB function to initiate a remote wakeup. Set by                 |

|        |          | firmware to drive resume signaling on the USB lines to the host or upstream              |

|        |          | hub. Cleared by hardware when resume signaling is done.                                  |

## Table 13. USB SIE Interface Register

#### EPINDEX

Address: 05H Reset State: 1xxx xx00B

Endpoint Index Register. This Register identifies the endpoint pair. Its contents select the transmit and receive FIFO pair and serve as an index to endpoint-specific XFRs.

| 7    |      |      |            | 0      |

|------|------|------|------------|--------|

| HORF | <br> | <br> | <br>EPINX1 | EPINX0 |

| Bit    | Bit      | Function                                                                  |

|--------|----------|---------------------------------------------------------------------------|

| Number | Mnemonic |                                                                           |

| 7      | HORF     | Hub/function Bit:                                                         |

|        |          | 1 = Hub. Selects USB hub FIFOs and XFRs.                                  |

|        |          | 0 = Function. Selects USB function FIFOs and XFRs.                        |

| 6:2    |          | Reserved:                                                                 |

|        |          | Values read from these bits are indeterminate. Write zeros to these bits. |

| 1:0    | EPINX1:0 | Endpoint Index:                                                           |

|        |          | 00 = Endpoint  0.                                                         |

|        |          | 01 = Endpoint  1.                                                         |

|        |          | 10 = Endpoint  2.                                                         |

|        |          | 11 = Endpoint  3.                                                         |

#### **Table 14. Endpoint Index Register**

The value in this register selects the associated bank of endpoint-indexed XFRs including TXDAT, TXCON, TXFLG, TXCNT, TXSTAT, RXDAT, RXCON, RXFLG, RXCNT, RXSTAT and EPCON.

| EPCON<br>(Endpoint-indexed)         | Reset State:   | Address:<br>Endpoint 0<br>Hub Endpoint 1<br>Function Endpoint 1,2,3 | 06H<br>001x 0101B<br>x0xx xx00B<br>x0xx xx00B |

|-------------------------------------|----------------|---------------------------------------------------------------------|-----------------------------------------------|

| Endpoint Control Register. This XFR | configures the | e operation of the endpoint spe                                     | cified by EPINDEX.                            |

| 7     |       |       |          |        |      | 0      |

|-------|-------|-------|----------|--------|------|--------|

| RXSTL | TXSTL | CTLEP | <br>RXIE | RXEPEN | TXOE | TXEPEN |

| Bit    | Bit      | Function                                                                                                                                    |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic |                                                                                                                                             |

| 7      | RXSTL    | Stall Receive Endpoint:                                                                                                                     |

|        |          | Set this bit to stall the receive endpoint. Clear this bit only when the host                                                               |

|        |          | has intervened through commands sent down endpoint 0. When this bit is                                                                      |

|        |          | set and RXSETUP is clear, the receive endpoint will respond with a                                                                          |

|        |          | STALL handshake to a valid OUT token. When this bit is set and                                                                              |

|        |          | RXSETUP is set, the receive endpoint will NAK. This bit does not affect                                                                     |

|        |          | the reception of SETUP token by a control endpoint.                                                                                         |

| 6      | TXSTL    | Stall Transmit Endpoint:                                                                                                                    |

|        |          | Set this bit to stall the transmit endpoint. This bit should be cleared only                                                                |

|        |          | when the host has intervened through commands sent down endpoint 0.<br>When this bit is set and RXSETUP is clear, the receive endpoint will |

|        |          | respond with a STALL handshake to a valid IN token. When this bit is set                                                                    |

|        |          | and RXSETUP is set, the receive endpoint will NAK.                                                                                          |

| 5      | CTLEP    | Control Endpoint:                                                                                                                           |

|        |          | Set this bit to configure the endpoint as a control endpoint. Only control                                                                  |

|        |          | endpoint is capable of receiving SETUP tokens.                                                                                              |

| 4      |          | Reserved:                                                                                                                                   |

|        |          | Value read from this bit is indeterminate. Write zero to this bit.                                                                          |

| 3      | RXIE     | Receive Input Enable:                                                                                                                       |

|        |          | Set this bit to enable data from the USB to be written into the receive                                                                     |

|        |          | FIFO. If cleared, the endpoint will not write the received data into the                                                                    |

|        |          | receive FIFO and at the end of reception, but will return a NAK handshake                                                                   |

|        |          | on a valid OUT token if the RXSTL bit is not set. This bit does not affect a                                                                |

|        |          | valid SETUP token. A valid SETUP token and packet overrides this bit if it is cleared, and place the receive data in the FIFO.              |

| 2      | RXEPEN   | Receive Endpoint Enable:                                                                                                                    |

| 2      | KALI LIV | Set this bit to enable the receive endpoint. When disabled, the endpoint                                                                    |

|        |          | does not respond to valid OUT or SETUP token. This bit is hardware read-                                                                    |

|        |          | only and has the highest priority among RXIE and RXSTL. Note that                                                                           |

|        |          | endpoint 0 is enabled for reception upon reset.                                                                                             |

| 1      | TXOE     | Transmit Output Enable:                                                                                                                     |

|        |          | This bit is used to enable the data in TXDAT to be transmitted. If cleared,                                                                 |

|        |          | the endpoint returns a NAK handshake to a valid IN token if the TXSTL                                                                       |

|        |          | bit is not set.                                                                                                                             |

| 0      | TXEPEN   | Transmit Endpoint Enable:                                                                                                                   |

|        |          | This bit is used to enable the transmit endpoint. When disabled, the                                                                        |

|        |          | endpoint does not response to a valid IN token. This bit is hardware read-                                                                  |

|        |          | only. Note that endpoint 0 is enabled for transmission upon reset.                                                                          |

## Table 15. Endpoint Control Register

#### WDTRST

Address: 07H Reset State: xxxx xxxB

Watchdog Timer Reset Register. After device reset, the hardware watchdog is cleared and disabled. Write AAH to WDTRST register can clear and enable the watchdog timer. The watchdog timer overflows in 10.9 ms. If the WDT overflows, it initiates a device reset. Firmware should write AAH to WDTRST to clear the WDT before it overflows.

| 7         | 0 |

|-----------|---|

| WDTRST7:0 |   |

| Bit<br>Number | Bit<br>Mnemonic | Function                                                                     |

|---------------|-----------------|------------------------------------------------------------------------------|

| 7:0           | WDTRST7:0       | Watchdog Timer Reset (write-only):<br>Write AAH to clear and enable the WDT. |

Table 16. Watchdog Timer Reset Register

0

**USB Device Controller with Hub**

TXDAT (Endpoint-indexed)

Address: 08H Reset State: xxxx xxxx B

Transmit FIFO Data Register. Data to be transmitted by the FIFO specified by EPINDEX is first written to this register.

7 TXDAT7:0

| Bit<br>Number | Bit<br>Mnemonic | Function                                                                                                                  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| 7:0           | TXDAT7:0        | Transmit Data Byte (write-only):                                                                                          |

|               |                 | To write data to the transmit FIFO, write to this register. The write pointer is incremented automatically after a write. |

Table 17. Transmit FIFO Data Register

TXCON (Endpoint-indexed) Address: 09H Reset State: 0xxx xxxB

Transmit FIFO Control Register. Controls the transmit FIFO specified by EPINDEX.

| 7     |      |      |      | 0 |

|-------|------|------|------|---|

| TXCLR | <br> | <br> | <br> |   |

| Bit    | Bit      | Function                                                                                                                                                                                    |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic |                                                                                                                                                                                             |

| 7      | TXCLR    | Transmit Clear:                                                                                                                                                                             |

|        |          | Setting this bit flushes the transmit FIFO, resets all the read/write pointers, sets the EMPTY bit in TXFLG, and clears all other bits in TXFLG. After the flush, hardware clears this bit. |

| 6:0    |          | Reserved:                                                                                                                                                                                   |

|        |          | Values read from these bits are indeterminate. Write zeros to these bits.                                                                                                                   |

Table 18. Transmit FIFO Control Register

TXFLG (Endpoint-indexed)

Address: 0AH Reset State: xxxx 1000B

Transmit FIFO Flag Register. These flags indicate the status of data packets in the transmit FIFO specified by EPINDEX.

| 7 |      |           |        |       | 0     |

|---|------|-----------|--------|-------|-------|

|   | <br> | <br>TXEMP | TXFULL | TXURF | TXOVF |

| Bit    | Bit      | Function                                                                                                                                         |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic |                                                                                                                                                  |

| 7:4    |          | Reserved:                                                                                                                                        |

|        |          | Values read from these bits are indeterminate. Write zeros to these bits.                                                                        |

| 3      | TXEMP    | Transmit FIFO Empty Flag (read-only):                                                                                                            |

|        |          | Hardware sets this bit when the data set has been read out of the transmit                                                                       |

|        |          | FIFO by SIL. Hardware clears this bit when the empty condition no longer                                                                         |

|        |          | exists. This bit always tracks the current transmit FIFO status. This flag is                                                                    |

|        |          | also set when a zero-length data packet is transmitted.                                                                                          |

| 2      | TXFULL   | Transmit FIFO Full Flag (read-only):                                                                                                             |

|        |          | This flag indicates the data set is present in the transmit FIFO. This bit is                                                                    |

|        |          | set after write to TXCNT to reflect the condition of the data set. Hardware clears this bit when the data set has been successfully transmitted. |

| 1      | TXURF    | Transmit FIFO Under-run Flag (read-, clear-only)*:                                                                                               |

|        |          | Hardware sets this flag when an addition byte is read from an empty                                                                              |

|        |          | transmit FIFO. This is a sticky bit that must be cleared through firmware                                                                        |

|        |          | by writing a '0' to this bit. When the transmit FIFO under-runs, the read                                                                        |

|        |          | pointer will not advance it remains locked in the empty position.                                                                                |

| 0      | TXOVF    | Transmit FIFO Overrun Flag (read-, clear-only)*:                                                                                                 |