# IR04H420

#### **Features**

- Output Power MOSFETs in half-bridge configuration

- 500V Rated Breakdown Voltage

- High side gate drive designed for bootstrap operation

- Matched propagation delay for both channels

- Independent high and low side output channels

- Undervoltage lockout

- 5V Schmitt-triggered input logic

- Half-Bridge output in phase with IN

- Cross conduction prevention logic

- Internally set dead time

- Shut down input turns off both channels

#### **Description**

The IR04H420 is a high voltage, high speed half bridge. Proprietary HVIC and latch immune CMOS technologies, along with the HEXFET® power MOSFET technology, enable ruggedized single package construction. The logic inputs are compatible with standard CMOS or LSTTL outputs. The front end features an independent high and low side driver in phase with the logic compatible input signals. The output features two HEXFETs in a half-bridge configuration with a high pulse current buffer stage designed for minimum cross-conduction in the half-bridge. Propagation delays for the high and low side power MOSFETs are matched to simplify use. The device can operate up to 500 volts.

## HIGH VOLTAGE HALF-BRIDGE

#### **Product Summary**

| V <sub>IN</sub> (max)                   | 500V        |

|-----------------------------------------|-------------|

| t <sub>on/off</sub>                     | 130 ns      |

| t <sub>rr</sub>                         | 270 ns      |

| R <sub>DS(on)</sub>                     | $3.0\Omega$ |

| P <sub>D</sub> (T <sub>A</sub> = 25 °C) | 2.0W        |

#### **Package**

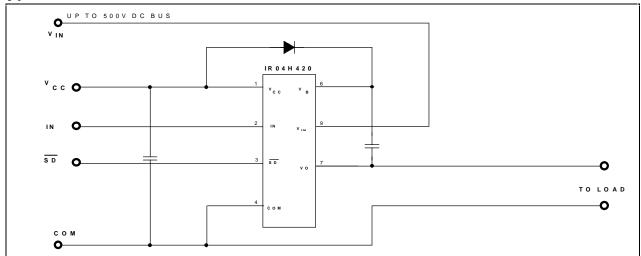

### **Typical Connection**

## **Absolute Maximum Ratings**

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The Thermal Resistance and Power Dissipation ratings are measured under board mounted and still air conditions.

|                 | Parameter                                          |      |                       |       |

|-----------------|----------------------------------------------------|------|-----------------------|-------|

| Symbol          | Definition                                         | Min. | Max.                  | Units |

| V <sub>IN</sub> | High Voltage Supply                                | -0.3 | 500                   |       |

| $V_{B}$         | High Side Floating Supply Absolute Voltage         | -0.3 | 525                   |       |

| VO              | Half-Bridge Output Voltage                         | -0.3 | V <sub>IN</sub> + 0.3 | V     |

| V <sub>IH</sub> | Logic Input Voltage (IN & SD)                      | -0.3 | V <sub>CC</sub> + 0.3 |       |

| V <sub>CC</sub> | Low Side and Logic Fixed Supply Voltage            | -0.3 | 25                    |       |

| dv/dt           | Peak Diode Recovery dv/dt                          |      | 3.5                   | V/ns  |

| P <sub>D</sub>  | Package Power Dissipation @ T <sub>A</sub> ≤ +25°C |      | 2.00                  | W     |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient            |      | 60                    | °C/W  |

| TJ              | Junction Temperature                               | -55  | 150                   |       |

| Ts              | Storage Temperature                                | -55  | 150                   | ٥C    |

| TL              | Lead Temperature (Soldering, 10 seconds)           |      | 300                   |       |

## **Recommended Operating Conditions**

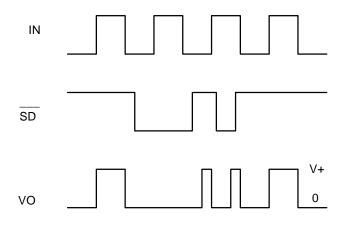

The Input/Output logic timing diagram is shown in Figure 1. For proper operation the device should be used within the recommended conditions.

|                 | Parameter                                        |          |                 |       |

|-----------------|--------------------------------------------------|----------|-----------------|-------|

| Symbol          | Definition                                       | Min.     | Max.            | Units |

| V <sub>B</sub>  | High Side Floating Supply Absolute Voltage       | VO + 10  | VO + 20         |       |

| $V_{IN}$        | High Voltage Supply                              |          | 500             | V     |

| VO              | Half-Bridge Output Voltage                       | (note 1) | 500             |       |

| Vcc             | Low Side and Logic Fixed Supply Voltage          | 10       | 20              |       |

| V <sub>IH</sub> | Logic Input Voltage (IN & SD)                    | 0        | V <sub>CC</sub> |       |

| I <sub>D</sub>  | Continuous Drain Current (T <sub>A</sub> = 25°C) |          | 0.7             | Α     |

|                 | $(T_A = 85^{\circ}C)$                            |          | 0.5             |       |

| T <sub>A</sub>  | Ambient Temperature                              | -40      | 125             | °C    |

Note 1: Logic operational for VO of -5 to 500 V. Logic state held for VO of -5 to - VB.

## **Dynamic Electrical Characteristics**

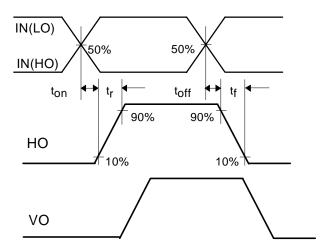

$V_{BIAS}$  ( $V_{CC}$ ,  $V_B$ ) = 15V and  $T_A$  = 25°C unless otherwise specified. Switching time waveform definitions are shown in figure 2.

|                  | Parameter                                                       |      | $T_A = 25^{\circ}C$ |      |       |                         |

|------------------|-----------------------------------------------------------------|------|---------------------|------|-------|-------------------------|

| Symbol           | Definition                                                      | Min. | Тур.                | Max. | Units | Test Conditions         |

| t <sub>on</sub>  | Turn-On Propagation Delay (see note 2)                          |      | 600                 | 720  |       | V <sub>S</sub> = 0 V    |

| t <sub>off</sub> | Turn-Off Propagation Delay (see note 2)                         |      | 90                  | 200  |       | $V_{S} = 500 \text{ V}$ |

| t <sub>r</sub>   | Turn-On Rise Time (see note 2)                                  |      | 80                  | 120  | ns    |                         |

| t <sub>f</sub>   | Turn-Off Fall Time (see note 2)                                 |      | 40                  | 70   |       |                         |

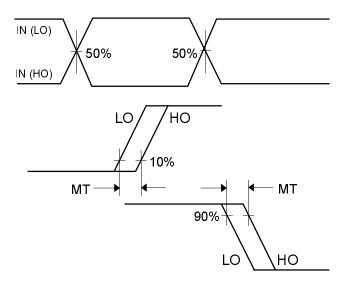

| MT               | Delay Matching, HS & LS Turn-On/Off                             |      | 30                  |      |       |                         |

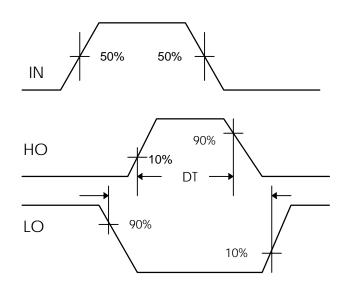

| DT               | Deadtime, LS Turn-Off to HS Turn-On & HS Turn-On to LS Turn-Off |      | 500                 | 750  |       |                         |

| t <sub>rr</sub>  | Reverse Recovery Time (MOSFET Body Diode)                       |      | 260                 |      |       | I <sub>F</sub> = 0.7 A  |

| Qrr              | Reverse Recovery Charge (MOSFET Body Diode)                     |      | 0.7                 |      | μC    | $di/dt = 100A/\mu s$    |

Note 2: Switching times as specified and illustrated in figure 2 are referenced to the MOSFET gate input voltage. This is shown as HO in figure 2.

#### **Static Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{B}$ ) = 15V and  $T_{A}$  = 25°C unless otherwise specified. The Input voltage and current levels are referenced to COM.

|                        | Parameter                                                    | Т    | $T_A = 25^{\circ}C$ |      |       |                         |  |

|------------------------|--------------------------------------------------------------|------|---------------------|------|-------|-------------------------|--|

| Symbol                 | Definition                                                   | Min. | Тур.                | Max. | Units | Test Conditions         |  |

| Supply                 | Supply Characteristics                                       |      |                     |      |       |                         |  |

| V <sub>CCUV+</sub>     | V <sub>CC</sub> Supply Undervoltage Positive Going Threshold | 8.8  | 9.3                 | 9.8  | V     |                         |  |

| V <sub>CCUV</sub> -    | V <sub>CC</sub> Supply Undervoltage Negative Going Threshold | 7.5  | 8.2                 | 8.6  |       |                         |  |

| Iqcc                   | Quiescent V <sub>CC</sub> Supply Current                     |      | 140                 | 240  |       |                         |  |

| I <sub>QBS</sub>       | Quiescent V <sub>BS</sub> Supply Current                     |      | 20                  | 50   | μA    |                         |  |

| los                    | Offset Supply Leakage Current                                |      |                     | 50   | ] [   | $V_{B} = V_{S} = 500V$  |  |

| Input Ch               | naracteristics                                               |      |                     |      |       |                         |  |

| VIH                    | Logic "1" Input Voltage                                      | 2.7  |                     |      |       |                         |  |

| V <sub>IL</sub>        | Logic "0" Input Voltage                                      |      |                     | 0.8  | V     | $V_{CC} = 10V$ to $20V$ |  |

| $V_{SD.TH+}$           | SD Input Positive Going Threshold                            | 2.7  |                     |      |       |                         |  |

| $V_{SD.TH-}$           | SD Input Negative Going Threshold                            |      |                     | 0.8  |       |                         |  |

| I <sub>IN+</sub>       | Logic "1" Input Bias Current                                 |      | 20                  | 40   | μA    |                         |  |

| I <sub>IN</sub> -      | Logic "0" Input Bias Current                                 |      |                     | 1.0  | μΑ    |                         |  |

| Output Characteristics |                                                              |      |                     |      |       |                         |  |

| R <sub>DS(on)</sub>    | Static Drain-to-Source On-Resistance                         |      | 3.0                 |      | Ω     | I <sub>D</sub> = 700mA  |  |

| V <sub>SD</sub>        | Diode Forward Voltage                                        |      | 0.8                 |      | V     | T <sub>i</sub> = 150 °C |  |

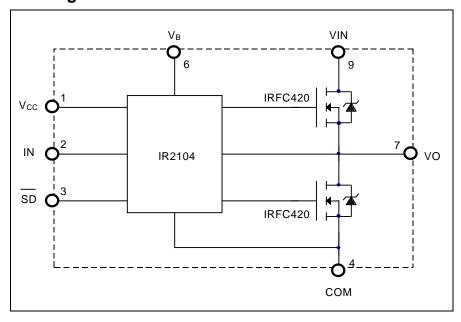

# **Functional Block Diagram**

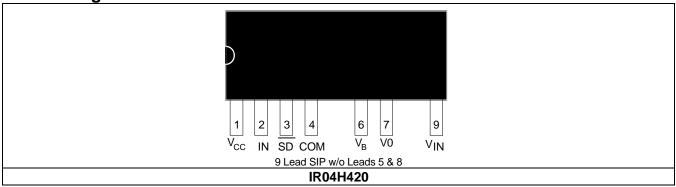

## **Lead Definitions**

|                 | Lead                                                                                                                                          |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | Description                                                                                                                                   |

| Vcc             | Logic and internal gate drive supply voltage.                                                                                                 |

| IN              | Logic input for high and low side gate driver outputs (HO and LO), in phase with HO                                                           |

| SD              | Logic input for shutdown                                                                                                                      |

| V <sub>B</sub>  | High side gate drive floating supply. For bootstrap operation a high voltage fast recovery diode is needed to feed from $V_{CC}$ to $V_{B}$ . |

| V <sub>IN</sub> | High voltage supply.                                                                                                                          |

| VO              | Half-Bridge output.                                                                                                                           |

| COM             | Logic and low side of Half-Bridge return.                                                                                                     |

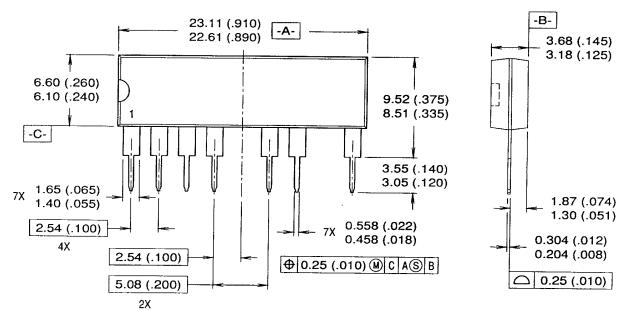

**Lead Assignments**

Figure 1. Input/Output Timing Diagram

Figure 2. Switching Time Waveform Definitions

Figure 3. Delay Matching Waveform Definitions

Figure 4. Deadtime Waveform Definitions

IR04H420

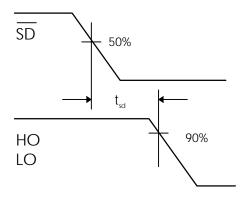

Figure 5. Shutdown Waveform Definitions

#### NOTES:

- 1. DIMENSIONING & TOLERANCING PER ANSI Y14.5M-1982.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSIONS ARE SHOWN IN MILLIMETERS (INCHES).

Package Outline

WORLD HEADQUARTERS: 233 KANSAS ST., EL SEGUNDO, CA 90245 USA • (310)322-3331 • FAX (310)322-3332 • TELEX 472-0403 EUROPEAN HEADQUARTERS: HURST GREEN, OXTED, SURREY RH8 9BB, UK • (44)0883 713215 • FAX (944)0883 714234 • TELEX 95219