Data Sheet May 1999 File Number 4284.5

#### NTSC/PAL Video Encoder

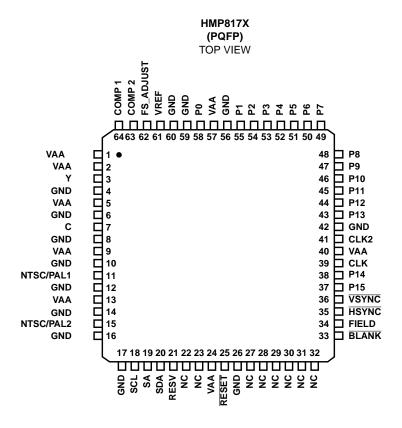

The HMP8170, HMP8171, HMP8172, and HMP8173 NTSC and PAL encoders are designed for use in systems requiring the generation of high-quality NTSC and PAL video.

YCbCr digital video data drive the P0-P15 inputs. The Y data is optionally lowpass filtered to 6MHz and drives the Y analog output. Cb and Cr are each lowpass filtered to 1.3MHz, quadrature modulated, and added together. The result drives the C analog output. The digital Y and C data are also added together and drive the two composite analog outputs.

The DACs can drive doubly-terminated (37.5 $\Omega$ ) lines, and run at a 2x oversampling rate to simplify the analog output filter requirements.

# **Applications**

- DVD Players

- · Video CD Players

- · Digital VCRs

- · Multimedia PCs

#### Related Products

- NTSC/PAL Encoders

- HMP8154, HMP8156A

- NTSC/PAL Decoders

- HMP8115

#### Features

- (M) NTSC and (B, D, G, H, I, M, N, NC) PAL Operation

- · BT.601 and Square Pixel Operation

- · Digital Input Formats

- 8-bit, 16-bit 4:2:2 YCbCr

- 8-bit BT.656

- · Analog Output Formats

- Y/C + Two Composite

- RGB + Composite

- YUV + Composite

- Flexible Video Timing Control

- Timing Master or Slave

- Selectable Polarity on Each Control Signal

- Programmable Blank Output Timing

- · "Sliced" VBI Data Support

- Closed Captioning

- Widescreen Signalling (WSS)

- BT.653 System B and C Teletext

- NABTS (North American Broadcast Teletext)

- WST (World System Teletext)

- Four 2x Oversampling, 10-Bit DACs

- Fast I<sup>2</sup>C Interface

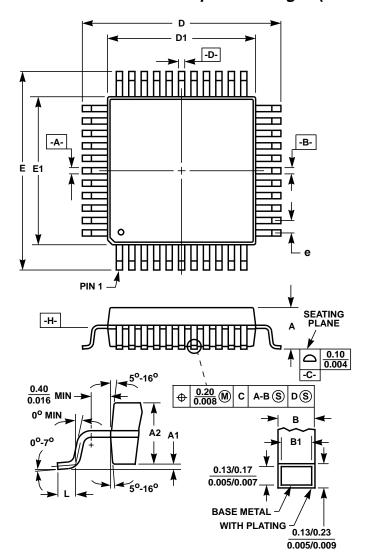

# Ordering Information

| PART NUM                                                               | IBER     | MACROVISION<br>v7.01 | RGB / YUV<br>OUTPUTS | TEMP. RANGE<br>(°C) | PACKAGE             | PKG. NO.  |

|------------------------------------------------------------------------|----------|----------------------|----------------------|---------------------|---------------------|-----------|

| HMP8170CN                                                              |          | no                   | no                   | 0 to 70             | 64 Ld PQFP (Note 2) | Q64.14x14 |

| HMP8171CN                                                              | (Note 1) | yes                  | no                   | 0 to 70             | 64 Ld PQFP (Note 2) | Q64.14x14 |

| HMP8172CN                                                              |          | no                   | yes                  | 0 to 70             | 64 Ld PQFP (Note 2) | Q64.14x14 |

| HMP8173CN                                                              | (Note 1) | yes                  | yes                  | 0 to 70             | 64 Ld PQFP (Note 2) | Q64.14x14 |

| HMP817xEVAL1 Daughter Card Evaluation Platform, where x is replaced by |          |                      |                      |                     | 2, or 3 (Note 3).   |           |

#### NOTES:

- 1. The HMP8171 and HMP8173 may be purchased by Macrovision Authorized Buyers only. These devices are protected by U.S. patent numbers 4,631,603, 4,577,216, and 4,819,098, and other intellectual property rights. The use of Macrovision's copy protection technology in the devices must be authorized by Macrovision and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited.

- 2. PQFP is also known as QFP and MQFP.

- 3. Evaluation board descriptions are in the Applications section.

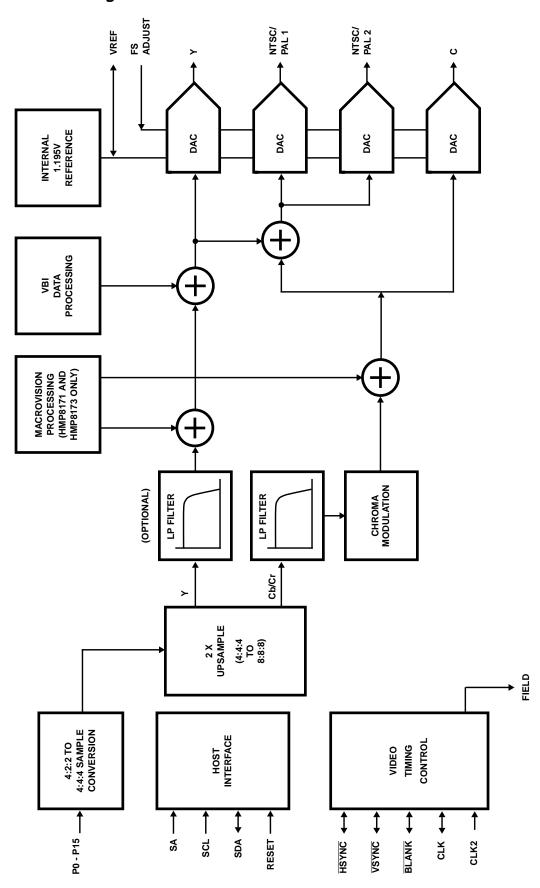

# Functional Block Diagram

# **Functional Operation**

The HMP8170 - HMP8173 are fully integrated digital encoders. All accept YCbCr digital video input data and generate analog video output signals. The four outputs are two composite video signals and Y/C (S-Video). The HMP8172 and HMP8173 can also be configured to output one composite and component RGB or YUV video.

The HMP817x accepts pixel data in one of several formats and transforms it into 4:4:4 sampled luminance and chrominance (YCbCr) data. The encoder then interpolates the YCbCr data to twice the pixel rate and low pass filters it to match the bandwidth of the video output format. If enabled, the encoder also adds vertical blanking interval (VBI) information to the Y data. At the same time, the encoder modulates the chrominance data with a digitally synthesized subcarrier. Finally, the encoder outputs luminance, chrominance, and their sum as analog signals using 10-bit D/A converters.

The HMP817x provides operating modes to support all versions of the NTSC and PAL standards and accepts full size input data with rectangular (BT.601) and square pixel aspect ratios. It operates from a single clock at twice the pixel clock rate determined by the operating mode.

The HMP817x's video timing control is flexible. It may operate as the master, generating the system's video timing control signals, or it may accept external timing controls. The polarity of the timing controls and the number of active pixels and lines are programmable.

# Pixel Data Input

The HMP817x accepts BT.601 YCbCr pixel data via the P0-P15 input pins. The definition of each pixel input pin is determined by the input format selected in the input format register. The definition for each mode is shown in Table 1.

The YCbCr luminance and color difference signals are each 8 bits, scaled 0 to 255. The nominal range for Y is 16 (black) to 235 (white). Y values less than 16 are clamped to 16; values greater than 235 are processed normally. The nominal range for Cb and Cr is 16 to 240 with 128 representing zero. Cb and Cr values outside their nominal range are processed normally. Note that when converted to the analog outputs, some combinations of YCbCr outside their nominal ranges would generate a composite video signal larger than the analog output limit. The composite signal will be clipped, but the S-video outputs (Y and C) will note be.

The color difference signals are time multiplexed into one 8-bit bus beginning with a Cb sample. The Y and CbCr busses may be input in parallel (16-bit mode) or may be time multiplexed and input as a single bus (8-bit mode). The single bus may also contain SAV and EAV video timing reference codes or ancillary data (BT.656 mode).

**TABLE 1. PIXEL DATA INPUT FORMATS**

| PIN<br>NAME                                        | 16-BIT<br>4:2:2<br>YCBCR                                                                     | 8-BIT<br>4:2:2<br>YCBCR                                                                                                      | BT.656                                                            |

|----------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| P0<br>P1<br>P2<br>P3<br>P4<br>P5<br>P6<br>P7       | Cb0, Cr0<br>Cb1, Cr1<br>Cb2, Cr2<br>Cb3, Cr3<br>Cb4, Cr4<br>Cb5, Cr5<br>Cb6, Cr6<br>Cb7, Cr7 | Ignored                                                                                                                      |                                                                   |

| P8<br>P9<br>P10<br>P11<br>P12<br>P13<br>P14<br>P15 | Y0<br>Y1<br>Y2<br>Y3<br>Y4<br>Y5<br>Y6<br>Y7                                                 | Y0, Cb0, Cr0<br>Y1, Cb1, Cr1<br>Y2, Cb2, Cr2<br>Y3, Cb3, Cr3<br>Y4, Cb4, Cr4<br>Y5, Cb5, Cr5<br>Y6, Cb6, Cr6<br>Y7, Cb7, Cr7 | YCbCr Data,<br>SAV and EAV<br>Sequences,<br>and<br>Ancillary Data |

# Pixel Input and Control Signal Timing

The pixel input timing and the video control signal input/output timing of the HMP817x depend on the part's operating mode. The periods when the encoder samples its inputs and generates its outputs are summarized in Table 2.

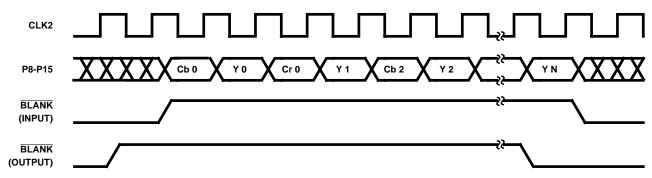

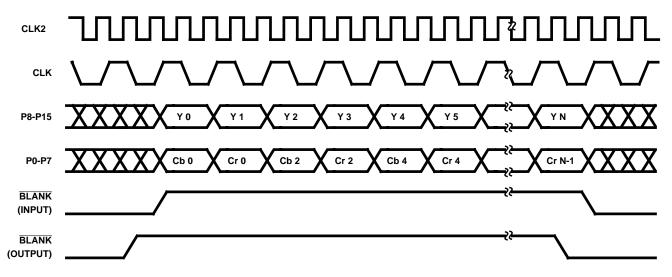

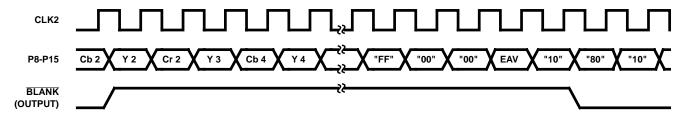

Figures 1, 2, and 3 show the timing of CLK, CLK2, BLANK, and the pixel input data with respect to each other. BLANK may be an input or an output; the figures show both. When it is an input, BLANK must arrive coincident with the pixel input data; all are sampled at the same time.

When BLANK is an output, its timing with respect to the pixel inputs depends on the blank timing select bit in the timing\_I/O\_1 register. If the bit is cleared, the HMP817x negates BLANK one CLK cycle before it samples the pixel inputs.

If the bit is set, the encoder negates BLANK during the same CLK cycle in which it samples the input data. In effect, the input data must arrive one CLK cycle earlier than when the bit is cleared. This mode is not shown in the figures.

TABLE 2. PIXEL INPUT AND CONTROL SIGNAL I/O TIMING

|              | INPUT PIXEL DATA          | VIDEO TIMING C            | ONTROL (NOTE)                         | CLK FREQUENCY  |               |  |

|--------------|---------------------------|---------------------------|---------------------------------------|----------------|---------------|--|

| INPUT FORMAT | SAMPLE                    | INPUT SAMPLE              | OUTPUT ON                             | INPUT          | OUTPUT        |  |

| 16-Bit YCbCr | Rising edge of CLK2 wher  | CLK is low                | Rising edge of CLK2 when CLK is high. | One-half CLK22 |               |  |

| 8-Bit YCbCr  | Every rising edge of CLK2 | Every rising edge of CLK2 | Any rising edge of CLK2               | Ignored        | One-half CLK2 |  |

| BT.656       | Every rising edge of CLK2 | Not Allowed               | Any rising edge of CLK2               | Ignored        | One-half CLK2 |  |

NOTE: Video timing control signals include HSYNC, VSYNC, BLANK and FIELD. The sync and blanking I/O directions are independent; FIELD is always an output.

#### 8-Bit YCbCr Format

When 8-bit YCbCr format is selected, the data is latched on each rising edge of CLK2. The pixel data must be [Cb Y Cr Y' Cb Y Cr Y' . . . ], with the first active data each scan line being Cb data. The pixel input timing is shown in Figure 1.

As inputs, BLANK, HSYNC, and VSYNC are latched on each rising edge of CLK2. As outputs, BLANK, HSYNC, and VSYNC are output following the rising edge of CLK2. If the CLK pin is configured as an input, it is ignored. If configured as an output, it is one-half the CLK2 frequency.

#### 16-Bit YCbCr Format

When 16-bit YCbCr format is selected, the pixel data is latched on the rising edge of CLK2 while CLK is low. The pixel input timing is shown in Figure 2.

As inputs, BLANK, HSYNC, and VSYNC are latched on the rising edge of CLK2 while CLK is low. As outputs, HSYNC, VSYNC, and BLANK are output following the rising edge of CLK2 while CLK is high. In these modes of operation, CLK is one-half the CLK2 frequency.

#### 8-Bit BT.656 Format

When BT.656 format is selected, data is latched on each rising edge of CLK2. The pixel input timing is shown in Figure 3. The figure shows the EAV code at the end of the line. The format of the SAV and EAV codes are shown in Table 3.

The BT.656 input may also include ancillary data to load the VBI or RTCI data registers. The HMP817x will use the ancillary data when enabled in the VBI data input and Timing I/O registers. The ancillary data formats and the enable registers are described later in this data sheet.

As inputs, the BLANK, HSYNC, and VSYNC pins are ignored since all timing is derived from the EAV and SAV sequences within the data stream. As outputs, BLANK, HSYNC and VSYNC are output following the rising edge of CLK2. If the CLK pin is configured as an input, it is ignored. If configured as an output, it is one-half the CLK2 frequency.

FIGURE 1. PIXEL INPUT TIMING - 8-BIT YCBCR

FIGURE 2. PIXEL INPUT TIMING - 16-BIT YCBCR

FIGURE 3. PIXEL INPUT TIMING - BT.656

TABLE 3. BT.656 EAV AND SAV SEQUENCES

| PIXEL INPUT     | P15 | P14 | P13 | P12 | P11 | P10 | P9 | P8 |

|-----------------|-----|-----|-----|-----|-----|-----|----|----|

| Preamble Word 1 | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  |

| Preamble Word 2 | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  |

| Preamble Word 3 | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  |

| Status Word     | 1   | F   | V   | Н   | P3  | P2  | P1 | P0 |

NOTES:

F: 0 = Field 1; 1 = Field 2

V: 0 = Active Line; 1 = Vertical Blanking H: 0 = Start Active Video; 1 = End Active Video

P3 - P0: Protection bits; Ignored

# Video Timing Control

The pixel input data and the output video timing of the HMP817x are at 50 or 59.94 fields per second interlaced. The timing is controlled by the BLANK, HSYNC, VSYNC, FIELD, and CLK2 pins.

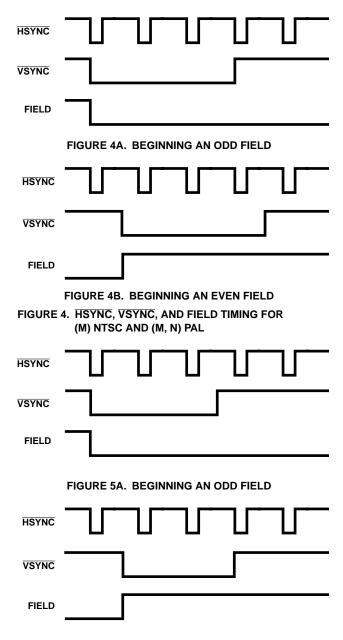

#### HSYNC, VSYNC, and Field Timing

The leading edge of  $\overline{\text{HSYNC}}$  indicates the beginning of a horizontal sync interval. If  $\overline{\text{HSYNC}}$  is an output, it is asserted for about 4.7µs. If  $\overline{\text{HSYNC}}$  is an input, it must be active for at least two CLK2 periods. The width of the analog horizontal sync tip is determined from the video standard and does not depend on the width of  $\overline{\text{HSYNC}}$ .

The leading edge of VSYNC indicates the beginning of a vertical sync interval. If VSYNC is an output, it is asserted for 3 scan lines in (MM) NTSC and (M, N) PAL modes or 2.5 scan lines in (B, D, G, H, I, NC) PAL modes. If VSYNC is an input, it must be asserted for at least two CLK2 periods.

When HSYNC and VSYNC are configured as outputs, their leading edges will occur simultaneously at the start of an odd field. At the start of an even field, the leading edge of VSYNC occurs in the middle of the line.

When HSYNC and VSYNC are configured as inputs, the HMP817x provides a programmable HSYNC window for determining FIELD. The window is specified with respect to the leading or trailing edge of VSYNC. The edge is selected in the field control register. When HSYNC is found inside the window, then the encoder sets FIELD to the value specified in the field control register.

The HMP817x provides programmable timing for the  $\overline{VSYNC}$  input. At the active edge of  $\overline{VSYNC}$ , the encoder

resets its vertical half-line counter to the value specified by the field control register. This allows the input and output syncs to be offset, although the data must still be aligned.

The FIELD signal is always an output and changes state near each leading edge of VSYNC. The delay between the syncs and FIELD depends on the encoder's operating mode as summarized in Table 4. In modes in which the encoder uses CLK to gate its inputs and outputs, the FIELD signal may be delayed 0-12 additional CLK2 periods.

**TABLE 4. FIELD OUTPUT TIMING**

| OPERATI               | NG MODE                |               |                                                                                                                                                 |

|-----------------------|------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC I/O<br>DIRECTION | BLANK I/O<br>DIRECTION | CLK2<br>DELAY | COMMENTS                                                                                                                                        |

| Input                 | Input                  | 148           | FIELD lags VSYNC switching from odd to even.  FIELD lags the earlier of VSYNC and HSYNC when syncs are aligned when switching from even to odd. |

| Input                 | Output                 | 138           | FIELD lags VSYNC.                                                                                                                               |

| Output                | Don't Care             | 32            | FIELD leads VSYNC.                                                                                                                              |

Figure 4 illustrates the HSYNC, VSYNC, and FIELD general timing for (M) NTSC and (M, N) PAL. Figure 5 illustrates the general timing for (B, D, G, H, I, NC) PAL. In the figures, all the signals are shown active low (their reset state), and FIELD is low during odd fields.

FIGURE 5B. BEGINNING AN EVEN FIELD

FIGURE 5. HSYNC, VSYNC, AND FIELD TIMING FOR

(B, D, G, H, I, NC) PAL

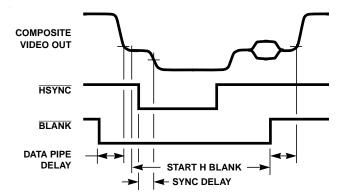

#### **BLANK** Timing

The encoder uses the  $\overline{\text{HSYNC}}$ ,  $\overline{\text{VSYNC}}$ , FIELD signals to generate a standard composite video waveform with no active video (black burst). The signal includes only sync tips, color burst, and optionally, a 7.5 IRE blanking setup. Based on the  $\overline{\text{BLANK}}$  signal, the encoder adds the pixel input data to the video waveform.

The encoder ignores the pixel input data when BLANK is asserted. Instead of the input data, the encoder generates the blanking level. The encoder also ignores the pixel inputs when generating VBI data on a specific line, even if BLANK is negated.

There must be an even number of active and total pixels per line. In the 8-bit YCbCr modes, the number of active and total pixels per line must be a multiple of four. Note that if BLANK is an output, half-line blanking on the output video cannot be done.

The HMP817x never adds a 7.5 IRE blanking setup during the active line time on scan lines 1-21 and 263-284 for (M) NTSC, scan lines 523-18 and 260-281 for (M) PAL, and scan lines 623-22 and 311-335 for (B, D, G, H, I, N) PAL, allowing the generation of video test signals, timecode, and other information by controlling the pixel inputs appropriately.

The relative timing of BLANK, HSYNC, and the output video depends on the blanking and sync I/O directions. The typical timing relation is shown in Figure 6. The delays which vary with operating mode are indicated. The width of the composite sync tip and the location and duration of the color burst are fixed based on the video format.

FIGURE 6. HSYNC, BLANK, AND OUTPUT VIDEO TIMING, NORMAL MODE

When BLANK is an output, the encoder asserts it during the inactive portions of active scan lines (horizontal blanking) and for all of each inactive scan line (vertical blanking). The inactive scan lines blanked each field are determined by the start\_v\_blank and end\_v\_blank registers. The inactive portion of active scan lines is determined by the start\_h\_blank and end\_h\_blank registers.

The zero count for horizontal blanking is 32 CLK2 cycles before the 50% point of the composite sync. From this zero point, the HMP817x counts every other CLK2 cycle. When the count reaches the value in the start\_h\_blank register, the encoder negates  $\overline{BLANK}$ . When the count reaches the value in the end\_h\_blank register,  $\overline{BLANK}$  is asserted. There may be an additional 0-3 CLK2 delays in modes which use CLK.

The data pipeline delay through the HMP817x is 26 CLK2 cycles. In operating modes which use CLK to gate the inputs into the encoder, the delay may be an additional 0-7 CLK2 cycles. The delay from BLANK to the start or end of active video is an additional one-half CLK cycle when the blank timing select bit is cleared. The active video may also appear to end early or start late since the HMP817x controls the blanking edge rates.

TABLE 5. TYPICAL VIDEO TIMING PARAMETERS

|                             | PIXELS I | PER LINE | HBLANK REGI | STER VALUES | VBLANK REGISTER VALUES |           | CLK2  |  |  |  |  |

|-----------------------------|----------|----------|-------------|-------------|------------------------|-----------|-------|--|--|--|--|

| VIDEO STANDARD              | TOTAL    | ACTIVE   | START       | END         | START                  | END       | (MHz) |  |  |  |  |

| RECTANGULAR PIXELS (BT.601) |          |          |             |             |                        |           |       |  |  |  |  |

| (M) NTSC                    | 858      | 720      | 842 (0x34a) | 122 (0x7a)  | 259 (0x103)            | 19 (0x13) | 27.0  |  |  |  |  |

| (B, D, G, H, I) PAL         | 864      | 720      | 853 (0x355) | 133 (0x85)  | 310 (0x136)            | 22 (0x16) | 27.0  |  |  |  |  |

| (M) PAL                     | 858      | 720      | 842 (0x34a) | 122 (0x7a)  | 259 (0x103)            | 19 (0x13) | 27.0  |  |  |  |  |

| (N) PAL                     | 864      | 720      | 853 (0x355) | 133 (0x85)  | 309 (0x135)            | 21 (0x15) | 27.0  |  |  |  |  |

| (NC) PAL                    | 864      | 720      | 853 (0x355) | 133 (0x85)  | 310 (0x136)            | 22 (0x16) | 27.0  |  |  |  |  |

| SQUARE PIXELS               |          |          |             |             |                        |           |       |  |  |  |  |

| (M) NTSC                    | 780      | 640      | 758 (0x2f6) | 118 (0x76)  | 259 (0x103)            | 19 (0x13) | 24.54 |  |  |  |  |

| (B, D, G, H, I) PAL         | 944      | 768      | 923 (0x39b) | 155 (0x9b)  | 310 (0x136)            | 22 (0x16) | 29.5  |  |  |  |  |

| (M) PAL                     | 780      | 640      | 758 (0x2f6) | 118 (0x76)  | 259 (0x103)            | 19 (0x13) | 24.54 |  |  |  |  |

| (N) PAL                     | 944      | 768      | 923 (0x39b) | 155 (0x9b)  | 309 (0x135)            | 21 (0x15) | 29.5  |  |  |  |  |

| (NC) PAL                    | 944      | 768      | 923 (0x39b) | 155 (0x9b)  | 310 (0x136)            | 22 (0x16) | 29.5  |  |  |  |  |

The delay from the active edge of HSYNC to the 50% point of the composite sync is 4-39 CLK2 cycles depending on the HMP817x operating mode. The delay is shortest when the encoder is the timing master; it is longest when in slave mode.

# **CLK2 Input Timing**

The CLK2 input clocks all of the HMP817x, including its video timing counters. For proper operation, all of the HMP817x inputs must be synchronous with CLK2. The frequency of CLK2 depends on the device's operating mode and the total number of pixels per line. The standard clock frequencies are shown in Table 5.

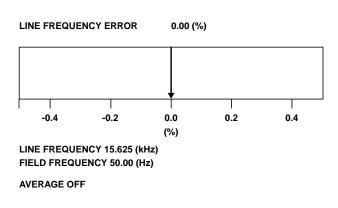

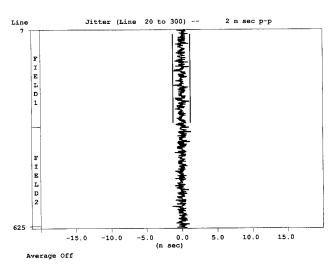

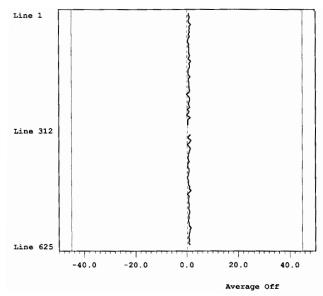

Note that the color subcarrier is derived from the CLK2 input. Any jitter on CLK2 will be transferred to the color subcarrier, resulting in color changes. Just 400ps of jitter on CLK2 causes up to a 1 degree color subcarrier phase shift. Thus, CLK2 should be derived from a stable clock source, such as a crystal. The use of a PLL to generate CLK2 is not recommended.

# Video Processing

# Upsampling

The encoder begins the video processing with the pixel input data. It converts the 4:2:2 YCbCr data to 4:4:4 data. The conversion is done by 2x upsampling the Cb and Cr data. The CbCr upsampling function uses linear interpolation. The HMP817x then upsamples the 4:4:4 data to generate 8:8:8 data. Again, the encoder uses linear interpolation for the upsampling.

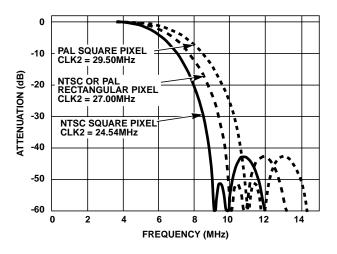

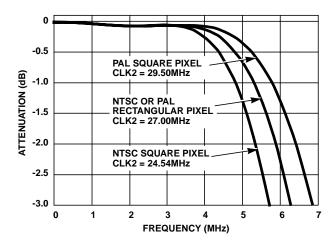

## Horizontal Filtering

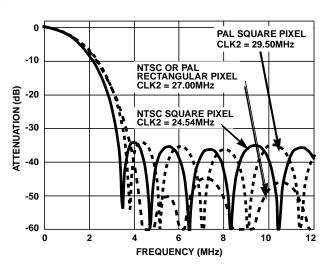

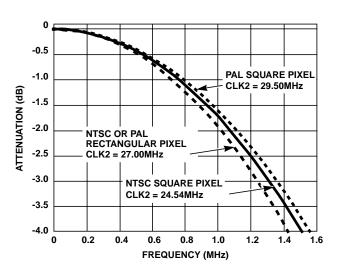

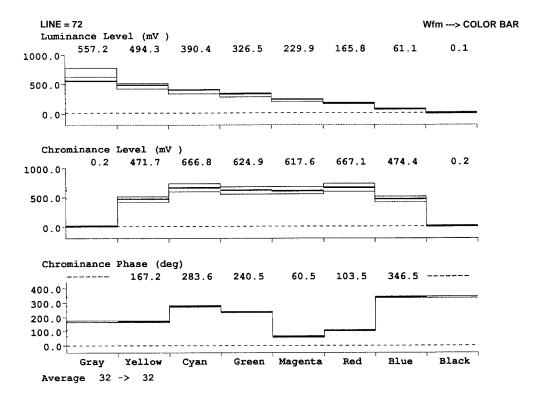

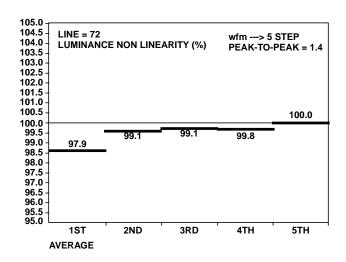

Unless disabled, the HMP817x lowpass filters the Y data to 6.0MHz. Lowpass filtering Y removes any aliasing artifacts due to the upsampling process, and simplifies the analog output filters. The Y 6.0MHz lowpass filter response is shown in Figure 7. At this point, the HMP817x also scales the Y data to generate the proper output levels for the various video standards.

The HMP817x lowpass filters the Cb and Cr data to 1.3MHz prior to modulation. The lowpass filtering removes any aliasing artifacts due to the upsampling process (simplifying the analog output filters) and also properly bandwidth-limits Cb and Cr prior to modulation. The chrominance filtering is not optional like luminance filtering. The Cb and Cr 1.3MHz lowpass filter response is shown in Figure 8.

FIGURE 7A. FULL SPECTRUM

FIGURE 7B. PASS BAND

FIGURE 7. Y LOWPASS FILTER RESPONSE

FIGURE 8A. FULL SPECTRUM

FIGURE 8B. PASS BAND

FIGURE 8. Cb AND Cr LOWPASS FILTER RESPONSE

## **Color Subcarrier Generation**

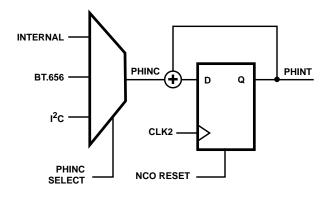

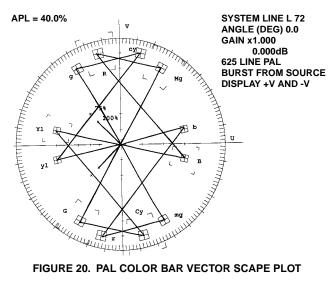

The HMP817x uses a numerically controlled oscillator (NCO) clocked by CLK2 and a sine look up ROM to generate the color subcarrier. As shown in Figure 9, the phase increment value (PHINC) of the NCO may come from the encoder's internal look up table, BT.656 ancillary data, or a control register. The PHINC source is selected in timing I/O register 2.

FIGURE 9. COLOR SUBCARRIER GENERATION NCO.

The MSBs of the accumulated phase value (PHINT) are used to address the encoder's sine look up ROM. The sine values from the ROM are pre-scaled to generate the proper levels for the various video standards. Prescaling outside the CbCr data path minimizes color processing artifacts. The HMP817x modulates the filtered 8:8:8 chrominance data with the synthesized subcarrier.

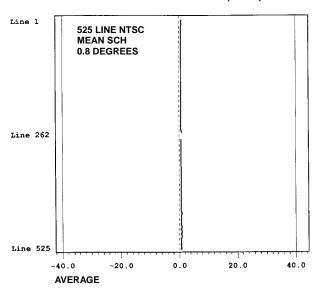

The SCH phase is 0 degrees after reset but then changes monotonically over time due to residue in the NCO. In an ideal system, zero SCH phase would be maintained forever. In reality, this is impossible to achieve due to pixel clock frequency tolerances and digital rounding errors. When the PHINC source is BT.656 data, the SCH phase reset should be disabled.

If enabled, the HMP817x resets the NCO periodically to avoid an accumulation of SCH phase error. The reset occurs at the beginning of each field to burst phase sequence. The sequence repeats every 4 fields for NTSC or 8 fields for PAL.

Resetting the SCH phase every four fields (NTSC) or eight fields (PAL) avoids the accumulation of SCH phase error at the expense of requiring any NTSC/PAL decoder after the encoder be able to handle very minor "jumps" (up to 2 degrees) in the SCH phase at the beginning of each four-field or eight-field sequence. Most NTSC/PAL decoders are able to handle this due to video editing requirements.

# Composite Video Limiting

The HMP817x adds the luminance and modulated chrominance together with the sync, color burst, and optional blanking pedestal to form the composite video data. If enabled in the video processing register, the encoder limits the active video so that it is always greater than one-eighth of full scale. This corresponds to approximately one-half the sync height. This allows the generation of "safe" video in the event non-standard YCbCr values are input to the device.

#### Controlled Edges

The NTSC and PAL video standards specify edge rates and rise and fall times for portions of the video waveform. The HMP817x automatically implements controlled edge rates and rise and fall times on these edges:

- 1. Analog Horizontal Sync (Rising and Falling Edges)

- 2. Analog Vertical Sync Interval (Rising and Falling Edges)

- 3. Color Burst Envelope

- 4. Blanking of Analog Active Video

- 5. Closed Captioning Information

- 6. WSS Information

- 7. Teletext Information

#### "Sliced" VBI Data

The HMP817x generates three types of vertical blanking interval data: closed captioning, widescreen signalling, and teletext data. The data is generated on the scan lines specified by the selected output video standard which are enabled in the VBI data control register. During scan lines with VBI data, the pixel inputs are ignored.

#### Closed Captioning (CC)

The HMP817x captioning data output includes clock run-in and start bits followed by the captioning data. During closed captioning encoding, the pixel inputs are ignored on the scan lines containing captioning information.

The HMP817x has two 16-bit registers containing the captioning information. Each 16-bit register is organized as two cascaded 8-bit registers. One 16-bit register (caption 21) is read out serially during line 18, 21 or 22; the other 16-bit register (WSS 284) is read out serially during line 281, 284 or 335. The data registers are shifted out LSB first.

The captioning output level is 50 IRE for a logic 1 and 0 IRE for a logic 0. All transitions between levels are controlled to have a raised-cosine shape. The rise or fall time of any transition is 240-288ns.

The caption data registers may be loaded via the I<sup>2</sup>C interface or as BT.656 ancillary data. Table 6 illustrates the format of the caption data as BT.656 ancillary data. The transfer should occur only once per field before the start of the SAV sequence of the line containing the captioning output.

When written via the I<sup>2</sup>C interface, the bytes may be written in any order but both must be written within one frame time for proper operation. If the registers are not updated, the encoder resends the previously loaded values.

The HMP817x provides a write status bit for each captioning line. The encoder clears the write status bit to '0' when captioning is enabled and both bytes of the captioning data register have been written. The encoder sets the write status bit to '1' after it outputs the data, indicating the registers are ready to receive new data.

Captioning information may be enabled for either line, both lines, or no lines. The captioning modes are summarized in Table 7.

TABLE 6. BT.656 ANCILLARY DATA FORMAT FOR CLOSED CAPTIONING DATA

| PIXEL INPUT             | P15  | P14 | P13 | P12 | P11    | P10    | P9     | P8     |

|-------------------------|------|-----|-----|-----|--------|--------|--------|--------|

| Preamble 1              | 0    | 0   | 0   | 0   | 0      | 0      | 0      | 0      |

| Preamble 2              | 1    | 1   | 1   | 1   | 1      | 1      | 1      | 1      |

| Preamble 3              | 1    | 1   | 1   | 1   | 1      | 1      | 1      | 1      |

| Data ID                 | ep#  | ер  | 1   | 1   | 0      | 0      | 0      | Line   |

| Data Block Number       | ep#  | ер  | 0   | 0   | 0      | 0      | 0      | 1      |

| Data Word Count         | ep#  | ер  | 0   | 0   | 0      | 0      | 0      | 1      |

| Caption Register Byte 3 | ep#  | ер  | 0   | 0   | bit 15 | bit 14 | bit 13 | bit 12 |

| Caption Register Byte 1 | ep#  | ер  | 0   | 0   | bit 11 | bit 10 | bit 9  | bit 8  |

| Caption Register Byte 1 | ep#  | ер  | 0   | 0   | bit 7  | bit 6  | bit 5  | bit 4  |

| Caption Register Byte 0 | ep#  | ер  | 0   | 0   | bit 3  | bit 2  | bit 1  | bit 0  |

| CRC                     | P14# | Х   | Х   | Х   | Х      | Х      | Х      | Х      |

#### NOTES:

The even parity (EP and EP#) bits are ignored. Line = Data Register Select: 0 = Line 21; 1 = 284. X = Don't Care.

#### **TABLE 7. CLOSED CAPTIONING MODES**

| CLOSED                    |                                                          | CAPTIONIN    | G REGISTER   | WRITE STATUS BIT         |                          |  |

|---------------------------|----------------------------------------------------------|--------------|--------------|--------------------------|--------------------------|--|

| CAPTIONING<br>ENABLE BITS | OUTPUT LINE(S)                                           | 284A<br>284B | 21A<br>21B   | 284                      | 21                       |  |

| 00                        | None                                                     | Ignored      | Ignored      | Always 1                 | Always 1                 |  |

| 01                        | 21 (NTSC)<br>18 (M PAL)<br>22 (Other PAL)                | Ignored      | Caption Data | Always 1                 | 0 = Loaded<br>1 = Output |  |

| 10                        | 284 (NTSC)<br>281 (M PAL)<br>335 (Other PAL)             | Caption Data | Ignored      | 0 = Loaded<br>1 = Output | Always 1                 |  |

| 11                        | 21, 284 (NTSC)<br>18, 281 (M PAL)<br>22, 335 (Other PAL) | Caption Data | Caption Data | 0 = Loaded<br>1 = Output | 0 = Loaded<br>1 = Output |  |

### Widescreen Signalling (WSS)

The HMP817x WSS data output includes clock run-in and start codes followed by the WSS data. For NTSC operation, the WSS data is followed by six bits of CRC data.

The HMP817x has two 14-bit registers containing the WSS information and two 6-bit registers containing the WSS CRC data. Each 14-bit register is organized as a 6-bit register cascaded with an 8-bit one. One 14-bit register (WSS 20) is read out serially during line 17, 20 or 23; the other 14-bit register (caption 283) is read out serially during line 280, 283 or 336. The data registers are shifted out LSB first.

The WSS output level depends on the video format. For NTSC operation (EIAJ CPX-1204), the WSS output level is 70 IRE for a logic 1 and 0 IRE for a logic 0. All transitions between levels are controlled to have a raised-cosine shape with a rise or fall time of 240ns. For PAL operation (ITU-R BT.1119), the WSS output level is 71.5 IRE for a logic 1 and 0 IRE for a logic 0. All transitions between levels are controlled to have a raised-cosine shape with a rise or fall time of 118ns.

The WSS data registers may be loaded via the I<sup>2</sup>C interface or as BT.656 ancillary data. Table 8 illustrates the format of the WSS data as BT.656 ancillary data. The transfer should occur only once per field before the start of the SAV sequence of the line containing the WSS output.

When written via the I<sup>2</sup>C interface, the bytes may be written in any order but all three bytes of each enabled line must be written within one frame time for proper operation. If the registers are not updated, the encoder resends the previously loaded values.

The HMP817x provides a write status bit for each WSS line. The encoder clears the write status bit to '0' when WSS is enabled and all bytes of the WSS data register have been written. The encoder sets the write status bit to '1' after it outputs the data, indicating the registers are ready to receive new data.

WSS information may be enabled for either line, both lines, or no lines. The WSS modes are summarized in Table 9.

TABLE 8. BT.656 ANCILLARY DATA FORMAT FOR WIDESCREEN SIGNALLING DATA

| PIXEL INPUT       | P15  | P14 | P13 | P12 | P11    | P10    | P9     | P8     |

|-------------------|------|-----|-----|-----|--------|--------|--------|--------|

| Preamble 1        | 0    | 0   | 0   | 0   | 0      | 0      | 0      | 0      |

| Preamble 2        | 1    | 1   | 1   | 1   | 1      | 1      | 1      | 1      |

| Preamble 3        | 1    | 1   | 1   | 1   | 1      | 1      | 1      | 1      |

| Data ID           | ep#  | ер  | 1   | 1   | 0      | 0      | 1      | Line   |

| Data Block Number | ep#  | ер  | 0   | 0   | 0      | 0      | 0      | 1      |

| Data Word Count   | ep#  | ер  | 0   | 0   | 0      | 0      | 1      | 0      |

| WSS Data Nibble 3 | ep#  | ер  | 0   | 0   | 0      | 0      | bit 13 | bit 12 |

| WSS Data Nibble 2 | ep#  | ер  | 0   | 0   | bit 11 | bit 10 | bit 9  | bit 8  |

| WSS Data Nibble 1 | ep#  | ер  | 0   | 0   | bit 7  | bit 6  | bit 5  | bit 4  |

| WSS Data Nibble 0 | ep#  | ер  | 0   | 0   | bit 3  | bit 2  | bit 1  | bit 0  |

| WSS CRC Nibble 1  | ep#  | ер  | 0   | 0   | 0      | 0      | bit 5  | bit 4  |

| WSS CRC Nibble 0  | ep#  | ер  | 0   | 0   | bit 3  | bit 2  | bit 1  | bit 0  |

| Reserved          | ep#  | ер  | 0   | 0   | 0      | 0      | 0      | 0      |

| Reserved          | ep#  | ер  | 0   | 0   | 0      | 0      | 0      | 0      |

| CRC               | P14# | Х   | Х   | Х   | Х      | Х      | Х      | Х      |

#### NOTES:

The even parity (EP and EP#) bits are ignored.

Line = Data Register Select: 0 = Line 20; 1 = 283.

The WSS CRC data bits are ignored during PAL operation but must be included in the transfer.

X = Don't Care.

TABLE 9. WIDESCREEN SIGNALLING MODES

|                    |                                                          | WSS RE                | GISTERS            | WRITE STATUS BIT         |                          |  |

|--------------------|----------------------------------------------------------|-----------------------|--------------------|--------------------------|--------------------------|--|

| WSS<br>ENABLE BITS | OUTPUT LINE(S)                                           | 283A, 283B,<br>CRC283 | 20A, 20B,<br>CRC20 | 283                      | 20                       |  |

| 00                 | None                                                     | Ignored               | Ignored            | Always 1                 | Always 1                 |  |

| 01                 | 20 (NTSC)<br>17 (M PAL)<br>23 (Other PAL)                | Ignored               | WSS Data           | Always 1                 | 0 = Loaded<br>1 = Output |  |

| 10                 | 283 (NTSC)<br>280 (M PAL)<br>336 (Other PAL)             | WSS Data              | Ignored            | 0 = Loaded<br>1 = Output | Always 1                 |  |

| 11                 | 20, 283 (NTSC)<br>17, 280 (M PAL)<br>23, 336 (Other PAL) | WSS Data              | WSS Data           | 0 = Loaded<br>1 = Output | 0 = Loaded<br>1 = Output |  |

NOTE: The CRC registers are always ignored during PAL operation.

#### **Teletext**

The HMP817x supports ITU-R BT.653 625-line and 525-line teletext system B and C generation. WST (World System Teletext) is the same as BT.653 system B. NABTS (North American Broadcast Teletext Specification) is the same as BT.653 525-line system C. NABTS is also used to transmit Intel Intercast information.

During the teletext encoding, the line's pixel inputs are ignored. The teletext information includes a 16-bit clock synchronization code; the HMP817x automatically generates it.

The teletext output level depends on the video format. For system B teletext, the output level is 66 IRE for a logic 1 and 0 IRE for a logic 0. All transitions between levels are controlled to have a raised-cosine shape with a rise or fall time of 200ns. For system C teletext, the output level is 70 IRE for a logic 1 and 0 IRE for a logic 0. All transitions between levels are controlled to have a raised-cosine shape with a rise or fall time of 200ns.

The HMP817x generates teletext output on any scan line that includes teletext data in that line's BT.656 ancillary data. The encoder must receive the ancillary data before the SAV sequence in order to output the teletext data. Table 10 shows the BT.656 ancillary data format for loading the teletext data registers.

TABLE 10. BT.656 ANCILLARY DATA FORMAT FOR TELETEXT DATA

| PIXEL INPUT          | P15  | P14 | P13  | P12 | P11     | P10     | P9      | P8      |  |  |  |

|----------------------|------|-----|------|-----|---------|---------|---------|---------|--|--|--|

| Preamble 1           | 0    | 0   | 0    | 0   | 0       | 0       | 0       | 0       |  |  |  |

| Preamble 2           | 1    | 1   | 1    | 1   | 1       | 1       | 1       | 1       |  |  |  |

| Preamble 3           | 1    | 1   | 1    | 1   | 1       | 1       | 1       | 1       |  |  |  |

| Data ID              | ep#  | ер  | 1    | 1   | 0       | 1       | 0       | 0       |  |  |  |

| Data Block Number    | ep#  | ер  | 0    | 0   | 0       | 0       | 0       | 1       |  |  |  |

| Data Word Count      | ep#  | ер  | 0    | 1   | 0       | 1       | 1       | 0       |  |  |  |

| Teletext Register    | ep#  | ер  | Line | Sys | bit 343 | bit 342 | bit 341 | bit 340 |  |  |  |

| Data<br>(86 Nibbles) | ep#  | ер  | 0    | 0   | bit 339 | bit 338 | bit 337 | bit 336 |  |  |  |

| ,                    |      |     |      |     |         |         |         |         |  |  |  |

|                      | ep#  | ер  | 0    | 0   | bit 7   | bit 6   | bit 5   | bit 4   |  |  |  |

|                      | ep#  | ер  | 0    | 0   | bit 3   | bit 2   | bit 1   | bit 0   |  |  |  |

| Reserved             | ep#  | ер  | 0    | 0   | 0       | 0       | 0       | 0       |  |  |  |

| Reserved             | ep#  | ер  | 0    | 0   | 0       | 0       | 0       | 0       |  |  |  |

| CRC                  | P14# | Х   | Х    | Х   | Х       | Х       | Х       | Х       |  |  |  |

#### NOTES:

The even parity (EP and EP#) bits are ignored.

Line = Standard Select: 0 = 525 Lines; 1 = 625 Lines

Sys = System Select: 0 = System B; 1 = System C.

625-line system B uses 43 bytes; all bits are used.

525-line system B uses 35 bytes; bits 343-280 are ignored. 525-line system C uses 34 bytes; bits 343-272 are ignored.

X = Don't Care.

TABLE 11. BT.656 ANCILLARY DATA FORMAT FOR PHINC DATA

| PIXEL INPUT              | P15  | P14 | P13 | P12 | P11    | P10    | P9     | P8     |

|--------------------------|------|-----|-----|-----|--------|--------|--------|--------|

| Preamble 1               | 0    | 0   | 0   | 0   | 0      | 0      | 0      | 0      |

| Preamble 2               | 1    | 1   | 1   | 1   | 1      | 1      | 1      | 1      |

| Preamble 3               | 1    | 1   | 1   | 1   | 1      | 1      | 1      | 1      |

| Data ID                  | ep#  | ер  | 1   | 1   | 0      | 1      | 0      | 1      |

| Data Block Number        | ep#  | ер  | 0   | 0   | 0      | 0      | 0      | 1      |

| Data Word Count          | ep#  | ер  | 0   | 0   | 0      | 0      | 1      | 1      |

| HPLL                     | ep#  | ер  | 0   | 0   | bit 15 | bit 14 | bit 13 | bit 12 |

| Increment<br>(4 Nibbles) | ep#  | ер  | 0   | 0   | bit 11 | bit 10 | bit 9  | bit 8  |

| (4 Nibbles)              | ep#  | ер  | 0   | 0   | bit 7  | bit 6  | bit 5  | bit 4  |

|                          | ep#  | ер  | 0   | 0   | bit 3  | bit 2  | bit 1  | bit 0  |

| FSCPLL                   | ep#  | ер  | PSW | 0   | bit 31 | bit 30 | bit 29 | bit 28 |

| Increment<br>(8 Nibbles) | ep#  | ер  | F2  | F1  | bit 27 | bit 26 | bit 25 | bit 24 |

| (o Nibbles)              |      |     |     |     |        |        |        |        |

|                          | ep#  | ер  | 0   | 0   | bit 7  | bit 6  | bit 5  | bit 4  |

|                          | ep#  | ер  | 0   | 0   | bit 3  | bit 2  | bit 1  | bit 0  |

| CRC                      | P14# | Х   | Х   | Х   | Х      | Х      | Х      | Х      |

NOTES:

The even parity (EP and EP#) bits are ignored.

HPLL, PSW, F2, and F1 are ignored.

X = Don't Care.

#### Macrovision

The HMP8171 and HMP8173 provide the copy protection system specified by the *Macrovision Antitaping Process for Digital Platforms* document, revision 7.01, September 6, 1996.

The devices are protected by U.S. patent numbers 4,631,603, 4,577,216, and 4,819,098 and other intellectual property rights. The use of Macrovision's copy protection technology in the device must be authorized by Macrovision and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited.

Additional information about Macrovision in the HMP8171 and HMP8173 is available to Macrovision Authorized Buyers only. Tech Brief 359, *HMP8171/HMP8173 Macrovision Registers* provides the details required.

# Analog Outputs

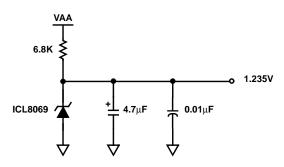

The HMP817x converts the video data into analog signals using four 10-bit DACs running at the CLK2 rate. The DACs output a current proportional to the digital data. The full scale output current is determined by the reference voltage VREF and an external resistor RSET. The full scale output current is given by:

$$I_{FULLSCALE}$$

(mA) = 3.9 \* VREF (V)/RSET (k $\Omega$ ) (EQ 1.)

VREF must be chosen such that it is within the part's operating range; RSET must be chosen such that the maximum output current is not exceeded.

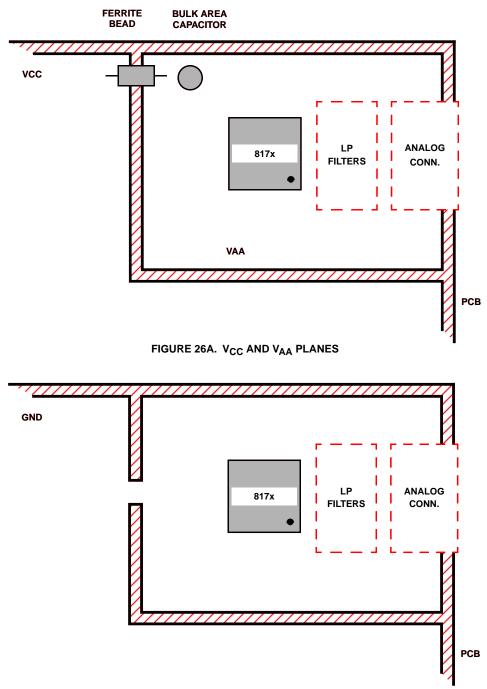

If the VREF pin is not connected, the HMP817x uses the internal reference voltage. Otherwise, the applied voltage overdrives the internal reference. If an external reference is used, it must decoupled from any power supply noise. An example external reference circuit is shown in the Applications section.

The HMP817x generates  $1V_{P-P}$  nominal video signals across  $37.5\Omega$  loads, corresponding to doubly terminated  $75\Omega$  lines. The encoder may also drive larger loads. The full scale output current and load must be chosen such that the maximum output voltage is not exceeded.

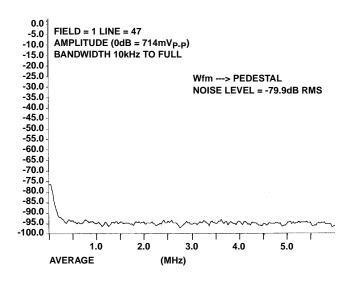

#### Output DAC Filtering

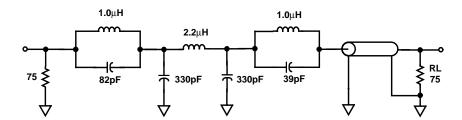

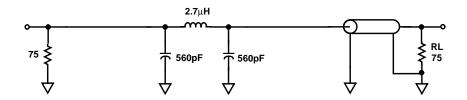

Since the DACs run at 2x the pixel sample rate, the  $\sin(x)/x$  rolloff of the outputs is greatly reduced, and there are fewer high frequency artifacts in the output spectrum. This allows using simple analog output filters. The analog output filter should be flat to  $F_8/4$  and have good rejection at  $3F_8/4$ . Example filters are shown in the Applications section.

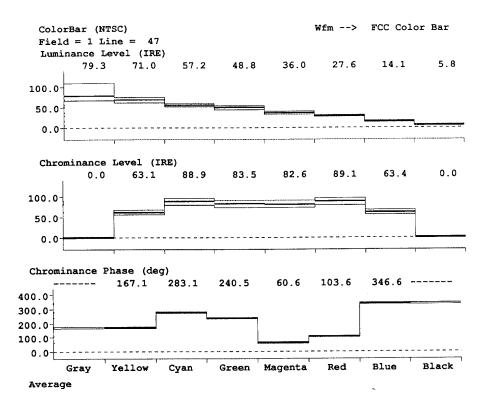

### Composite + Y/C Output Mode

The HMP817x provides composite with S-video output mode. When S-video outputs are selected, the encoder outputs the luminance, modulated chrominance, and two copies of the composite video signals. All four outputs are time aligned. The output pin assignments are summarized in Table 12.

#### Composite + RGB Output Mode

The HMP8172/HMP8173 also provide composite with component RGB output mode. When analog RGB video is selected, the HMP817x transforms the filtered 8:8:8 YCbCr data into 8:8:8 RGB data. The transform matrix uses different coefficients to generate NTSC or PAL video levels.

The analog RGB outputs have a range of 0.3-1.0V with an optional blanking pedestal. Composite sync information (0.0-0.3V) may be optionally added to the green output. VBI data is not included on the RGB outputs. The HMP817x also generates composite video when in RGB output mode. All four outputs are time aligned.

The HMP817x provides selectable pin outs for the RGB outputs. When the SCART compatibility bit is cleared, the analog composite video is output onto the NTSC/PAL 1 pin. Red information is output onto the NTSC/PAL 2 pin, blue information is output onto the C pin, and green information is output onto the Y pin.

When the bit is set, the analog composite video is output onto the Y pin. Red information is output onto the C pin, blue video is output on the NTSC/PAL 2 pin, and the green signal is output on the NTSC/PAL 1 pin. The output pin assignments are summarized in Table 12.

| <b>TARIF 12</b> | OUTPUT PIN | LASSIGNMENTS |

|-----------------|------------|--------------|

|            |      |                       | OUTPUT MODE (SCART SELECT BIT) |                     |                     |

|------------|------|-----------------------|--------------------------------|---------------------|---------------------|

| PIN NAME   | PIN# | COMP. WITH Y/C<br>(X) | COMP. W/ RGB<br>(0)            | COMP. W/ RGB<br>(1) | COMP. W/ YUV<br>(X) |

| Y          | 3    | Luma                  | Green                          | Composite           | Composite           |

| С          | 7    | Chroma                | Blue                           | Red                 | V                   |

| NTSC/PAL 1 | 11   | Composite             | Composite                      | Green               | Y                   |

| NTSC/PAL 2 | 15   | Composite             | Red                            | Blue                | U                   |

#### Composite + YUV Output Mode

The HMP8172/HMP8173 also provide composite with component YUV output mode. When analog YUV video is selected, the HMP817x scales the filtered YCbCr data to match the levels required by its DACs. During the scaling, values less than 16 are clamped to 16. The scaling factors for Cb and Cr are the same, but the CbCr scaling factor is different from the Y scaling factor. The encoder uses different sets of scale factors for NTSC and PAL to accommodate their different black levels.

The analog YUV outputs have a range of 0.3-1.0V with an optional blanking pedestal. Composite sync information (0.0-0.3V) may be optionally added to the Y output. VBI data is included on the Y output. The HMP817x also generates composite video when in YUV output mode. All four outputs are time aligned. The output pin assignments are summarized in Table 12.

#### **Power Down Modes**

To reduce power dissipation, any of the four output DACs may be turned off. Each DAC has an independent enable bit. Each output may be disabled in the host control register.

When the power down mode is enabled, all of the DACs and internal voltage reference are powered down (forcing their outputs to zero) and the data pipeline registers are disabled. The host processor may still read from and write to the internal control registers.

#### Host Interfaces

#### Reset

The HMP817x resets to its default operating mode on power up, when the reset pin is asserted for at least four CLK cycles, or when the software reset bit of the host control register is set. During the reset cycle, the encoder returns its internal registers to their reset state and deactivates the I<sup>2</sup>C interface.

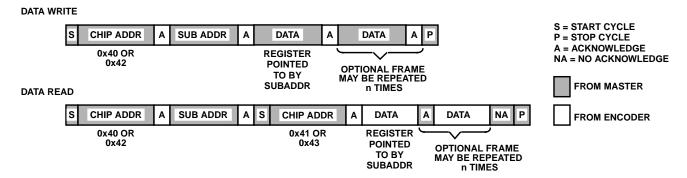

#### I<sup>2</sup>C Interface

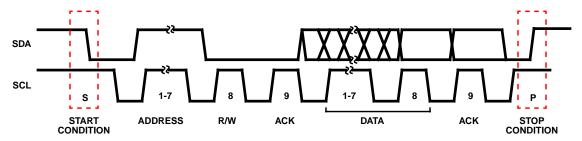

The HMP817x provides a standard  $I^2C$  interface and supports fast-mode (up to 400Kbps) transfers. The device acts as a slave for receiving and transmitting data only. It will not respond to general calls or initiate a transfer. The encoder's slave address is either  $0100\ 000x_B$  when the SA input pin is low or  $0100\ 001x_B$  when it is high. (The 'x' bit in the address is the  $I^2C$  read flag.)

The  $I^2C$  interface consists of the SDA and SCL pins. When the interface is not active, SCL and SDA must be pulled high using external 4-6k $\Omega$  pull-up resistors. The  $I^2C$  clock and data timing is shown in Figures 10 and 11.

During I<sup>2</sup>C write cycles, the first data byte after the slave address specifies the sub address, and is written into the address register. Only the seven LSBs of the subaddress are used; the MSB is ignored. Any remaining data bytes in the

I<sup>2</sup>C write cycle are written to the control registers, beginning with the register specified by the address register. The 7-bit address register is incremented after each data byte in the I<sup>2</sup>C write cycle. Data written to reserved bits within registers or reserved registers is ignored.

During  $I^2C$  read cycles, data from the control register specified by the address register is output. The address register is incremented after each data byte in the  $I^2C$  read cycle. Reserved bits within registers return a value of "0". Reserved registers return a value of  $00_H$ .

The HMP817x's operating modes are determined by the contents of its internal registers which are accessed via the I<sup>2</sup>C interface. All internal registers may be written or read by the host processor at any time. However, some of the bits and words are read only or reserved and data written to these bits is ignored.

Table 13 lists the HMP817x's internal registers. Their bit descriptions are listed in Tables 14 through 45.

**TABLE 13. CONTROL REGISTER NAMES**

| SUB ADDRESS<br>(HEX) | CONTROL REGISTER   | RESET CONDITION |

|----------------------|--------------------|-----------------|

| 00                   | product ID         | -               |

| 01                   | output format      | 00 <sub>H</sub> |

| 02                   | input format       | 06 <sub>H</sub> |

| 03                   | video processing   | 80 <sub>H</sub> |

| 04                   | timing I/O 1       | 00 <sub>H</sub> |

| 05                   | timing I/O 2       | 00H             |

| 06                   | VBI data enable    | 00 <sub>H</sub> |

| 07                   | VBI data input     | 00 <sub>H</sub> |

| 08-0D                | reserved           |                 |

| 0E                   | host control 1     | 1E <sub>H</sub> |

| 0F                   | host control 2     | 00 <sub>H</sub> |

| 10                   | caption_21A        | 80 <sub>H</sub> |

| 11                   | caption_21B        | 80 <sub>H</sub> |

| 12                   | caption_284A       | 80 <sub>H</sub> |

| 13                   | caption_284B       | 80 <sub>H</sub> |

| 14                   | WSS_20A            | 00 <sub>H</sub> |

| 15                   | WSS_20B            | 00 <sub>H</sub> |

| 16                   | WSS_283A           | 00 <sub>H</sub> |

| 17                   | WSS_283B           | 00 <sub>H</sub> |

| 18                   | CRC_20             | 3F <sub>H</sub> |

| 19                   | CRC_283            | 3F <sub>H</sub> |

| 1A-1F                | reserved           | -               |

| 20                   | start h_blank low  | 4A <sub>H</sub> |

| 21                   | start h_blank high | 03 <sub>H</sub> |

| 22                   | end h_blank        | 7A <sub>H</sub> |

| 23                   | start v_blank low  | 03 <sub>H</sub> |

| 24                   | start v_blank high | 01 <sub>H</sub> |

| 25                   | end v_blank        | 13 <sub>H</sub> |

| 26                   | field control 1    | 00 <sub>H</sub> |

| 27                   | field control 2    | 00 <sub>H</sub> |

| 28-2F                | reserved           | -               |

| 30-6A                | test and unused    | -               |

| 6B-6F                | phase increment    | -               |

| 70-7F                | test and unused    | -               |

FIGURE 10. I<sup>2</sup>C SERIAL TIMING FLOW

FIGURE 11. REGISTER WRITE PROGRAMMING FLOW

**TABLE 14. PRODUCT ID REGISTER**

|               | SUB ADDRESS = 00 <sub>H</sub> |                                                                                                                                     |                          |  |

|---------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| BIT<br>NUMBER | FUNCTION                      | DESCRIPTION                                                                                                                         | RESET<br>STATE           |  |

| 7-0           | Product ID                    | This 8-bit register specifies the last two digits of the product number. It is a read-only register. Data written to it is ignored. | 70H<br>71H<br>72H<br>73H |  |

### TABLE 15. OUTPUT FORMAT REGISTER

|               | SUB ADDRESS = 01 <sub>H</sub> |                                                                                                                                                                                                                                                                                   |                |  |

|---------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| BIT<br>NUMBER | FUNCTION                      | DESCRIPTION                                                                                                                                                                                                                                                                       | RESET<br>STATE |  |

| 7-5           | Video Timing<br>Standard      | 000 = (M) NTSC<br>001 = reserved<br>010 = (B, D, G, H, I) PAL<br>011 = (M) PAL<br>100 = (N) PAL<br>101 = (NC) PAL<br>110 = reserved<br>111 = reserved                                                                                                                             | 000B           |  |

| 4-3           | Output Format                 | 00 = Composite + Y/C 01 = Composite + YUV (HMP8172 and HMP8173 only) 10 = Composite + RGB without sync on green (HMP8172 and HMP8173 only) 11 = Composite + RGB with sync on green (HMP8172 and HMP8173 only)                                                                     | 00B            |  |

| 2-0           | NTSC / PAL<br>Setup Select    | These bits specify the blanking pedestal during active video, from 0 IRE ("000") to 7.5 IRE ("111"). Typically, these bits should be a "111" during (M) NTSC and (M, N) PAL operation. Otherwise, they should be a "000". These bits do not affect the analog RGB or YUV outputs. | 111B           |  |

# TABLE 16. INPUT FORMAT REGISTER

| SUB ADDRESS = 02 <sub>H</sub> |              |                                                                                                                                                                     |                    |

|-------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| BIT<br>NUMBER                 | FUNCTION     | DESCRIPTION                                                                                                                                                         | RESET<br>STATE     |

| 7-5                           | Input Format | 000 = 16-bit 4:2:2 YCbCr<br>001 = 8-bit 4:2:2 YCbCr<br>010 = 8-bit BT.656<br>011 = Reserved<br>100 = Reserved<br>101 = Reserved<br>110 = Reserved<br>111 = Reserved | 000 <sub>B</sub>   |

| 4 - 0                         | Reserved     |                                                                                                                                                                     | 00000 <sub>B</sub> |

### TABLE 17. VIDEO PROCESSING REGISTER

|               | SUB ADDRESS = 03 <sub>H</sub> |                                                                                                                                                                                                                                                                                                    |                  |  |

|---------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| BIT<br>NUMBER | FUNCTION                      | DESCRIPTION                                                                                                                                                                                                                                                                                        | RESET<br>STATE   |  |

| 7             | Luminance<br>Processing       | 0 = None<br>1 = Y Lowpass filtering enabled                                                                                                                                                                                                                                                        | 1 <sub>B</sub>   |  |

| 6             | Composite Video<br>Limiting   | 0 = None<br>1 = Lower limit of composite active video is about half the sync height                                                                                                                                                                                                                | 0 <sub>B</sub>   |  |

| 5             | SCH Phase<br>Mode             | 0 = Never reset SCH phase<br>1 = Reset SCH phase every 4 (NTSC) or 8 (PAL) fields                                                                                                                                                                                                                  | 1 <sub>B</sub>   |  |

| 4             | RGB / YUV<br>Setup Select     | This bits specifies the blanking pedestal on the analog RGB and YUV outputs during active video. Typically, this bit should be a "1" during (M) NTSC and (M, N) PAL operation. Otherwise, it should be a "0". This bit does not affect the analog composite or Y/C outputs.  0 = 0 IRE 1 = 7.5 IRE | 0 <sub>B</sub>   |  |

| 3             | RGB Output<br>Pins Select     | This bit configures on what pins the analog RGB video is output.  0 = HMP8156 compatible  1 = SCART compatible                                                                                                                                                                                     | 0 <sub>B</sub>   |  |

| 2-0           | Reserved                      |                                                                                                                                                                                                                                                                                                    | 000 <sub>B</sub> |  |

# TABLE 18. TIMING I/O REGISTER #1

|               | SUB ADDRESS = 04 <sub>H</sub>  |                                                                                                                                                                                                                                                                                                 |                |

|---------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| BIT<br>NUMBER | FUNCTION                       | DESCRIPTION                                                                                                                                                                                                                                                                                     | RESET<br>STATE |

| 7             | BLANK<br>Timing Select         | This bit is ignored unless BLANK is configured to be an output.  0 = Data for the first active pixel of the scan line must arrive the CLK cycle after the encoder negates BLANK.  1 = Data for the first active pixel of the scan line must arrive immediately after the encoder negates BLANK. | 0 <sub>B</sub> |

| 6             | Reserved                       |                                                                                                                                                                                                                                                                                                 | 0 <sub>B</sub> |

| 5             | BLANK Output<br>Control        | 0 = BLANK is an input<br>1 = BLANK is an output                                                                                                                                                                                                                                                 | 0 <sub>B</sub> |

| 4             | BLANK<br>Polarity              | 0 = Active low (low during blanking) 1 = Active high (high during blanking)                                                                                                                                                                                                                     | 0 <sub>B</sub> |

| 3             | HSYNC and VSYNC Output Control | 0 = HSYNC and VSYNC are inputs 1 = HSYNC and VSYNC are outputs                                                                                                                                                                                                                                  | 0 <sub>B</sub> |

| 2             | HSYNC<br>Polarity              | 0 = Active low (low during horizontal sync) 1 = Active high (high during horizontal sync)                                                                                                                                                                                                       | 0 <sub>B</sub> |

| 1             | VSYNC<br>Polarity              | 0 = Active low (low during vertical sync) 1 = Active high (high during vertical sync)                                                                                                                                                                                                           | 0 <sub>B</sub> |

| 0             | FIELD<br>Polarity              | 0 = Active low (low during odd fields) 1 = Active high (high during odd fields)                                                                                                                                                                                                                 | 0 <sub>B</sub> |

# TABLE 19. TIMING I/O REGISTER #2

|               | SUB ADDRESS = 05 <sub>H</sub> |                                                                                                                                                                                                    |                 |  |

|---------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| BIT<br>NUMBER | FUNCTION                      | DESCRIPTION                                                                                                                                                                                        | RESET<br>STATE  |  |

| 7-6           | Reserved                      |                                                                                                                                                                                                    | 00 <sub>B</sub> |  |

| 5             | CLK Polarity Control          | 0 = Inputs are sampled when CLK is low (see Table 2). 1 = Inputs are sampled when CLK is high.                                                                                                     | 0 <sub>B</sub>  |  |

| 4             | CLK Output Control            | 0 = CLK is an input<br>1 = CLK is an output                                                                                                                                                        | 0 <sub>B</sub>  |  |

| 3             | Aspect Ratio Mode             | This bit must be set to "0" during BT.656 input mode.  0 = Rectangular (BT.601) pixels  1 = Square pixels                                                                                          | 0 <sub>B</sub>  |  |

| 2             | Reserved                      |                                                                                                                                                                                                    | 0 <sub>B</sub>  |  |

| 1-0           | Subcarrier PHINC<br>Select    | Selects the source of the color subcarrier NCO phase increment value.  00 = Internal (fixed) data.  01 = Reserved  10 = BT.656 RTCI ancillary data  11 = I <sup>2</sup> C interface PHINC register | 00B             |  |

#### TABLE 20. AUXILIARY DATA ENABLE REGISTER

|               |                             | SUB ADDRESS = 06 <sub>H</sub>                                                                                                                                                                                                                                                                                                                       |                 |

|---------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BIT<br>NUMBER | FUNCTION                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         | RESET<br>STATE  |

| 7-6           | Closed Captioning<br>Enable | 00 = Closed caption disabled 01 = Closed caption enabled for odd fields: line 21 for NTSC, line 18 for (M) PAL, or line 22 for (B, D, G, H, I, N, NC) PAL 10 = Closed caption enabled for even fields: line 284 for NTSC, line 281 for (M) PAL, or line 335 for (B, D, G, H, I, N, NC) PAL 11 = Closed caption enabled for both odd and even fields | 00 <sub>B</sub> |

| 5-4           | WSS Enable                  | 00 = WSS disabled<br>01 = WSS enabled for odd fields: line 20 for NTSC; line 17 for (M) PAL, or line 23 for (B, D, G,<br>H, I, N, NC) PAL<br>10 = WSS enabled for even fields: line 283 for NTSC, line 280 for (M) PAL, or line 336 for (B,<br>D, G, H, I, N, NC) PAL<br>11 = WSS enabled for both odd and even fields                              | 00 <sub>B</sub> |

| 3             | Teletext Enable             | 00 = Teletext disabled<br>01 = System B teletext enabled<br>10 = System C teletext enabled<br>11 = reserved                                                                                                                                                                                                                                         | 00 <sub>B</sub> |

| 1-0           | Reserved                    |                                                                                                                                                                                                                                                                                                                                                     | 00 <sub>B</sub> |

# TABLE 21. VBI DATA INPUT REGISTER

| SUB ADDRESS = 07H |                                             |                                                                                                                                                                                                                               |                   |

|-------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| BIT<br>NUMBER     | FUNCTION                                    | DESCRIPTION                                                                                                                                                                                                                   | RESET<br>STATE    |

| 7                 | Closed Caption<br>Line 21<br>BT.656 Enable  | Setting this bit enables BT.656 ancillary data to be written into the closed caption line 21 data registers. It is ignored unless in the BT.656 input mode.  0 = Ignore BT.656 ancillary data 1 = Use BT.656 ancillary data   | 0 <sub>B</sub>    |

| 6                 | Closed Caption<br>Line 284<br>BT.656 Enable | Setting this bit enables BT.656 ancillary data to be written into the closed caption line 284 data registers. It is ignored unless in the BT.656 input mode.  0 = Ignore BT.656 ancillary data  1 = Use BT.656 ancillary data | 0 <sub>B</sub>    |

| 5                 | WSS Line 20<br>BT.656 Enable                | Setting this bit enables BT.656 ancillary data to be written into the WSS line 20 data registers. It is ignored unless in the BT.656 input mode.  0 = Ignore BT.656 ancillary data  1 = Use BT.656 ancillary data             | 0 <sub>B</sub>    |

| 4                 | WSS Line 283<br>BT.656 Enable               | Setting this bit enables BT.656 ancillary data to be written into the WSS line 283 data registers. It is ignored unless in the BT.656 input mode.  0 = Ignore BT.656 ancillary data  1 = Use BT.656 ancillary data            | 0 <sub>B</sub>    |

| 3-0               | Reserved                                    |                                                                                                                                                                                                                               | 0000 <sub>B</sub> |

### **TABLE 22. HOST CONTROL REGISTER 1**

| SUB ADDRESS = 0E <sub>H</sub> |                                            |                                                                                                                                                       |                  |

|-------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| BIT<br>NUMBER                 | FUNCTION                                   | DESCRIPTION                                                                                                                                           | RESET<br>STATE   |

| 7-5                           | Reserved                                   |                                                                                                                                                       | 000 <sub>B</sub> |

| 4                             | Closed Caption<br>Line 21<br>Write Status  | 0 = Caption_21A and Caption_21B data registers contain unused data 1 = Data has been output, host processor may now write to the registers            | 1 <sub>B</sub>   |

| 3                             | Closed Caption<br>Line 284<br>Write Status | 0 = Caption_284A and Caption_284B data registers contain unused data 1 = Data has been output, host processor may now write to the registers          | 1 <sub>B</sub>   |

| 2                             | WSS<br>Line 20<br>Write Status             | 0 = WSS_20A, WSS_20B, CRC_20A, and CRC_20B data registers contain unused data 1 = Data has been output, host processor may now write to the registers | 1 <sub>B</sub>   |

| 1                             | WSS<br>Line 283<br>Write Status            | 0 = WSS_283A and WSS_283B data registers contain unused data<br>1 = Data has been output, host processor may now write to the registers               | 1 <sub>B</sub>   |

| 0                             | Reserved                                   |                                                                                                                                                       | 0 <sub>B</sub>   |

#### **TABLE 23. HOST CONTROL REGISTER 2**

|               | SUB ADDRESS = 0F <sub>H</sub>          |                                                                                                                              |                 |

|---------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BIT<br>NUMBER | FUNCTION                               | DESCRIPTION                                                                                                                  | RESET<br>STATE  |

| 7             | Software Reset                         | Setting this bit to "1" initiates a software reset. It is automatically reset to a "0" after the reset sequence is complete. | 0 <sub>B</sub>  |

| 6             | General<br>Power Down                  | This bit powers down all DAC outputs and most of the digital circuitry.  0 = Normal operation  1 = Power down mode           | 0 <sub>B</sub>  |

| 5             | Power Down<br>NTSC/PAL 1<br>Output DAC | This bit powers down only the NTSC/PAL 1 DAC output.  0 = Normal operation  1 = Power down mode                              | 0 <sub>B</sub>  |

| 4             | Power Down<br>NTSC/PAL 2<br>Output DAC | This bit powers down only the NTSC/PAL 2 DAC output.  0 = Normal operation  1 = Power down mode                              | 0 <sub>B</sub>  |

| 3             | Power Down<br>Y Output DAC             | This bit powers down only the Y DAC output.  0 = Normal operation  1 = Power down mode                                       | 0 <sub>B</sub>  |

| 2             | Power Down<br>C Output DAC             | This bit powers down only the C DAC output.  0 = Normal operation  1 = Power down mode                                       | 0 <sub>B</sub>  |

| 1-0           | Reserved                               |                                                                                                                              | 00 <sub>B</sub> |

#### TABLE 24. CLOSED CAPTION\_21A DATA REGISTER

| SUB ADDRESS = 10 <sub>H</sub> |                             |                                                                                                                                                                                                                                 |                 |  |

|-------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| BIT<br>NUMBER                 |                             |                                                                                                                                                                                                                                 |                 |  |