HI5810

# CMOS 10 Microsecond, 12-Bit, Sampling A/D Converter with Internal Track and Hold

August 1997

| Features                      |

|-------------------------------|

|                               |

| • Throughput Rate             |

| Built-In Track and Hold       |

| Single Supply Voltage         |

| Maximum Power Consumption40mW |

| Internal or External Clock    |

| • 1MHz Input Bandwidth3dB     |

|                               |

## **Applications**

- Remote Low Power Data Acquisition Systems

- Digital Audio

- DSP Modems

- General Purpose DSP Front End

- μP Controlled Measurement Systems

- Process Controls

- Industrial Controls

## Description

The HI5810 is a fast, low power, 12-bit, successive-approximation, analog-to-digital converter. It can operate from a single 3V to 6V supply and typically draws just 1.9mA when operating at 5V. The HI5810 features a built-in track and hold. The conversion time is as low as 10µs with a 5V supply.

The twelve data outputs feature full high speed CMOS three-state bus driver capability, and are latched and held through a full conversion cycle. The output is user selectable: [i.e., 12-bit, 8-bit (MSBs), and/or 4-bit (LSBs)]. A data ready flag, and conversion-start input complete the digital interface.

An internal clock is provided and is available as an output. The clock may also be over-driven by an external source.

### **Ordering Information**

| PART<br>NUMBER | INL (LSB)<br>(MAX OVER<br>TEMP.) | TEMP.<br>RANGE<br>(°C) | PACKAGE      | PKG.<br>NO. |

|----------------|----------------------------------|------------------------|--------------|-------------|

| HI5810JIP      | ±2.5                             | -40 to 85              | 24 Ld PDIP   | E24.3       |

| HI5810KIP      | ±2.0                             | -40 to 85              | 24 Ld PDIP   | E24.3       |

| HI5810JIB      | ±2.5                             | -40 to 85              | 24 Ld SOIC   | M24.3       |

| HI5810KIB      | ±2.0                             | -40 to 85              | 24 Ld SOIC   | M24.3       |

| HI5810JIJ      | ±2.5                             | -40 to 85              | 24 Ld CERDIP | F24.3       |

| HI5810KIJ      | ±2.0                             | -40 to 85              | 24 Ld CERDIP | F24.3       |

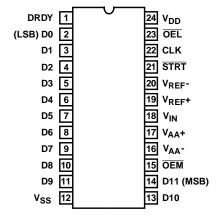

#### **Pinout**

HI5810 (PDIP, CERDIP, SOIC) TOP VIEW

#### HI5810

## Absolute Maximum Ratings

##

## Operating Conditions

| Temperature Range               |              |

|---------------------------------|--------------|

| PDIP. SOIC, and CERDIP Packages | 40°C to 85°C |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1) CERDIP Package | θ <sub>JA</sub> ( <sup>o</sup> C/W)<br>60<br>80 | θ <sub>JC</sub> ( <sup>o</sup> C/W)<br>12<br>N/A |

|-----------------------------------------------------|-------------------------------------------------|--------------------------------------------------|

| PDIP Package                                        | 80                                              |                                                  |

| SOIC Package                                        | 75                                              | N/A                                              |

| Maximum Junction Temperature                        |                                                 |                                                  |

| Plastic Packages                                    |                                                 | 150 <sup>o</sup> C                               |

| Hermetic Package                                    |                                                 | 175 <sup>0</sup> C                               |

| Maximum Storage Temperature Range                   | 65                                              | 5°C to 150°C                                     |

| Maximum Lead Temperature (Soldering, 1              | I0s)                                            | 300°C                                            |

| (SOIC - Lead Tips Only)                             |                                                 |                                                  |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **Electrical Specifications**

$V_{DD} = V_{AA} + = 5V$ ,  $V_{REF} + = +4.608V$ ,  $V_{SS} = V_{AA} - = V_{REF} - = GND$ , CLK = External 1.5MHz, Unless Otherwise Specified

| PARAMETER                                  |   |                                                                            |     | 25°C           |      | -40°C 1 |      |            |

|--------------------------------------------|---|----------------------------------------------------------------------------|-----|----------------|------|---------|------|------------|

|                                            |   | TEST CONDITIONS                                                            | MIN | TYP            | МАХ  | MIN     | МАХ  | UNITS      |

| ACCURACY                                   |   |                                                                            |     | •              | •    |         | •    |            |

| Resolution                                 |   |                                                                            | 12  | -              | -    | 12      | -    | Bits       |

| Integral Linearity Error, INL              | J |                                                                            | -   | -              | ±2.5 | -       | ±2.5 | LSB        |

| (End Point)                                | K |                                                                            | -   | -              | ±2.0 | -       | ±2.0 | LSB        |

| Differential Linearity Error, DNL          | J |                                                                            | -   | -              | ±2.0 | -       | ±2.0 | LSB        |

|                                            | K |                                                                            | -   | -              | ±2.0 | -       | ±2.0 | LSB        |

| Gain Error, FSE                            | J |                                                                            | -   | -              | ±3.5 | -       | ±3.5 | LSB        |

| (Adjustable to Zero)                       | K |                                                                            | -   | -              | ±2.5 | -       | ±2.5 | LSB        |

| Offset Error, V <sub>OS</sub>              | J |                                                                            | -   | -              | ±2.5 | -       | ±2.5 | LSB        |

| (Adjustable to Zero)                       | K |                                                                            | -   | -              | ±1.5 | -       | ±1.5 | LSB        |

| DYNAMIC CHARACTERISTICS                    |   |                                                                            |     |                |      |         |      |            |

| Signal to Noise Ratio, SINAD<br>RMS Signal | J | $f_S$ = Internal Clock, $f_{ N}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{ N}$ = 1kHz | -   | 68.8<br>62.1   | -    | -       | -    | dB<br>dB   |

| RMS Noise + Distortion                     | K | $f_S$ = Internal Clock, $f_{ N}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{ N}$ = 1kHz | -   | 71.0<br>63.6   | -    | -       | -    | dB<br>dB   |

| Signal to Noise Ratio, SNR<br>RMS Signal   | J | $f_S$ = Internal Clock, $f_{IN}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{IN}$ = 1kHz | -   | 70.5<br>63.2   | -    | -       | -    | dB<br>dB   |

| RMS Noise                                  | K | $f_S$ = Internal Clock, $f_{ N}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{ N}$ = 1kHz | -   | 71.5<br>65.0   | -    | -       | -    | dB<br>dB   |

| Total Harmonic Distortion, THD             | J | $f_S$ = Internal Clock, $f_{ N}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{ N}$ = 1kHz | -   | -73.9<br>-68.4 | -    | -       | -    | dBc<br>dBc |

|                                            | K | $f_S$ = Internal Clock, $f_{ N}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{ N}$ = 1kHz | -   | -80.3<br>69.7  | -    | -       | -    | dBc<br>dBc |

| Spurious Free Dynamic Range, SFDR          | J | $f_S$ = Internal Clock, $f_{ N}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{ N}$ = 1kHz | -   | 75.4<br>69.2   | -    | -       | -    | dB<br>dB   |

|                                            |   | $f_S$ = Internal Clock, $f_{ N}$ = 1kHz<br>$f_S$ = 1.5MHz, $f_{ N}$ = 1kHz | -   | 80.9<br>70.7   | -    | -       | -    | dB<br>dB   |

| ANALOG INPUT                               |   |                                                                            | -   | •              | •    |         | -    |            |

| Input Current, Dynamic                     |   | At V <sub>IN</sub> = V <sub>REF</sub> +, 0V                                | -   | ±125           | ±150 | -       | ±150 | μΑ         |

## HI5810

|                                                                                        |                                          |          | 25°C |     | -40°C 1 |     |          |

|----------------------------------------------------------------------------------------|------------------------------------------|----------|------|-----|---------|-----|----------|

| PARAMETER                                                                              | TEST CONDITIONS                          | MIN      | TYP  | МАХ | MIN     | MAX | UNITS    |

| Input Current, Static                                                                  | Conversion Stopped                       | -        | ±0.6 | ±10 | -       | ±10 | μΑ       |

| Input Bandwidth -3dB                                                                   |                                          | -        | 1    | -   | -       | -   | MHz      |

| Reference Input Current                                                                |                                          | -        | 160  | -   | -       | -   | μΑ       |

| Input Series Resistance, R <sub>S</sub>                                                | In Series with Input C <sub>SAMPLE</sub> | -        | 420  | -   | -       | -   | Ω        |

| Input Capacitance, C <sub>SAMPLE</sub>                                                 | During Sample State                      | -        | 380  | -   | -       | -   | pF       |

| Input Capacitance, C <sub>HOLD</sub>                                                   | During Hold State                        | -        | 20   | -   | -       | -   | pF       |

| DIGITAL INPUTS OEL, OEM, STRT                                                          | •                                        | -        |      |     | •       | •   |          |

| High-Level Input Voltage, VIH                                                          |                                          | 2.4      | -    | -   | 2.4     | -   | V        |

| Low-Level Input Voltage, VIL                                                           |                                          | -        | -    | 0.8 | -       | 0.8 | V        |

| Input Leakage Current, I <sub>IL</sub>                                                 | Except CLK, V <sub>IN</sub> = 0V, 5V     | -        | -    | ±10 | -       | ±10 | μΑ       |

| Input Capacitance, C <sub>IN</sub>                                                     |                                          | -        | 10   | -   | -       | -   | pF       |

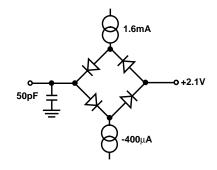

| DIGITAL OUTPUTS                                                                        | -                                        | <b>E</b> |      |     | •       |     |          |

| High-Level Output Voltage, VOH                                                         | I <sub>SOURCE</sub> = -400μA             | 4.6      | -    | -   | 4.6     | -   | V        |

| Low-Level Output Voltage, V <sub>OL</sub>                                              | I <sub>SINK</sub> = 1.6mA                | -        | -    | 0.4 | -       | 0.4 | V        |

| Three-State Leakage, I <sub>OZ</sub>                                                   | Except DRDY, V <sub>OUT</sub> = 0V, 5V   | -        | -    | ±10 | -       | ±10 | μΑ       |

| Output Capacitance, C <sub>OUT</sub>                                                   | Except DRDY                              | -        | 20   | -   | -       | -   | pF       |

| CLOCK                                                                                  |                                          | <b>E</b> | •    |     |         |     |          |

| High-Level Output Voltage, VOH                                                         | I <sub>SOURCE</sub> = -100μA (Note 2)    | 4        | -    | -   | 4       | -   | V        |

| Low-Level Output Voltage, V <sub>OL</sub>                                              | I <sub>SINK</sub> = 100μA (Note 2)       | -        | -    | 1   | -       | 1   | V        |

| Input Current                                                                          | CLK Only, V <sub>IN</sub> = 0V, 5V       | -        | -    | ±5  | -       | ±5  | mA       |

| TIMING                                                                                 | -                                        |          |      |     | •       |     |          |

| Conversion Time (t <sub>CONV</sub> + t <sub>ACQ</sub> )<br>(Includes Acquisition Time) |                                          | 10       | -    | -   | 10      | -   | μs       |

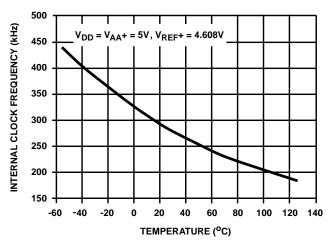

| Clock Frequency                                                                        | Internal Clock, (CLK = Open)             | 200      | 300  | 400 | 150     | 500 | kHz      |

|                                                                                        | External CLK (Note 2)                    | 0.05     | -    | 2.0 | -       | -   | MHz      |

| Clock Pulse Width, t <sub>LOW</sub> , t <sub>HIGH</sub>                                | External CLK (Note 2)                    | 100      | -    | -   | 100     | -   | ns       |

| Aperture Delay, t <sub>D</sub> APR                                                     | (Note 2)                                 | -        | 35   | 50  | -       | 70  | ns       |

| Clock to Data Ready Delay, t <sub>D1</sub> DRDY                                        | (Note 2)                                 | -        | 105  | 150 | -       | 180 | ns       |

| Clock to Data Ready Delay, t <sub>D2</sub> DRDY                                        | (Note 2)                                 | -        | 100  | 160 | -       | 195 | ns       |

| Start Removal Time, t <sub>R</sub> STRT                                                | (Note 2)                                 | 75       | 30   | -   | 75      | -   | ns       |

| Start Setup Time, t <sub>SU</sub> STRT                                                 | (Note 2)                                 | 85       | 60   | -   | 100     | -   | ns       |

| Start Pulse Width, t <sub>W</sub> STRT                                                 | (Note 2)                                 | 10       | 4    | -   | 15      | -   | ns       |

| Start to Data Ready Delay, t <sub>D3</sub> DRDY                                        | (Note 2)                                 | -        | 65   | 105 | -       | 120 | ns       |

| Clock Delay from Start, t <sub>D</sub> STRT                                            | (Note 2)                                 | -        | 60   | -   | -       | -   | ns       |

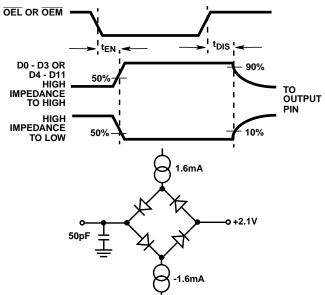

| Output Enable Delay, t <sub>EN</sub>                                                   | (Note 2)                                 | -        | 20   | 30  | -       | 50  | ns       |

| Output Disabled Delay, t <sub>DIS</sub>                                                | (Note 2)                                 | -        | 80   | 95  | -       | 120 | ns       |

| POWER SUPPLY CHARACTERISTICS                                                           | 1                                        |          |      |     |         | !   | •        |

| Supply Current, I <sub>DD</sub> + I <sub>AA</sub>                                      |                                          | T -      | 2.6  | 8   | -       | 8.5 | mA       |

| NOTE:                                                                                  |                                          |          |      |     |         |     | <u>`</u> |

NOTE:

2. Parameter guaranteed by design or characterization, not production tested.

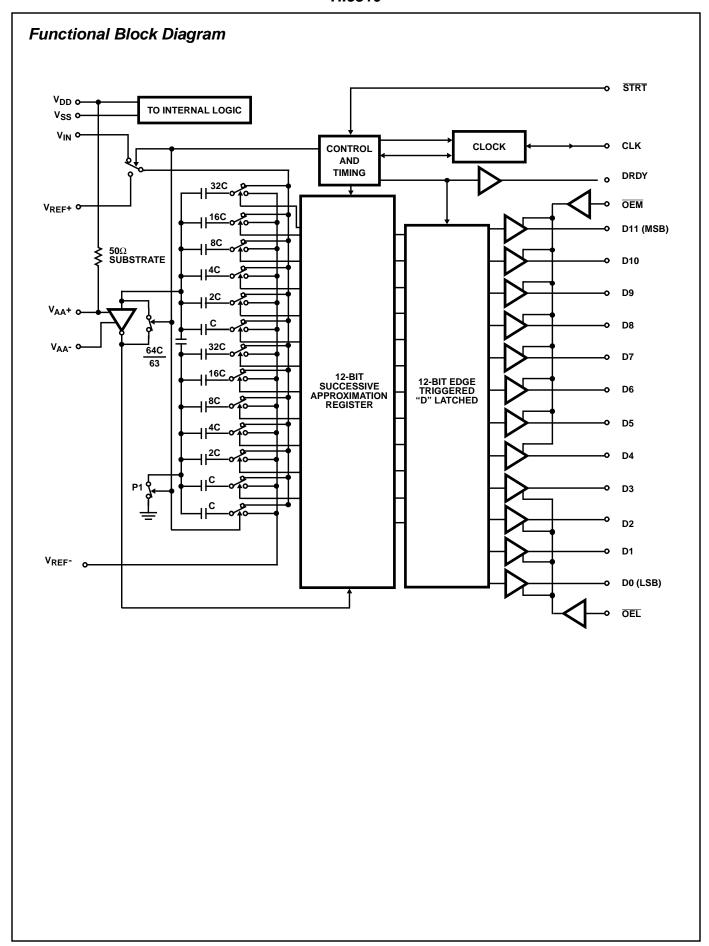

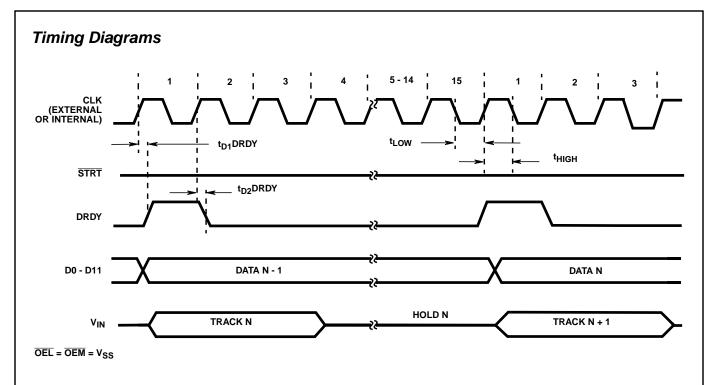

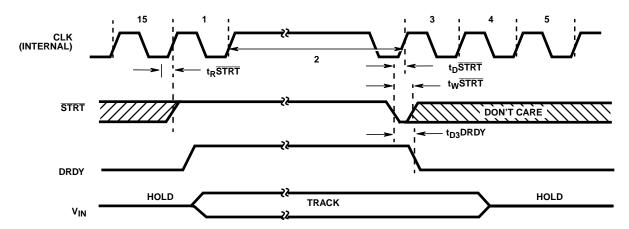

FIGURE 1. CONTINUOUS CONVERSION MODE

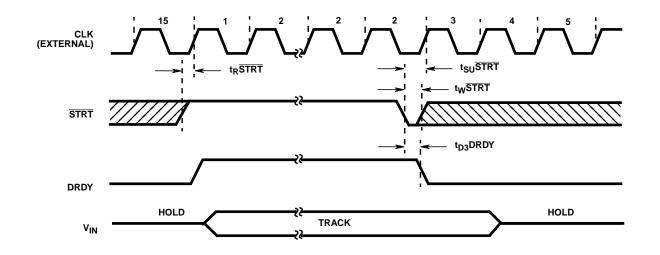

FIGURE 2. SINGLE SHOT MODE EXTERNAL CLOCK

## Timing Diagrams (Continued)

FIGURE 3. SINGLE SHOT MODE INTERNAL CLOCK

FIGURE 5. TIMING LOAD CIRCUIT

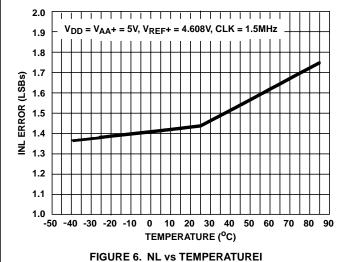

## **Typical Performance Curves**

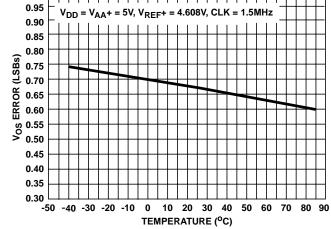

FIGURE 7. OFFSET ERROR vs TEMPERATURE

1.00

-1.0

-1.1

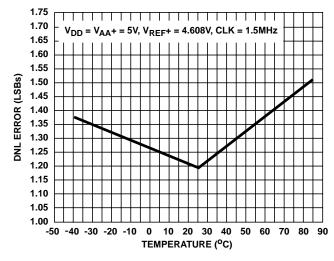

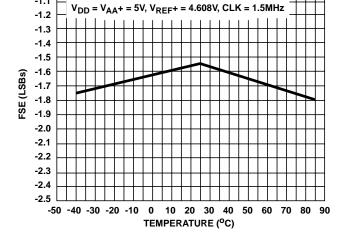

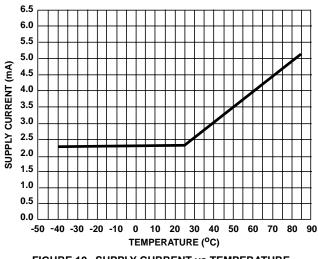

## Typical Performance Curves (Continued)

#### FIGURE 8. DNL vs TEMPERATURE

FIGURE 9. FULL SCALE ERROR vs TEMPERATURE

FIGURE 10. SUPPLY CURRENT vs TEMPERATURE

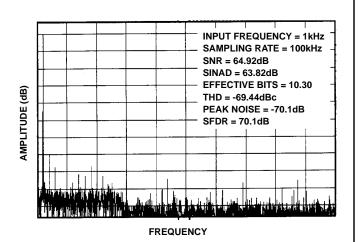

FIGURE 11. FFT SPECTRUM

FIGURE 12. INTERNAL CLOCK FREQUENCY vs TEMPERATURE

**TABLE 1. PIN DESCRIPTIONS**

| PIN NO. | NAME               | DESCRIPTION                                                                                                                       |

|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1       | DRDY               | Output flag signifying new data is available.<br>Goes high at end of clock period 15. Goes low<br>when new conversion is started. |

| 2       | D0                 | Bit-0 (Least Significant Bit, LSB).                                                                                               |

| 3       | D1                 | Bit 1.                                                                                                                            |

| 4       | D2                 | Bit 2.                                                                                                                            |

| 5       | D3                 | Bit 3.                                                                                                                            |

| 6       | D4                 | Bit 4.                                                                                                                            |

| 7       | D5                 | Bit 5.                                                                                                                            |

| 8       | D6                 | Bit 6.                                                                                                                            |

| 9       | D7                 | Bit 7.                                                                                                                            |

| 10      | D8                 | Bit 8.                                                                                                                            |

| 11      | D9                 | Bit 9.                                                                                                                            |

| 12      | V <sub>SS</sub>    | Digital Ground, (0V).                                                                                                             |

| 13      | D10                | Bit 10.                                                                                                                           |

| 14      | D11                | Bit 11 (Most Significant Bit, MSB)                                                                                                |

| 15      | OEM                | Three-State Enable for D4-D11. Active low input.                                                                                  |

| 16      | V <sub>AA</sub> -  | Analog Ground, (0V).                                                                                                              |

| 17      | V <sub>AA</sub> +  | Analog Positive Supply. (+5V) (See text.)                                                                                         |

| 18      | V <sub>IN</sub>    | Analog Input.                                                                                                                     |

| 19      | V <sub>REF</sub> + | Reference Voltage Positive Input, sets 4095 code end of input range.                                                              |

| 20      | V <sub>REF</sub> - | Reference Voltage Negative Input, sets 0 code end of input range.                                                                 |

| 21      | STRT               | Start Conversion Input active low, recognized after end of clock period 15.                                                       |

| 22      | CLK                | CLK Input or Output. Conversion functions are synchronized to positive going edge (see text).                                     |

| 23      | ŌĒĹ                | Three-State Enable for D0 D3. Active low input.                                                                                   |

| 24      | $V_{DD}$           | Digital Positive Supply (+5V).                                                                                                    |

## Theory of Operation

The HI5810 is a CMOS 12-bit, Analog-to-Digital Converter that uses capacitor charge balancing to successively approximate the analog input. A binarily weighted capacitor network forms the A/D heart of the device. See the block diagram for the HI5810.

The capacitor network has a common node which is connected to a comparator. The second terminal of each capacitor is individually switchable to the input,  $V_{\mbox{\scriptsize REF}^+}$  or  $V_{\mbox{\scriptsize REF}^-}.$

During the first three clock periods of a conversion cycle, the switchable end of every capacitor is connected to the input and the comparator is being auto balanced at the capacitor common node.

During the fourth period, all capacitors are disconnected from the input; the one representing the MSB (D11) is connected to the  $V_{REF}+$  terminal; and the remaining capacitors to  $V_{REF}-$ . The capacitor common node, after the charges balance out, will indicate whether the input was above  $^{1}/_{2}$  of (V\_REF+ - V\_REF-). At the end of the fourth period, the comparator output is stored and the MSB capacitor is either left connected to  $V_{REF}+$  (if the comparator was high) or returned to  $V_{REF}-$ . This allows the next comparison to be at either  $^{3}/_{4}$  or  $^{1}/_{4}$  of (V\_REF+ - V\_REF-).

At the end of periods 5 through 14, capacitors representing D10 through D1 are tested, the result stored, and each capacitor either left at  $V_{REF}$ + or at  $V_{REF}$ -.

At the end of the 15th period, when the LSB (D0) capacitor is tested, (D0) and all the previous results are shifted to the output registers and drivers. The capacitors are reconnected to the input, the comparator returns to the balance state, and the data ready output goes active. The conversion cycle is now complete.

#### **Analog Input**

The analog input pin is a predominately capacitive load that changes between the track and hold periods of the conversion cycle. During hold, clock period 4 through 15, the input loading is leakage and stray capacitance, typically less than  $5\mu A$  and 20pF.

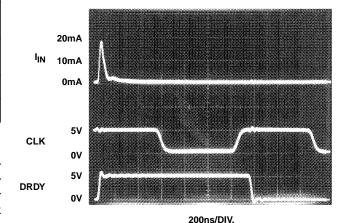

At the start of input tracking, clock period 1, some charge is dumped back to the input pin. The input source must have low enough impedance to dissipate the current spike by the end of the tracking period as shown in Figure 13. The amount of charge is dependent on supply and input voltages. The average current is also proportional to clock frequency.

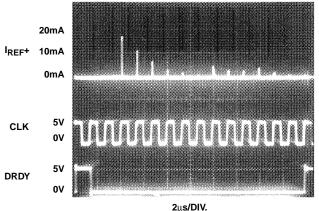

CONDITIONS:  $V_{DD} = V_{AA} + = 5.0V$ ,  $V_{REF} + = 4.608V$ ,  $V_{IN} = 4.608V$ , CLK = 750kHz,  $T_A = 25^{\circ}C$

FIGURE 13. TYPICAL ANALOG INPUT CURRENT

As long as these current spikes settle completely by end of the signal acquisition period, converter accuracy will be preserved. The analog input is tracked for 3 clock cycles. With an external clock of 1.5MHz the track period is  $2\mu s$ .

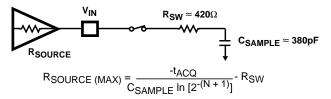

A simplified analog input model is presented in Figure 14. During tracking, the A/D input ( $V_{IN}$ ) typically appears as a 380pF capacitor being charged through a 420 $\Omega$  internal switch resistance. The time constant is 160ns. To charge this capacitor from an external "zero  $\Omega$ " source to 0.5 LSB (1/8192), the charging time must be at least 9 time constants or 1.4 $\mu$ s. The maximum source impedance ( $R_{SOURCE}$  Max) for a 2 $\mu$ s acquisition time settling to within 0.5 LSB is 164 $\Omega$ .

If the clock frequency was slower, or the converter was not restarted immediately (causing a longer sample time), a higher source impedance could be tolerated.

FIGURE 14. ANALOG INPUT MODEL IN TRACK MODE

#### Reference Input

The reference input V<sub>REF</sub>+ should be driven from a low impedance source and be well decoupled.

As shown in Figure 15, current spikes are generated on the reference pin during each bit test of the successive approximation part of the conversion cycle as the charge balancing capacitors are switched between  $V_{REF}$ - and  $V_{REF}+$  (clock periods 5 - 14). These current spikes must settle completely during each bit test of the conversion to not degrade the accuracy of the converter. Therefore  $V_{REF}+$  and  $V_{REF}-$  should be well bypassed. Reference input  $V_{REF}-$  is normally connected directly to the analog ground plane. If  $V_{REF}-$  is biased for nulling the converters offset it must be stable during the conversion cycle.

CONDITIONS:  $V_{DD} = V_{AA} + = 5.0V$ ,  $V_{REF} + = 4.608V$ ,  $V_{IN} = 2.3V$ , CLK = 750kHz,  $T_A = 25^{\circ}C$

FIGURE 15. TYPICAL REFERENCE INPUT CURRENT

The HI5810 is specified with a 4.608V reference, however, it will operate with a reference down to 3V having a slight degradation in performance.

#### **Full Scale and Offset Adjustment**

In many applications the accuracy of the HI5810 would be sufficient without any adjustments. In applications where accuracy is of utmost importance full scale and offset errors may be adjusted to zero.

The V<sub>REF</sub>+ and V<sub>REF</sub>- pins reference the two ends of the analog input range and may be used for offset and full scale adjustments. In a typical system the V<sub>REF</sub>- might be returned to a clean ground, and the offset adjustment done on an input amplifier. V<sub>REF</sub>+ would then be adjusted to null out the full scale error. When this is not possible, the V<sub>REF</sub>- input can be adjusted to null the offset error, however, V<sub>REF</sub>- must be well decoupled.

Full scale and offset error can also be adjusted to zero in the signal conditioning amplifier driving the analog input (V<sub>IN</sub>).

#### **Control Signal**

The HI5810 may be synchronized from an external source by using the STRT (Start Conversion) input to initiate conversion, or if STRT is tied low, may be allowed to free run. Each conversion cycle takes 15 clock periods.

The input is tracked from clock period 1 through period 3, then disconnected as the successive approximation takes place. After the start of the next period 1 (specified by t<sub>D</sub> data), the output is updated.

The DRDY (Data Ready) status output goes high (specified by  $t_{D1}DRDY$ ) after the start of clock period 1, and returns low (specified by  $t_{D2}DRDY$ ) after the start of clock period 2.

The 12 data bits are available in parallel on three-state bus driver outputs. When low, the  $\overline{\text{OEM}}$  input enables the most significant byte (D4 through D11) while the  $\overline{\text{OEL}}$  input enables the four least significant bits (D0 - D3).  $t_{EN}$  and  $t_{DIS}$  specify the output enable and disable times.

If the output data is to be latched externally, either the trailing edge of data ready or the next falling edge of the clock after data ready goes high can be used.

When STRT input is used to initiate conversions, operation is slightly different depending on whether an internal or external clock is used.

Figure 3 illustrates operation with an internal clock. If the  $\overline{\text{STRT}}$  signal is removed (at least  $t_R\overline{\text{STRT}})$  before clock period 1, and is not reapplied during that period, the clock will shut off after entering period 2. The input will continue to track and the DRDY output will remain high during this time.

A low signal applied to  $\overline{STRT}$  (at least  $t_W \overline{STRT}$  wide) can now initiate a new conversion. The  $\overline{STRT}$  signal (after a delay of  $(t_D \overline{STRT})$ ) causes the clock to restart.

Depending on how long the clock was shut off, the low portion of clock period 2 may be longer than during the remaining cycles.

The input will continue to track until the end of period 3, the same as when free running.

Figure 2 illustrates the same operation as above but with an external clock. If  $\overline{STRT}$  is removed (at least  $t_R \overline{STRT}$ ) before clock period 2, a low signal applied to  $\overline{STRT}$  will drop the DRDY flag as before, and with the first positive going clock edge that meets the ( $t_{SU} \overline{STRT}$ ) setup time, the converter will continue with clock period 3.

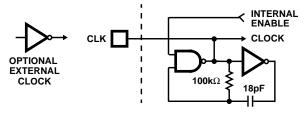

#### Clock

The HI5810 can operate either from its internal clock or from one externally supplied. The CLK pin functions either as the clock output or input. All converter functions are synchronized with the rising edge of the clock signal.

Figure 16 shows the configuration of the internal clock. The clock output drive is low power: if used as an output, it should not have more than 1 CMOS gate load applied, and stray wiring capacitance should be kept to a minimum.

The internal clock will shut down if the A/D is not restarted after a conversion. The clock could also be shut down with an open collector driver applied to the CLK pin. This should only be done during the sample portion (the first three clock periods) of a conversion cycle, and might be useful for using the device as a digital sample and hold.

If an external clock is supplied to the CLK pin, it must have sufficient drive to overcome the internal clock source. The external clock can be shut off, but again, only during the sample portion of a conversion cycle. At other times, it must be above the minium frequency shown in the specifications. In the above two cases, a further restriction applies in that the clock should not be shut off during the third sample period for more than 1ms. This might cause an internal charge pump voltage to decay.

If the internal or external clock was shut off during the conversion time (clock cycles 4 through 15) of the A/D, the output might be invalid due to balancing capacitor droop.

An external clock must also meet the minimum  $t_{LOW}$  and  $t_{HIGH}$  times shown in the specifications. A violation may cause an internal miscount and invalidate the results.

FIGURE 16. INTERNAL CLOCK CIRCUITRY

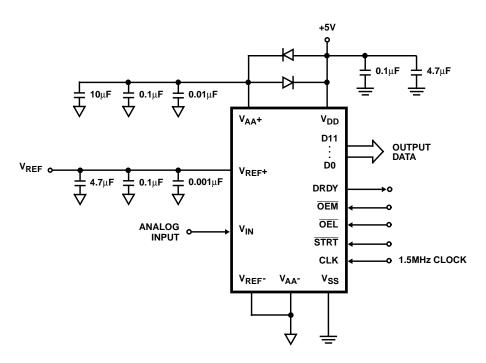

#### **Power Supplies and Grounding**

$V_{DD}$  and  $V_{SS}$  are the digital supply pins: they power all internal logic and the output drivers. Because the output drivers can cause fast current spikes in the  $V_{DD}$  and  $V_{SS}$  lines,  $V_{SS}$  should have a low impedance path to digital ground and  $V_{DD}$  should be well bypassed.

Except for  $V_{AA}$ +, which is a substrate connection to  $V_{DD}$ , all pins have protection diodes connected to  $V_{DD}$  and  $V_{SS}$ . Input transients above  $V_{DD}$  or below  $V_{SS}$  will get steered to the digital supplies.

The  $V_{AA}$ + and  $V_{AA}$ - terminals supply the charge balancing comparator only. Because the comparator is autobalanced between conversions, it has good low frequency supply rejection. It does not reject well at high frequencies however;  $V_{AA}$ - should be returned to a clean analog ground and  $V_{AA}$ + should be RC decoupled from the digital supply as shown in Figure 17.

There is approximately  $50\Omega$  of substrate impedance between  $V_{DD}$  and  $V_{AA}+$ . This can be used, for example, as part of a low pass RC filter to attenuate switching supply noise. A  $10\mu F$  capacitor from  $V_{AA}+$  to ground would attenuate 30kHz noise by approximately 40dB. Note that back-to-back diodes should be placed from  $V_{DD}$  to  $V_{AA}+$  to handle supply to capacitor turn-on or turn-off current spikes.

#### **Dynamic Performance**

Fast Fourier Transform (FFT) techniques are used to evaluate the dynamic performance of the A/D. A low distortion sine wave is applied to the input of the A/D converter. The input is sampled by the A/D and its output stored in RAM. The data is than transformed into the frequency domain with a 4096 point FFT and analyzed to evaluate the converters dynamic performance such as SNR and THD. See Typical Performance Characteristics.

#### Signal-To-Noise Ratio

The signal to noise ratio (SNR) is the measured RMS signal to RMS sum of noise at a specified input and sampling frequency. The noise is the RMS sum of all except the fundamental and the first five harmonic signals. The SNR is dependent on the number of quantization levels used in the converter. The theoretical SNR for an N-bit converter with no differential or integral linearity error is: SNR = (6.02N + 1.76)dB. For an ideal 12-bit converter the SNR is 74dB. Differential and integral linearity errors will degrade SNR.

#### Signal-To-Noise + Distortion Ratio

SINAD is the measured RMS signal to RMS sum of noise plus harmonic power and is expressed by the following.

#### **Effective Number of Bits**

The effective number of bits (ENOB) is derived from the SINAD data;

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

#### **Total Harmonic Distortion**

The total harmonic distortion (THD) is the ratio of the RMS sum of the second through sixth harmonic components to the fundamental RMS signal for a specified input and sampling frequency.

#### **Spurious-Free Dynamic Range**

The spurious-free dynamic range (SFDR) is the ratio of the fundamental RMS amplitude to the RMS amplitude of the next largest spur or spectral component. If the harmonics are buried in the noise floor it is the largest peak.

**TABLE 2. CODE TABLE**

|                                | INPUT<br>VOLTAGE†    |         | BINARY OUTPUT CODE |     |    |    |    |    |    |    |    |    |    |     |

|--------------------------------|----------------------|---------|--------------------|-----|----|----|----|----|----|----|----|----|----|-----|

| CODE                           | $V_{REF} + = 4.608V$ | DECIMAL | MSB                |     |    |    |    |    |    |    |    |    |    | LSB |

| DESCRIPTION                    |                      | COUNT   | D11                | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| Full Scale (FS)                | 4.6069               | 4095    | 1                  | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   |

| FS - 1 LSB                     | 4.6058               | 4094    | 1                  | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0   |

| <sup>3</sup> / <sub>4</sub> FS | 3.4560               | 3072    | 1                  | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

| <sup>1</sup> / <sub>2</sub> FS | 2.3040               | 2048    | 1                  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

| <sup>1</sup> / <sub>4</sub> FS | 1.1520               | 1024    | 0                  | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

| 1 LSB                          | 0.001125             | 1       | 0                  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1   |

| Zero                           | 0                    | 0       | 0                  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

<sup>†</sup>The voltages listed above represent the ideal lower transition of each output code shown as a function of the reference voltage.

FIGURE 17. GROUND AND SUPPLY DECOUPLING

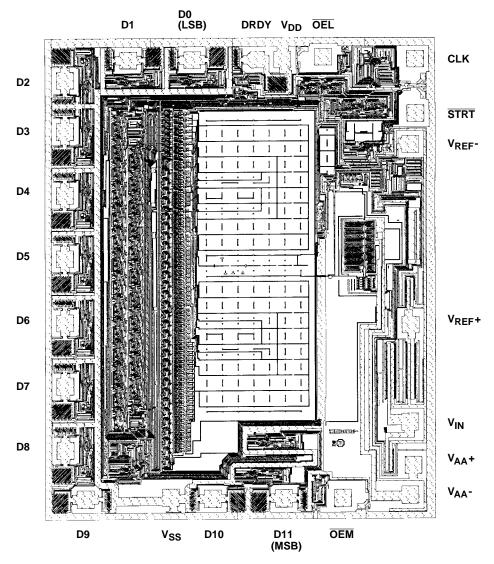

**PASSIVATION:**

#### Die Characteristics

**DIE DIMENSIONS:**

3200μm x 3940μm Type: PSG

Thickness: 13kÅ ±2.5kÅ

METALLIZATION:

WORST CASE CURRENT DENSITY:

Type: AlSi

Thickness:  $11k\mathring{A} \pm 1k\mathring{A}$ 1.84 x  $10^5$  A/cm<sup>2</sup>

## Metallization Mask Layout

#### HI5810

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com