# Intel® 82870DH DDR Memory Hub (DMH) Datasheet

#### **Product Features**

- Two independent DDR DIMM channels per DMH.

- 4 DIMMs per DDR Channel.

- Registered PC1600 DDR DIMMs.

- Write Buffers to minimize large turnaround times.

- Pass through architecture for Read and Write accesses.

- Supports 128 Mb, 256 Mb, 512 Mb and 1 Gb DDR SDRAM technologies.

- Each DMH supports a wide range of memory size.

- Up to 4 GB using 128 Mb device.

- Up to 8 GB using 256 Mb device.

- Up to 16 GB using 512 Mb device.

- Up to 32 GB using 1 Gb device.

- Support of RDRAM CMOS signals to facilitate initialization and read/write of registers.

- DMH internal registers accessed through CMOS signal interface.

- Tunnels DDR SDRAM protocol over RSL.

- Integrated System Management Bus (SMB) controller to read and write data from/to SPD EEPROM on the DIMMs.

- 1.6 GB/s data rates in either 16-byte or 32-byte DDR DIMM transfer mode.

- 567 pin OLGA package.

Document Number: 251113-001 August 2002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82870DH DDR Memory Hub may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

Intel and Itanium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2002, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

$l^2C$  is a two-wire communication bus /protocol developed by Phillips. SMBus is a subset of the  $l^2C$  bus/protocol developed by Intel. Implementation of the  $l^2C$  bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Phillips Electronics, N.V. and North American Phillips Corporation.

| 1 | Overv  | iew                                          | 1-1  |  |  |  |  |

|---|--------|----------------------------------------------|------|--|--|--|--|

|   | 1.1    | 1-1                                          |      |  |  |  |  |

|   | 1.2    | Supported Memory Configurations              |      |  |  |  |  |

|   |        | 1.2.1 Memory Capacity                        |      |  |  |  |  |

|   | 1.3    | Terminology                                  |      |  |  |  |  |

|   | 1.4    | Reference Documents                          |      |  |  |  |  |

|   | 1.5    | Revision History                             |      |  |  |  |  |

| 2 | Signal | Description                                  | 2-1  |  |  |  |  |

|   | 2.1    | Main Channel Interface                       | 2-1  |  |  |  |  |

|   | 2.2    | Branch Channel Interface                     |      |  |  |  |  |

|   | 2.3    | Reset and Test Signals                       | 2-3  |  |  |  |  |

|   | 2.4    | Voltage References                           |      |  |  |  |  |

| 3 | Regist | ters                                         | 3-1  |  |  |  |  |

|   | 3.1    | Gen – General Purpose Register               | 3-1  |  |  |  |  |

|   | 3.2    | DSTIM – DIMM Strobe Timing Register          |      |  |  |  |  |

|   | 3.3    | MCTIM – Main Channel Timing Register         |      |  |  |  |  |

|   | 3.4    | BCTIM – Branch Channel Timing Register       |      |  |  |  |  |

|   | 3.5    | DGR – DIMM Geometry Register                 |      |  |  |  |  |

|   | 3.6    | 3                                            |      |  |  |  |  |

|   | 3.7    | SDI – SDRAM Initialization Register          |      |  |  |  |  |

|   | 3.8    | RCC – RAMBUS Current Control Register        |      |  |  |  |  |

|   | 3.9    | RIR – RAC Initialization Register            |      |  |  |  |  |

|   | 3.10   | SPD – Serial Presence Detect Status Register |      |  |  |  |  |

|   | 3.11   | PWR – Power Up Control Register              |      |  |  |  |  |

|   | 3.12   | VID – Vendor Identification Register         |      |  |  |  |  |

|   | 3.13   | RID – Revision Identification Register       |      |  |  |  |  |

|   | 3.14   | MUARS – DMH Unified Access Register Select   |      |  |  |  |  |

|   | 3.15   | MUARD – DMH Unified Access Register Data     |      |  |  |  |  |

|   |        | 3.15.1 DMH Unified Access Registers          |      |  |  |  |  |

|   | 3.16   | SPDID – SPD Device ID Register               |      |  |  |  |  |

|   | 3.17   | DID – Device Identification Register         | 3-13 |  |  |  |  |

| 4 | Functi | onal Description                             | 4-1  |  |  |  |  |

|   | 4.1    | Operation Overview                           |      |  |  |  |  |

|   | 4.2    | Main Channel to Branch Channel Translation   | 4-2  |  |  |  |  |

|   |        | 4.2.1 MCP Format and Timing                  |      |  |  |  |  |

|   |        | 4.2.2 MCP Command Type Field                 |      |  |  |  |  |

|   |        | 4.2.3 MCP for DIMM Activate Command          | 4-3  |  |  |  |  |

|   |        | 4.2.4 MCP for DIMM Read/Write Command        |      |  |  |  |  |

|   |        | 4.2.5 MCP for Extended Commands              |      |  |  |  |  |

|   | 4.3    | DMH Time Synchronization Packet              |      |  |  |  |  |

|   | 4.4    | Main Channel Periodic Calibration            |      |  |  |  |  |

|   |        | 4.4.1 Current Calibration                    |      |  |  |  |  |

|   |        | 4.4.2 Temperature Calibration                | 4-5  |  |  |  |  |

| 4.5      | Branch Channel Periodic Calibration      |                         |   |

|----------|------------------------------------------|-------------------------|---|

|          | 4.5.1 Slew Rate Calibration              | 4-1                     | 6 |

|          | 4.5.2 Read Strobe 2.2 ns Delay Calibrati | on4-                    | 6 |

| 4.6      | Transfer Mode                            | 4-                      | 6 |

|          | 4.6.1 32-Byte Mode                       | 4-                      | 6 |

|          | 4.6.2 16-Byte Mode                       | 4-                      | 7 |

| 4.7      | Write Buffers                            | 4-                      | 7 |

| 4.8      | Memory Translation Rules                 | 4-                      | 7 |

|          | 4.8.1 Read Rules                         | 4-                      | 7 |

|          | 4.8.2 Write Rules                        | 4-                      | 8 |

|          | 4.8.3 Miscellaneous Rules                | 4-6                     | 8 |

|          |                                          | 4-                      |   |

|          | •                                        | 4-                      |   |

|          |                                          | ansactions4-            |   |

| 4.9      | Error Mechanisms                         |                         |   |

|          |                                          | 94-                     |   |

| 4.10     | System Clocking                          |                         |   |

| 4.11     | Serial Interface                         |                         |   |

|          | 4.11.1 Overview                          |                         |   |

|          | 4.11.2 MSIO Transaction Packet Formats   |                         |   |

|          | 4.11.3 MSIO Bus Interface                |                         |   |

|          | 4.11.4 BSIO Bus Interface                |                         |   |

| 4.12     | DDR SDRAM Transactions                   |                         |   |

| 7.12     | 4.12.1 DIMM Initialization               |                         |   |

| 4.13     | Reset                                    |                         |   |

| 4.13     | 4.13.1 Power Good Sequence               |                         |   |

|          | 4.13.1 Power Good Sequence               |                         |   |

|          | 4.13.3 Local Reset                       |                         |   |

|          |                                          |                         |   |

| 1 1 1    | 4.13.4 MSIO Local Reset                  |                         |   |

| 4.14     | Initialization                           |                         |   |

|          | 4.14.1 RAC Initialization                |                         |   |

|          | 4.14.2 DDR DIMM Sizing                   |                         |   |

|          | 4.14.3 DDR DIMM Initialization           |                         |   |

|          | 4.14.4 DDR Read Strobe Delay Calibratio  |                         |   |

|          | 4.14.5 DDR DIMM Path Delay Calibration   | 4-19                    | 9 |

| Electric | al Specifications                        | 5-                      | 1 |

|          | •                                        |                         |   |

| 5.1      | Non-Operational Maximum Rating           |                         |   |

| 5.2      | Operation Power Delivery Specification   |                         |   |

| 5.3      | Main Channel Interface                   |                         |   |

|          |                                          | Voltage Specification5- |   |

|          | •                                        | 5-:                     |   |

| - 4      |                                          | 5-                      |   |

| 5.4      | DDR Interface                            |                         |   |

|          | •                                        | 5-3                     |   |

|          | •                                        | ents5                   |   |

|          | •                                        | 5                       |   |

|          | •                                        | 5                       |   |

| 5.5      | Miscellaneous Signals Interface          |                         |   |

|          | ·                                        | 5-                      |   |

|          |                                          | 5-                      |   |

|          | 5.5.3 AC Specification                   | 5-`                     | 7 |

5

# intط

| 6              | Ballou | ut and Package Information                                     | 6-1  |

|----------------|--------|----------------------------------------------------------------|------|

|                | 6.1    | 567-Ball OLGA1 Package Information                             | 6-1  |

|                | 6.2    | Ballout Signal List                                            |      |

| 7              | Testa  | bility                                                         | 7-1  |

|                | 7.1    | Parametric Test Mode                                           | 7-1  |

| <b>Figures</b> |        |                                                                |      |

| riguics        | 1-1    | Fully Loaded SNC Example                                       | 1_1  |

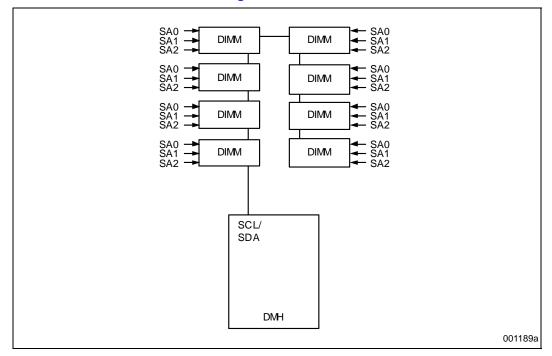

|                | 1-2    | DMH Driving Both DIMM Channels, Four DIMMs per Channel         |      |

|                | 4-1    | DMH Block Diagram                                              |      |

|                | 4-2    | Driving MCP to DIMM Address and Control Lines                  |      |

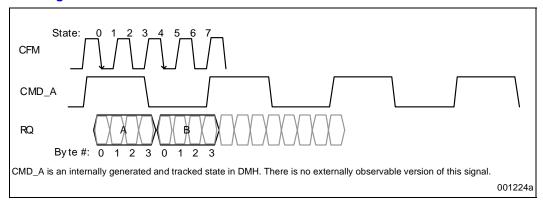

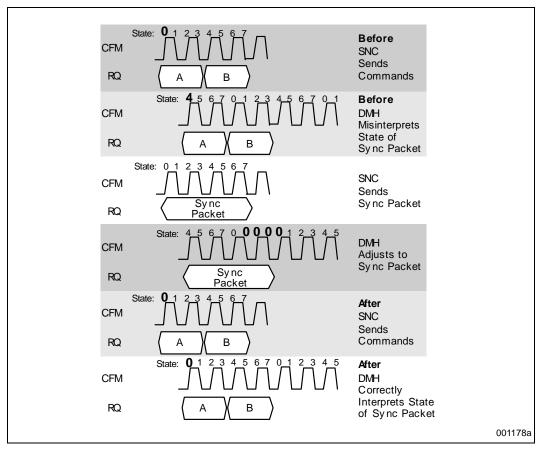

|                | 4-3    | Phase Shifted MCP Command State Tracker and Correction         |      |

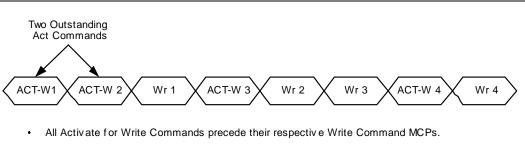

|                | 4-4    | Example of Valid Write Command Ordering                        |      |

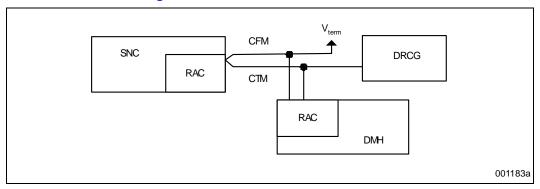

|                | 4-5    | DRCG Connection Diagram                                        |      |

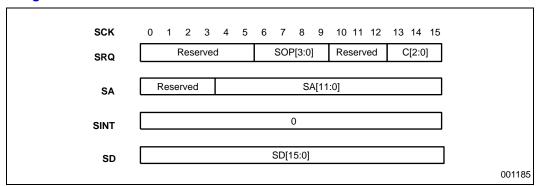

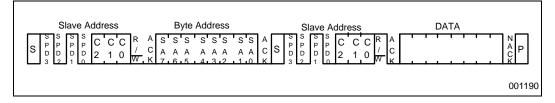

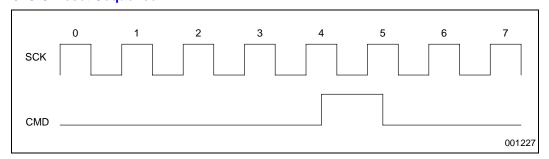

|                | 4-6    | Register Read MSIO Transaction                                 |      |

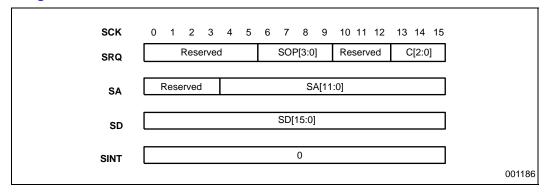

|                | 4-7    | Register Write MSIO Transaction                                |      |

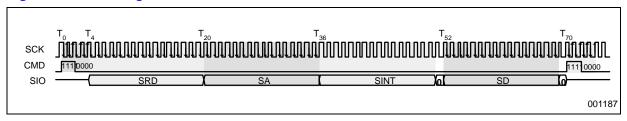

|                | 4-8    | MSIO Register Read Transaction                                 |      |

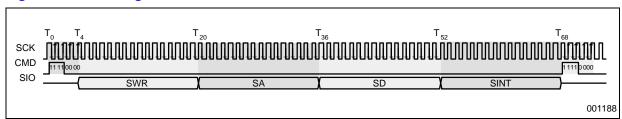

|                | 4-9    | MSIO Register Write Transaction                                |      |

|                | 4-10   | Connection of DIMM Serial I/O Signals                          |      |

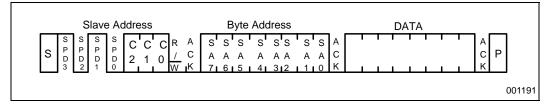

|                | 4-11   | Random Byte Read Timing                                        |      |

|                | 4-12   | Byte Write Register Timing                                     |      |

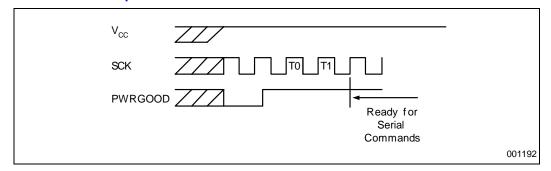

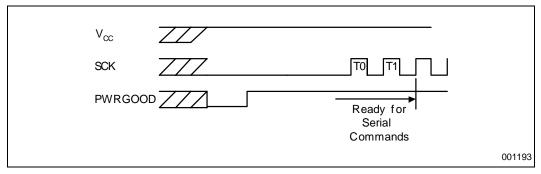

|                | 4-13   | PWRGOOD Sequence Method 1                                      |      |

|                | 4-14   | PWRGOOD Sequence Method 2                                      |      |

|                | 4-15   | SIO Reset Sequence                                             |      |

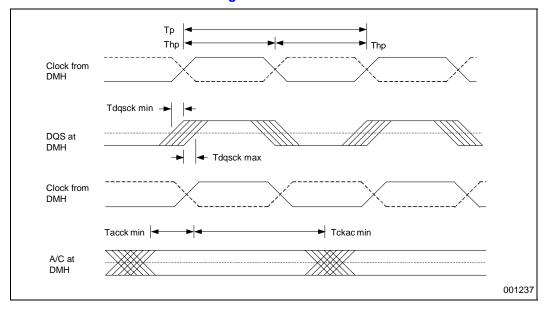

|                | 5-1    | SSTL-2 Common Clock AC Timing                                  |      |

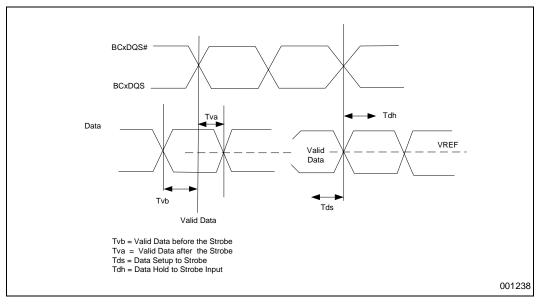

|                | 5-2    | SSTL-2 Source Synchronous AC Timing                            |      |

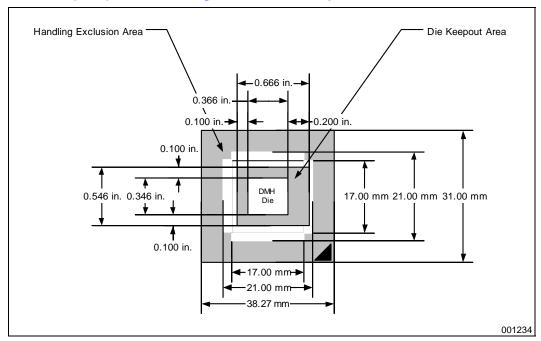

|                | 6-1    | 567-Ball (DMH) OLGA1 Package Dimensions - Top View             |      |

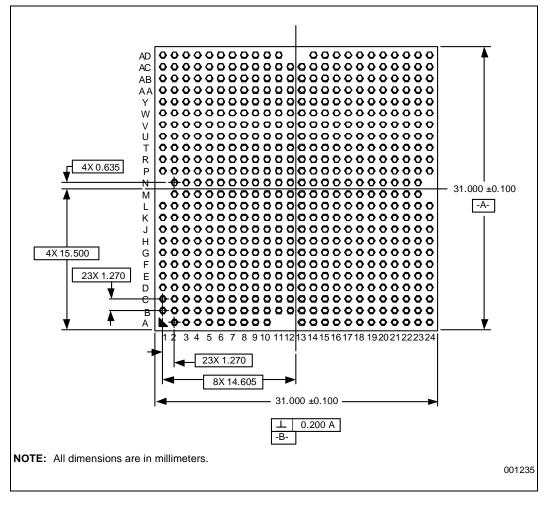

|                | 6-2    | 567-Ball (DMH) OLGA1 Package Dimensions – Bottom View          |      |

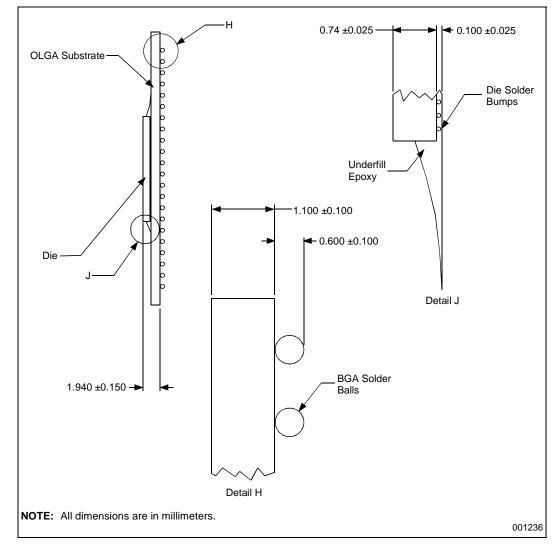

|                | 6-3    | 567-Ball (DMH) OLGA1 Solder Balls Detail                       |      |

| <b>Tables</b>  |        |                                                                |      |

|                | 1-1    | Memory Size                                                    | 1-3  |

|                | 2-1    | Main Channel Interface Signals                                 |      |

|                | 2-2    | Branch Channel Interface Signals                               |      |

|                | 2-3    | Reset and Miscellaneous Signals                                |      |

|                | 2-4    | Voltage Reference Signals                                      | 2-4  |

|                | 3-1    | Unified Access Register Definitions                            | 3-11 |

|                | 4-1    | Encoding of ST and SF                                          | 4-3  |

|                | 4-2    | Write Buffer Burst Operation for Read-Hit Operations           | 4-9  |

|                | 4-3    | MSIO Packet Field Definitions                                  | 4-11 |

|                | 4-4    | SCK Clock Divider Frequency Table                              | 4-14 |

|                | 4-5    | DDR SDRAM Command Encoding for SDI Register                    |      |

|                | 5-1    | Absolute Maximum Non-Operational DC Ratings at the Package Pin | 5-1  |

|                | 5-2    | Voltage and Current Specifications                             |      |

|                | 5-3    | DMH Main Channel Signal Groups                                 | 5-2  |

|                | 5-4    | Main Channel Vref Specification                                |      |

|                | 5-5    | RSL Data Group, DC Parameters                                  |      |

|                | 5-7    | Main Channel "CMOS 1.8 I/O" DC Parameters                      |      |

|                | 5-6    | RSL Clocks, DC Parameters                                      |      |

|                | 5-8    | DMH DDR Signal Groups                                          | 5-3  |

| 5-9  | DMH DDR Vref Specifications                | 5-4 |

|------|--------------------------------------------|-----|

| 5-10 | SSTL_2 DC Parameters                       |     |

| 5-11 | SSTL_2 Common Clock AC Specification       | 5-4 |

| 5-13 | SSTL_2 Output Clock Parameters             | 5-5 |

| 5-12 | SSTL_2 Source Synchronous AC Specification | 5-5 |

| 5-14 | Signal Groups                              | 5-6 |

| 5-15 | CMOS 1.8V Input DC Parameters              | 5-6 |

| 5-16 | CMOS 1.8V Output DC Parameters             | 5-7 |

| 5-17 | CMOS 2.5V DC Parameters                    | 5-7 |

| 5-18 | CMOS 1.8V Input AC Parameters              | 5-7 |

| 5-20 | CMOS 2.5V AC Parameters                    | 5-8 |

| 5-19 | CMOS 1.8V Output AC Parameters             | 5-8 |

| 6-1  | DMH Ball List                              | 6-4 |

| 6-2  | DMH Signal – Ball Number                   |     |

| 7-1  | Parametric Test Control Signals            | 7-1 |

| 7-2  | Parametric Test Pin Order                  | 7-1 |

int<sub>el®</sub>

Overview

#### **System Architecture** 1.1

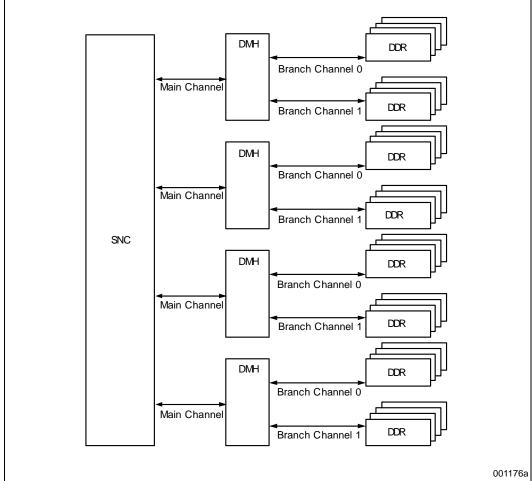

Figure 1-1. Fully Loaded SNC Example

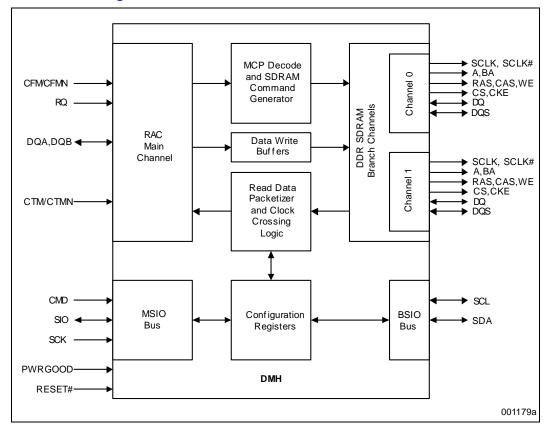

The DDR Memory Hub (DMH) is a memory translator hub that provides a mechanism for tunneling DDR SDRAM transactions between a Main Channel (RAMBUS\* interface) and two Branch Channels (DDR SDRAM interfaces). While all RAMBUS signals maintain electrical compatibility with RDRAM pins, the RAMBUS signals are logically redefined to packetize DDR SDRAM I/O traffic. The DMH tunnels SDRAM packets between the Main Channel and a Branch Channel with deterministic timing.

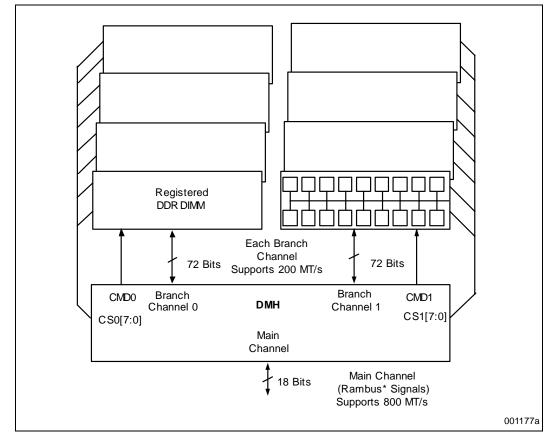

The DMH interfaces two 8-byte-wide DDR DIMM channels to a single, 2-byte-wide Main Channel as shown in Figure 1-2. Each DDR DIMM channel may contain from 0 to 4 DIMMs. The DMH supports a maximum of 8 DIMMs (4 each on each branch channel), and requires at least 1 DIMM.

Figure 1-2. DMH Driving Both DIMM Channels, Four DIMMs per Channel

The DMH facilitates memory devices isolation and correction for X4 memory geometries. The DMH facilitates this by ensuring that no data bit is mapped onto the same SDRAM device as any of its ECC bits. The mapping allows the Scalability Node Controller (SNC) to organize data and ECC symbols in an arrangement that allows ECC to reconstruct all four bits of data associated with a failed SDRAM device.

### 1.2 Supported Memory Configurations

The DMH supports 128 Mb, 256 Mb, 512 Mb, and 1 Gb<sup>1</sup> PC1600 DDR SDRAM memory technologies in 4-bank, X4 and X8 geometries, on 184-pin DIMMs.

### 1.2.1 Memory Capacity

Table 1-1 defines the minimum and maximum memory configurations supported by the DMH with various DDR SDRAM technologies.

<sup>1. 1</sup> Gb devices are not validated at the time of writing.

Table 1-1. Memory Size

| DDR SDRAM<br>Technology | DIMM Size         | DDR DIMM Device Organization <sup>a</sup>                                                      | Minimum<br>Configuration <sup>b</sup> | Maximum<br>Configuration <sup>c</sup> |

|-------------------------|-------------------|------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|

| 128 Mb                  | 16Mx72<br>(128MB) | 4M x 8 bit x 4 Bank x 9 DRAMs/Side x 1 Side                                                    | 128 MB                                | 1 GB                                  |

|                         | 32Mx72<br>(256MB) | 4M x 8 bit x 4 Bank x 9 DRAMs/Side x 2 Sides<br>8M x 4 bit x 4 Bank x 18 DRAMs/Side x 1 Side   | 256 MB                                | 2 GB                                  |

|                         | 64Mx72<br>(512MB) | 8M x 4 bit x 4 Bank x 18 DRAMs/Side x 2 Sides                                                  | 512 MB                                | 4 GB                                  |

| 256 Mb                  | 32Mx72<br>(256MB) | 8M x 8 bit x 4 Bank x 9 DRAMs/Side x 1 Side                                                    | 256 MB                                | 2 GB                                  |

|                         | 64Mx72<br>(512MB) | 8M x 8 bit x 4 Bank x 9 DRAMs/Side x 2 Sides<br>16M x 4 bit x 4 Bank x 18 DRAMs/Side x 1 Side  | 512 MB                                | 4 GB                                  |

|                         | 128Mx72<br>(1GB)  | 16M x 4 bit x 4 Bank x 18 DRAMs/Side x 2 Sides                                                 | 1 GB                                  | 8 GB                                  |

| 512 Mb                  | 64Mx72<br>(512MB) | 16M x 8 bit x 4 Bank x 9 DRAMs/Side x 1 Side                                                   | 512 MB                                | 4 GB                                  |

|                         | 128Mx72<br>(1GB)  | 16M x 8 bit x 4 Bank x 9 DRAMs/Side x 2 Sides<br>32M x 4 bit x 4 Bank x 18 DRAMs/Side x 1 Side | 1 GB                                  | 8 GB                                  |

|                         | 256Mx72<br>(2GB)  | 32M x 4 bit x 4 Bank x 18 DRAMs/Side x 2 Sides                                                 | 2 GB                                  | 16 GB                                 |

| 1 Gb                    | 128Mx72<br>(1GB)  | 32M x 8 bit x 4 Bank x 9 DRAMs/Side x 1 Side                                                   | 1 GB                                  | 8 GB                                  |

|                         | 256Mx72<br>(2GB)  | 32M x 8 bit x 4 Bank x 9 DRAMs/Side x 2 Sides<br>64M x 4 bit x 4 Bank x 18 DRAMs/Side x 1 Side | 2 GB                                  | 16 GB                                 |

|                         | 512Mx72<br>(4GB)  | 64M x 4 bit x 4 Bank x 18 DRAMs/Side x 2 Sides                                                 | 4 GB                                  | 32 GB                                 |

#### **Terminology** 1.3

| SNC    | Scalable Node Controller. Processor system bus interface and memory controller for the Intel <sup>®</sup> E8870 chipset.                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSL    | RAMBUS Signaling Level. The name of the signaling technology used by RAMBUS.                                                                               |

| SSTL_2 | Stub Series Terminated Logic. Signal levels used in DDR DIMM data I/O.                                                                                     |

| RAC    | RAMBUS ASIC Cell. It is the embedded cell designed by RAMBUS that interfaces with the RAMBUS devices using RSL signaling. The RAC communicates to the RMC. |

| RMC    | RAMBUS Memory Controller. This is the logic that directly interfaces to the RAC.                                                                           |

<sup>a. A DIMM Side is defined as a group of DRAMs that share a common Chip Select.

b. DMH configured with 1 DDR DIMM on 1 Branch Channel.

c. DMH configured with 4 DDR DIMMs on each (of 2) Branch Channel, for a total of 8 DIMMs.</sup>

DDR SDRAM Double Data Rate Synchronous Dynamic Random Access

Memory as defined by the Jedec DDR SDRAM

specification.

DIMM Dual Inline Memory Module.

MCP Memory Control Packets.

DMH DDR Memory Hub.

Main Channel The RAC signals used to communicate with SNC.

Branch Channel A DDR DIMM bus.

CFM Clock From Master - Main Channel Receive clock.

CTM Clock To Master - Main Channel Transmit clock.

RQ Main Channel Request Control Signals (RSL signal level).

DQA/DQB Main Channel Data Signals (RSL signal level).

MSIO Bus The Main Channel Serial I/O bus. Uses the RAC serial I/O

CMOS signals.

BSIO Bus The Branch Channel Serial I/O bus. This is the DIMM Serial

Presence Detect interface.

MT/s Mega-Transfers per second.

#### 1.4 Reference Documents

- Jedec Standard JESD-21C

- Jedec Standard 79 (JESD79)

- I<sup>2</sup>C Bus Specifications, Version 2.0

- Intel® E8870 Scalable Node Controller (SNC) Datasheet

### 1.5 Revision History

| Revision<br>Number | Description                       | Date        |

|--------------------|-----------------------------------|-------------|

| -001               | Initial release of this document. | August 2002 |

# intel® Signal Description

The following notations are used to describe the signal types and their drive state:

- I Input pin

- O Output pin

- I/O Bidirectional input/output pin

- Z Tri-stated

- L Driven low

- H Driven high

- Output state is indeterminate

#### **Main Channel Interface** 2.1

The Main Channel is the interface between the SNC and DMH.

**Table 2-1. Main Channel Interface Signals**

| Signal   | Туре                | State during<br>PWRGOOD<br>Deassertion | Description                                                                                                                                                      |

|----------|---------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQA[8:0] | I/O<br>RSL          | ?                                      | Data Bus, Data Byte A: Bidirectional 9-bit data bus A. These correspond to the DQA[8:0] signals on the RAC.                                                      |

| DQB[8:0] | I/O<br>RSL          | ?                                      | Data Bus, Data Byte B: Bidirectional 9-bit data bus B. These correspond to the DQB[8:0] signals on the RAC.                                                      |

| RQ[7:0]  | l<br>RSL            | I                                      | Request Control: These signals carry the memory control packets (MCP) from the SNC to the DMH. These correspond to the RRq[2:0] and CRq[4:0] signals on the RAC. |

| SIO      | I/O<br>CMOS<br>1.8V | I                                      | Serial I/O Chain:<br>Serial input/output pins used for reading and writing<br>control registers.                                                                 |

| SCK      | I<br>CMOS<br>1.8V   | I                                      | Serial Clock: Clock source used for timing of the SIO and CMD signals. This corresponds to the SCK signal on the RAC.                                            |

| CMD      | I<br>CMOS<br>1.8V   | I                                      | Serial Command: Serial command input used for control register read and write operations. This corresponds to the CMD signal on the RAC.                         |

| СТМ      | l<br>RSL            | I                                      | Clock to RAC Master: One of the two differential transmit clock signals used for DMH to RAC Master operations.                                                   |

| CTMN     | l<br>RSL            | I                                      | Clock to RAC Master Complement: One of the two differential transmit clock signals used for DMH to RAC Master operations.                                        |

**Table 2-1. Main Channel Interface Signals (Continued)**

| Signal | Туре     | State during<br>PWRGOOD<br>Deassertion | Description                                                                                                           |

|--------|----------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| CFM    | l<br>RSL | I                                      | Clock from RAC Master: One of the differential receive clock signals used for RAC Master to DMH operation.            |

| CFMN   | l<br>RSL | I                                      | Clock from RAC Master Complement: One of the differential receive clock signals used for RAC Master to DMH operation. |

#### 2.2 Branch Channel Interface

The DMH drives two DDR Branch Channels. Channel 0 signals are prefixed with BC0 and channel 1 with BC1. Except for Table 2-2, the prefix is omitted in this document when discussing an aspect of the signal that applies to both ports. Unless specified in Table 2-2, signals on BC0 and BC1 are electrically identical, meaning they use the same voltage and current levels.

**Table 2-2. Branch Channel Interface Signals**

| Signal                     | Туре                      | State during<br>PWRGOOD<br>Deassertion | Description                                                                                                                                                                                                              |

|----------------------------|---------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BC0A[14:0]<br>BC1A[14:0]   | O<br>SSTL_2<br>Class II   | L                                      | SDRAM Address: Used for providing multiplexed row and column address to SDRAM. Each set of address pins can drive up to eight rows of SDRAM.                                                                             |

| BC0BA[1:0]<br>BC1BA[1:0]   | O<br>SSTL_2<br>Class II   | L                                      | SDRAM Bank Active:<br>Used to select the bank within a device.                                                                                                                                                           |

| BC0DQ[71:0]<br>BC1DQ[71:0] | I/O<br>SSTL_2<br>Class II | Z                                      | SDRAM Data: BC0DQ and BC1DQ are independent to allow different data to be read or written on both ports simultaneously.                                                                                                  |

| BC0RAS#<br>BC1RAS#         | O<br>SSTL_2<br>Class II   | L                                      | SDRAM Row Address Strobe: Used with CS#, CAS# and WE# to specify the SDRAM command. Each signal can drive up to eight SDRAM rows. CS# selects the row.                                                                   |

| BC0CAS#<br>BC1CAS#         | O<br>SSTL_2<br>Class II   | L                                      | SDRAM Column Address Strobe: Used with CS#, RAS# and WE# to specify the SDRAM command. These signals are used to latch the column and bank addresses. Each signal can drive up to eight SDRAM rows.                      |

| BC0WE#<br>BC1WE#           | O<br>SSTL_2<br>Class II   | L                                      | SDRAM Write Enable: Used with CS#, CAS# and RAS# to specify the SDRAM command. These signals are used for write and precharge operations of SDRAM. Each signal can drive up to eight SDRAM rows.                         |

| BC0CS#[7:0]<br>BC1CS#[7:0] | O<br>SSTL_2<br>Class II   | L                                      | SDRAM Chip Select: These signals are used for selecting one of eight SDRAM rows. CS#[0] is used to select the first row and CS#[1] is used to select a second row if present, etc. to CS#[7] which selects the last row. |

| BC0CKE<br>BC1CKE           | O<br>SSTL_2<br>Class II   | L                                      | SDRAM Clock Enable: These signals are used for signaling commands to an SDRAM row.                                                                                                                                       |

**Table 2-2. Branch Channel Interface Signals (Continued)**

| Signal                                                         | Туре                              | State during<br>PWRGOOD<br>Deassertion | Description                                                                                                                                                |

|----------------------------------------------------------------|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BC0SCLK[3:0]<br>BC0SCLK#[3:0]<br>BC1SCLK[3:0]<br>BC1SCLK#[3:0] | O<br>SSTL_2<br>Class II           | L<br>H<br>L<br>H                       | SDRAM Clocks: One pair of differential clock signals for each DIMM.                                                                                        |

| BC0DQS[17:0]<br>BC1DQS[17:0]                                   | I/O<br>SSTL_2<br>Class II         | Z                                      | SDRAM Data Strobe: DDR data strobes. Some of these pins are dual mode, and are DQM pins for X8 memory configuration as specified in Jedec Standard JESD79. |

| SREF                                                           | O<br>SSTL_2<br>Class II           | L                                      | SDRAM Feedback Output: Used to calibrate the SDRAM clock.                                                                                                  |

| SREFFB                                                         | I<br>SSTL_2<br>Class II           | I                                      | SDRAM Feedback Input:<br>Used to calibrate the SDRAM clock.                                                                                                |

| BC0SRCAL<br>BC1SRCAL                                           | I/O<br>SSTL_2<br>Class II         | Z                                      | Slew-rate Calibration: BC0 tied to ground through 50 Ohm resistor BC1 tied to VCC25 through 50 Ohm resistor                                                |

| SDA                                                            | I/O<br>CMOS<br>Open Drain<br>2.5V | Z                                      | Serial Data/Address: Used to read and write the Serial Presence Detect EEPROMS associated with the DIMMs Controlled by this DMH.                           |

| SCL                                                            | I/O<br>CMOS<br>Open Drain<br>2.5V | Z                                      | Serial Clock: Used to read and write the Serial Presence Detect EEPROMS associated with the DIMMs Controlled by this DMH.                                  |

# 2.3 Reset and Test Signals

**Table 2-3. Reset and Miscellaneous Signals**

| Signal  | Туре                            | State during<br>PWRGOOD<br>Deassertion | Description                                                                                           |

|---------|---------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|

| TSO     | I<br>CMOS<br>Open Drain<br>2.5V | I                                      | Disables all outputs except TSO and XOROUT.                                                           |

| PWRGOOD | I<br>CMOS<br>1.8V               | I                                      | Power Good: This pin is used for asynchronous reset of the entire DMH.                                |

| RESET#  | I<br>CMOS<br>1.8V               | I                                      | <b>DMH Reset</b> : This signal is used for resetting the DMH internal logic during power up sequence. |

| XORIN   | I<br>CMOS<br>1.8V               | I                                      | Parametric XOR tree input.                                                                            |

| XOROUT  | O<br>CMOS<br>1.8V               | ?                                      | Parametric XOR tree output.                                                                           |

# 2.4 Voltage References

**Table 2-4. Voltage Reference Signals**

| Signal                           | Description                                                                                                     |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------|

| VREF[A,B]RAC                     | RSL reference voltage for the RAC.                                                                              |

| VCCRAC                           | 1.8V digital power for RAC.     1.8V source for DMH core operation.     1.8V source for CMD, SCK, and SIO pins. |

| VCCRACA                          | Filtered Analog $V_{CC}$ : Provide $V_{CC}$ to RAC interface DLL.                                               |

| VCCDLY                           | Filtered 1.8V for the DMH internal delay cells.                                                                 |

| VCC25                            | 2.5V source for DDR and 2.5V I/Os.                                                                              |

| VSS                              | Ground                                                                                                          |

| AD[0:1]VREF                      | DDR Address VREF                                                                                                |

| BC0VREF[A,B,C]<br>BC1VREF[A,B,C] | DDR VREF                                                                                                        |

| BC0VSSA[A,B,C]<br>BC1VSSA[A,B,C] | DDR VREF Vss                                                                                                    |

The DMH has internal configuration and control registers. These registers are accessed via the MSIO bus (see Section 4.11, "Serial Interface").

#### **Gen – General Purpose Register** 3.1

Address: 01h Default: 0000h Access: R/W Size: 16 bits

| Bit  | Description                   |  |

|------|-------------------------------|--|

| 15:0 | General purpose R/W register. |  |

#### **DSTIM – DIMM Strobe Timing Register** 3.2

Address: 02h Default: 0000h R/W Access: Size: 16 bits

Offsets each DIMM read-strobe-capture-window forward, relative to the base setting contained in the t<sub>DPL</sub> field.

| Bit   | Description                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------|

| 15:14 | Branch Channel 1, DIMM 7 Strobe Offset (t <sub>DSD7</sub> ):                                                                  |

|       | Bits [15:14] t <sub>DSD7</sub> in CFMs 0 0 0 0 1 1 1 0 2 1 1 3                                                                |

| 13:12 | Branch Channel 1, DIMM 6 Strobe Offset (t <sub>DSD6</sub> ):  Bits [13:12] t <sub>DSD6</sub> in CFMs 0 0 0 0 1 1 1 0 2 1 1 3  |

| 11:10 | Branch Channel 1, DIMM 5 Strobe Offset (t <sub>DSD5</sub> ):  Bits [11:10] t <sub>DSD5</sub> in CFMs  0 0 0 0 1 1 1 0 2 1 1 3 |

| Bit      |                                                              | Description                                         |  |

|----------|--------------------------------------------------------------|-----------------------------------------------------|--|

| 9:8      | Branch Channel 1, DIMM 4 Strobe Offset (t <sub>DSD4</sub> ): |                                                     |  |

| (cont'd) | Bits [9:8]                                                   | t <sub>DSD4</sub> in CFMs                           |  |

|          | 0 0                                                          | 0                                                   |  |

|          | 0 1                                                          | 1                                                   |  |

|          | 10                                                           | 2 3                                                 |  |

| 7:6      |                                                              |                                                     |  |

| 7.0      |                                                              | annel 0, DIMM 3 Strobe Offset (t <sub>DSD3</sub> ): |  |

|          | Bits [7:6]                                                   | t <sub>DSD3</sub> in CFMs                           |  |

|          | 00                                                           | 0<br>1                                              |  |

|          | 10                                                           | 2                                                   |  |

|          | 11                                                           | 3                                                   |  |

| 5:4      | Branch Cha                                                   | annel 0, DIMM 2 Strobe Offset (t <sub>DSD2</sub> ): |  |

|          | Bits [5:4]                                                   | t <sub>DSD2</sub> in CFMs                           |  |

|          | 0 0                                                          | 0                                                   |  |

|          | 01                                                           | 1                                                   |  |

|          | 10                                                           | 2 3                                                 |  |

| 3:2      | Branch Cha                                                   | annel 0, DIMM 1 Strobe Offset (t <sub>DSD1</sub> ): |  |

|          | Bits [3:2]                                                   | t <sub>DSD1</sub> in CFMs                           |  |

|          | 00                                                           | 0                                                   |  |

|          | 0 1                                                          | 1                                                   |  |

|          | 10                                                           | 2 3                                                 |  |

| 4.0      | 11                                                           |                                                     |  |

| 1:0      |                                                              | annel 0, DIMM 0 Strobe Offset (t <sub>DSD0</sub> ): |  |

|          | Bits [1:0]                                                   | t <sub>DSD0</sub> in CFMs                           |  |

|          | 0 0                                                          | 0<br>1                                              |  |

|          | 10                                                           |                                                     |  |

|          | 11                                                           | 3                                                   |  |

# 3.3 MCTIM – Main Channel Timing Register

Address: 03h

Default: 0006h

Access: R/W

Size: 16 bits

| Bit   | Description                                                                                                                                                                                                                                                                |                                                                                   |                        |                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-------------------------------------------------|

| 15:13 | Reserved                                                                                                                                                                                                                                                                   |                                                                                   |                        |                                                 |

| 12    | Data Transfer Size (DTS):                                                                                                                                                                                                                                                  |                                                                                   |                        |                                                 |

|       | 1 = 16-byte Mode. The DMH transfers 16 bytes of data for each access.                                                                                                                                                                                                      |                                                                                   |                        |                                                 |

|       | 0 = 32-byte Mode. The DMH transfers 32 bytes of data for each access.                                                                                                                                                                                                      |                                                                                   |                        |                                                 |

| 11    | Reserved                                                                                                                                                                                                                                                                   |                                                                                   |                        |                                                 |

| 10:8  | Main Channel Read Delay (t <sub>LVL</sub> ): Set by a SNC initialization procedure. Specifies the number of CTM pipe stages that data is delayed from the time that it appears at the DQS I/O pins of the DMH to the time it is driven at the DQA/DQB I/O pins of the DMH. |                                                                                   |                        |                                                 |

|       | Bit[7:4]                                                                                                                                                                                                                                                                   | t <sub>LVL</sub> in CFMs                                                          |                        |                                                 |

|       | 000                                                                                                                                                                                                                                                                        | 2                                                                                 |                        |                                                 |

|       | 0 0 1                                                                                                                                                                                                                                                                      | 3                                                                                 |                        |                                                 |

|       | 010                                                                                                                                                                                                                                                                        | 4<br>5                                                                            |                        |                                                 |

|       | 100                                                                                                                                                                                                                                                                        | 6                                                                                 |                        |                                                 |

|       | 1 0 1                                                                                                                                                                                                                                                                      | 7                                                                                 |                        |                                                 |

|       | 110                                                                                                                                                                                                                                                                        | 8                                                                                 |                        |                                                 |

| 7.5   | 111                                                                                                                                                                                                                                                                        | 9                                                                                 |                        |                                                 |

| 7:5   | Reserved                                                                                                                                                                                                                                                                   |                                                                                   |                        |                                                 |

| 4:0   | Specifies a                                                                                                                                                                                                                                                                | inel Write Delay (t <sub>o</sub><br>additional pipestage<br>of the write data tra | e delays fron          | n the completion of a MCP Write Command, to the |

|       | Bit[4:0]                                                                                                                                                                                                                                                                   | t <sub>CWD</sub> in CFMs                                                          | Bit[4:0]               | t <sub>CWD</sub> in CFMs                        |

|       | 00000                                                                                                                                                                                                                                                                      | Reserved                                                                          | 10000                  | 15                                              |

|       | 00001                                                                                                                                                                                                                                                                      | Reserved                                                                          | 10001                  | 16                                              |

|       | 00010                                                                                                                                                                                                                                                                      | Reserved                                                                          | 10010                  | 17                                              |

|       | 00011                                                                                                                                                                                                                                                                      | Reserved<br>Reserved                                                              | 10011                  | 18<br>19                                        |

|       | 00101                                                                                                                                                                                                                                                                      | Reserved                                                                          | 10101                  | 20                                              |

|       | 00110                                                                                                                                                                                                                                                                      | 5                                                                                 | 10110                  | 21                                              |

|       | 00111                                                                                                                                                                                                                                                                      | 6                                                                                 | 10111                  | 22                                              |

|       | 01000                                                                                                                                                                                                                                                                      | 7<br>8                                                                            | 1 1 0 0 0<br>1 1 0 0 1 | 23<br>24                                        |

|       | 01011                                                                                                                                                                                                                                                                      | 9                                                                                 | 11011                  | 25                                              |

|       | 01011                                                                                                                                                                                                                                                                      | 10                                                                                | 11011                  | 26                                              |

|       | 01100                                                                                                                                                                                                                                                                      | 11                                                                                | 11100                  | 27                                              |

|       | 01101                                                                                                                                                                                                                                                                      | 12                                                                                | 11101                  | 28                                              |

|       | 01110                                                                                                                                                                                                                                                                      | 13<br>14                                                                          | 11110<br>11111         | 29<br>30                                        |

# 3.4 BCTIM – Branch Channel Timing Register

Address: 04h

Default: 0002h

Access: R/W

Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15:9 | Reserved                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 8    | Manual DIMM Path Latency Calibration Enable (DPLE): Setting this bit to 1 causes the DMH to perform a DIMM Path Latency calibration on both branch channels. Upon completion of the calibration, the DMH resets the bit to 0. The Main channel should remain quiescent throughout the calibration procedure. The results of this command are stored in the t <sub>DPL</sub> field of this register. |  |  |

| 7    | Reserved                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 6:4  | Branch Channel DIMM Path Latency (t <sub>DPL</sub> ): Specifies the number of CFM round-trip delays from the time a DIMM drives data to the time it appears at the I/O pins of the DMH. This field is typically set by the DIMM path calibration procedure (see DPLE field above), but can be set manually as well.                                                                                 |  |  |

|      | Bit[6:4] t <sub>DPL</sub> in CFMs                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|      | 000 0<br>001 1<br>010 2<br>011 3<br>100 4<br>101 5<br>110 6<br>111 7                                                                                                                                                                                                                                                                                                                                |  |  |

| 3    | Reserved                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 2:0  | DIMM CAS Latency (t <sub>CL</sub> ): This bit specifies the number of SCLKs from when a read command is sampled by the SDRAMs to when the DMH samples read data from the SDRAMs.                                                                                                                                                                                                                    |  |  |

|      | Bit[2:0] t <sub>CL</sub> in SCLKs                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|      | 0 0 0 Reserved<br>0 0 1 Reserved<br>0 1 0 2<br>0 1 1 Reserved<br>1 0 0 Reserved<br>1 0 1 1.5<br>1 1 0 2.5<br>1 1 1 Reserved                                                                                                                                                                                                                                                                         |  |  |

# 3.5 DGR – DIMM Geometry Register

Address: 05h

Default: 0000h

Access: R/W

Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15:8 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 7:0  | Branch Channel Geometry: Each bit specifies the X4 or X8 geometry of a single or double-density DIMM. This configures the DMH to respond to the appropriate DIMM data strobes and drive dual-use DQM pins appropriately Setting a bit to 0 indicates X4 geometry, while setting a bit to one specifies X8 geometry.                                                                                                           |  |  |

|      | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|      | Controls geometry for Branch Channel 0, DIMM0 Controls geometry for Branch Channel 0, DIMM1 Controls geometry for Branch Channel 0, DIMM2 Controls geometry for Branch Channel 0, DIMM3 Controls geometry for Branch Channel 1, DIMM0 Controls geometry for Branch Channel 1, DIMM1 Controls geometry for Branch Channel 1, DIMM2 Controls geometry for Branch Channel 1, DIMM2 Controls geometry for Branch Channel 1, DIMM3 |  |  |

# 3.6 MRF – Mode Register Set Function Register

Address: 06h

Default: 0000h

Access: R/W

Size: 16 bits

| Bit  | Description                                                                                                                                               |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Reserved                                                                                                                                                  |

| 14:0 | Mode Register Function (MRF): A[14:0] bit values to be used with MRS command of <b>SDI</b> register below. See MRF bits of the <b>SDI</b> register below. |

# 3.7 SDI – SDRAM Initialization Register

Address: 07h

Default: 0000h

Access: R/W

Size: 16 bits

| Bit   |                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | Reserved                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10    | When this rows on bo                                                     | SIC (BRD): bit is set to 1, the command specified by the SIC field (bits [2:0]) is issued to all SDRAM oth branch channels. When this bit is 0, the SIC command is issued only to the branch nd row specified by the BC and CS fields.                                                                                                                                                                                                                                                                                                            |

| 9:8   | These bits                                                               | ister Function (MRF): define the value of BA[1:0] driven on the SDRAM pins during an MRS command. The onto A[14:0] are defined in the preceding MRF register.                                                                                                                                                                                                                                                                                                                                                                                     |

| 7     | When set t                                                               | C Operation (ISO): to 1, the execution of the command specified in the SIC field starts. After the execution is the DMH clears this bit to 0. The software must check to see if this bit is 0 before writing ster.                                                                                                                                                                                                                                                                                                                                |

| 6     | Specifies that 1 = Branc                                                 | annel (BC):<br>he branch channel to be used with the SIC operation when the BRD field is set to 0.<br>h Channel 1<br>h Channel 0                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5:3   | Specifies the set to 0.                                                  | e Select (CS):<br>he DIMM Side (by Chip Select) to be used with the SIC operation when the BRD field is                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | Bits[5:3]<br>0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 1 | DIMM Side Select  CS#[0]  CS#[1]  CS#[2]  CS#[3]  CS#[4]  CS#[6]  CS#[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.0   | This field a on the brar SDRAMs. to logic one                            | itialization Command (SIC): illows the DMH to issue various commands to the SDRAM row specified by the CS field, inch channel specified by the BC field. This field is provided for BIOS to initialize the The BIOS programs this field with an appropriate command and then sets the ISO field is. When the DMH observes the ISO field set to 1 it performs the operation specified by Id. Upon completion of the operation, DMH sets the ISO field to logic 0.  SIC  NOP Command: When DMH receives this command it issues a NOP command to the |

|       | 001                                                                      | DIMM side specified by the BC and CS bits of this register.  DDR delay line calibration: When DMH receives this command it issues a DDR delay line calibration sequence to both branch channels. This command sets the DQS strobe delay to 2.2ns. This command ignores CS, BC, and BRD.  Do not perform this command while in self-refresh mode.                                                                                                                                                                                                  |

|       | 010                                                                      | Precharge: When DMH receives this command it issues a Precharge command to the DIMM side specified by the BC and CS bits of this register. Precharge mode (all banks or single bank) is determined by Bank Address (BA) and precharge all (PA) bits, which are set through the MRF field of this register and the preceding MRF register. Refer to Jedec Standard JESD79 for Precharge command details.                                                                                                                                           |

|       | 011                                                                      | Mode Register Set: When DMH receives this command it issues a Mode Register Set (MRS) command. The MRF bits of this register, combine with the preceding MRF register to define the DDR SDRAM Mode register bits. Refer to Jedec Standard JESD79 for Mode Register Set command details.                                                                                                                                                                                                                                                           |

| Bit      |     | Description                                                                                                                                                                     |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0      | 100 | Reserved                                                                                                                                                                        |

| (cont'd) | 101 | Auto Refresh: When the DMH receives this command it issues an Auto Refresh command to the DIMM side specified by the BC and CS bits of this register. This command ignores BRD. |

|          | 110 | Reserved                                                                                                                                                                        |

|          | 111 | Reserved                                                                                                                                                                        |

# 3.8 RCC – RAMBUS Current Control Register

Address: 0Bh

Default: 0040h

Access: R/W

Size: 16 bits

This register returns the value of the RAC's internal Current Calibration register, which is set by performing a manual current calibration or by auto calibration (see Section 4.4.1, "Current Calibration").

Note:

The contents written to this register cannot be directly read back. After writing to this register, preform a Manual Current Calibration to load the register contents into the RAC's internal Current Calibration register.

| Bit  | Description                                                                                    |  |

|------|------------------------------------------------------------------------------------------------|--|

| 15:7 | Reserved                                                                                       |  |

| 6:0  | Current Control: This seven bit field controls the current for RSL pins DQA[8:0] and DQB[8:0]. |  |

# 3.9 RIR – RAC Initialization Register

Address: 0Ch Default: 0000h

Access: R/W: RIC, IRO R-O: RC, RSP

40.11.

Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:6 | Reserved                                                                                                                                                                                                                                                   |

| 5    | Ready for Synchronization Packet (RSP): The DMH sets this bit to 1 when it is ready to accept a Clock-Synchronization MCP. The BIOS must check this bit before sending the Synchronization packet to DMH.                                                  |