#### **DATA COMMUNICATIONS**

# 9-Line ULTRA3 LVD/SE SCSI Terminator

The IMP2119 is a multimode SCSI terminator that conforms to the SCSI Parallel Interconnect-2 (SPI-2) specification developed by the T10 standards committee for low voltage differential (LVD) termination. Multimode compatibility permits the use of legacy devices on the bus without hardware alterations. Automatic mode selection is achieved through voltage detection on the diffsense line.

The IMP2119 delivers the ultimate in SCSI bus performance while saving component cost and board area. Elimination of the external capacitors also mitigates the need for a lengthy capacitor selection process. The individual high bandwidth drivers also maximize channel separation and reduce channel to channel noise and cross talk. The high bandwidth architecture insures ULTRA3 performance.

When the IMP2119 is enabled, the differential sense (DIFFSENSE) pin supplies a voltage between 1.2V and 1.4V. In application, this pin is tied to the DIFFSENSE input of the corresponding LVD transceivers. This action enables the LVD transceiver function. DIFFSENSE is capable of supplying a maximum of 15mA. Tying the DIFFSENSE pin HIGH places the IMP2119 in a high impedance state indicating the presence of an HVD device. Tying the pin LOW places the part in a single-ended mode while also signaling the multimode transceiver to operate in a single-ended mode.

Recognizing the needs of portable and configurable peripherals, the IMP2119 have a TTL compatible sleep/disable mode. During this sleep/disable mode, power dissipation is reduced to a meager 15µA while also placing all outputs in a high impedance state. Also during

#### **Key Features**

- Auto-selectable LVD or single-ended termination

- ◆ 3.0pF maximum disabled output capacitance

- ◆ Fast response, no external capacitors required

- ◆ Compatible with active negation drivers

- ♦ 15µA supply current in disconnect mode

- ◆ Logic command disconnects all termination lines

- **◆ DIFFSENSE line driver**

- Ground driver integrated for single-ended operation

- ◆ Current limit and thermal protection

- ◆ Hot-swap compatible (single-ended)

- ◆ Compatible with SCSI, SPI-2, SPI-3, SPI-4 ULTRA160 and ULTRA320

- ◆ Pin compatible with DS2119

sleep/disable mode, the DIFFSENSE function is disabled and is placed in a high impedance state.

Another key feature of the IMP2119 is the master/slave function. Driving this pin HIGH or floating the pin enables the 1.3V DIFFSENSE reference. Driving the pin LOW disables the on board DIFFSENSE reference and enables use of an external master reference device.

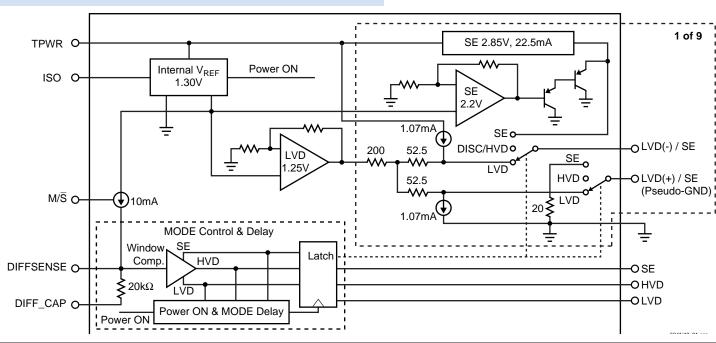

### **Block Diagram**

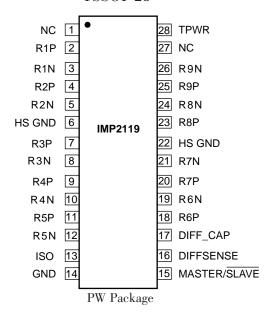

#### **Pin Configuration**

#### TSSOP-28

## **Ordering Information**

| Part Number | Temperature Range | Package              |

|-------------|-------------------|----------------------|

| IMP2119CPW  | 0°C to 70°C       | 28-pin Plastic TSSOP |

For Tape and Reel, append the letter "T" to part number. (i.e. IMP2119CPW/T) Note:

## Absolute Maximum Ratings<sup>1</sup>

TermPwr Voltage .....+7V **Operating Junction Temperature** Storage Temperature Range .....-65°C to 150°C Lead Temperature (Soldering, 10 sec.) ..... 300°C

1. Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of the specified terminal.

#### Thermal Data

PW Package:

Thermal Resistance Junction-to-Ambient,  $\theta_{JA}$  .....  $100^{\circ}C/W$

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. No ambient airflow is assumed.

## Pin Description

| Function                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Negative signal termination lines for LVD mode. Signal termination lines for SE mode.                                                                                       |

| Positive signal termination lines for LVD mode. Pseudo-ground lines for SE mode.                                                                                            |

| Power supply pin for terminator. Connect to SCSI bus TermPwr. Must be decoupled by one                                                                                      |

| 4.7μF low-ESR capacitor for every three terminator devices. It is absolutely necessary to                                                                                   |

| connect this pin to the decoupling capacitor through a very low impedance (big traces on PCB).                                                                              |

| Keeping distances very short from the decoupling capacitors to the TPWR pin is also critical.                                                                               |

| The value of the decoupling capacitor is somewhat layout dependant and some applications may benefit from an additional 0.1µF decoupling capacitor at the TPWR pin.         |

| Enables / disables terminator. See Table 2 for logic levels                                                                                                                 |

| Terminator ground pin. Connect to ground                                                                                                                                    |

| Sometimes referred to as M/S pin. Used to select which terminator is the controlling device. MASTER/SLAVE pin HIGH or Open enables the DIFFSENSE output drive. See Table 1. |

| This is a dual function pin. It drives the SCSI bus DIFFSENS line. It is also the sense pin to                                                                              |

| detect the SCSI bus mode (LVD, SE or HVD). DIFFSENSE output drive can be disabled with a                                                                                    |

| LOW level on the MASTER/SLAVE pin. See Table 1 and Table 2. Internally connected to DIFF _CAP pin trough 20Kohms resistor.                                                  |

| Internally connected to DIFFSENSE pin through $20k\Omega$ resistor. It can be used as a mode sense                                                                          |

| pin when the device is a non-controlling terminator (MASTER/SLAVE pin is LOW). An RC filter                                                                                 |

| $(20k\Omega / 0.1\mu\text{F})$ is not required on the IMP2119 , as it has an internal timer.                                                                                |

| No Connect. Pins should be left open.                                                                                                                                       |

| ·                                                                                                                                                                           |

|                                                                                                                                                                             |

|                                                                                                                                                                             |

|                                                                                                                                                                             |

© 2002 IMP, Inc. Data Communications

## Recommended Operating Conditions<sup>2</sup>

|                          | Parameter | Symbol            | Min | Тур | Max        | Units       |

|--------------------------|-----------|-------------------|-----|-----|------------|-------------|

| TermPwr Voltage          | LVD       | V <sub>TERM</sub> | 3.0 |     | 5.25       | V           |

|                          | SE        |                   | 3.5 |     | 5.25       |             |

| Signal Line Voltage      |           |                   | 0   |     | 5.0        | V           |

| Disconnect Input Voltage |           |                   | 0   |     | $V_{TERM}$ | V           |

| Operating Virtual Junct  |           | 0                 |     | 70  | °C         |             |

|                          |           | -                 |     |     |            | 5044/40 400 |

Note: 2. Range over which the device is functional.

5241/42\_t03.ep

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over the operating ambient temperature range of  $0^{\circ}C \le T_A \le 70^{\circ}C$ . TermPwr = 4.75V. ISO : IMP2119 = LOW. Low duty cycle pulse testing techniques are used which maintain junction and case temperatures equal to the ambient temperature.

| Parameter                         | Symbol                   | Condition                                      | Min   | Тур  | Max   | Units |

|-----------------------------------|--------------------------|------------------------------------------------|-------|------|-------|-------|

| LVD Terminator Section            |                          |                                                |       | • -  |       |       |

| TermPwr Supply Current            | LVD <sub>ICC</sub>       | All terminator lines = Open                    |       | 25   | 30    | mA    |

|                                   |                          | ISO> 2.0 V                                     |       | 1    | 35    | μΑ    |

| Common Mode Voltage               | $V_{CM}$                 |                                                | 1.125 | 1.25 | 1.375 | V     |

| Offset Voltage                    | $V_{FSB}$                | Open circuit between – and + (see Note 3)      | 100   | 112  | 125   | mV    |

| Differential Terminator Impedance | $Z_D$                    | $V_{OUT}$ differential = $-1V$ to $1V$         | 100   | 105  | 110   | Ω     |

| Common Mode Impedance             | Z <sub>CM</sub>          | 0V to 2.5V                                     | 100   | 200  | 300   | Ω     |

| Output Capacitance                | Co                       | ISO > 2.0 V                                    |       | 2.5  |       | pF    |

| Output Leakage                    | I <sub>LEAK</sub>        | ISO > 2.0V                                     |       |      | 2     | μΑ    |

|                                   |                          | $V_{LINE} = 0V$ to 4V, $T_A = 25$ °C           |       |      |       |       |

|                                   |                          | ISO > 2.0 V                                    |       | 1    |       |       |

|                                   |                          | TPWR = $0V$ , $V_{LINE} = 2.7V$                |       |      |       |       |

| Mode Change Delay                 | t <sub>DF</sub>          | DIFFSENSE = 1.4V to 0V                         |       | 115  |       | ms    |

| DIFFSENSE Section                 |                          |                                                |       |      |       |       |

| DIFFSENSE Output Voltage          | $V_{DIFF}$               |                                                | 1.2   | 1.3  | 1.4   | V     |

| DIFFSENSE Output Source Current   | I <sub>DIFF</sub>        | $V_{DIFF} = 0V$                                | 5.0   |      | 15.0  | mA    |

| DIFFSENSE Sink Current            | I <sub>SINK (DIFF)</sub> | V <sub>DIFF</sub> = 2.75V                      |       |      | 200   | μΑ    |

| DIFFSENSE Output Leakage          | I <sub>LEAK (DIFF)</sub> | ISO > 2.0V                                     |       |      | 10    | μΑ    |

|                                   |                          | T <sub>A</sub> = 25°C                          |       |      |       |       |

| Single-Ended Terminator Section   |                          |                                                |       |      |       |       |

| TermPwr Supply Current            | SE I <sub>CC</sub>       | All terminator lines = Open, MASTER/SLAVE = 0V |       | 7    | 10    | mA    |

|                                   |                          | All terminator lines = 0.2V, MASTER/SLAVE = 0V |       | 214  | 226   |       |

|                                   |                          | DISCONNECT > 2.0V                              |       | 15   | 35    | μΑ    |

| Terminator Output High Voltage    | Vo                       |                                                | 2.6   | 2.85 |       | V     |

| Output Current                    | Io                       | V <sub>OUT</sub> = 0.2V                        | 21    | 23   | 24    | mA    |

| Sink Current                      | I <sub>SINK</sub>        | V <sub>OUT</sub> = 4V, all lines               | 45    | 65   |       | mA    |

| Output Capacitance                | Co                       | ISO > 2.0V                                     |       | 2.5  |       | pF    |

| Leakage Current                   | I <sub>LEAK</sub>        | ISO > 2.0V                                     |       |      | 2     | μΑ    |

|                                   |                          | $V_{OUT} = 0V$ to 4V, $T_A = 25$ °C            |       |      |       |       |

|                                   |                          | ISO > 2.0 V                                    |       | I    |       |       |

|                                   |                          | TPWR= 0V, $_{LINE}$ = 2.7V, $T_{A}$ = 25°C     |       |      |       |       |

| Ground Driver Impedance           | Z <sub>G</sub>           | I = 1mA                                        |       |      | 100   | Ω     |

| Thermal Shutdown                  |                          |                                                |       | 150  |       | °C    |

Note: 3. Open circuit fallsafe voltage.

## **Electrical Characteristics**

| Parameter               | Symbol               | Condition           | Min                                   | Тур | Max | Units |

|-------------------------|----------------------|---------------------|---------------------------------------|-----|-----|-------|

| ISO Section             |                      |                     | · · · · · · · · · · · · · · · · · · · |     |     |       |

| ISO Thresholds          | V <sub>TH</sub>      |                     | 0.8                                   |     | 2.0 | V     |

| Input Current           | I <sub>IL</sub>      | ISO= 0 V            |                                       |     | 10  | μΑ    |

|                         | I <sub>IH</sub>      | ISO = 2.4V          |                                       | 100 |     | nA    |

| MASTER/SLAVE Section    |                      |                     | · · · · · · · · · · · · · · · · · · · |     |     |       |

| MASTER/SLAVE Thresholds | V <sub>TH (MS)</sub> |                     | 0.8                                   |     | 2.0 | V     |

| Input Current           | I <sub>IL (MS)</sub> | MASTER/SLAVE = 0V   |                                       |     | 10  | μΑ    |

|                         | lu (Me)              | MASTER/SLAVE = 2.4V |                                       | 100 |     | nA    |

© 2002 IMP, Inc. Data Communications

## **Application Information**

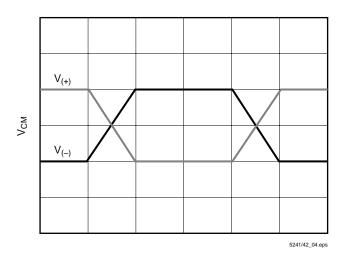

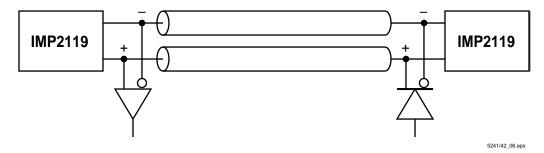

Figure 1. Bus Voltage

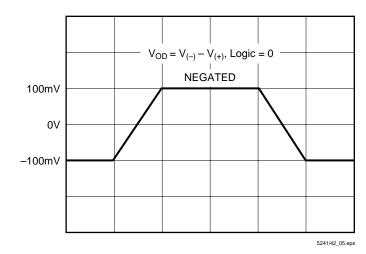

Figure 2. V<sub>OD</sub>

Figure 3.

Table 1. MASTER/SLAVE Function Table

| MASTER/SLAVE   | DIFFSENSE Status | Output Current |

|----------------|------------------|----------------|

| L*             | HiZ              | 0mA            |

| Н              | 1.3V             | 15mA Source    |

| Open (Pull-up) | 1.3V             | 15mA Source    |

<sup>\*</sup> When in the LOW state, the terminator will detect the DIFFSENSE line state.

5241/42\_t06.at3

Table 2. DIFFSENSE/Power Up/Power Down Function Table

| IMP2119    |              | Outputs |      |         |

|------------|--------------|---------|------|---------|

| DISCONNECT | DIFFSENSE    | Status  | Туре | Current |

| L          | L < 0.5V     | Enable  | SE   | 7mA     |

| L          | 0.7V to 1.9V | Enable  | LVD  | 21mA    |

| L          | H > 2.4V     | Disable | Hi Z | 1mA     |

| Н          | X            | Disable | Hi Z | 10μΑ    |

| Open       | X            | Disable | Hi Z | 10μΑ    |

5241/42\_t07.eps

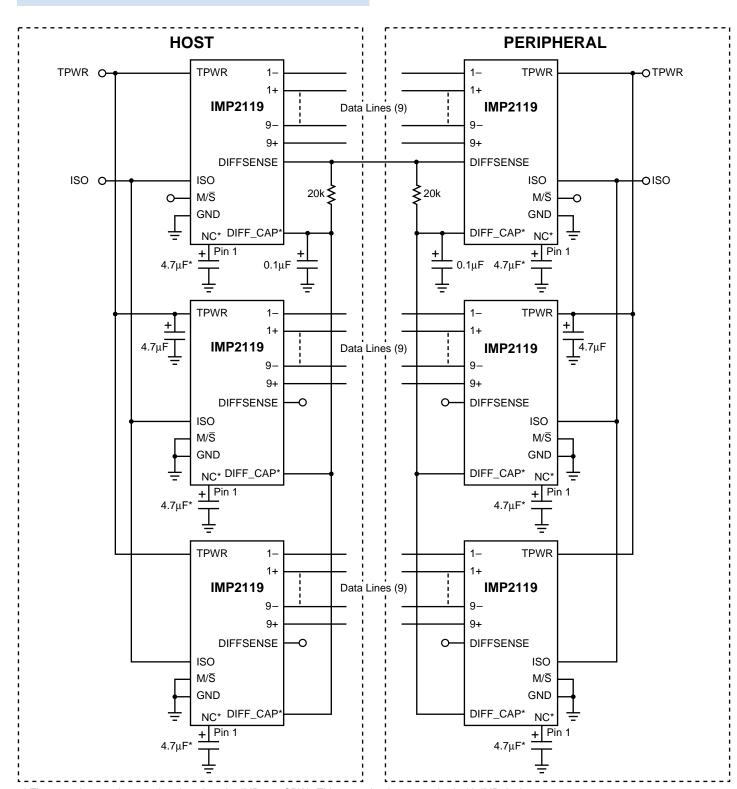

## **Application Information**

<sup>\*</sup> The capacitor on pin 1 can be placed on the IMP2119CPW. This capacitor is not required with IMP devices.

Figure 5. Suggested IMP2119 Universal Application Schematic

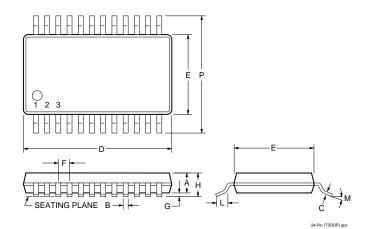

## **Package Dimensions**

#### PW

#### Thin Small Shrink Outline (TSSOP) (28-Pin)

| Inches |           |                 | Millimeters    |        |  |

|--------|-----------|-----------------|----------------|--------|--|

|        | Min       | Min Max         |                | Max    |  |

|        | Thin Smal | ll Shrink Outli | ne (TSSOP) (28 | 3-Pin) |  |

| Α      | .032      | .041            | 0.80           | 1.05   |  |

| В      | 0.007     | 0.012           | 0.19           | 0.30   |  |

| С      | 0.0035    | 0.0079          | 0.09           | 0.20   |  |

| D      | 0.378     | 0.386           | 9.60           | 9.80   |  |

| Е      | 0.169     | 0.176           | 4.30           | 4.5    |  |

| F      | 0.025     | BSC             | 0.65 BSC       |        |  |

| G      | 0.002     | 0.005           | 0.05           | 0.15   |  |

| Н      | _         | 0.047           | _              | 1.20   |  |

| L      | 0.017     | 0.030           | 0.45           | 0.75   |  |

| М      | 0°        | 8°              | 0°             | 8°     |  |

| Р      | 0.246     | 0.256           | 6.25           | 6.50   |  |

| *LC    | -         | 0.004           | _              | 0.10   |  |

<sup>\*</sup> Lead Coplanarity.

5241/42\_t01.

IMP, Inc. Corporate Headquarters 2830 N. First Street San Jose, CA 95134-2071

Tel: 408-432-9100 Fax: 408-434-1085

e-mail: info@impinc.com http://www.impweb.com