## Liquid Crystal Display Controller

The IN472-3-3 Liquid Crystal Display (LDC) Controller is a perpheral member of the COPS<sup>TM</sup> family, fabricated using CMOS technology. The IN472-3 drives a multiplexed liquid crystal directly. Data is loaded serially and is held in internal latches. The In472-3 contains an on-chip oscillator and generates all the multi-level waveforms for back-planes and segment outputs on a triplex display. One IN472-3 can drive 36 segments multiplexed as  $3 \times 12$  ( $4^{1}/_{2}$  digit display). Two IN472-3 devices can be used together to drive 72 segments ( $3 \times 24$ ) which could be an  $8^{1}/_{2}$  digit display.

- Direct interface to TRIPLEX LCD

- Low power dissipation (100 µW typ.)

- Low cost

- Compatible with all COP400 processors

- Needs no refresh from processor

- On-chip oscillator and latches

- Expandable to longer displays

- Software compatible with COP470 V.F.Display Driver Chip

- Operates from display voltage

- MICROWIRE<sup>TM</sup> compatible serial I/O

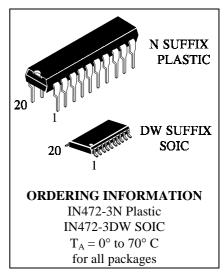

- 20-pin Dual-In-Line package

| <b>Pin Description</b> |

|------------------------|

|------------------------|

| Pin             | Description                             |

|-----------------|-----------------------------------------|

| CS              | Chip select                             |

| V <sub>DD</sub> | Power supply (display voltage)          |

| GND             | Ground                                  |

| DI              | Serial data input                       |

| SK              | Serial clock input                      |

| BPA             | Display backplane A (or oscillator in)  |

| BPB             | Display backplane B                     |

| BP <sub>C</sub> | Display backplane C (or oscillator out) |

| SA1~SA4         | 12 multiplexed outputs                  |

## PIN ASSIGNMENT

| SB1        | C | 1• | 20         | þ | SA4 |

|------------|---|----|------------|---|-----|

| SC3        | Ľ | 2  | 1 <b>9</b> | þ | SA3 |

| SB3        | Ľ | 3  | 1 <b>8</b> | þ | SC1 |

| CS         | Ľ | 4  | 17         | þ | BPB |

| $v_{DD}$   | С | 5  | 1 <b>6</b> | þ | BPC |

| GND        | C | 6  | 15         | þ | BPA |

| <b>D</b> 1 | С | 7  | 14         | þ | SK  |

| SA2        | C | 8  | 13         | þ | SC4 |

| SB4        | Ľ | 9  | 12         | þ | SC2 |

| SB2        | С | 10 | 11         | þ | SA1 |

|                                 |                                    |                        | Guarant                  | eed Limit              |      |

|---------------------------------|------------------------------------|------------------------|--------------------------|------------------------|------|

| Symbol                          | Parameter                          | Test<br>Conditions     |                          | Max                    | Unit |

| $V_{\text{DD}}$                 | Power Supply Voltage               |                        | 3.0                      | 5.5                    | V    |

| I <sub>DD</sub>                 | Power Supply Current (Note 1)      | V <sub>DD</sub> =5.5 V |                          | 250                    | μA   |

| V <sub>IL</sub>                 | Input Levels DI, SK, CS            |                        |                          | 0.8                    | V    |

| V <sub>IH</sub>                 |                                    |                        | $0.7 V_{DD}$             | V <sub>DD</sub>        |      |

| V <sub>IL</sub>                 | BPA (as Osc. in)                   |                        |                          | 0.6                    | V    |

| $V_{\mathrm{IH}}$               |                                    |                        | V <sub>DD</sub> -0.6     | V <sub>DD</sub>        |      |

| V <sub>OL</sub>                 | Output Levels, BPC (as Osc. Out)   |                        |                          | 0.4                    | V    |

| V <sub>OH</sub>                 |                                    |                        | V <sub>DD</sub> -0.4     | V <sub>DD</sub>        |      |

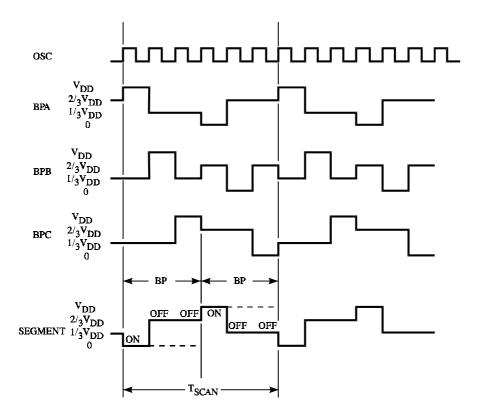

| V <sub>BPA,BPB,BPC</sub><br>ON  | Backplane Outputs (BPA,BPB,BPC)    | During                 | $V_{DD}$ - $\Delta V$    | V <sub>DD</sub>        | V    |

| V <sub>BPA,BPB,BPC</sub><br>OFF |                                    | BP + Time              | $1/3V_{DD}$ - $\Delta V$ | $1/3V_{DD} + \Delta V$ |      |

| V <sub>BPA,BPB,BPC</sub><br>ON  | Backplane Outputs (BPA,BPB,BPC)    | During                 | 0                        | ΔV                     | V    |

| V <sub>BPA,BPB,BPC</sub><br>OFF |                                    | BP - Time              | $2/3V_{DD}$ - $\Delta V$ | $2/3V_{DD} + \Delta V$ |      |

| V <sub>SEG</sub> ON             | Segment Outputs $(SA_1 \sim SA_4)$ | During                 | 0                        | ΔV                     | V    |

| V <sub>SEG</sub> OFF            |                                    | BP + Time              | $2/3V_{DD}$ - $\Delta V$ | $2/3V_{DD} + \Delta V$ |      |

| V <sub>SEG</sub> ON             | Segment Outputs $(SA_1 \sim SA_4)$ | During                 | $V_{DD}$ - $\Delta V$    | V <sub>DD</sub>        | V    |

| V <sub>SEG</sub> OFF            |                                    | BP - Time              | $1/3V_{DD}$ - $\Delta V$ | $1/3V_{DD} + \Delta V$ |      |

|                                 | Internal Oscillator Frequency      |                        | 15                       | 80                     | kHz  |

|                                 | Frame Time (Int. Osc. ÷ 192)       |                        | 2.4                      | 12.8                   | ms   |

| $1/T_{SCAN}$                    | Scan Frequency                     |                        | 39                       | 208                    | Hz   |

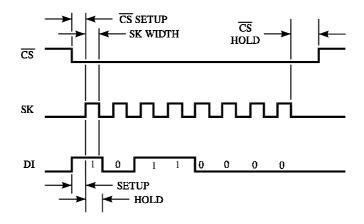

|                                 | SK Clock Frequency                 |                        | 4                        | 250                    | kHz  |

|                                 | SK Width                           |                        | 1.7                      |                        | μs   |

| t <sub>SETUP</sub>              | DI Data Stup                       |                        | 1.0                      |                        | μs   |

| t <sub>HOLD</sub>               | DI Data Hold                       |                        | 100                      |                        | ns   |

| t <sub>SETUP</sub>              | CS                                 |                        | 1.0                      |                        | μs   |

| t <sub>HOLD</sub>               | 1                                  |                        | 1.0                      |                        | 1    |

|                                 | Output Loading Capacitance         |                        |                          | 100                    | pF   |

## **DC ELECTRICAL CHARACTERISTICS** (GND=0 V, $V_{DD}$ =3.0 V to 5.5 V, $T_A$ = 0°C to 70°C (depends on display characteristics)

Note 1: Power supply current as measured in stand-alone mode with all outputs open and all inputs at  $V_{DD}$ . Note 2:  $\Delta V - 0.05 V_{DD}$ .

Figure 1. Serial Load Timing Diagram

Figure 2. Backplane and Segment Waveforms