# GUARANTEED LOW SKEW CMOS CLOCK DRIVER/BUFFER

QS532807

### **FEATURES:**

- JEDEC compatible LVTTL level

- 10 low skew clock outputs

- Clock input is 5V tolerant

- Pinout and function compatible with QS5807

- $25\Omega$  on-chip resistors available for low noise

- Input hysteresis for better noise margin

- Guaranteed low skew:

- 0.35ns output skew (same bank)

- 0.6ns output skew (different bank)

- 0.75ns part-to-part skew

- Available in QSOP and SOIC packages

### **DESCRIPTION:**

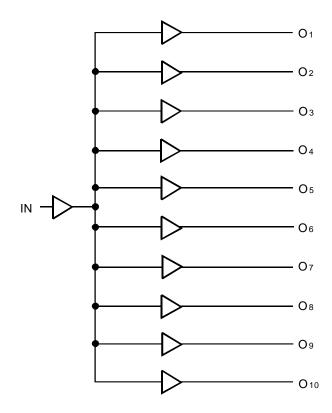

The QS532807 clock driver/buffer circuit can be used for clock buffering schemes where low skew is a key parameter. The QS532807 offers ten non-inverting outputs. Designed in IDT's proprietary QCMOS process, these devices provide low propagation delay buffering with onchip skew of 0.35ns for same-transition, same bank signals. The QS532807 has on-chip series termination resistors for lower noise clock signals. The QS532807 series resistor version is recommended for driving unterminated lines with capacitive loading and other noise sensitive clock distribution circuits. These clock buffer products are designed for use in high-performance workstations, embedded and personal computing systems. Several devices can be used in parallel or scattered throughout a system for guaranteed low skew, system-wide clock distribution networks.

# **FUNCTIONAL BLOCK DIAGRAM**

# INDUSTRIAL TEMPERATURE RANGE

SEPTEMBER 2000

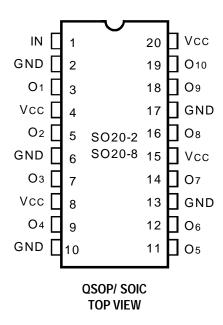

# **PIN CONFIGURATION**

# **ABSOLUTE MAXIMUM RATINGS (1)**

| Symbol                | Description                             | Max.             | Unit |

|-----------------------|-----------------------------------------|------------------|------|

| V <sub>TERM</sub> (2) | Supply Voltage to Ground                | - 0.5 to +4.6    | ٧    |

|                       | DC Output Voltage Vouт                  | - 0.5 to Vcc+0.5 | ٧    |

| V <sub>TERM</sub> (3) | DC Input Voltage VIN                    | - 0.5 to +7      | ٧    |

| Vac                   | AC Input Voltage (pulse width ≤20ns)    | -3               | ٧    |

| Іоит                  | DC Output Current VIN < 0               | -20              | mA   |

|                       | DC Output Current Max. Sink Current/Pin | 120              | mA   |

| Tstg                  | Storage Temperature                     | - 65 to +150     | °C   |

| TJ                    | Junction Temperature                    | 150              | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Vcc Terminals.

- 3. All terminals except Vcc.

# **CAPACITANCE** $(T_A = +25^{\circ}C, f = 1.0MHz, V_{IN} = 0V)$

|      | QSOP |          | SOIC |          |      |

|------|------|----------|------|----------|------|

| Pins | Тур. | Max. (1) | Тур. | Max. (1) | Unit |

| CIN  | 3    | 6        | 5    | 7        | pF   |

#### NOTE:

1. This parameter is guaranteed but not production tested.

## PIN DESCRIPTION

| Pin Names | 1/0 | Description   |

|-----------|-----|---------------|

| IN        | ĺ   | Clock Input   |

| Ox        | 0   | Clock Outputs |

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial:  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 3.3V \pm 0.3V$

| Symbol       | Parameter                   | Test Conditions                         | Min.      | Typ. <sup>(1)</sup> | Max. | Unit |

|--------------|-----------------------------|-----------------------------------------|-----------|---------------------|------|------|

| VIH          | Input HIGH Voltage          | Guaranteed Logic HIGH for All Inputs    | 2         | 1.7                 | 5.5  | ٧    |

| VIL          | Input LOW Voltage           | Guaranteed Logic LOW for All Inputs     | -0.5      | _                   | 0.8  | V    |

| Vic          | Clamp Diode Voltage (3)     | Vcc = Min., IIN = -18mA                 | _         | -0.7                | -1.2 | ٧    |

| Vон          | Output HIGH Voltage         | Vcc = Min., Iон = -100µA                | Vcc - 0.2 | _                   | _    | ٧    |

|              |                             | Vcc = Min., IOH = -8mA                  | 2.4       | _                   | _    |      |

|              |                             | Vcc = Min., IoL = 100μA                 | _         | _                   | 0.2  |      |

| Vol          | Output LOW Voltage          | Vcc = Min., IoL = 6mA                   | _         | _                   | 0.4  | ٧    |

|              |                             | Vcc = Min., IoL = 8mA                   | _         | _                   | 0.5  |      |

| lin          | Input Leakage Current       | Vcc = Max., Vin = Vcc or GND            | _         | _                   | ±1   | μΑ   |

| loff         | Input Power Off Leakage     | Vcc = 0V, VIN = Vcc or GND              | _         | _                   | ±1   | μΑ   |

| los          | Short Circuit Current (2,3) | Vcc = Max., Vout = GND                  | -60       | -195                | _    | mA   |

| lodh         | Output HIGH Current         | Vcc = 3.3V, VIN = VIH or VIL, VO = 1.5V | -50       | -80                 | -200 | mA   |

| IODL         | Output LOW Current          | Vcc = 3.3V, VIN = VIH or VIL, VO = 1.5V | 50        | 112                 | 200  | mA   |

| $\Delta V$ T | Input Hysteresis            | VTLH - VTHL for All Inputs              | _         | 0.2                 | _    | ٧    |

| Rout         | Output Resistance (4)       | Vcc = Min., IoL = 12mA                  | _         | 28                  | _    | Ω    |

#### NOTES:

- 1. Typical values are at Vcc = 3.3V, TA = 25°C.

- 2. Not more than one output should be used to test this high power condition. Duration is less than one second.

- 3. Guaranteed by design but not tested.

- 4. Output resistance represents the total output impedance of the logic device and includes added series termination resistance.

# POWER SUPPLY CHARACTERISTICS

| Symbol | Parameter                                   | Test Conditions                  |                  | Typ. <sup>(2)</sup> | Max. | Unit            |

|--------|---------------------------------------------|----------------------------------|------------------|---------------------|------|-----------------|

| Icc    | Quiescent Power Supply Current              | Vcc = Max., Vin = GND or Vcc     |                  | 0.01                | 100  | μΑ              |

| Δlcc   | Supply Current per Input HIGH               | Vcc = Max., Vin = 3V             |                  | 0.1                 | 30   | μΑ              |

|        |                                             | Input toggling at 50% duty cycle |                  |                     |      |                 |

| ICCD   | Dynamic Power Supply Current per Output (1) | Vcc = Max., outputs Enabled      |                  | 60                  | 90   | μ <b>A</b> /MHz |

| Ic     | Total Power Supply Current Examples (1,3)   | VCC = Max.,                      | VIN = GND or Vcc | 6                   | 10   | mA              |

|        |                                             | Input at 50% duty cycle          |                  |                     |      |                 |

|        |                                             | fi = 10MHz                       |                  |                     |      |                 |

|        |                                             | VCC = Max.,                      | VIN = GND or Vcc | 1.5                 | 3    |                 |

|        |                                             | Input at 50% duty cycle          |                  |                     |      |                 |

|        |                                             | $f_1 = 2.5MHz$                   |                  |                     |      |                 |

#### NOTES

- 1. Guaranteed by design but not tested. CL = 0pF.

- 2. Typical values are for reference only. Conditions are Vcc = 3.3V, TA = 25°C.

- 3.  $IC = ICC + (\Delta ICC)(DH)(NT) + ICCD (fo)(No)$

where:

DH = Input Duty Cycle

NT = Number of TTL HIGH inputs at DH (one)

fo = Output Frequency

No = Number of outputs at fo (ten)

# **SWITCHING CHARACTERISTICS OVER OPERATING RANGE**

$T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 3.3V \pm 0.3V$

CLOAD = 50pF (no resistor)

| Symbol       | Parameter (1)                                                                  | Min. | Max. | Unit |

|--------------|--------------------------------------------------------------------------------|------|------|------|

| tsk(01)      | Skew between all outputs, same transition                                      | Ī    | 0.5  | ns   |

| tsk(p)       | Pulse Skew; skew between opposite transitions of the same output (tphl - tplh) | 1    | 0.5  | ns   |

| tsk(t)       | Part-to-part skew (2)                                                          | _    | 1    | ns   |

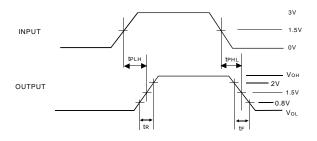

| tplh<br>tphl | Propagation Delay <sup>(3)</sup> IN to Ox                                      | 1.5  | 5.2  | ns   |

| tr           | Output Rise Time, 0.8V to 2V                                                   | l    | 2    | ns   |

| tF           | Output Fall Time, 2V to 0.8V                                                   | l    | 2    | ns   |

#### NOTES:

- 1. Skew parameters are guaranteed across temperature range, but not tested.

- 2. tsk(T) only applies to devices of the same transition, part type, temperature, power supply voltage, loading, and package.

- 3. The propagation delay range indicated by Min. and Max. specifications results from process and environmental variables. These propagation delays do not imply limit skew.

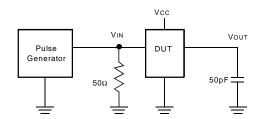

# **TEST CIRCUITS AND WAVEFORMS**

Pulse generator for all pulses:  $f \le 1.0 MHz$ ;  $tF \le 2.5 ns$ ;  $tR \le 2.5 ns$

## **PROPAGATION DELAY**

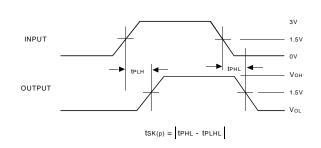

## PULSE SKEW — tsk(P)

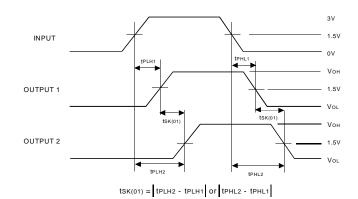

### OUTPUT SKEW — tsk(01)

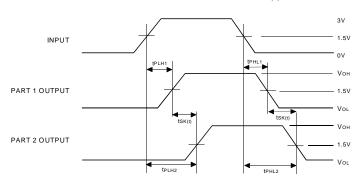

## PART-TO-PART SKEW — tsk(T)

tSK(t) = tPLH2 - tPLH1 or tPHL2 - tPHL1

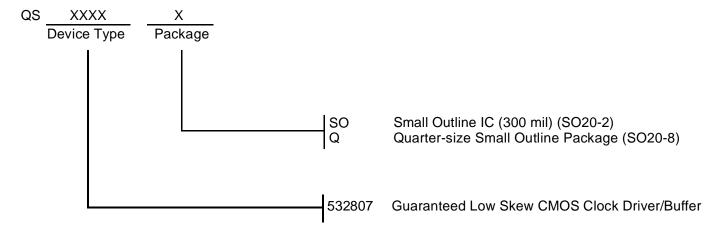

## ORDERING INFORMATION

CORPORATE HEADQUARTERS 2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*