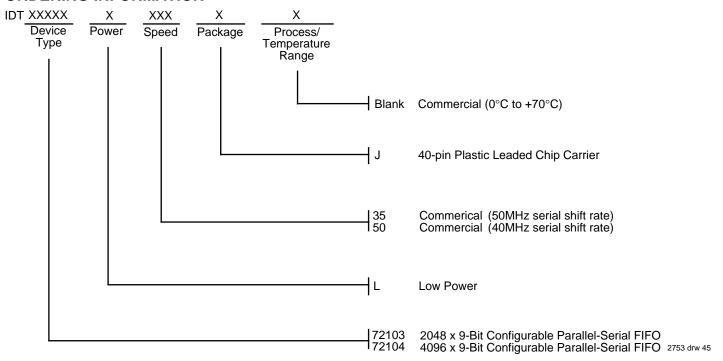

# CMOS PARALLEL-SERIAL FIFO 2048 x 9, 4096 x 9

IDT72103 IDT72104

### **FEATURES:**

- 35ns parallel port access time, 45ns cycle time

- 50MHz serial input/output frequency

- Serial-to-parallel, parallel-to-serial, serial-to-serial, and parallel-to-parallel operations

- Expandable in both depth and width with no external components

- Flexishift<sup>™</sup> Sets programmable serial word width from 4 bits to any width with no external components

- Multiple flags: Full, Almost-Full (Full-1/8), Full-Minus-One, Empty, Almost-Empty (Empty + 1/8), Empty-Plus One, and Half-Full

- Asynchronous and simultaneous read or write operations

- Dual-Port, zero fall-through time architecture

- · Retransmit capability in single-device mode

- Packaged in 44-pin PLCC

- Industrial temperature range (-40°C to +85°C) is available, tested to military electrical specifications

#### **APPLICATIONS:**

- High-speed data acquisition systems

- · Local area network (LAN) buffer

- · High-speed modem data buffer

- Remote telemetry data buffer

- FAX raster video data buffer

- Laser printer engine data buffer

- High-speed parallel bus-to-bus communications

- · Magnetic media controllers

- Serial link buffer

### **DESCRIPTION:**

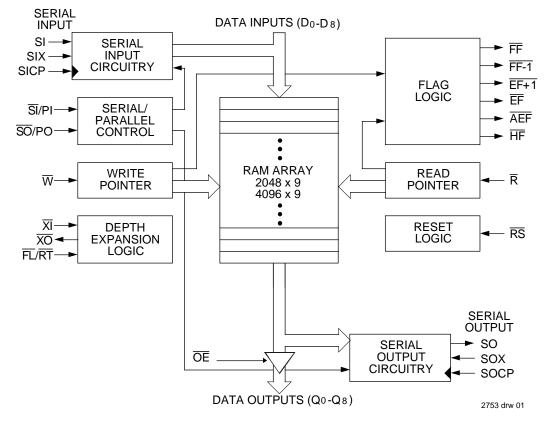

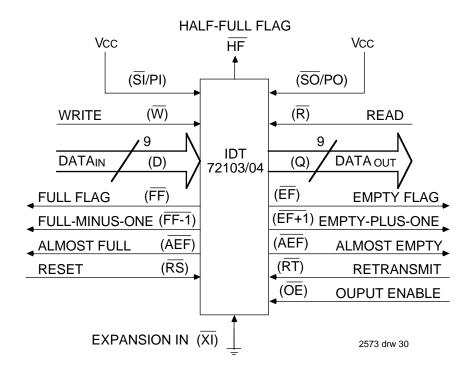

The IDT72103/72104 are high-speed Parallel-Serial FIFOs to be used with high-performance systems for functions such as serial communications, laser printer engine control and local area networks.

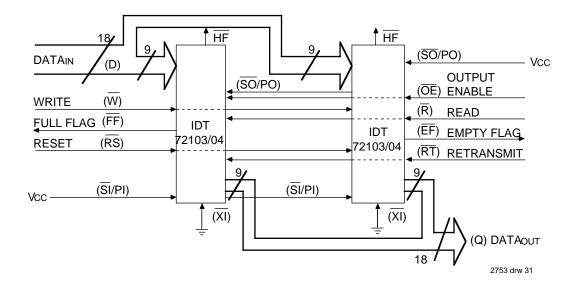

A serial input, a serial output and two 9-bit parallel ports make four modes of data transfer possible: serial-to-parallel, parallel-to-serial, serial-to-serial, and parallel-to-parallel. The IDT72103/72104 are expandable in both depth and width for all of these operational configurations.

### **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology,Inc.

### **DESCRIPTION (CONTINUED)**

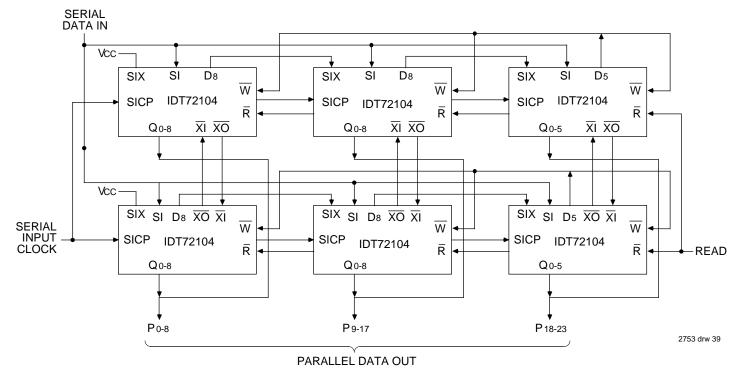

The IDT72103/72104 may be configured to handle serial word widths of four or greater using IDT's unique Flexishift feature. Flexishift allows serial width and depth expansion without external components. For example, you may configure a 4K x 24 FIFO using three IDT72104s in a serial width expansion configuration.

Seven flags are provided to signal memory status of the FIFO. The flags are  $\overline{FF}$  (Full),  $\overline{AF}$  (7/8 full),  $\overline{FF}$ –1 (Full-minusone),  $\overline{EF}$  (Empty),  $\overline{AE}$  (1/8 full),  $\overline{EF}$ +1 (Empty-plus-one), and  $\overline{HF}$  (Half-full).

Read  $(\overline{R})$  and Write  $(\overline{W})$  control pins are provided for asynchronous and simultaneous operations. An output enable  $(\overline{OE})$  control pin is available on the parallel output port for high-impedance control. The depth expansion control pins  $\overline{XO}$  and  $\overline{XI}$  are provided to allow cascading for deeper FIFOs.

The IDT72103/72104 are manufactured using IDT's CMOS technology.

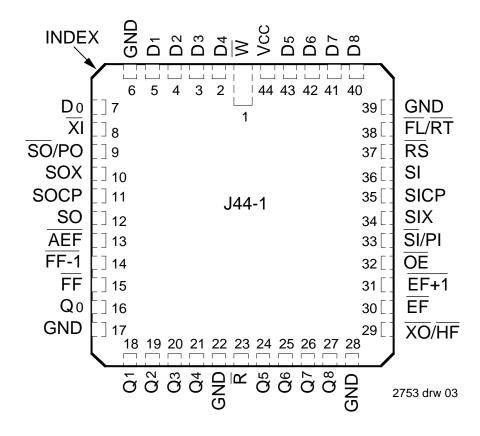

### PIN CONFIGURATIONS

PLCC TOP VIEW

### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol            | Rating                               | Commercial   | Unit        |

|-------------------|--------------------------------------|--------------|-------------|

| $V_{\text{TERM}}$ | Terminal Voltage with Respect to GND | -0.5 to +7.0 | V           |

| T <sub>A</sub>    | Operating Temperature                | 0 to +70     | °C          |

| T <sub>BIAS</sub> | Temperature Under Bias               | -55 to +125  | °C          |

| T <sub>STG</sub>  | Storage Temperature                  | -55 to +125  | °C          |

| I <sub>OUT</sub>  | DC Output Current                    | 50           | mA          |

|                   |                                      |              | 2753 tbl 01 |

### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **CAPACITANCE** (TA = $+25^{\circ}$ C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 10   | pF   |

| Соит   | Output Capacitance       | Vout = 0V  | 12   | pF   |

NOTE:

2753 tbl 02

1. This parameter is sampled and not 100% tested.

### RECOMMENDED DC OPERATING CONDITIONS

| Symbol                         | Parameter                        | Min. | Тур. | Max. | Unit     |

|--------------------------------|----------------------------------|------|------|------|----------|

| V <sub>ccc</sub>               | Commercial Supply<br>Voltage     | 4.5  | 5.0  | 5.5  | <b>V</b> |

| GND                            | Supply Voltage                   | 0    | 0    | 0    | >        |

| V <sub>IH</sub>                | Input High Voltage<br>Commercial | 2.0  | _    | _    | V        |

| V <sub>IL</sub> <sup>(1)</sup> | Input Low Voltage                | _    | _    | 0.8  | V        |

NOTE:

2753 tbl 03

### PIN DESCRIPTION

| Symbol | Name                                                 | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Do-D8  | Data Inputs<br>Serial Input Word<br>Width Select     | I/O | In a parallel input configuration – data inputs for 9-bit wide data. In a serial input configuration – one of the nine output pins is used to select the serial input word width.                                                                                                                                                                                                                                                                                                                         |

| RS     | Reset                                                | 1   | When $\overline{RS}$ is set low, internal READ and WRITE pointers are set to the first location of the RAM array. $\overline{EF}$ , $\overline{EF+1}$ , $\overline{AEF}$ are all LOW after a reset, while $\overline{FF}$ , $\overline{FF-1}$ , $\overline{HF}$ are HIGH after a reset.                                                                                                                                                                                                                   |

| W      | Write                                                | I   | A parallel word write cycle is initiated on the falling edge of $\overline{W}$ if the $\overline{FF}$ is high. When the FIFO is full, FF will go low inhibiting further write operations to prevent data overflow. In a serial input configuration, data bits are clocked into the input shift register and the write pointer does not advance until a full parallel word is assembled. One of the pins, Di, is connected to $\overline{W}$ and advances the write pointer every i-th serial input clock. |

| R      | Read                                                 | I   | A read cycle is initiated on the falling edge of $\overline{R}$ if the $\overline{EF}$ is HIGH. After all the data from the FIFO has been read $\overline{EF}$ will go LOW inhibiting further read operations. In a serial output configuration, a data word is read from memory into the output shift register. One of the pins, Qj, is connected to $\overline{R}$ and advances the read pointer every j-th serial output clock.                                                                        |

| FL/RT  | First Load/<br>Retransmit                            | I   | This is a dual-purpose pin. In multiple-device mode, $\overline{FL}/\overline{RT}$ is grounded to indicate the first device loaded. In single-device mode, $\overline{FL}/\overline{RT}$ acts as the retransmit input. Single-device mode is initiated by grounding the $\overline{XI}$ pin.                                                                                                                                                                                                              |

| XI     | Expansion In                                         | I   | In single-device mode, $\overline{XI}$ is grounded. In depth expansion or daisy chain mode, $\overline{XI}$ is connected to the $\overline{XO}$ pin of the previous device.                                                                                                                                                                                                                                                                                                                               |

| ŌĒ     | Output Enable                                        | I   | When $\overline{OE}$ is LOW, both parallel and serial outputs are enabled. When $\overline{OE}$ is HIGH, the parallel output buffers are placed in a high-impedance state.                                                                                                                                                                                                                                                                                                                                |

| Q0-Q8  | Data Outputs /<br>Serial Output<br>Word Width Select | 0   | In a parallel output configuration - data outputs for 9-bit wide data. In a serial output configuration - one of nine output pins used to select the serial output word width.                                                                                                                                                                                                                                                                                                                            |

| FF     | Full Flag                                            | 0   | FF is asserted LOW when the FIFO is full and further write operations are inhibited. When the FF is HIGH, the FIFO is not full and data can be written into the FIFO.                                                                                                                                                                                                                                                                                                                                     |

| FF-1   | Full-1 Flag                                          | 0   | FF-1 goes LOW when the FIFO memory array is one word away from being full. It will remain LOW when every memory location is filled.                                                                                                                                                                                                                                                                                                                                                                       |

2753 tbl 04

<sup>1. 1.5</sup>V undershoots are allowed for 10ns once per cycle.

### **PIN DESCRIPTION (Continued)**

| Symbol | Name                              | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XO/HF  | Expansion Out/<br>Half-Full Flag  | 0   | $\overline{HF}$ is LOW when the FIFO is more than half-full in the single device or width expansion modes. The $\overline{HF}$ will remain LOW until the difference between the write and read pointers is less than or equal to one-half of the FIFO memory. In depth expansion mode, a pulse is written from $\overline{XO}$ to $\overline{XI}$ of the next device when the last location in the FIFO is filled. Another pulse is sent from $\overline{XO}$ to $\overline{XI}$ of the next device when the last FIFO location is read. |

| ĀĒF    | Almost-Empty/<br>Almost-Full Flag | 0   | When $\overline{AEF}$ is LOW, the FIFO is empty to 1/8 full or 7/8 full to completely full. If $\overline{AEF}$ is HIGH, then the FIFO is greater than 1/8 full, but less than 7/8 full.                                                                                                                                                                                                                                                                                                                                                 |

| EF+1   | Empty+1 Flag                      | 0   | EF+ 1 is LOW when there is zero or one word word in the FIFO memory array.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ĒĒ     | Empty Flag                        | 0   | EF goes LOW when the FIFO is empty and further read operations are inhibited. FF is HIGH when the FIFO is not empty and data reads are permitted.                                                                                                                                                                                                                                                                                                                                                                                        |

| SI     | Serial Input                      | I   | Data input for serial data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SO     | Serial Output                     | 0   | Data output for serial data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SICP   | Serial Input Clock                | I   | This pin is the serial input clock. On the rising edge of the SICP signal, new serial data bits are read into the serial input shift register.                                                                                                                                                                                                                                                                                                                                                                                           |

| SOCP   | Serial Output<br>Clock            | Ι   | This pin is the serial output clock. On the rising edge of the SOCP signal, new serial data bits are read from the serial output shift register.                                                                                                                                                                                                                                                                                                                                                                                         |

| SIX    | Serial Input<br>Expansion         | _   | SIX controls the serial input expansion for word widths greater than 9 bits. In a serial input configuration, the SIX pin of the least significant device is tied HIGH. The SIX pin of all other devices is connected to the D <sub>8</sub> pin of the previous device. In parallel input configurations or serial input configurations of 9 bits or less, SIX is tied HIGH.                                                                                                                                                             |

| SOX    | Serial Output<br>Expansion        | I   | SOX controls the serial output expansion for word widths greater than 9 bits. In a serial output configuration, the SOX pin of the least significant device is tied HIGH. The SOX pin of all other devices is connected to the Q8 pin of the previous device. In parallel output configurations or serial output configurations of 9 bits or less, SOX is tied HIGH.                                                                                                                                                                     |

| SI/PI  | Serial/Parallel Input             | I   | When this pin is HIGH, the FIFO is in a parallel input configuration and accepts input data through $D_0$ - $D_8$ . When $\overline{SI}/PI$ is LOW, the FIFO is in a serial input configuration and data is input through SI.                                                                                                                                                                                                                                                                                                            |

| SO/PO  | Serial/Parallel Output            | I   | When this pin is HIGH, the FIFO is in a parallel output configuration and sends output data through Q <sub>0</sub> -Q <sub>8</sub> . When <del>SO</del> /PO is LOW the FIFO is in a serial output configuration and data is input through SO.                                                                                                                                                                                                                                                                                            |

| GND    | Ground                            |     | One ground pin for the DIP package and five ground pins for the LCC/PLCC packages.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Vcc    | Power                             |     | One + 5V power pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

2753 tbl 05

### DC ELECTRICAL CHARACTERISTICS

(Commercial:  $V_{CC} = 5.0V \pm 10\%$ ,  $T_A = 0$ °C to +70°C)

|                                       |                                                                                                                               | IDT72103/72104<br>Commercial<br>tA = 35, 50ns |      |      |      |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|------|------|

| Symbol                                | Parameter                                                                                                                     | Min.                                          | Тур. | Max. | Unit |

| I <sub>IL</sub> <sup>(1)</sup>        | Input Leakage Current<br>(Any Input)                                                                                          | <b>–</b> 1                                    | _    | 1    | μА   |

| I <sub>OL</sub> (2)                   | Output Leakage Current                                                                                                        | -10                                           | _    | 10   | μΑ   |

| V <sub>OH</sub>                       | Output Logic "1" Voltage, I <sub>OUT</sub> = -2mA <sup>(4)</sup>                                                              | 2.4                                           | _    | _    | V    |

| V <sub>OL</sub>                       | Output Logic "0" Voltage, I <sub>OUT</sub> = 8mA <sup>(5)</sup>                                                               | _                                             | _    | 0.4  | V    |

| I <sub>CC1</sub> (3)                  | Average V <sub>cc</sub> Power Supply Current                                                                                  |                                               | 90   | 140  | mA   |

| I <sub>CC2</sub> (3)                  | Average Standby Current $(\overline{R} = \overline{W} = \overline{RS} = \overline{FL/RT} = V_{IH})$ (SOCP = SICP = $V_{IL}$ ) | _                                             | 8    | 12   | mA   |

| I <sub>CC3</sub> (L) <sup>(3,6)</sup> | Power Down Current                                                                                                            | _                                             | _    | 2    | mA   |

NOTES: 2753 tbl 06

- NOTES:

1. Measurements with  $0.4 \le V_{IN} \le V_{CC}$ .

2.  $\overline{R} \ge V_{IH}$ , SOCP  $\le$  VIL,  $0.4 \le V_{OUT} \le V_{CC}$ .

3.  $I_{CC}$  measurements are made with outputs open.

4. For SO,  $I_{OUT} = -8mA$ .

5. For SO,  $I_{OUT} = 16mA$ .

6. SOCP = SICP  $\le$  0.2V; other Inputs =  $V_{CC}$  -0.2V.

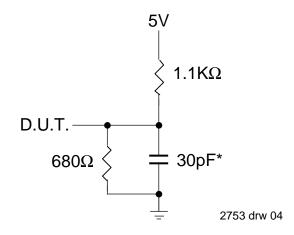

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 3ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 1 |

2753 tbl 07

or equivalent circuit

Figure 1. Ouput Load

\*Including jig and scope capacitances

### **AC ELECTRICAL CHARACTERISTICS**

(Commercial:  $VCC = 5.0V \pm 10\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ )

|         |                                                                                      |              | Comm             |          |                                                  |         |               |

|---------|--------------------------------------------------------------------------------------|--------------|------------------|----------|--------------------------------------------------|---------|---------------|

|         |                                                                                      |              | 103L35<br>104L35 |          | 103L50<br>104L50                                 |         | Tii           |

| Symbol  | Parameter                                                                            | Min.         | Max.             | Min.     | Max.                                             | Unit    | Timing Figure |

| fs      | Parallel Shift Frequency                                                             |              | 22.2             |          | 15                                               | MHz     | i igui e      |

| fSOCP   | Serial-Out Shift Frequency                                                           |              | 50               |          | 40                                               | MHz     | _             |

| fSICP   | Serial-In Shift Frequency                                                            | + =          | 50               | <u> </u> | 40                                               | MHz     | <u> </u>      |

| l       | EL-OUTPUT MODE TIMINGS                                                               |              | 30               |          | 40                                               | IVII IZ |               |

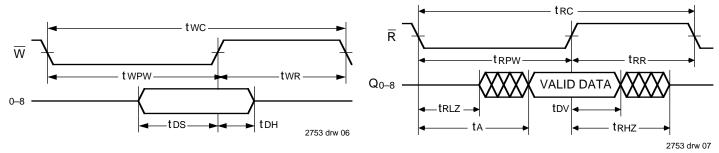

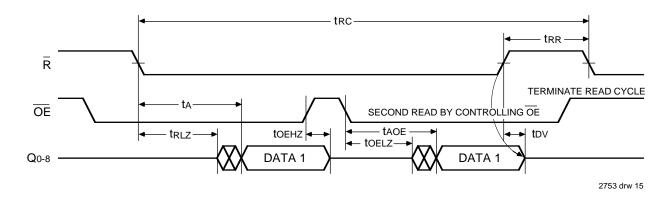

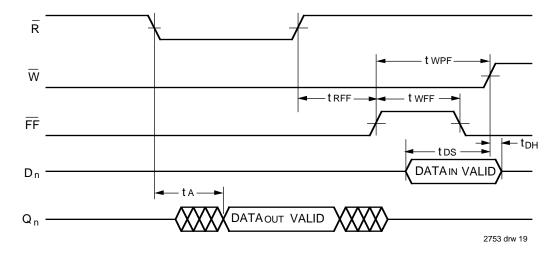

| tA      | Access Time                                                                          |              | 35               | T        | 50                                               | ns      | 4             |

| trr     | Read Recovery Time                                                                   | 10           |                  | 15       |                                                  | ns      | 4             |

| trpw    | Read Pulse Width                                                                     | 35           |                  | 50       |                                                  | ns      | 4             |

| trc     | Read Cycle Time                                                                      | 45           | + =              | 65       |                                                  | ns      | 4             |

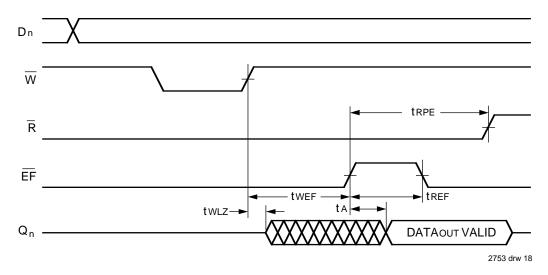

| twLz    | Write Pulse LOW to Data Bus at Low-Z <sup>(1)</sup>                                  | 5            |                  | 15       |                                                  |         | 15            |

|         | Read Pulse LOW to Data Bus at Low-Z <sup>(1)</sup>                                   | 5            | _                | 10       |                                                  | ns      | 4             |

| tRLZ    |                                                                                      | 5            |                  | 10       |                                                  | ns      | 4             |

| tRHZ    | Read Pulse HIGH to Data Bus at High-Z <sup>(1)</sup> Data Valid from Read Pulse HIGH | <del>-</del> | 20               | _        | 30                                               | ns      |               |

| tDV     |                                                                                      | 5            | _                | 5        |                                                  | ns      | 4             |

|         | EL-INPUT MODE TIMINGS                                                                | 10           |                  | 1 00     | <del>                                     </del> |         | 1 2           |

| tDS     | Data Set-up Time  Data Hold Time                                                     | 18           |                  | 20       |                                                  | ns      | 3             |

| tDH     |                                                                                      | 0            | _                | 0        | _                                                | ns      | 3             |

| twc     | Write Cycle Time                                                                     | 45           | _                | 50       | _                                                | ns      | 3             |

| twpw    | Write Pulse Width                                                                    | 35           | _                | 40       | _                                                | ns      | 3             |

| twr     | Write Recovery Time                                                                  | 10           | _                | 10       | _                                                | ns      | 3             |

| RESET I |                                                                                      | <del></del>  | ı                | T        |                                                  |         | 1             |

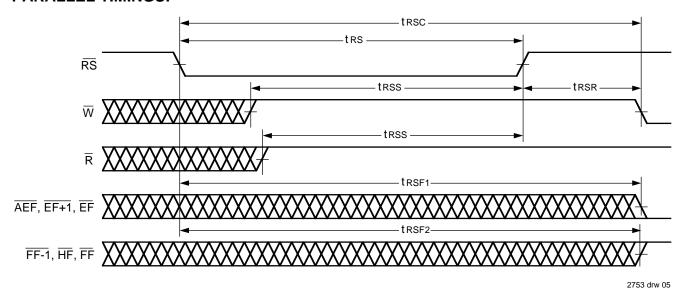

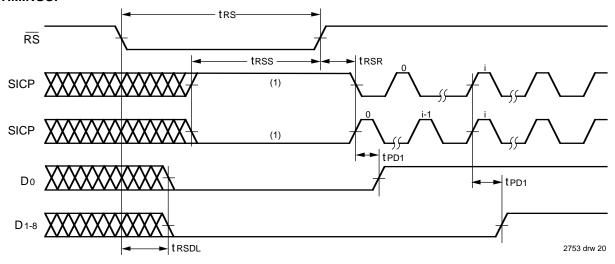

| trsc    | Reset Cycle Time                                                                     | 45           | _                | 50       | _                                                | ns      | 2,18          |

| trs     | Reset Pulse Width                                                                    | 35           | _                | 40       | _                                                | ns      | 2,18          |

| trss    | Reset Set-up Time                                                                    | 35           | _                | 40       | _                                                | ns      | 2,18          |

| trsr    | Reset Recovery Time                                                                  | 10           | _                | 10       | _                                                | ns      | 2,17,18       |

|         | TO FLAG TIMINGS                                                                      |              |                  | 1        |                                                  |         | 1             |

| tRSF1   | Reset to EF, AEF, and EF+1 LOW                                                       |              | 45               | _        | 65                                               | ns      | 2             |

| tRSF2   | Reset to HF, FF, and FF-1 LOW                                                        |              | 45               | _        | 65                                               | ns      | 2             |

| RESET T | O OUTPUT TIMINGS – SERIAL MODE ONLY                                                  |              |                  | Г        |                                                  | Ī       | 1             |

| trsql   | Reset Going LOW to Q <sub>0-8</sub> LOW                                              | 20           | _                | 20       | _                                                | ns      | 18            |

| trsqh   | Reset Going HIGH to Q <sub>0-8</sub> HIGH                                            | 20           |                  | 20       | _                                                | ns      | 18            |

| trsdl   | Reset Going LOW to D <sub>0-8</sub> LOW                                              | 20           | _                | 20       | _                                                | ns      | 17            |

| RETRAN  | ISMIT TIMINGS                                                                        |              |                  |          |                                                  |         |               |

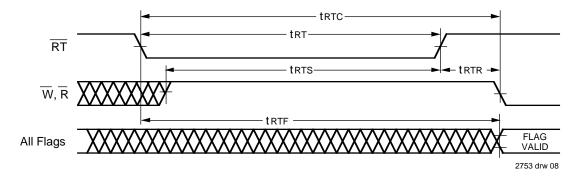

| trtc    | Retransmit Cycle Time                                                                | 45           | _                | 50       | _                                                | ns      | 5             |

| trt     | Retransmit Pulse Width                                                               | 35           | _                | 40       |                                                  | ns      | 5             |

| trts    | Retransmit Set-up Time                                                               | 35           | _                | 40       | _                                                | ns      | 5             |

| trtr    | Retransmit Recovery Time                                                             | 10           | _                | 10       | _                                                | ns      | 5             |

| trtf    | Retransmit to Flags                                                                  |              | 35               | _        | 50                                               | ns      | 5             |

| PARALL  | EL MODE FLAG TIMINGS                                                                 |              |                  |          |                                                  |         |               |

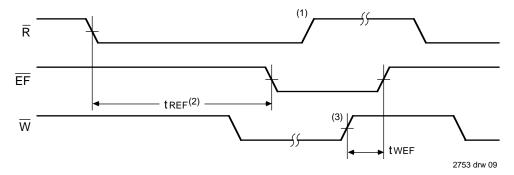

| tref    | Read LOW to EF LOW                                                                   | _            | 30               | _        | 45                                               | ns      | 6             |

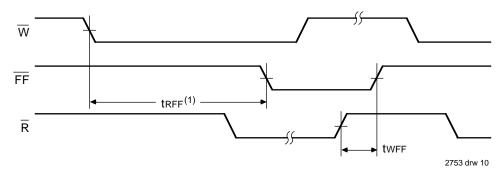

| trff    | Read HIGH to FF HIGH                                                                 |              | 30               |          | 45                                               | ns      | 7             |

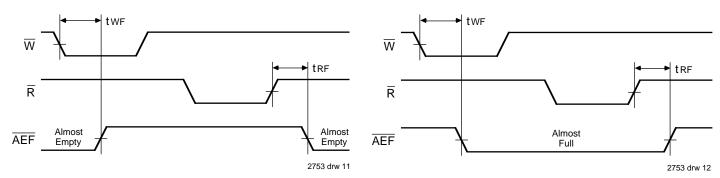

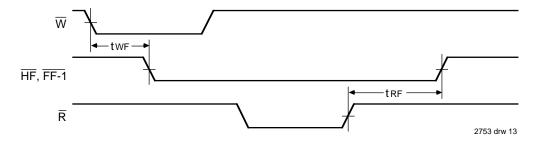

| trf     | Read HIGH to Transitioning HF, AEF and FF-1                                          |              | 45               | _        | 65                                               | ns      | 8,9,10        |

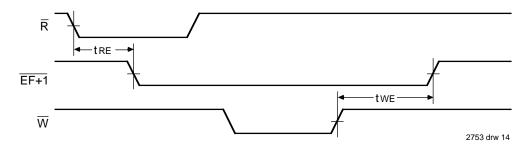

| tre     | Read LOW to EF+1 LOW                                                                 |              | 45               | _        | 65                                               | ns      | 11            |

| trpe    | Read Pulse Width after EF HIGH                                                       | 35           |                  | 40       |                                                  | ns      | 15            |

| tweF    | Write HIGH to EF HIGH                                                                | _            | 30               | _        | 45                                               | ns      | 6             |

| twff    | Write LOW to FF LOW                                                                  | _            | 30               | _        | 45                                               | ns      | 7             |

| twF     | Write LOW to Transitioning HF, AEF and FF-1                                          | _            | 45               | _        | 65                                               | ns      | 8,9,10        |

| twE     | Write HIGH to EF+1 HIGH                                                              | <u> </u>     | 45               | _        | 65                                               | ns      | 11            |

|         |                                                                                      | 1            | 1                |          |                                                  |         |               |

1. Values guaranteed by design, not tested.

### **AC ELECTRICAL CHARACTERISTICS**

(Commercial:  $V_{CC} = 5.0V \pm 10\%$ ,  $T_A = 0$ °C to +70°C)

|               |                                                   |      | Comm                       |      |          | Timing |                  |

|---------------|---------------------------------------------------|------|----------------------------|------|----------|--------|------------------|

|               |                                                   |      | IDT72103L35<br>IDT72104L35 |      |          |        | 103L50<br>104L50 |

| Symbol        | Parameter                                         | Min. | Max.                       | Min. | Max.     | Unit   | Figure           |

| DEPTH         | EXPANSION MODE TIMINGS                            |      | ı                          | u .  |          |        | •                |

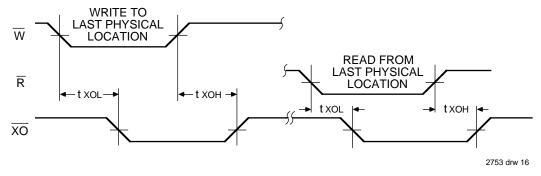

| txoL          | Read/Write to XO LOW                              | _    | 35                         | _    | 50       | ns     | 13               |

| tхон          | Read/Write to XO HIGH                             | _    | 35                         | _    | 50       | ns     | 13               |

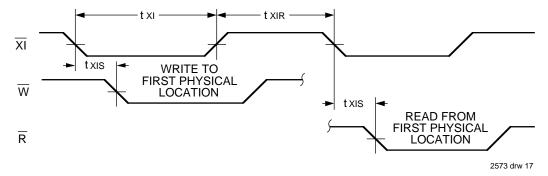

| txı           | XI Pulse Width                                    | 35   | _                          | 50   | <u> </u> | ns     | 14               |

| txir          | XI Recovery Time                                  | 10   | _                          | 10   | _        | ns     | 14               |

| txis          | XI Set-up Time                                    | 15   | _                          | 15   |          | ns     | 14               |

| SERIAL-       | INPUT MODE TIMINGS                                |      |                            | •    |          |        | •                |

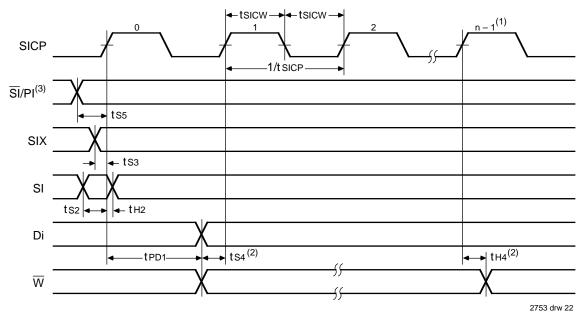

| ts2           | Serial Data In Set-up Time to SICP Rising Edge    | 12   | _                          | 15   | _        | ns     | 19               |

| tH2           | Serial Data In Hold Time to SICP Rising Edge      | 0    | _                          | 0    | _        | ns     | 19               |

| ts3           | SIX Set-up Time to SICP Rising Edge               | 5    | -                          | 5    | _        | ns     | 19               |

| ts4           | W Set-up Time to SICP Rising Edge                 | 5    | _                          | 5    | _        | ns     | 19               |

| tH4           | W Hold Time to SICP Rising Edge                   | 7    | _                          | 7    | _        | ns     | 19               |

| tsicw         | Serial In Clock Width High/Low                    | 8    | _                          | 10   | _        | ns     | 19               |

| tS5           | SI/PI Set-up Time to SICP Rising Edge             | 35   |                            | 50   | l —      | ns     | 19               |

| SERIAL-       | OUTPUT MODE TIMINGS                               |      |                            | 1    | 1        |        |                  |

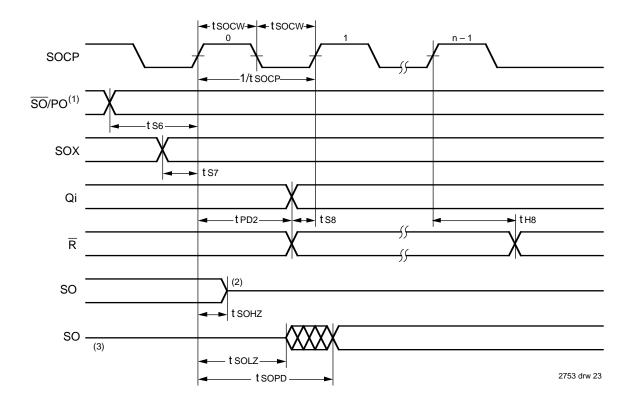

| ts6           | SO/PO Set-up Time to SOCP Rising Edge             | 35   | _                          | 50   | _        | ns     | 20               |

| ts7           | SOX Set-up Time to SOCP Rising Edge               | 5    | _                          | 5    |          | ns     | 20               |

| ts8           | R Set-up Time to SOCP Rising Edge                 | 5    | _                          | 5    | _        | ns     | 20               |

| tH8           | R Hold Time to SOCP Rising Edge                   | 7    | _                          | 7    | _        | ns     | 20               |

| tsocw         | Serial Out Clock Width HIGH/LOW                   | 8    | _                          | 10   | _        | ns     | 20               |

| SERIAL        | MODE RECOVERY TIMINGS                             |      |                            | u .  |          |        |                  |

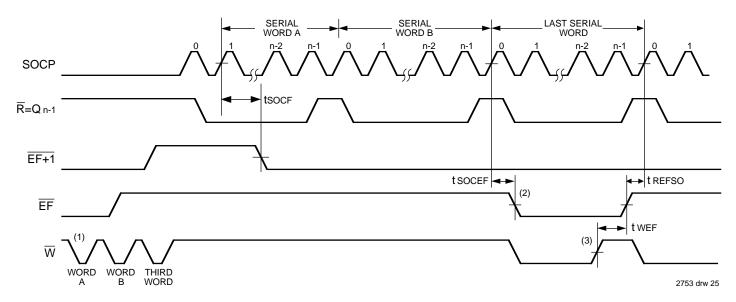

| trefso        | Recovery Time SOCP after EF Goes HIGH             | 35   | _                          | 80   | _        | ns     | 22               |

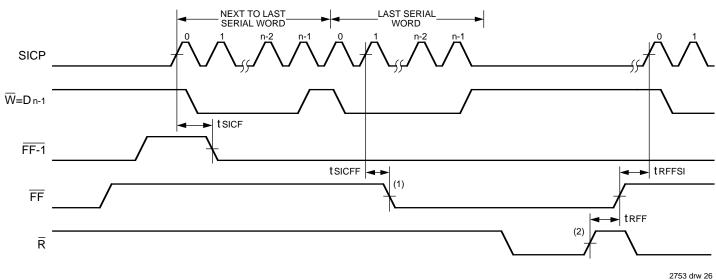

| trffsi        | Recovery Time SICP after FF Goes HIGH             | 15   | _                          | 15   | _        | ns     | 23               |

| SERIAL        | MODE FLAG TIMINGS                                 |      | ı                          | I.   |          |        |                  |

| tsocef        | SOCP Rising Edge (Bit 0- Last Word) to EF LOW     | _    | 20                         | _    | 25       | ns     | 22               |

| tsocff        | SOCP Rising Edge (Bit 0- First Word) to FF HIGH   | _    | 30                         | _    | 40       | ns     | 24               |

| tsocf         | SOCP Rising Edge to FF-1, HF, AEF HIGH            | _    | 30                         | _    | 40       | ns     | 24,26            |

| tsocf         | SOCP Rising Edge to AEF, EF, EF+1 LOW             | _    | 30                         | _    | 40       | ns     | 22,26            |

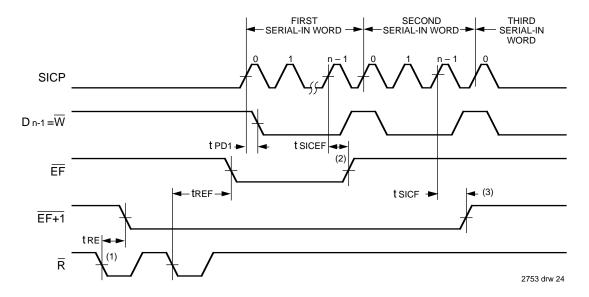

| tsicef        | SICP Rising Edge (Last Bit-First Word) to EF HIGH | _    | 45                         | _    | 65       | ns     | 21               |

| tsicff        | SICP Rising Edge (Bit 1-Last Word) to FF LOW      | _    | 30                         | _    | 40       | ns     | 23               |

| tsicf         | SICP Rising Edge to EF+1, AEF HIGH                | _    | 45                         | _    | 65       | ns     | 21,25            |

| tsicf         | SICP Rising Edge to FF-1, HF, AEF HIGH            | _    | 45                         | _    | 65       | ns     | 23,25            |

| SERIAL-       | INPUT MODE TIMINGS                                |      |                            | ı    |          |        |                  |

| tPD1          | SICP Rising Edge to D <sup>(1)</sup>              | 5    | 17                         | 5    | 20       | ns     | 17,19            |

| SERIAL-       | OUTPUT MODE TIMINGS                               |      |                            | ı    | 1        |        |                  |

| tPD2          | SOCP Rising Edge to Q <sup>(1)</sup>              | 5    | 17                         | 5    | 20       | ns     | 20               |

| tsohz         | SOCP Rising Edge to SO at High-Z <sup>(1)</sup>   | 5    | 16                         | 5    | 16       | ns     | 20               |

| tsolz         | SOCP Rising Edge to SO at Low-Z <sup>(1)</sup>    | 5    | 22                         | 5    | 22       | ns     | 20               |

| tsopd         | SOCP Rising Edge to Valid Data on SO              |      | 18                         | _    | 18       | ns     | 20               |

|               | Γ ENABLE/DISABLE TIMINGS                          | I    | 1                          | 1    | 1        |        | 1                |

| toehz         | Output Enable to High-Z (Disable)(1)              | _    | 16                         | _    | 16       | ns     | 12               |

|               | . ,                                               | 5    | <u> </u>                   | 5    |          | nc     | 12               |

| <b>t</b> OELZ | Output Enable to Low-Z (Enable)(1)                | 3    | _                          | 5    |          | ns     | 12               |

NOTE

2753 tbl 09

1. Values guaranteed by design, not tested.

### **GENERAL SIGNAL DESCRIPTION**

#### INPUTS:

### Data Inputs (Do-D8)

The parallel-in mode is selected by connecting the  $\overline{SI}/PI$  pin to Vcc. Do-D8 are the data input lines.

The serial-input mode is selected by grounding the SI/PI pin. The D0-D8 lines are control output pins used to program the serial word width.

### Reset (RS)

Reset is accomplished whenever the  $\overline{\text{RS}}$  input is taken to a low state. Both internal read and write pointers are set to the first location during reset. A reset is required after power up before a write operation can take place. Both Read  $(\overline{\text{R}})$  and Write  $(\overline{\text{W}})$  inputs must be HIGH during reset.

### Write $(\overline{\mathbb{W}})$

A write cycle is initiated on the falling edge of  $\overline{W}$  provided the Full Flag ( $\overline{FF}$ ) is not asserted. Data set-up and hold times must be met with respect to the rising edge of  $\overline{W}$ . Data is stored in the RAM array sequentially and independently of any on going read operation.

When the FIFO is full, the FF will go LOW inhibiting further write operations to prevent data overflow. After a valid read operation is completed, the FF will go HIGH after tRFF allowing a valid write to begin.

### Read ( $\overline{R}$ )

A read cycle is initiated on the falling edge of  $\overline{R}$ , provided the  $\overline{EF}$  is not set. Data is accessed on a first-in/first out basis independent of any on going write operations. After  $\overline{R}$  goes HIGH, the Data Outputs (Q0-Q8) go to a high-impedance condition until the next read operation. When all the data has been read from the FIFO, the  $\overline{EF}$  will go LOW, and Q0-Q8 will go to a high-impedance state inhibiting further read operations. After the completion of a valid write operation, the  $\overline{EF}$  will go HIGH after twef allowing a valid read to begin.

### First Load/Retransmit (FL/RT)

In the depth-expansion mode, the  $\overline{FL}/\overline{RT}$  pin is grounded to indicate that it is the first device loaded. In the single-device mode, the  $\overline{FL}/\overline{RT}$  pin acts as the retransmit input. The single-device mode is initiated by grounding the Expansion-In  $(\overline{XI})$  pin.

The IDT72103/72104 can be made to retransmit data when the  $\overline{RT}$  input is pulsed LOW. A retransmit operation will set the internal read pointer to the first location and will not affect the write pointer. During retransmit,  $\overline{R}$  and  $\overline{W}$  must be set HIGH and the  $\overline{FF}$  will be affected depending on the relative locations of the read and write pointers. This feature is useful when less than 2048/4096 writes are performed between resets. The retransmit feature is not available in the depth expansion mode.

### Expansion In $(\overline{XI})$

The  $\overline{\text{XI}}$  pin is grounded to indicate an operation in the the single-device mode. In the depth expansion or daisy-chain mode, the  $\overline{\text{XI}}$  pin is connected to the  $\overline{\text{XO}}$  pin of the previous device.

### Output Enable (OE)

When  $\overline{OE}$  is HIGH, the parallel output buffers are tristated. When  $\overline{OE}$  is LOW, both parallel and serial outputs are enabled.

### Serial Input (SI)

Serial data is read into the serial input register via the SI pin. In both depth and serial width expansion modes, the serial-input signals of the different FIFOs in the expansion array are connected together.

### Serial Input Clock (SICP)

Serial data is read into the serial input register on the rising edge of the SICP signal. In both depth and serial width expansion modes, the SICP signals of the different FIFOs in the expansion array are connected together.

### Serial Output Clock (SOCP)

New serial data bits are read from the serial output register on the rising edge of the SOCP signal. In both depth and serial width expansion modes, the SOCP signals of the different FIFOs in the expansion array are connected together.

### Serial Input Expansion (SIX)

The SIX pin is tied HIGH for single-device serial or parallel input operation. In a serial input configuration, the SIX pin of the least significant device is tied HIGH. The SIX pin of all other devices is connected to the D<sub>8</sub> pin of the previous device.

### **Serial Output Expansion (SOX)**

The SOX pin is tied HIGH for single-device serial or parallel output operation. In a serial output configuration, the SOX pin of the least significant device is tied HIGH. The SOX pin of all other devices is connected to the Q8 pin of the previous device.

### Serial/Parallel Input (SI/PI)

The  $\overline{SI}/PI$  pin programs whether the IDT72103/72104 accepts parallel or serial data as input. When this pin is LOW, the FIFO expects serial data and the Do-D8 pins become output pins used to program the write signal and the serial input word width. For instance, connecting D8 to  $\overline{W}$  will program a serial word width of 9 bits; connecting D7 to  $\overline{W}$  will program a serial word width of 8 bits and so on.

### Serial/Parallel Output (SO/PO)

The  $\overline{SO}/PO$  pin programs whether the IDT72103/72104 outputs parallel or serial data. When this pin is LOW, the FIFO expects serial data and the Q0-Q8 pins output signals used to program the read signal and the serial output word width.

### **OUTPUTS:**

### Data Outputs (Q0-Q8)

Data outputs for 9-bit wide data. These output lines are in a high-impedance condition whenever  $\overline{R}$  is in a high state. The serial output mode is selected by grounding the  $\overline{SO}/PO$  pin. The Qo-Q8 lines are control pins used to program the serial word width.

### Serial Output (SO)

Serial data is output on the SO pin. In both depth and serial width expansion modes the serial output signals of the different FIFOs in the expansion array are connected together. Following reset, SO is tristated until the first rising edge of the Serial Out Clock (SOCP) signal. Data is clocked out least significant bit first. In the serial width expansion mode, SO is tristated again after the ninth bit is output.

### Full Flag (FF)

FF is asserted LOW when the FIFO is full. When the FIFO is full, the internal write pointer will not be incremented by any additional write pulses.

### Full Flag — Serial In Mode

When the FIFO is loaded serially, the Serial In Clock (SICP) asserts the  $\overline{\text{FF}}$ . On the second rising edge of the SICP for the last word in the FIFO, the  $\overline{\text{FF}}$  will assert LOW, and it will remain asserted until the next read operation. Note that when the  $\overline{\text{FF}}$  is asserted, the last SICP for that word will have to be stretched as shown in Figure 23.

#### Full Flag — Parallel-In Mode

When the FIFO is in the Parallel-In mode, the falling edge of  $\overline{W}$  asserts the  $\overline{FF}$  (LOW). The  $\overline{FF}$  is then de-asserted (HIGH) by subsequent read operations - either serial or parallel.

### Full-Minus — One Flag (FF-1)

The FF-1 flag is asserted low when the FIFO is one word away from being full. It will remain asserted when the FIFO is full.

### Expansion Out/Half-Full Flag (XO/HF)

In the single-device mode, the  $\overline{XO/HF}$  pin operates as a  $\overline{HF}$  pin when the  $\overline{XI}$  pin is grounded. After half of the memory is filled, the  $\overline{HF}$  will be set to LOW at the falling edge of the next write operation. It will remain set until the difference between the write pointer and read pointer is less than or equal to one-half of the FIFO total memory. The  $\overline{HF}$  is then reset by the rising edge of the read operation.

In the multiple-device mode, the  $\overline{XI}$  pin is connected to the  $\overline{XO}$  pin of the previous device. The  $\overline{XO}$  pin signals a pulse to the next device when the previous device reaches the best location of memory in the daisy chain configuration.

### Almost–Empty or Almost–Full Flag (AEF)

The  $\overline{AEF}$  asserts LOW if there are 0-255 or 1793-2048 bytes in the IDT72103, 2K x 9 FIFO. The  $\overline{AEF}$  asserts LOW if there are 0-511 or 3585-4096 bytes in the IDT72104, 4K x 9 FIFO.

### Empty-Plus-One Flag (EF+1)

In the parallel-output mode, the  $\overline{EF+1}$  flag is asserted LOW when there is one word or less in the FIFO. It will remain LOW when the FIFO is empty.

In the serial-output mode, the  $\overline{EF+1}$  flag operates as an  $\overline{EF+2}$  flag. It goes LOW when the second to the last word is read from the RAM array and is ready to be shifted out.

### Empty Flag (EF) — Parallel-Out Mode

When the FIFO is in the parallel out mode and there is only one word in the FIFO, the falling edge of the  $\overline{R}$  line will cause the  $\overline{EF}$  line to be asserted LOW. This is shown in Figure 6. The  $\overline{EF}$  is then de-asserted HIGH by either the rising edge of  $\overline{W}$  or the rising edge of SICP, as shown in Figure 6.

### Empty Flag — Serial-Out Mode

The use of the  $\overline{\text{EF}}$  is important for proper serial-out operation when the FIFO is almost empty. The  $\overline{\text{EF}}$  flag is asserted LOW after the first bit of the last word is shifted out. This is shown in Figure 22.

### TABLE 1 — STATUS FLAGS

| Number of<br>Words in FIFO<br>IDT72103 IDT72104 |           | FF | FF-1 | ĀĒĒ | ĦF | (1)<br>EF+1 | ĒF |

|-------------------------------------------------|-----------|----|------|-----|----|-------------|----|

| 0                                               | 0         | Н  | Н    | L   | Н  | L           | L  |

| 1                                               | 1         | Н  | Н    | L   | Н  | L           | Н  |

| 2-255                                           | 2-511     | Н  | Н    | L   | Н  | Н           | Н  |

| 256-1024                                        | 512-2048  | Н  | Н    | Н   | Н  | Н           | Н  |

| 1025-1792                                       | 2049-3584 | Н  | Н    | Н   | L  | Н           | Н  |

| 1793-2046                                       | 3585-4094 | Н  | Н    | L   | L  | Н           | Н  |

| 2047                                            | 4095      | Н  | L    | L   | L  | Н           | Н  |

| 2048                                            | 4096      | L  | L    | L   | L  | Н           | Н  |

NOTE:

2753 tbl 10

1. EF+1 acts as EF+2 in the serial out mode.

### **PARALLEL TIMINGS:**

Figure 2. Reset

Figure 3. Write Operation in Parallel Data In Mode

Figure 4. Read Operation in Parallel Data Out Mode

Figure 5. Retransmit

- 1. Data is valid on this edge.

- 2. The Empty Flag is asserted by  $\overline{R}$  in the Parallel-Out mode and is specified by tREF. The  $\overline{EF}$  flag is deasserted by the rising edge of  $\overline{W}$ .

- 3. First rising edge of Write after EF is set.

Figure 6. Empty Flag Timings in Parallel Out Mode

### NOTE:

1. For the assertion time, twrf is used when data is written in the Parallel mode. The FF is de-asserted by the rising edge of R.

Figure 7. Full Flag Timings in Parallel-In Mode

Figure 8. Almost-Empty Flag Region

Figure 9. Almost-Full Flag Region

Figure 10. Half-Full and Full-minus-1 Flag Timings

Figure 11. Empty+1 Flag Timings

Figure 12. Output Enable Timings

Figure 13. Expansion-Out

Figure 14. Expansion-In

Figure 15. Read Data Flow-Through Mode

Figure 16. Write Data Flow-Through Mode

### **SERIAL TIMINGS:**

### NOTE:

1. SICP should be in the steady LOW or HIGH during trss. The first LOW-HIGH (or HIGH-LOW) transition can begin after trss.

Figure 17. Reset Timings for Serial-In Mode

### NOTE:

1. SOCP should be in the steady LOW or HIGH during trss. The first LOW-HIGH (or HIGH-LOW) transition can begin after trsr.

igure 18. Reset Timings for Serial-Out Mode

- 1. For the stand alone mode,  $n \ge 4$  and the input bits are numbered 0 to n-1.

- 2. For the recommended interconnections, Di is to be directly tied to  $\overline{W}$  and the ts4 and tH4 requirements will be satisfied. For users that modify  $\overline{W}$  externally, ts4 and tH4 requirements have to be met.

- 3. After SI/PI has been set up, it cannot be dynamically changed; it can only be changed after a reset operation.

Figure 19. Write Operation In Serial-In Mode

#### NOTES

- 1. After SO/PO has been set up, it cannot be dynamically changed; it can only be changed after a reset operation.

- 2. For single device: Read out the last bit after EF is asserted.

- For Serial Width Expansion mode: Read out the last bit of the current memory location from the active device.

- 3. For single device: The operation starts after Reset.

- For Serial Width Expansion mode: Read the first bit of the current memory location from the active device.

Figure 20. Read Operation In Serial-Out Mode

- 1. Parallel Read shown for reference only. Can also use serial output mode.

- 2. The Empty Flag is de-asserted after the N–1 rising edge of SICP of the first serial-in word. In the Serial-Out mode, a new read operation can begin trees after EF goes HIGH. In the Parallel-Out mode, a new read operation can occur immedately after FF goes HIGH.

- 3. The EF+1 Flag is de-asserted after the N-1 rising edge of SICP of the second serial-in word.

Figure 21. Empty Flag and Empty+1 Flag De-assertion in the Serial-In Mode

### NOTES:

- 1. Parallel write shown for reference only. Can also use serial input mode.

- 2. The Empty Flag (EF) is asserted in Serial-Out mode by using the tsocer parameter. This parameter is measured in the worst case condition from the rising edge of the SOCP used to clock data bit 0. Whenever EF goes LOW, there is only one word to be shifted out. In the Parallel-In mode, the EF flag is de-asserted by the rising edge of W. In the Serial-In mode, the EF flag is de-asserted by the rising edge of W.

- 3. First Write rising edge after EF is set.

- 4. Once EF has gone LOW and the last bit of the final word has been shifted out, SOCP should not be clocked until EF goes HIGH.

Figure 22. Empty Flag and Empty+1 Flag Assertion in the Serial-Out Mode (FIFO Being Emptied)

- 1. The Full Flag is asserted in the Serial-In mode by using the tsicFF parameter. This parameter is measured in the worst case condition from the rising edge of SICP following a (tpD1+twFF) delay from the first SICP rising edge of the last word.

- 2. First Read rising edge after FF is set.

- 3. After FF goes LOW and the last bit of the final word has been clocked in, SICP should not be clocked until FF goes HIGH.

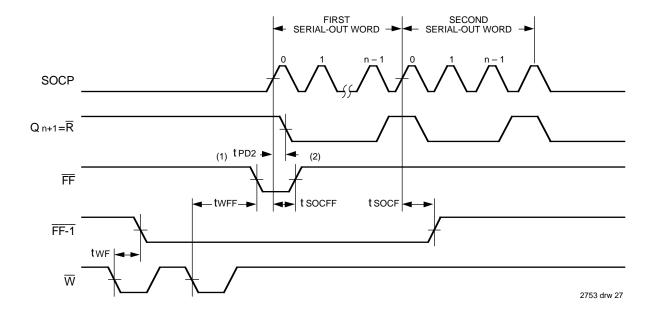

Figure 23. Full Flag and Full-1 Flag Assertlon in the Serial-In Mode (FIFO Being Filled)

#### NOTES:

- 1. The FIFO is full and a new read sequence is started.

- 2. On the first rising edge of SOCP, the FF is de-asserted. In the Serial-In mode, a new write operation can begin following trefs after FF, goes HIGH. In the Parallel-In mode, a new write operation can occur immediately after FF goes HIGH.

- 3. The  $\overline{\text{FF-1}}$  flag is de-asserted after the first SOCP of the second serial word.

Figure 24. Full Flag and Full-1 Flag De-assertion in the Serial-Out Mode

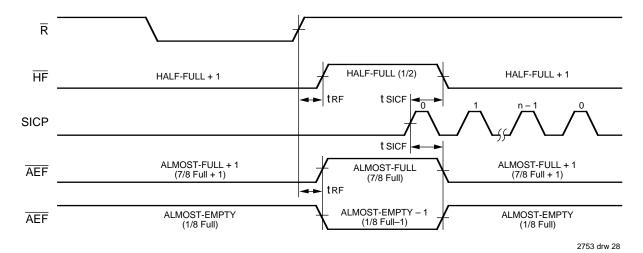

Figure 25. Half-Full, Almost-Full and Almost-Empty Timings for Serial-In Mode

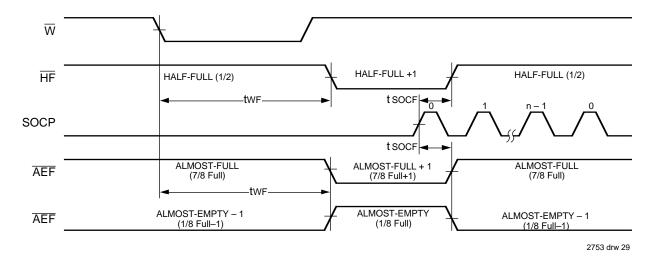

Figure 26. Half-Full, Almost-Full and Almost-Empty Timings for Serial-Out Mode

### **OPERATING DESCRIPTION**

### **PARALLEL OPERATING MODES:**

Parallel Data Input

By setting SI/PI HIGH, data is written into the FIFO in parallel through the D0-D8 input data lines.

#### **Parallel Data Output**

By setting  $\overline{SO}/PO$  HIGH, the parallel-out mode is chosen. In the parallel-out mode, as shown in Figure 4, data is available tA after the falling edge of  $\overline{R}$  and the output bus Q goes into high-impedance after  $\overline{R}$  goes HIGH.

Alternately, the user can access the FIFO by keeping  $\overline{R}$  LOW and enabling data on the bus by asserting  $\overline{OE}$ . When  $\overline{R}$  is LOW, the  $\overline{OE}$  is HIGH and the output bus is tri-stated. When  $\overline{R}$  is HIGH, the output bus is disabled irrespective of  $\overline{OE}$ . The

enable and disable timings for  $\overline{OE}$  are shown in Figure 12.

### **Single Device Mode**

A single IDT172103/72104 may be used when application requirements are for 2048/4096 words or less. The IDT72103/72104 is in the Single Device Configuration when the Expansion In  $(\overline{\text{XI}})$  control input is grounded (See Figure 27). In this mode, the  $\overline{\text{HF/XO}}$  is used as a Half-Full flag.

### **Width Expansion Mode**

Word width may be increased simply by connecting the corresponding input control signals of multiple devices. Status flags can be detected from any one of the connected devices. Figure 28 demonstrates an 18-bit word width by using two IDT72103/72104s. Any word width can be attained by adding additional IDT72103/72104.

Figure 27. Block Diagram of Single 2048 x 9/4096 x 9 FIFO in Parallel Mode

### **INPUT CONFIGURATION TABLE**

|                                |                   | Serial Input                     |                                              |                                                 |                                                 |  |  |  |

|--------------------------------|-------------------|----------------------------------|----------------------------------------------|-------------------------------------------------|-------------------------------------------------|--|--|--|

|                                |                   |                                  | Width Expansion                              |                                                 |                                                 |  |  |  |

| Pin                            | Parallel<br>Input | Single<br>Device                 | Least Significant<br>Device                  | All Other<br>Devices                            | Most Significant<br>Device                      |  |  |  |

| SĪ/PI                          | HIGH              | LOW                              | LOW                                          | LOW                                             | LOW                                             |  |  |  |

| SI                             | HIGH or LOW       | Input Data                       | Input Data                                   | Input Data                                      | Input Data                                      |  |  |  |

| SICP                           | HIGH or LOW       | Input Clock                      | Input Clock                                  | Input Clock                                     | Input Clock                                     |  |  |  |

| SIX                            | HIGH              | HIGH                             | HIGH                                         | D <sub>8</sub> of next least significant device | D <sub>8</sub> of next least significant device |  |  |  |

| W                              | Write Control     | D <sub>i</sub>                   | D <sub>i</sub> of most<br>significant device | D <sub>i</sub> of most<br>significant device    | D <sub>i</sub> of most<br>significant device    |  |  |  |

| D <sub>0</sub> -D <sub>8</sub> | Input Data        | No connect except D <sub>i</sub> | No connect except D <sub>8</sub>             | No connect except D <sub>8</sub>                | No connect except D <sub>i</sub>                |  |  |  |

| D <sub>i</sub> <sup>(1)</sup>  | _                 | W                                | _                                            | _                                               | W of all devices                                |  |  |  |

| D <sub>8</sub>                 | _                 | _                                | SIX of next most significant device          | SIX of next most significant device             | _                                               |  |  |  |

#### NOTE:

### **OUTPUT CONFIGURATION TABLE**

|                                |                    | Serial Output                       |                                              |                                                 |                                                 |  |  |  |

|--------------------------------|--------------------|-------------------------------------|----------------------------------------------|-------------------------------------------------|-------------------------------------------------|--|--|--|

|                                |                    |                                     |                                              | Width Expansion                                 |                                                 |  |  |  |

| Pin                            | Parallel<br>Output | Single<br>Device                    | Least Significant<br>Device                  | All Other<br>Devices                            | Most Significant<br>Device                      |  |  |  |

| <del>S</del> <del>O</del> /PO  | HIGH               | LOW                                 | LOW                                          | LOW                                             | LOW                                             |  |  |  |

| SO                             | _                  | Output Data                         | Output Data                                  | Output Data                                     | Output Data                                     |  |  |  |

| SOCP                           | HIGH or LOW        | Output Clock                        | Output Clock                                 | Output Clock                                    | Output Clock                                    |  |  |  |

| sox                            | HIGH               | HIGH                                | HIGH                                         | Q <sub>8</sub> of next least significant device | Q <sub>8</sub> of next least significant device |  |  |  |

| R                              | Read Control       | Q <sub>i</sub>                      | Q <sub>i</sub> of most<br>significant device | Q <sub>i</sub> of most<br>significant device    | Q <sub>i</sub> of most<br>significant device    |  |  |  |

| Q <sub>0</sub> -Q <sub>8</sub> | Output Data        | No connect<br>except D <sub>i</sub> | No connect except Q <sub>8</sub>             | No connect except Q <sub>8</sub>                | No connect except Qi                            |  |  |  |

| Q <sub>i</sub> <sup>(1)</sup>  | _                  | R                                   | _                                            | _                                               | R of all devices                                |  |  |  |

| Q <sub>8</sub>                 | _                  | _                                   | SOX of next most significant device          | SOX of next most significant device             | _                                               |  |  |  |

2753 tb I 12

<sup>2753</sup> tbl 11 1. D<sub>i</sub> refers to the rnost significant bit of the serial word. If multiple devices are width cascaded, D<sub>i</sub> is the rnost significant bit from the most significant device.

<sup>1.</sup>  $Q_i$  refers to the most significant bit of the serial word. If multiple devices are width cascaded,  $Q_i$  is the rnost significant bit from the most significant device.

1. Flag detection is accomplished by monitoring all the flag signals of either (any) device used in the width expansion configuration. Do not connect any flag signals together.

Figure 28. Block Diagram of 2048 x 18/4096 x 18 FIFO Memory Used in Width Expansion in Parallel Mode

### **TRUTH TABLES**

## TABLE 2: RESET AND RETRANSMIT —

### SINGLE DEVICE CONFIGURATION/WIDTH EXPANSION IN PARALLEL MODE

|            | Inputs <sup>(2)</sup> |    |    | Internal Status <sup>1)</sup> |                          | Outputs |    |    |

|------------|-----------------------|----|----|-------------------------------|--------------------------|---------|----|----|

| Mode       | RS                    | FL | XI | Read Pointer                  | Write Pointer            | ĀĒF, ĒF | FF | ĦF |

| Reset      | 0                     | Х  | 0  | Location Zero                 | Location Zero            | 0       | 1  | 1  |

| Retransmit | 1                     | 0  | 0  | Location Zero                 | Unchanged                | Х       | Х  | X  |

| Read/Write | 1                     | 1  | 0  | Increment <sup>(1)</sup>      | Increment <sup>(1)</sup> | Х       | Х  | Х  |

#### NOTES:

2753 tbl 13

Pointer will increment if appropriate flag is HIGH.

RS = Reset Input, FL/RT = First Load/Retransmit, EF = Empty Flag Output, FF = Full Flag Output,  $\overline{XI}$  = Expansion Input.

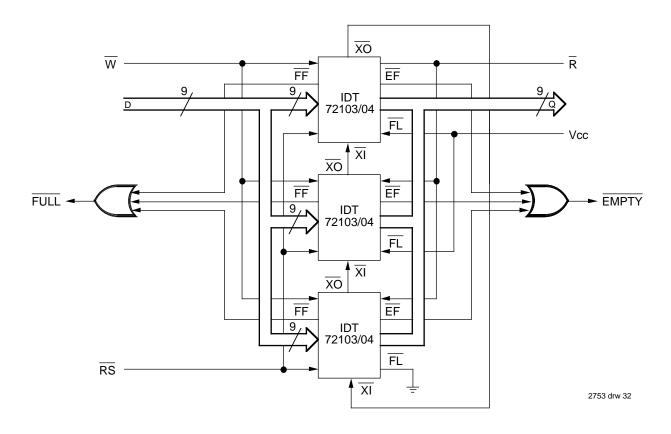

### **DEPTH EXPANSION (DAISY CHAIN) MODE**

The IDT72103/4 can be easily adapted to applications where the requirements are for greater than 2048/4096 words. Figure 29 demonstrates Depth Expansion using three IDT72103/4s. Any memory depth can be attained by adding additional IDT72103/4s. The IDT72103/4 operates in the Depth Expansion configuration when the following conditions are met:

- 1. The first device must be designated by grounding the First Load (FL) control input pin.

- 2. All other devices must have the  $\overline{FL}$  pin in the high state.

- 3. The Expansion Out  $(\overline{XO})$  pin of each device must be tied to the Expansion In  $(\overline{XI})$  pin of the next device. See Figure 29.

- 4. External logic is needed to generate a composite Full Flag (FF) and Empty Flag (EF). This requires the OR-ing of all EFs and OR-ing of all FFs (i.e., all must be set to generate the correct composite FF or EF). See Figure 29.

- 5. The Retransmit (RT) function and Half-Full Flag (HF) are not available in the Depth Expansion mode.

#### NOTE:

1.  $\overline{SI}/PI$  and  $\overline{SO}/PO$  pins are tied to VCC.

Figure 29. Block Diagram of 6,144 x 9/12,288 x 9-FIFO Memory, Depth Expansion in Parallel Mode

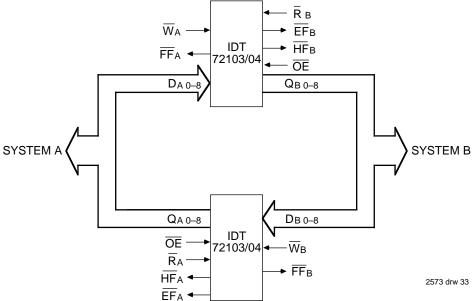

### **BIDIRECTIONAL MODE**

Applications requiring data buffering between two systems (each system capable of Read and Write operations) can be achieved by pairing IDT72103/4 as shown in Figure 30. Both Depth Expansion and Width Expansion may be used in this mode.

#### NOTE:

1. SI/PI and SO/PO pins are tied to VCC.

Figure 30. Bidirectional FIFO Mode

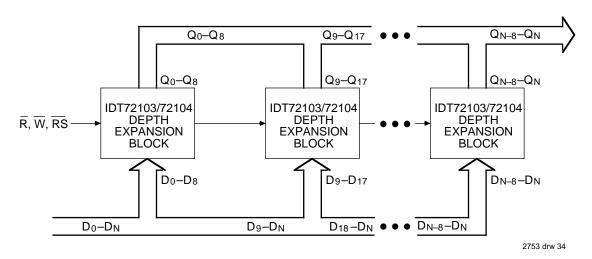

### **COMPOUND EXPANSION MODE**

The two expansion techniques described above can be applied together in a straightforward manner to achieve large FIFO arrays (see Figure 31).

#### NOTE:

- 1. SI/PI and SO/PO pins are tied to VCC.

- 2. For depth expansion block see DEPTH EXPANSION Section and Figure 29.

- 3. For Flag Detection see WIDTH EXPANSION SECTION and Figure 28.

Figure 31. Compound FIFO Expansion

| TABLE 3: RESET AND FIRST LOAD TRUTH TABLE — |

|---------------------------------------------|

| DEPTH EXPANSION/COMPOUND EXPANSION MODE     |

| Mode                            | Inputs <sup>(2)</sup> |    |     | Internal Status |               | Outputs |    |

|---------------------------------|-----------------------|----|-----|-----------------|---------------|---------|----|

|                                 | RS                    | FL | XI  | Read Pointer    | Write Pointer | ĒF      | FF |

| Reset-First<br>Device           | 0                     | 0  | (1) | Location Zero   | Location Zero | 0       | 1  |

| Retransmit all<br>Other Devices | 0                     | 1  | (1) | Location Zero   | Location Zero | 0       | 1  |

| Read/Write                      | 1                     | Х  | (1) | X               | Х             | X       | Х  |

1.  $\overline{XI}$  is connected to  $\overline{XO}$  of previous device.

2753 tbl 14

FF = Full Flag Output,

$\overline{XI}$  = Expansion Input.

### **SERIAL OPERATING MODES:**

### **Serial Data Input**

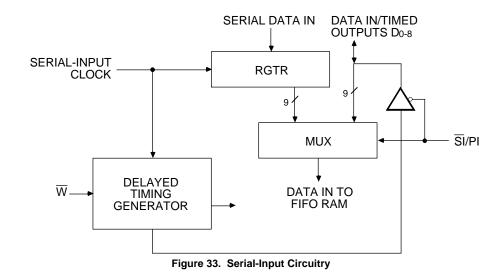

The Serial Input mode is selected by grounding the SI/PI line. The D0-8 lines are then outputs which are used to program the width of the serial word. They are taps off a digital delay line which are meant for connection to the  $\overline{W}$  input. For instance, connecting D6 to  $\overline{W}$  will program a serial word width of 7 bits, connecting D7 to  $\overline{W}$  will program a serial word width of 8 bits and so on.

By programming the serial word width, an economy of clock cycles is achieved. As an example, if the word width is 6 bits, then on every 6th clock cycle the serial data register is written in parallel into the FIFO RAM array. Thus, the possible clock cycles for an extra 3 bits of width in the RAM array are not required.

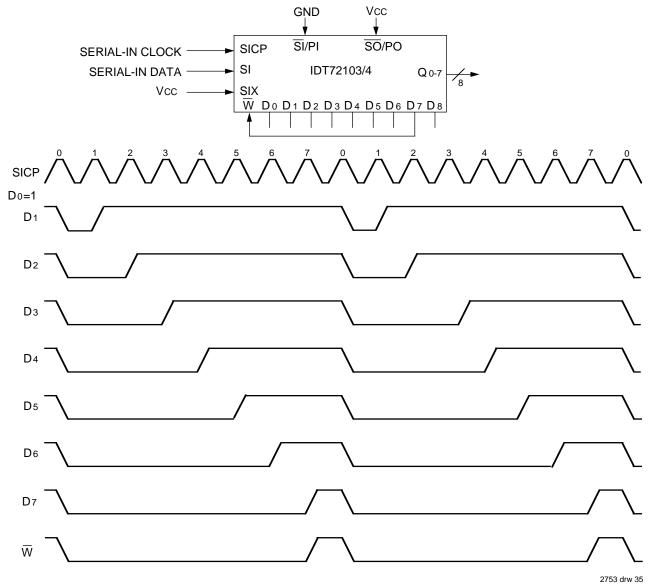

The SIX signal is used for Serial-In Expansion. When the serial word width is 9 or less, the SIX input must be tied HIGH. When more than 9 bits of serial word width is required, more than one device is required. The SIX input of the least significant device must be tied HIGH. The D8 pin of the least significant device must be tied to SIX of the next significant device. In other words, the SIX input of the most significant and intermediate devices must always be connected to the D8 of the next least significant device.

Figure 32 shows the relationship of the SIX, SICP and D0-8 lines. In the stand alone case (Figure 32), on the first LOW-to-HIGH of SICP, the D1-8 lines go LOW and the D0 line remains HIGH. On the next SICP clock edge, the D1 goes HIGH, then D2 and so on. This continues until the D line, which is connected to  $\overline{W}$ , goes HIGH. On the next clock cycle, after  $\overline{W}$  is HIGH, all of the D lines go LOW again and a new serial word input starts.

In the cascaded case, the first LOW-to-HIGH SICP clock edge for a serial word will cause all timed outputs (D) to go LOW except for D0 of the least significant device. The D outputs of the least significant device will go high on consecutive clock cycles until D8. When D8 goes HIGH, the SIX of the next device goes HIGH. On the next cycle after the SIX input is brought HIGH, the D0 goes HIGH; then on the next cycle D1 and so on. A Di output from the most significant device is issued to create the  $\overline{\rm W}$  for all cascaded devices.

The minimum serial word width is 4 bits and the maximum is virtually unlimited.

When in the Serial mode, the Least Significant Bit of a serial stream is shifted in first. If the FIFO output is in the Parallel mode, the first serial bit will come out on Q0. The second bit shifted in is on Q1 and so on.

In the Serial Cascade mode, the serial input (SI) pins must be connected together. Each of the devices then receives serial information together and uses the SIX and D0-8 lines to determine whether to store it or not.

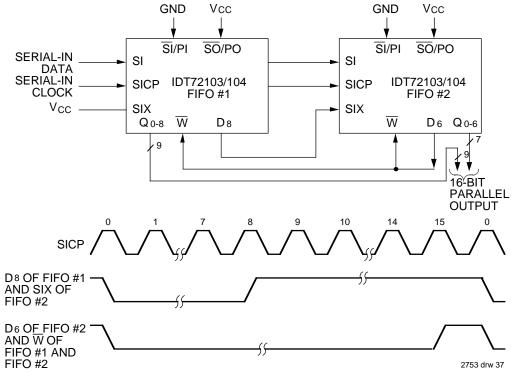

The example shown in Figure 34 shows the interconnections for a serializing FIFO that transfers data to the internal RAM in 16-bit quantities (i.e. every 16 SICP cycles). This corresponds to incrementing the write pointer every 16 SICP cycles.

Once  $\overline{W}$  goes HIGH With the last serial bit in, SICP should not be clocked again until  $\overline{FF}$  goes HIGH.

<sup>2.</sup>  $\overline{RS}$  = Reset Input,  $\overline{FL/RT}$  = First Load/Retransmit,  $\overline{EF}$  = Empty Flag Ouput,

### SINGLE DEVICE SERIAL INPUT CONFIGURATION

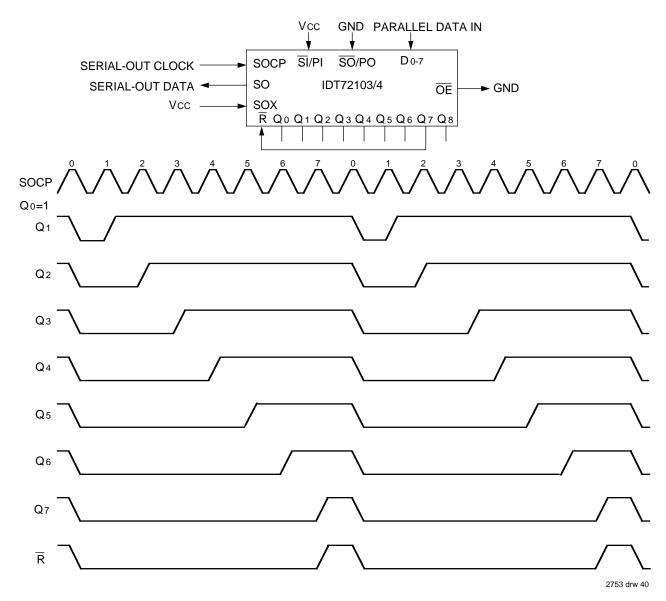

Figure 32. Serial-In Mode Where 8-Bit Parallel Output Data is Read

### **SERIAL INPUT WIDTH EXPANSION**

Figure 34. Serial-In Configuration for Serial-In to Parallel-Out Data of 16 bits

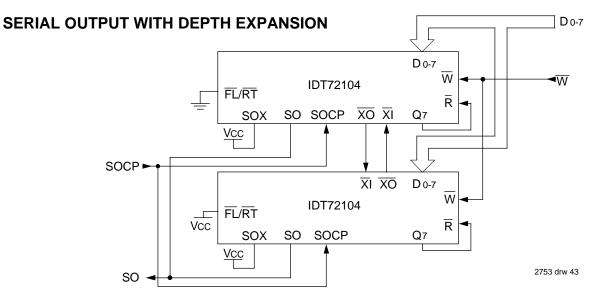

### **SERIAL INPUT WITH DEPTH EXPANSION**

### NOTE:

1. All \$\overline{SI}\$/PI pins are tied to GND and \$\overline{SO}\$/PO pins are tied to Vcc. oe is tied LOW. For \$\overline{FF}\$ and \$\overline{EF}\$ connections see Figure 29.

Figure 35. An 8K x 8 Serial-In, Parallel-Out FIFO

#### SERIAL INPUT WITH WIDTH AND DEPTH EXPANSION

#### NOTE:

1. All SI/PI pins are tied to GND. SO/PO pins are tied to Vcc. For FL/RT, FF and EF connections see Figure 29.

Figure 36. An 8K x 24 Serial-In, Parallel-Out FIFO Using Six IDT72104s

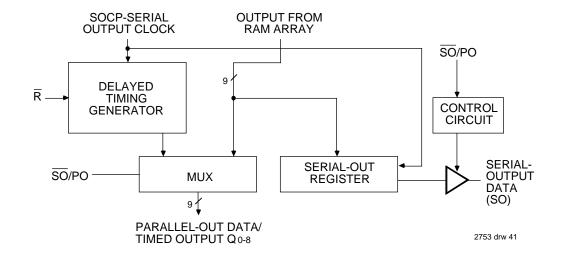

### **SERIAL DATA OUTPUT**

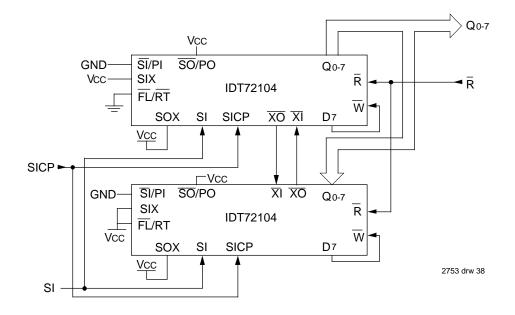

The Serial Output mode is selected by setting the SO/PO line LOW. When in the Serial-Out mode, one of the Q1-8 lines should be used to control the R signal. In the Serial-Out mode, the Q0-8 are taps off a digital delay line. By selecting one of these taps and connecting it to R, the width of the serial word to be read and shifted is programmed. For instance, if the Q5 line is connected to the R input, on every sixth clock cycle a new word is read from the FIFO RAM array and begins to be shifted out. The serial word is shifted out Least Significant Bit first. If the input mode of the FIFO is parallel, the information that was written into the D0 bit will come out as the first bit of the serial word. The second bit of the serial stream will be the D1 bit and so on.

In the stand alone case, the SOX line is tied HIGH and not used. On the first LOW-to-HIGH of the SOCP clock, all of the Q outputs except for Q0 go LOW and a new serial word is started. On the next clock cycle, Q1 will go HIGH, Q2 on the next clock cycle and so on, as shown in Figure 37. This continues until the Q line, which is connected to R, goes HIGH at which point all of the Q lines go LOW on the next clock and a new word is started.

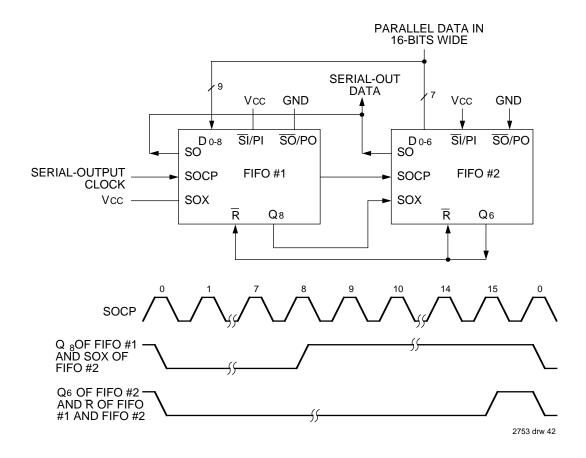

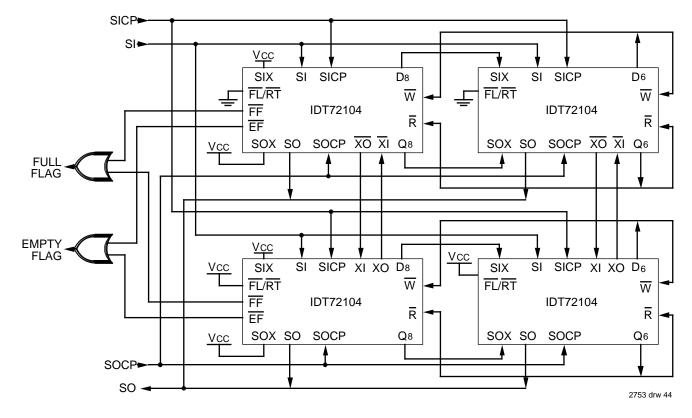

In the cascaded case, word width of more than 9 bits can