# VCSO BASED FEC CLOCK PLL / HITLESS SWITCHING OPTION

## GENERAL DESCRIPTION

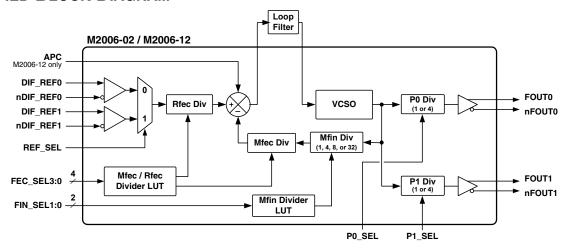

The M2006-02 and -12 are VCSO (Voltage Controlled SAW Oscillator) based clock generator PLLs designed for clock frequency translation and jitter attenuation. They support both forward and inverse FEC (Forward Error Correction) clock multiplication ratios, which are pin-selected from pre-programming look-up tables.

The M2006-12 adds Hitless Switching and Phase Build-out to enable SONET (GR-253) / SDH (G.813) MTIE and TDEV compliance during reference clock reselection. Hitless Switching (HS) engages when a 4ns or greater clock phase change is detected.

This phase-change triggered implementation of HS is not recommended when using an unstable reference (more than 1ns jitter pk-to-pk) or when the resulting phase detector frequency is less than 5MHz. Refer to full product data sheet for more information.

## **FEATURES**

- Pin-selectable PLL divider ratios support forward and inverse FEC ratio translation, including:

- 255/238 (OTU1) Mapping and 238/255 De-mapping

255/237 (OTU2) Mapping and 237/255 De-mapping

255/236 (OTU3) Mapping and 236/255 De-mapping

- Supports input reference and VCSO frequencies up to 700MHz, supports loop timing modes (Specify VCSO frequency at time of order)

- Low phase jitter < 0.5 ps rms typical</li> (12kHz to 20MHz or 50kHz to 80MHz)

- M2006-12 includes APC pin for Phase Build-out function (for absorption of the input phase change)

- Commercial and Industrial temperature grades

- Single 3.3V power supply

- Small 9 x 9 mm SMT (surface mount) package

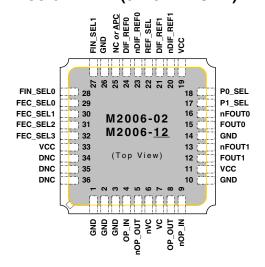

# PIN ASSIGNMENT (9 x 9 mm SMT)

### Example I/O Clock Frequency Combinations Using M2006-02/-12-622.0800 and Inverse FEC Ratios

| FEC PLL Ratio<br>Mfec / Rfec | Base Input Rate <sup>1</sup><br>(MHz) | Output Clock<br>(either output)<br>MHz |

|------------------------------|---------------------------------------|----------------------------------------|

| 1/1                          | 622.0800                              | 622.08                                 |

| 238/255                      | 666.5143                              | 022.06<br>0r                           |

| 237/255                      | 669.3266                              | 155.52                                 |

| 236/255                      | 236/255 672.1627                      |                                        |

Note 1: Input reference clock can be the base frequency shown divided by "Mfin", as shown in the following table.

#### Mfin Divider and Example Input Frequencies

| FIN_SEL1:0 |   | Mfin Value | For Base Input Rate of 622.0800<br>Sample Ref. Freq. (MHz) |

|------------|---|------------|------------------------------------------------------------|

| 1          | 1 | 1          | 622.08                                                     |

| 1          | 0 | 4          | 155.52                                                     |

| 0          | 1 | 8          | 77.76                                                      |

| 0          | 0 | 32         | 19.44                                                      |

#### SIMPLIFIED BLOCK DIAGRAM

M2006-02/-12 PB Rev 2.2 Revised 06Jul2004