## Hitachi Single-Chip Microcomputer

## H8/3802 Series

H8/3802 HD6473802, HD6433802 H8/3801 HD6433801 H8/3800 HD6433800

Hardware Manual

# HITACHI

ADE-602-203A Rev. 2.0 1/9/01 Hitachi Ltd.

### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

## List of Items Revised or Added for This Version

| Section                                                           | Page     | Item                                                                                         | Description                               |

|-------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------|-------------------------------------------|

| 1.1 Overview                                                      | 3        | Table 1.1 Features                                                                           | Description of time specification amended |

| 2.8.1 Memory Map                                                  | 46       | Figure 2.16(2) H8/3801 Memory<br>Map                                                         | Figure amended                            |

|                                                                   | 47       | Figure 2.16(3) H8/3800 Memory<br>Map                                                         | Figure amended                            |

| 3.3.1 Overview                                                    | 60       | Table 3.2 Interrupt Sources andTheir Priorities                                              | Amended                                   |

| 3.3.2 Interrupt Control Registers                                 | 61       | Table 3.3 Interrupt Control Registers                                                        | Initial values amended                    |

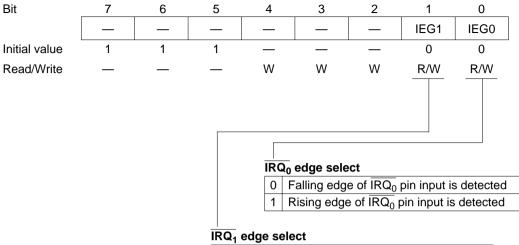

|                                                                   |          | 1. IRQ edge select register (IEGR)                                                           | Bits 4 to 2 amended                       |

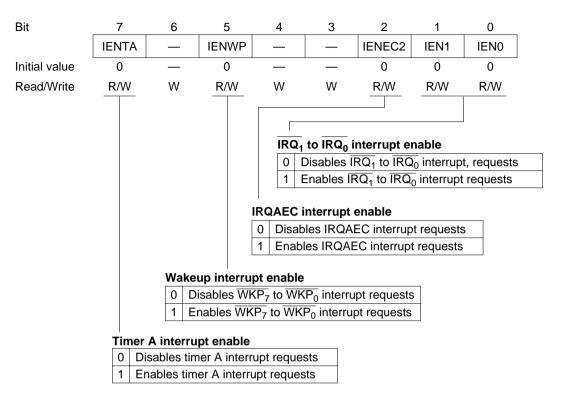

|                                                                   | 62       | <ol> <li>Interrupt enable register 1<br/>(IENR1)</li> </ol>                                  | Bits 6, 4, and 3 amended                  |

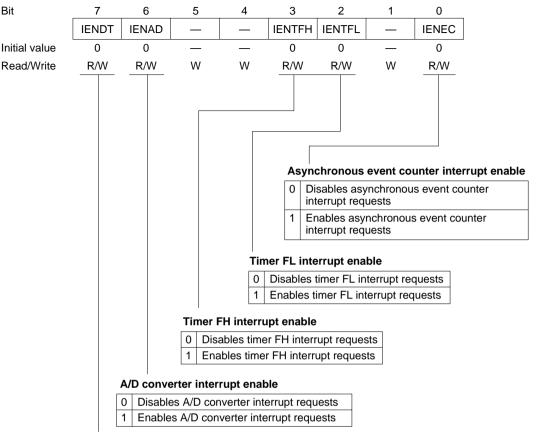

|                                                                   | 63 to 65 | 3. Interrupt enable register 2 (IENR2)                                                       | Bits 5, 4, and 1 amended                  |

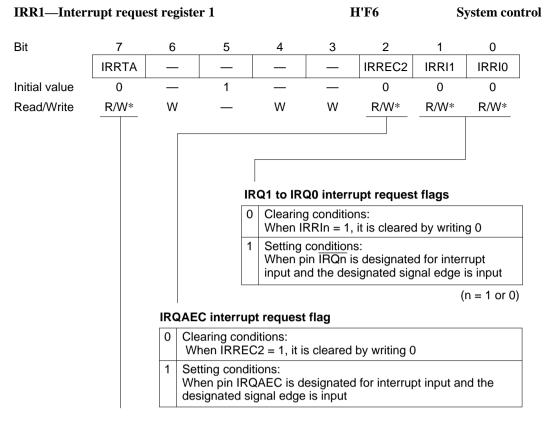

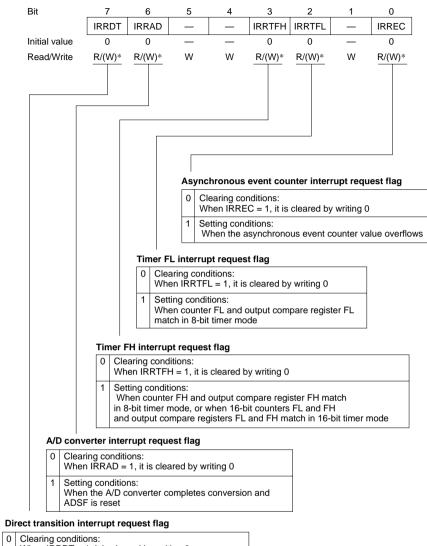

|                                                                   | 65       | 4. Interrupt request register 1 (IRR1)                                                       | Bits 6, 4, and 3 amended                  |

|                                                                   | 67, 68   | 5. Interrupt request register 2 (IRR2)                                                       | Bits 5, 4, and 1 amended                  |

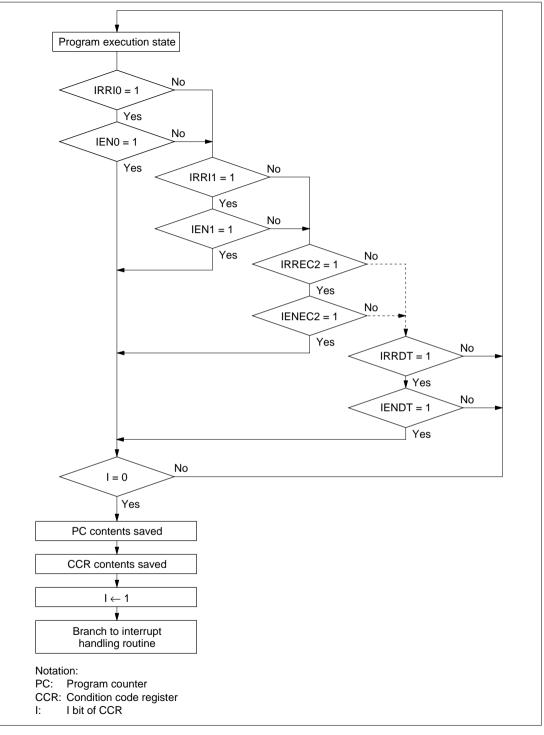

| 3.3.5 Interrupt<br>Operations                                     | 74       | Figure 3.3 Flow up to Interrupt Acceptance                                                   | Figure amended                            |

| 3.4.2 Notes on<br>Rewriting Port Mode<br>Registers                | 79       | Table 3.5Conditions under whichInterrupt Request Flag is Set to 1                            | IRREC2 flag condition amended             |

| 3.4.3 Interrupt<br>Request Flag Clearing<br>Methods               | 80       | 3.4.3 Interrupt Request Flag<br>Clearing Method                                              | Description added                         |

| 4.5 Note on Oscillators                                           | 90 to 92 | 4.5.1 Definition of Oscillation<br>Setting Standby Time                                      | Description added                         |

|                                                                   |          | 4.5.2 Notes on Use of Crystal<br>Oscillator Element(Excluding<br>Ceramic Oscillator Element) |                                           |

| 5.1 Overview                                                      | 95       | Table 5.2 Internal State in Each<br>Operating Mode                                           | Note 7 amended                            |

| 5.3.3 Oscillator Setting<br>Time after Standby<br>Mode is Cleared | 103      | Table 5.4 Clock Frequency and Setting Time                                                   | Changed                                   |

| Section                                             | Page     | Item                                                              | Description                                                      |

|-----------------------------------------------------|----------|-------------------------------------------------------------------|------------------------------------------------------------------|

| 5.5.2 Clearing<br>Subsleep Mode                     | 108      | Clearing by interrupt                                             | Description amended                                              |

| 5.6 Subactive Mode                                  | 109      | 5.6.1 Transition to Subactive Mode                                | Description amended                                              |

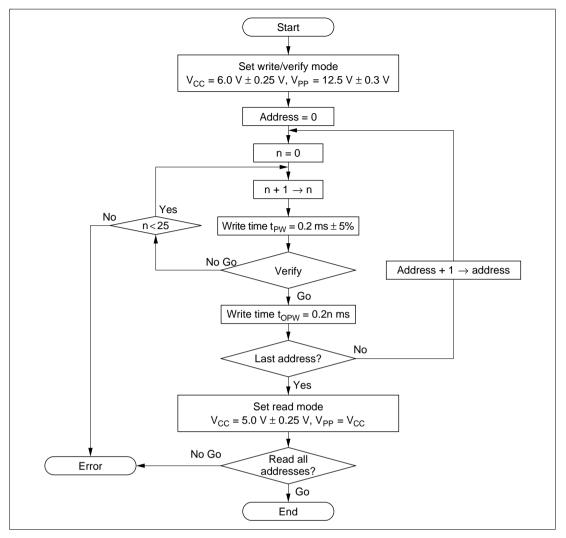

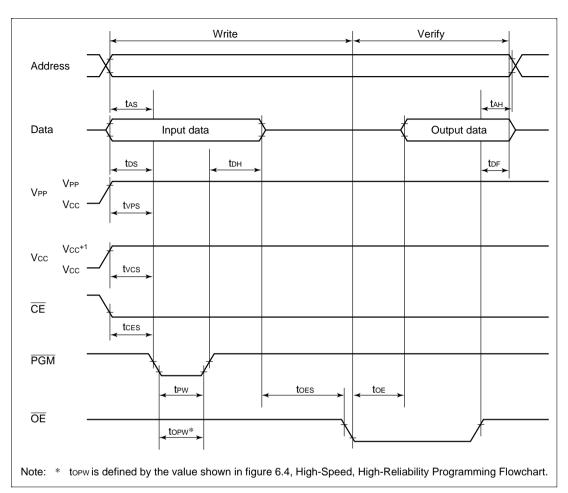

| 6.3.1 Writing and Verifying                         | 122      | Figure 6.4 High-Speed,High-<br>Reliability Programming Flow Chart | Write time t <sub>OPW</sub> amended                              |

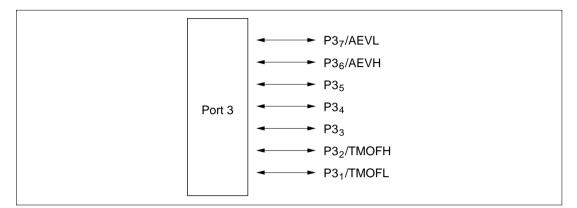

| 8.1 Overview                                        | 131, 132 | Table 8.1 Port Functions                                          | Other function of port 3<br>and description of port 9<br>amended |

| 8.2.2 Register<br>Configuration and<br>Description  | 133      | Table 8.2 Port 3 Registers                                        | Amended and register added                                       |

|                                                     | 134      | 1. Port data register 3 (PDR3)                                    | Bit 0 and description amended                                    |

|                                                     |          | 2. Port control register 3 (PCR3)                                 | Bit 0 and description amended                                    |

|                                                     |          | 3. Port pull-up control register 3 (PUCR3)                        | Bit 0 and description amended                                    |

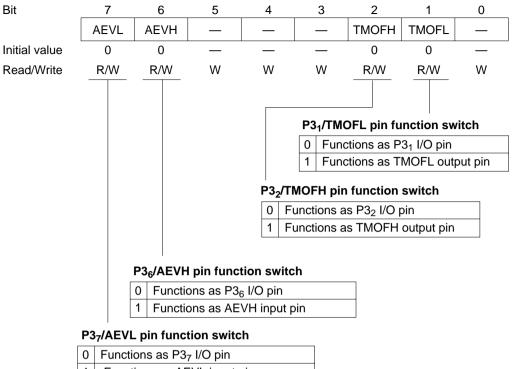

|                                                     | 135, 136 | 4. Port mode register 3 (PMR3)                                    | Bits 5 to 3 and 0, and description amended                       |

|                                                     | 136      | 5. Port mode register 2 (PMR2)                                    | Added                                                            |

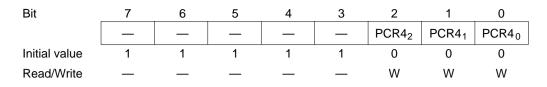

| 8.3.2 Register<br>Configuration and<br>Description  | 139      | Table 8.5 Port 4 Register                                         | Initial value amended                                            |

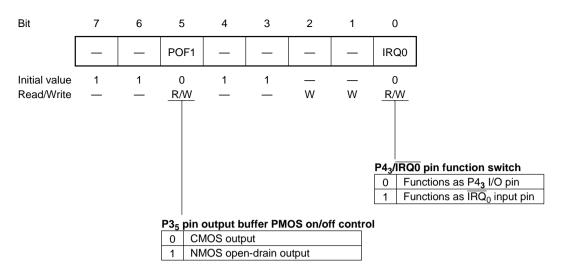

|                                                     | 140, 141 | 3. Port mode register 2 (PMR2)                                    | Bits 2 and 1, and description amended                            |

| 8.3.3 Pin Functions                                 | 141      | Table 8.6 Port 4 Pin Functions                                    | Description amended                                              |

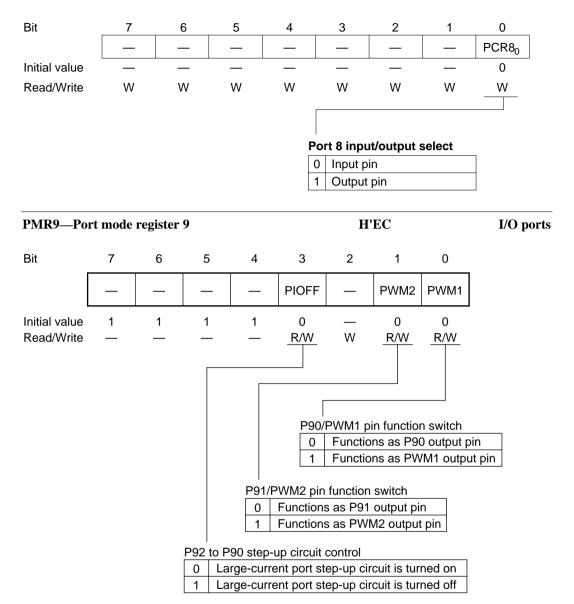

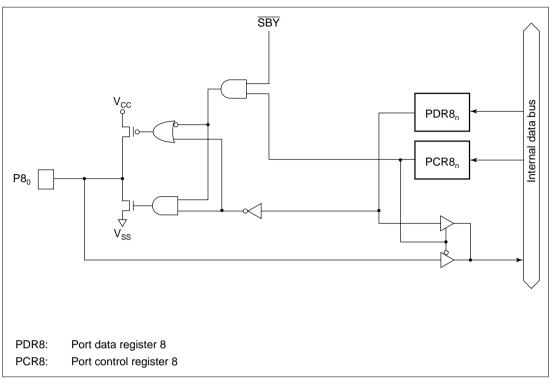

| 8.7.2 Register<br>Configuration and<br>Description  | 155      | Table 8.17 Port 8 Registers                                       | Initial value amended                                            |

|                                                     | 156      | 1. Port data register 8 (PDR8)                                    | Bits 7 to 1 amended                                              |

|                                                     |          | 2. Port control register 8 (PCR8)                                 | Bits 7 to 1 amended                                              |

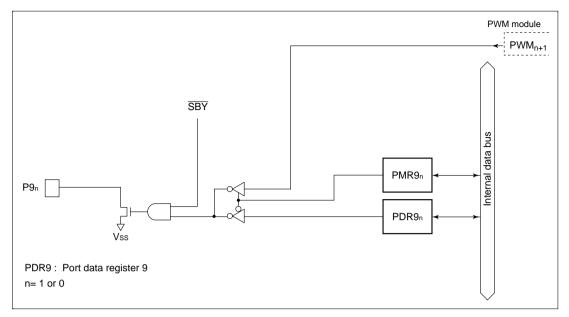

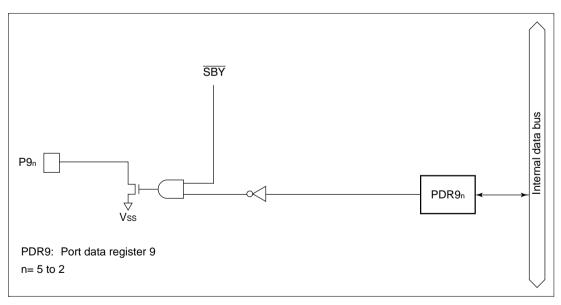

| 8.8 Port 9                                          | 158      | 8.8.1 Overview                                                    | Description amended                                              |

| 8.8.2 Register<br>Configuration and<br>Description  |          | Table 8.20 Port 9 Registers                                       | Initial value amended                                            |

|                                                     | 159      | 2. Port mode register 9 (PMR9)                                    | Bit 2 amended, description added, and Note changed               |

| 8.10.2 Register<br>Configuration and<br>Description | 165      | Table 8.26 Port B Register                                        | Initial values added                                             |

| Section                                              | Page     | Item                                                                                                                                                               | Description                                                |

|------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

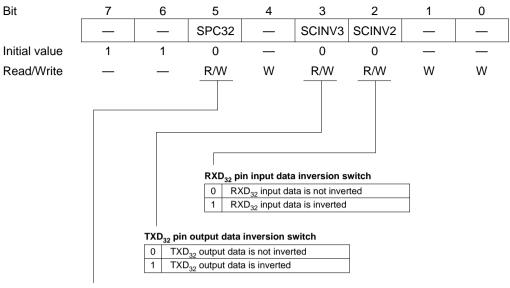

| 8.11.2 Register<br>Configuration and<br>Descriptions | 168, 169 | Serial Port Control Register<br>(SPCR)                                                                                                                             | Bits 4, 1, and 0, and description amended                  |

| 8.12 Application Note                                | 170      | 8.12.1 How to Handle an Unused Pin                                                                                                                                 | Description added                                          |

| 9.1 Overview                                         | 171      | Table 9.1 Timer Functions                                                                                                                                          | Internal clock of<br>asynchronous event<br>counter amended |

| 9.2.1 Overview                                       | 174      | Table 9.2 Timer A Registers                                                                                                                                        | Initial value amended                                      |

| 9.2.2 Register<br>Descriptions                       | 174      | 1. Timer mode register A (TMA)                                                                                                                                     | Bits 7 to 5 amended                                        |

| 9.2.5 Application Note                               | 178      | 9.2.5 Application Note                                                                                                                                             | Description added                                          |

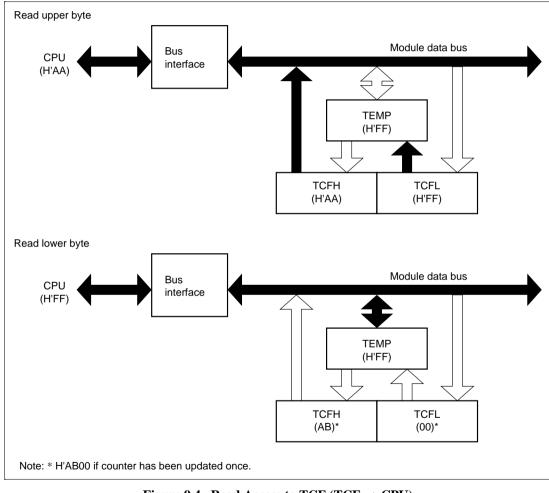

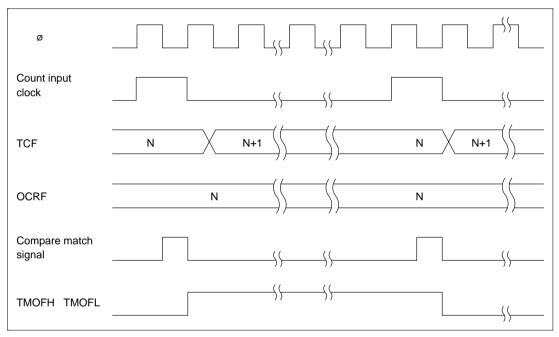

| 9.3.4 Operation                                      | 192      | 1. Timer F operation                                                                                                                                               | Description amended                                        |

|                                                      |          | a. Operation in 16-bit timer mode                                                                                                                                  |                                                            |

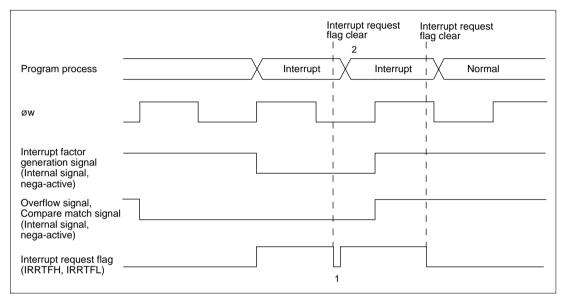

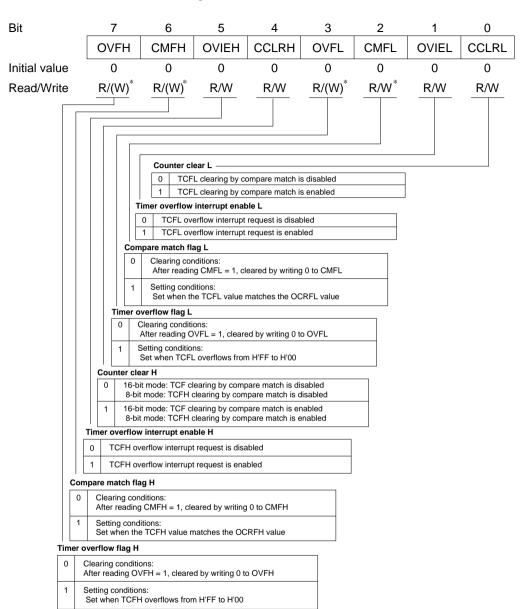

| 9.3.5 Application Note                               | 196, 197 | 3. Clear timer FH, timer FL<br>interrupt request flags (IRRTFH,<br>IRRTFL), timer overflow flags H, L<br>(OVFH, OVFL) and compare match<br>flags H, L (CMFH, CMFL) | Description added                                          |

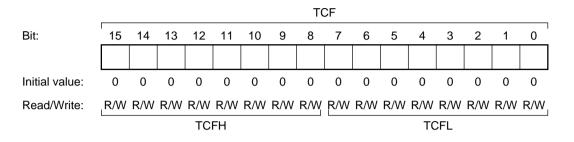

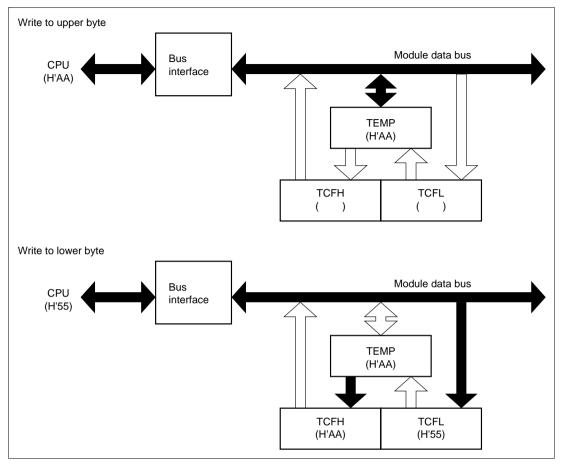

|                                                      |          | 4. Timer counter (TCF) read/write                                                                                                                                  |                                                            |

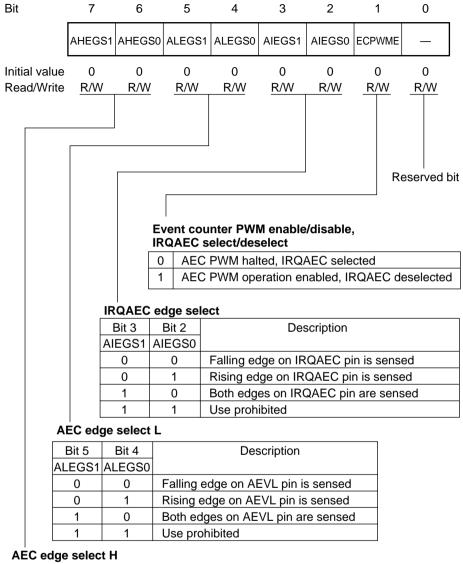

| 9.4.2 Register<br>Configurations                     | 202      | 5. Input pin edge selection register (AEGSR)                                                                                                                       | Bit name amended                                           |

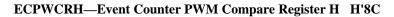

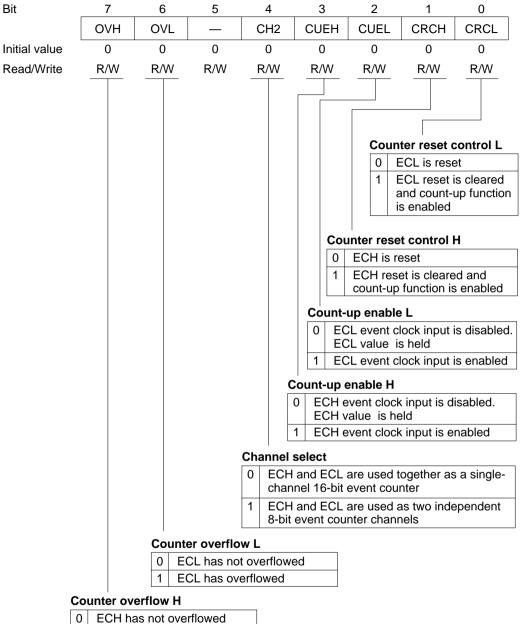

|                                                      | 204      | <ol> <li>Event counter control register<br/>(ECCR)</li> </ol>                                                                                                      | Bit name, R/W form, and description amended                |

|                                                      | 205      | 7. Event counter control/status register (ECCSR)                                                                                                                   | Bit name, R/W form, and description amended                |

| 10.1.4 Register<br>Configuration                     | 220      | Table 10.2 Registers                                                                                                                                               | Initial value of serial port control register amended      |

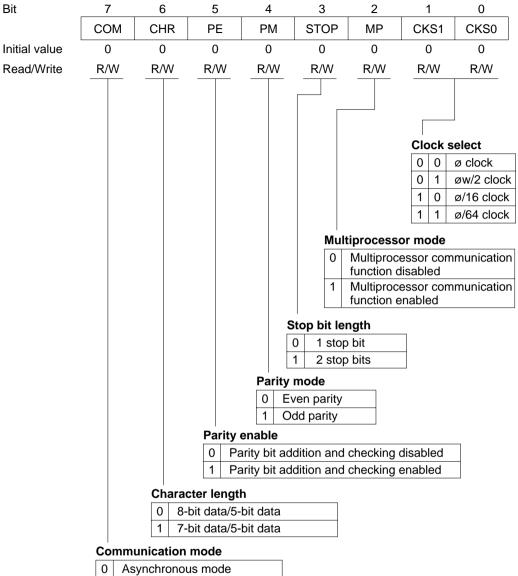

| 10.2 Register<br>Descriptions                        | 227      | 10.2.6 Serial control register 3 (SCR3)                                                                                                                            | Description of bit 5<br>amended                            |

|                                                      | 240      | 10.2.10 Serial Port Control<br>Register (SPCR)                                                                                                                     | Bits 4, 1, and 0, and description amended                  |

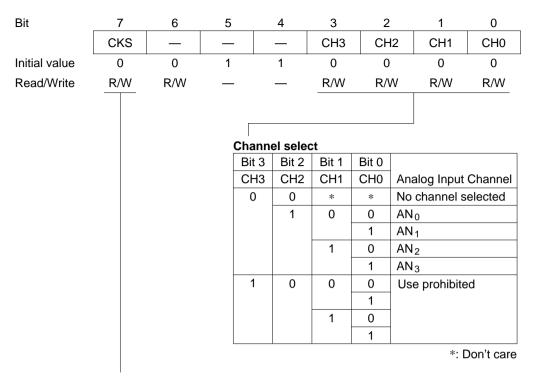

| 12.2 Register<br>Descriptions                        | 286, 287 | 12.2.2 A/D Mode Register (AMR)                                                                                                                                     | Bit 6 amended                                              |

| 12.6 Application Notes                               | 294      | 12.6 Application Notes                                                                                                                                             | 4th note added                                             |

| 13.1.4 Register<br>Configuration                     | 297      | Table 13.2 LCD Controller/Driver<br>Registers                                                                                                                      | Initial values amended                                     |

| Section                                            | Page          | ltem                                                     | Description                                               |

|----------------------------------------------------|---------------|----------------------------------------------------------|-----------------------------------------------------------|

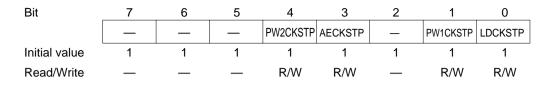

| 13.2 Register<br>Descriptions                      | 298           | 13.2.1 LCD Port Control Register<br>(LPCR)               | Bit 4 amended                                             |

|                                                    | 302           | 13.2.3 LCD Control Register 2<br>(LCR2)                  | Bits 4 to 0 amended                                       |

| 14.1 H8/3802 Series<br>Absolute Maximum<br>Ratings | 313           | Table 14.1 Absolute Maximum Ratings                      | Input voltage amended                                     |

| 14.2.2 DC<br>Characteristics                       | 318 to<br>321 | Table 14.2 DC Characteristics                            | Added and amended                                         |

| 14.2.3 AC<br>Characteristics                       | 323           | Table 14.3 Control Signal Timing                         | Amended                                                   |

| 14.2.4 A/D Converter<br>Characteristics            | 325           | Table 14.5 A/D Converter<br>Characteristics              | Test conditions amended                                   |

| 14.3 Operation Timing                              | 329           | Figure 14.5 SCI3 Synchronous<br>Mode Input/Output Timing | Reference figure in note amended                          |

| 14.6 Usage Note                                    | 331           | 14.6 Usage Note                                          | Added                                                     |

| B.2 Functions                                      | 356           | SPCR                                                     | Initial values and R/W forms amended                      |

|                                                    | 357           | AEGSR                                                    | R/W form of bit 0 amended                                 |

|                                                    | 358           | ECCR                                                     | R/W form of bit 0 amended                                 |

|                                                    | 359           | ECCSR                                                    | R/W form of bit 5 amended                                 |

|                                                    | 366           | ТМА                                                      | Initial values and R/W<br>forms of bits 7 to 5<br>amended |

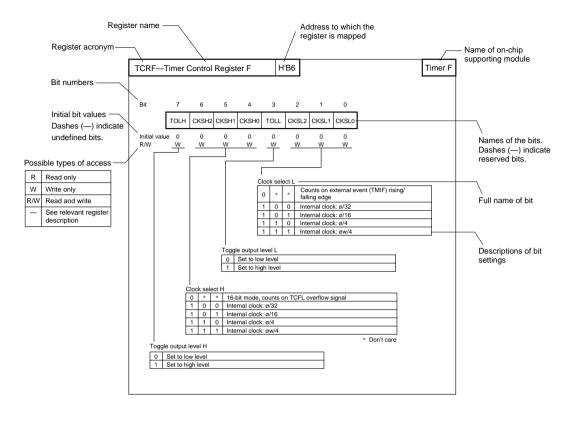

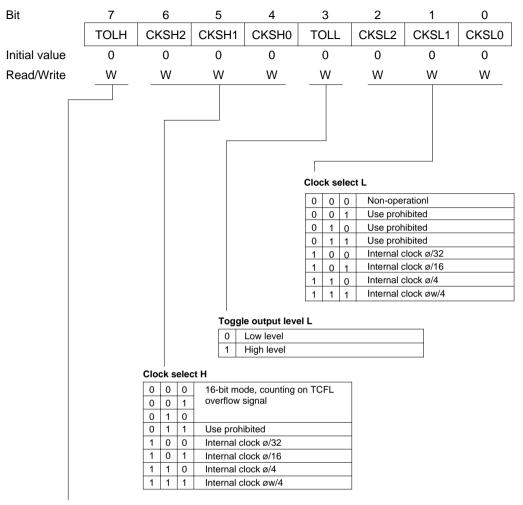

|                                                    | 368           | TCRF                                                     | Description of bits 6 to 4 amended                        |

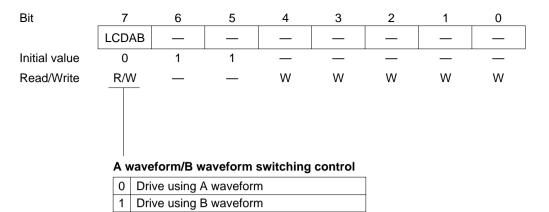

|                                                    | 371           | LPCR                                                     | Initial value and R/W form of bit 4 amended               |

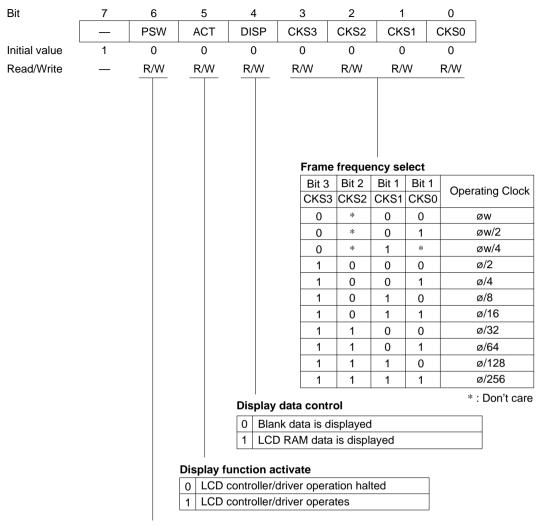

|                                                    | 372           | LCR                                                      | Description of bits 3 to 0 amended                        |

|                                                    | 373           | LCR2                                                     | Initial values and R/W<br>forms of bits 4 to 0<br>amended |

|                                                    | 374           | AMR                                                      | Initial value and R/W form of bit 6 amended               |

|                                                    | 375           | ADRRH                                                    | R/W forms amended                                         |

|                                                    | 376           | PMR2                                                     | Initial values and R/W forms amended                      |

|                                                    | 377           | PMR3                                                     | R/W forms amended                                         |

| Section       | Page | Item  | Description                                                                              |

|---------------|------|-------|------------------------------------------------------------------------------------------|

| B.2 Functions | 380  | PDR3  | Initial value amended and description added                                              |

|               |      | PDR4  | Descriptions added                                                                       |

|               | 381  | PDR5  | Description added                                                                        |

|               |      | PDR6  | Description added                                                                        |

|               |      | PDR7  | Description added                                                                        |

|               |      | PDR8  | Initial values amended and description added                                             |

|               | 382  | PDR9  | Description added                                                                        |

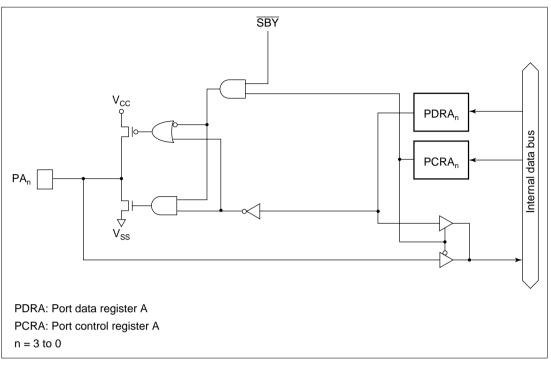

|               |      | PDRA  | Description added                                                                        |

|               |      | PDRB  | Description added                                                                        |

|               |      | PUCR3 | Initial value and R/W form amended                                                       |

|               | 383  | PCR3  | Initial value and R/W form amended                                                       |

|               | 385  | PCR8  | Initial values and R/W forms amended                                                     |

|               |      | PMR9  | Initial value and R/W form of bit 2 amended                                              |

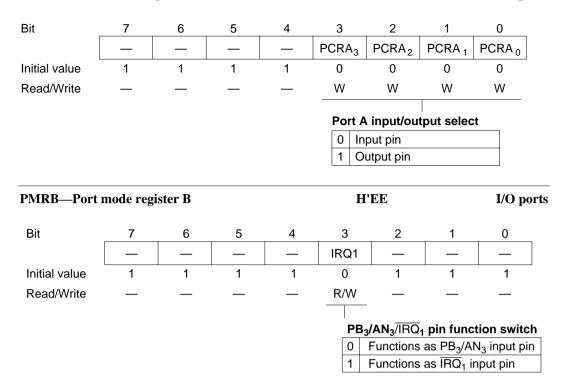

|               | 386  | PCRA  | Initial values of bits 7 to 4 amended                                                    |

|               |      | PMRB  | Initial values of bits 7 to 4 and 2 to 0 amended                                         |

|               | 389  | IEGR  | Initial values and R/W<br>forms of bits 7, 4 to 2 and<br>description of bit 1<br>amended |

|               | 390  | IENR1 | Initial values and R/W<br>forms of bits 6, 4, and 3<br>amended                           |

|               | 391  | IENR2 | Initial values and R/W<br>forms of bits 5, 4, and 1<br>amended                           |

|               | 392  | IRR1  | Initial values and R/W<br>forms of bits 6, 4, and 3<br>amended                           |

|               | 393  | IRR2  | Initial values and R/W<br>forms of bits 5, 4, and 1<br>amended                           |

| Section                      | Page | Item                                                         | Description        |

|------------------------------|------|--------------------------------------------------------------|--------------------|

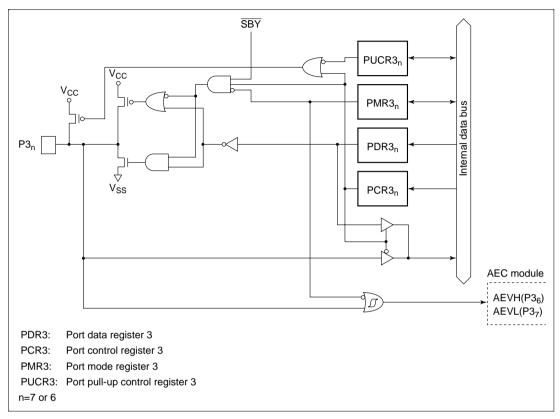

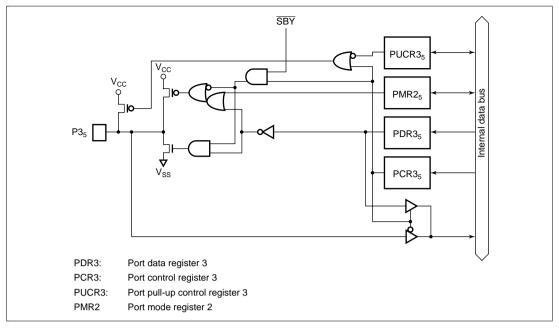

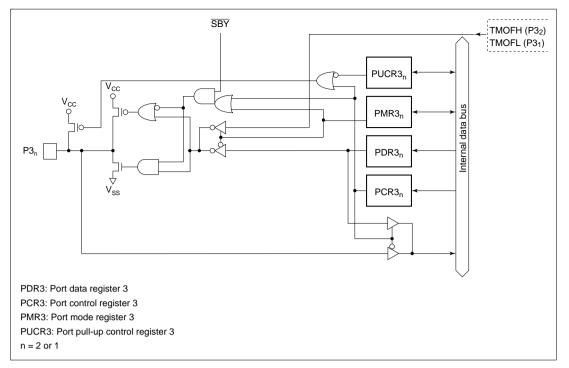

| C.1 Block Diagrams of Port 3 | 398  | Figure C.1(b) Port 3 Block<br>Diagram (Pin P3₅)              | Added              |

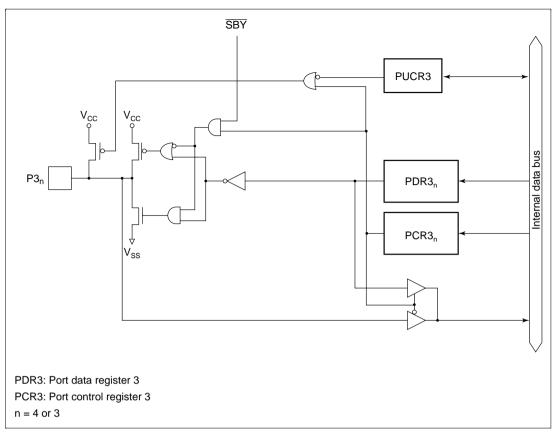

|                              | 399  | Figure C.1(c) Port 3 Block Diagram (Pins $P3_4$ and $P3_3$ ) | Pin $P3_5$ deleted |

| C.7 Block Diagrams of Port 9 | 409  | Figure C.7(a) Port 9 Block Diagram (Pins $P9_1$ and $P9_0$ ) | Figure amended     |

## Preface

The H8/300L Series of single-chip microcomputers has the high-speed H8/300L CPU at its core, with many necessary peripheral functions on-chip. The H8/300L CPU instruction set is compatible with the H8/300 CPU.

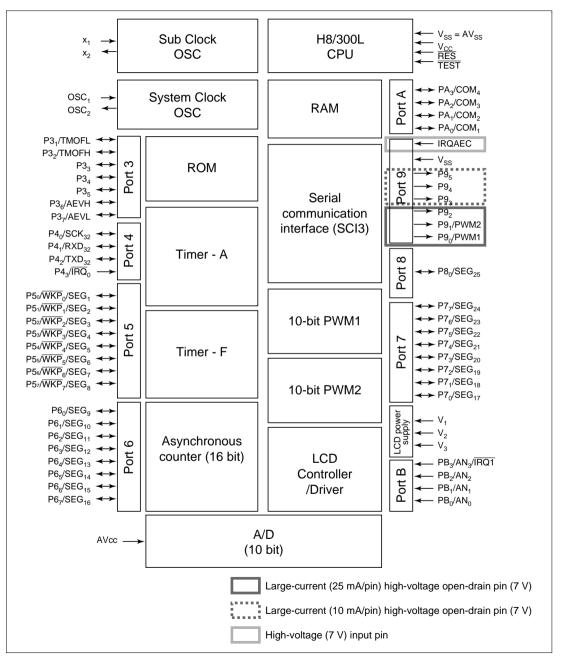

The H8/3802 Series has a system-on-a-chip architecture that includes such peripheral functions as an LCD controller/driver, three timers, a two-channel 10-bit PWM, a serial communication interface, and an A/D converter. This allows H8/3802 Series devices to be used as embedded microcomputers in systems requiring LCD display.

This manual describes the hardware of the H8/3802 Series. For details on the H8/3802 Series instruction set, refer to the H8/300L Series Programming Manual.

## Contents

| Secti | on 1                   | Overview                             | 1  |  |  |  |

|-------|------------------------|--------------------------------------|----|--|--|--|

| 1.1   | Overv                  | iew                                  | 1  |  |  |  |

| 1.2   | Internal Block Diagram |                                      |    |  |  |  |

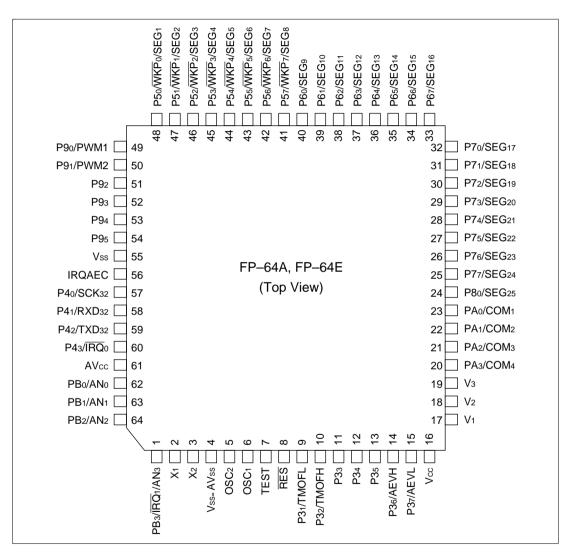

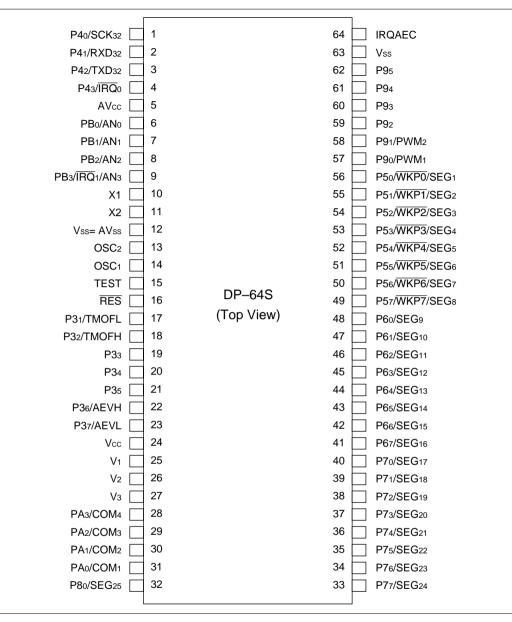

| 1.3   | Pin Ar                 | rangement and Functions              | 6  |  |  |  |

|       | 1.3.1                  | Pin Arrangement                      | 6  |  |  |  |

|       | 1.3.2                  | Pin Functions                        | 8  |  |  |  |

| Secti | on 2                   | CPU                                  | 11 |  |  |  |

| 2.1   |                        | iew                                  | 11 |  |  |  |

|       | 2.1.1                  | Features                             | 11 |  |  |  |

|       | 2.1.2                  | Address Space                        | 12 |  |  |  |

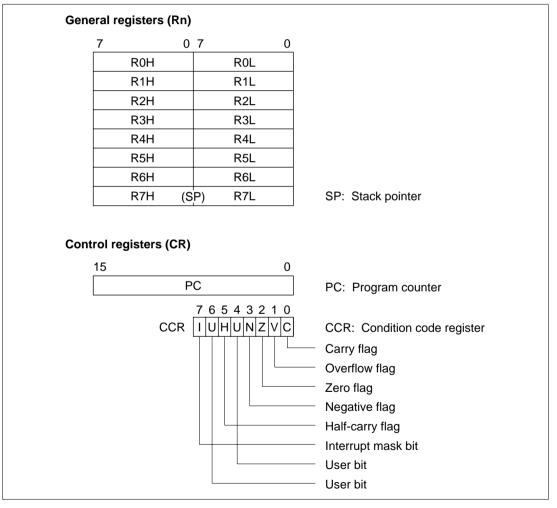

|       | 2.1.3                  | Register Configuration               | 12 |  |  |  |

| 2.2   | Regist                 | er Descriptions                      | 13 |  |  |  |

|       | 2.2.1                  | General Registers                    | 13 |  |  |  |

|       | 2.2.2                  | Control Registers                    | 13 |  |  |  |

|       | 2.2.3                  | Initial Register Values              | 14 |  |  |  |

| 2.3   | Data F                 | ormats                               | 15 |  |  |  |

|       | 2.3.1                  | Data Formats in General Registers    | 16 |  |  |  |

|       | 2.3.2                  | Memory Data Formats                  | 17 |  |  |  |

| 2.4   | Addre                  | ssing Modes                          | 18 |  |  |  |

|       | 2.4.1                  | Addressing Modes                     | 18 |  |  |  |

|       | 2.4.2                  | Effective Address Calculation        | 20 |  |  |  |

| 2.5   | Instruc                | tion Set                             | 24 |  |  |  |

|       | 2.5.1                  | Data Transfer Instructions           | 26 |  |  |  |

|       | 2.5.2                  | Arithmetic Operations                | 28 |  |  |  |

|       | 2.5.3                  | Logic Operations                     | 29 |  |  |  |

|       | 2.5.4                  | Shift Operations                     | 29 |  |  |  |

|       | 2.5.5                  | Bit Manipulations                    | 31 |  |  |  |

|       | 2.5.6                  | Branching Instructions               | 35 |  |  |  |

|       | 2.5.7                  | System Control Instructions          | 37 |  |  |  |

|       | 2.5.8                  | Block Data Transfer Instruction      | 38 |  |  |  |

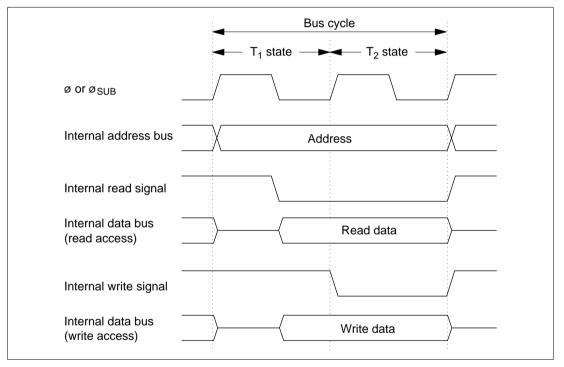

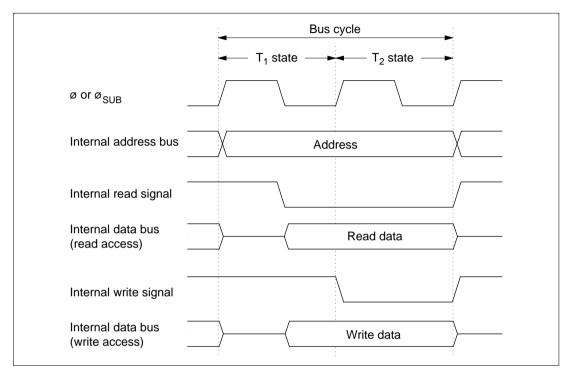

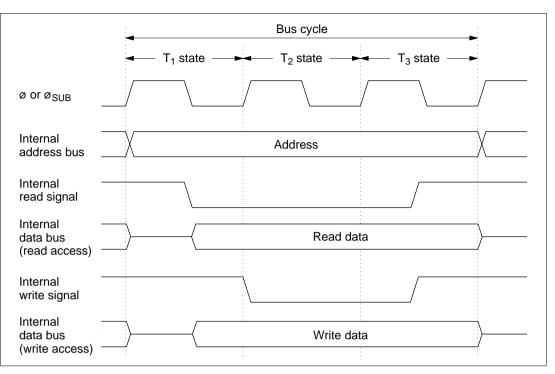

| 2.6   | Basic                  | Operational Timing                   | 40 |  |  |  |

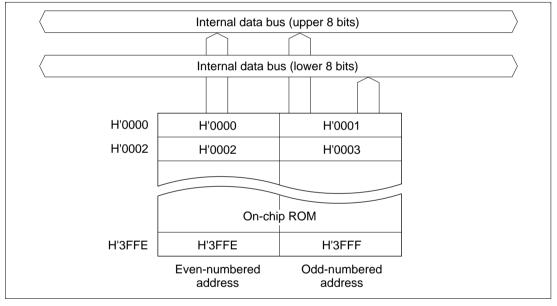

|       | 2.6.1                  | Access to On-Chip Memory (RAM, ROM)  | 40 |  |  |  |

|       | 2.6.2                  | Access to On-Chip Peripheral Modules | 41 |  |  |  |

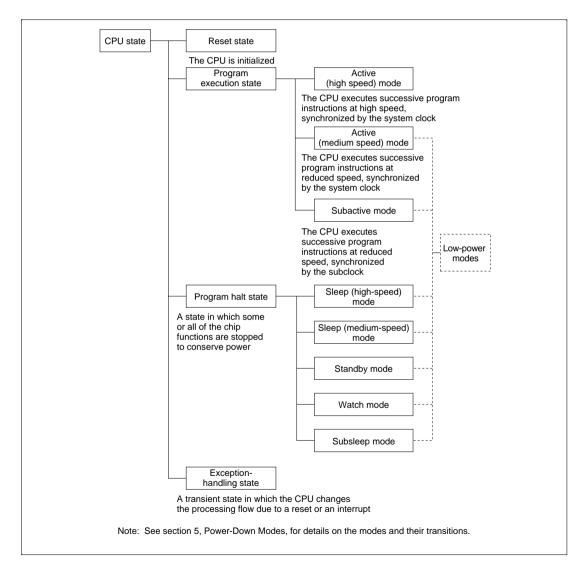

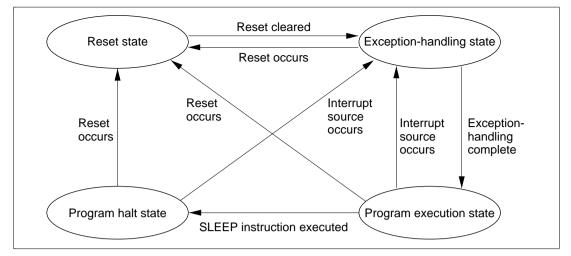

| 2.7   | CPU S                  | tates                                | 43 |  |  |  |

|       | 2.7.1                  | Overview                             | 43 |  |  |  |

|       | 2.7.2                  | Program Execution State              | 44 |  |  |  |

|       | 2.7.3                  | Program Halt State                   | 44 |  |  |  |

|       | 2.7.4                  | Exception-Handling State             | 44 |  |  |  |

| 2.8   | 8 Memory Map                                          |     |  |  |

|-------|-------------------------------------------------------|-----|--|--|

|       | 2.8.1 Memory Map                                      | 45  |  |  |

| 2.9   | Application Notes                                     | 48  |  |  |

|       | 2.9.1 Notes on Data Access                            | 48  |  |  |

|       | 2.9.2 Notes on Bit Manipulation                       | 50  |  |  |

|       | 2.9.3 Notes on Use of the EEPMOV Instruction          | 56  |  |  |

|       |                                                       |     |  |  |

| Secti | on 3 Exception Handling                               | 57  |  |  |

| 3.1   | Overview                                              | 57  |  |  |

| 3.2   | Reset                                                 | 57  |  |  |

|       | 3.2.1 Overview                                        | 57  |  |  |

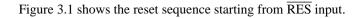

|       | 3.2.2 Reset Sequence                                  | 57  |  |  |

|       | 3.2.3 Interrupt Immediately after Reset               | 59  |  |  |

| 3.3   | Interrupts                                            | 59  |  |  |

|       | 3.3.1 Overview                                        | 59  |  |  |

|       | 3.3.2 Interrupt Control Registers                     | 61  |  |  |

|       | 3.3.3 External Interrupts                             | 70  |  |  |

|       | 3.3.4 Internal Interrupts                             | 71  |  |  |

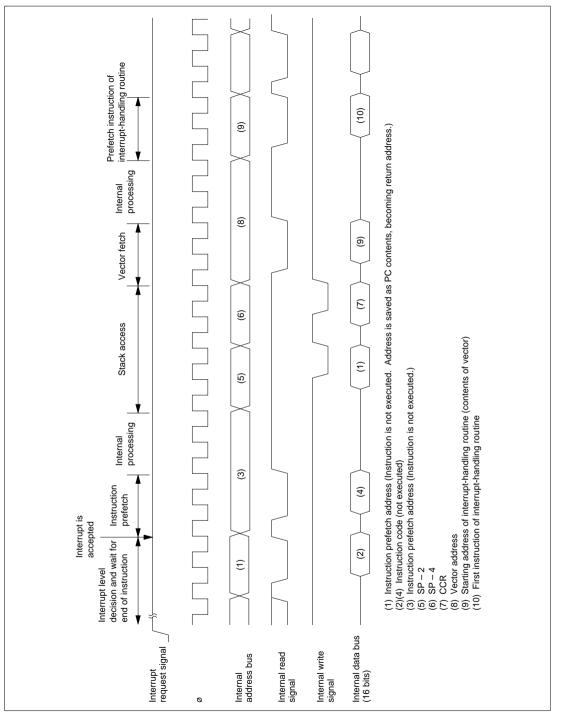

|       | 3.3.5 Interrupt Operations                            | 72  |  |  |

|       | 3.3.6 Interrupt Response Time                         | 77  |  |  |

| 3.4   | Application Notes                                     | 78  |  |  |

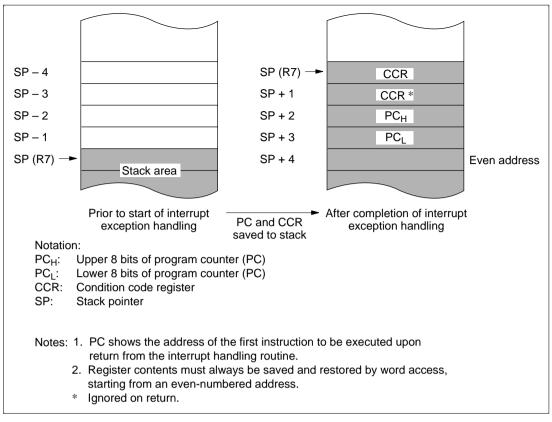

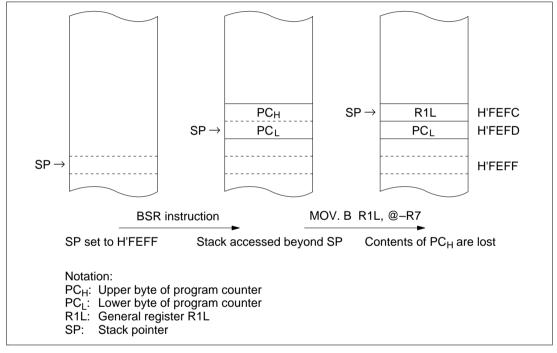

|       | 3.4.1 Notes on Stack Area Use                         | 78  |  |  |

|       | 3.4.2 Notes on Rewriting Port Mode Registers          | 79  |  |  |

|       | 3.4.3 Interrupt Request Flag Clearing Method          | 80  |  |  |

|       |                                                       |     |  |  |

| Secti | on 4 Clock Pulse Generators                           | 83  |  |  |

| 4.1   | Overview                                              | 83  |  |  |

|       | 4.1.1 Block Diagram                                   | 83  |  |  |

|       | 4.1.2 System Clock and Subclock                       | 83  |  |  |

| 4.2   | System Clock Generator                                | 84  |  |  |

| 4.3   | Subclock Generator                                    | 87  |  |  |

| 4.4   | Prescalers                                            | 89  |  |  |

| 4.5   | Note on Oscillators                                   | 90  |  |  |

|       | 4.5.1 Definition of Oscillation Settling Standby Time | 90  |  |  |

|       | 4.5.2 Notes on Use of Crystal Oscillator Element      |     |  |  |

|       | (Excluding Ceramic Oscillator Element)                | 92  |  |  |

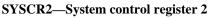

| Sect  | on 5 Power-Down Modes                                 | 02  |  |  |

|       |                                                       | 93  |  |  |

| 5.1   | Overview                                              | 93  |  |  |

| 5.0   | 5.1.1 System Control Registers                        | 96  |  |  |

| 5.2   | Sleep Mode                                            |     |  |  |

|       | 5.2.1 Transition to Sleep Mode                        |     |  |  |

|       | 5.2.2 Clearing Sleep Mode                             | 101 |  |  |

|       | 5.2.3    | Clock Frequency in Sleep (Medium-Speed) Mode                          | 102 |

|-------|----------|-----------------------------------------------------------------------|-----|

| 5.3   | Standby  | 7 Mode                                                                | 102 |

|       | 5.3.1    | Transition to Standby Mode                                            | 102 |

|       | 5.3.2    | Clearing Standby Mode                                                 | 102 |

|       | 5.3.3    | Oscillator Settling Time after Standby Mode is Cleared                | 103 |

|       | 5.3.4    | Standby Mode Transition and Pin States                                | 104 |

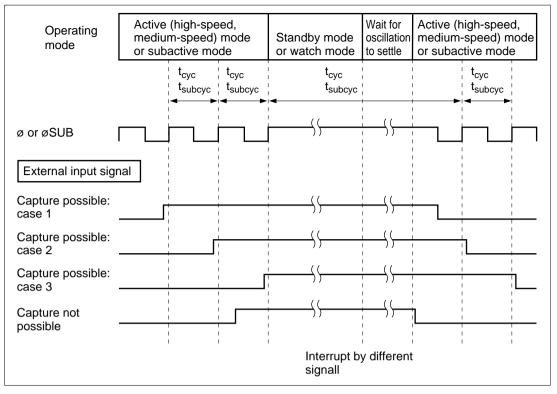

|       | 5.3.5    | Notes on External Input Signal Changes before/after Standby Mode      | 105 |

| 5.4   | Watch I  | Mode                                                                  | 107 |

|       | 5.4.1    | Transition to Watch Mode                                              | 107 |

|       | 5.4.2    | Clearing Watch Mode                                                   | 107 |

|       | 5.4.3    | Oscillator Settling Time after Watch Mode is Cleared                  | 107 |

|       | 5.4.4    | Notes on External Input Signal Changes before/after Watch Mode        | 107 |

| 5.5   | Subslee  | p Mode                                                                | 108 |

|       | 5.5.1    | Transition to Subsleep Mode                                           | 108 |

|       | 5.5.2    | Clearing Subsleep Mode                                                | 108 |

| 5.6   | Subactiv | ve Mode                                                               | 109 |

|       | 5.6.1    | Transition to Subactive Mode                                          | 109 |

|       | 5.6.2    | Clearing Subactive Mode                                               | 109 |

|       | 5.6.3    | Operating Frequency in Subactive Mode                                 | 109 |

| 5.7   | Active ( | (Medium-Speed) Mode                                                   | 110 |

|       | 5.7.1    | Transition to Active (Medium-Speed) Mode                              | 110 |

|       | 5.7.2    | Clearing Active (Medium-Speed) Mode                                   | 110 |

|       | 5.7.3    | Operating Frequency in Active (Medium-Speed) Mode                     | 110 |

| 5.8   | Direct 7 | Fransfer                                                              | 111 |

|       | 5.8.1    | Overview of Direct Transfer                                           | 111 |

|       | 5.8.2    | Direct Transition Times                                               | 112 |

|       | 5.8.3    | Notes on External Input Signal Changes before/after Direct Transition | 114 |

| 5.9   | Module   | Standby Mode                                                          | 115 |

|       | 5.9.1    | Setting Module Standby Mode                                           | 115 |

|       | 5.9.2    | Clearing Module Standby Mode                                          | 115 |

|       |          |                                                                       |     |

| Secti | on 6 F   | ROM                                                                   | 117 |

| 6.1   | Overvie  | ?W                                                                    | 117 |

|       | 6.1.1    | Block Diagram                                                         | 117 |

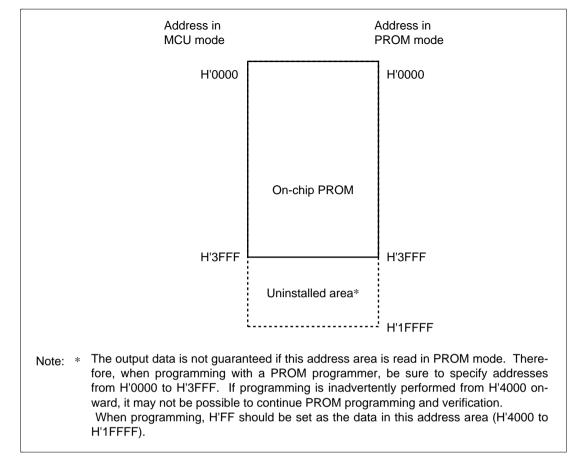

| 6.2   | H8/3802  | 2 PROM Mode                                                           | 118 |

|       | 6.2.1    | Setting to PROM Mode                                                  | 118 |

|       | 6.2.2    | Socket Adapter Pin Arrangement and Memory Map                         | 118 |

| 6.3   | H8/3802  | 2 Programming                                                         |     |

|       | 6.3.1    | Writing and Verifying                                                 |     |

|       | 6.3.2    | Programming Precautions                                               |     |

| 6.4   |          | ity of Programmed Data                                                |     |

|       |          |                                                                       |     |

| Secti | on 7   | RAM                                    | 129 |

|-------|--------|----------------------------------------|-----|

| 7.1   | Overv  | iew                                    | 129 |

|       | 7.1.1  | Block Diagram                          | 129 |

|       |        |                                        |     |

| Secti | on 8   | I/O Ports                              | 131 |

| 8.1   | Overv  | iew                                    | 131 |

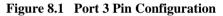

| 8.2   | Port 3 |                                        | 133 |

|       | 8.2.1  | Overview                               | 133 |

|       | 8.2.2  | Register Configuration and Description | 133 |

|       | 8.2.3  | Pin Functions                          | 137 |

|       | 8.2.4  | Pin States                             | 138 |

|       | 8.2.5  | MOS Input Pull-Up                      | 138 |

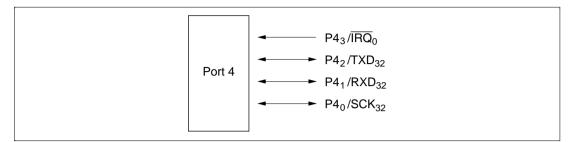

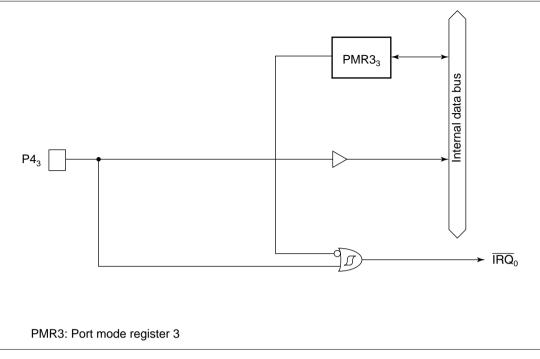

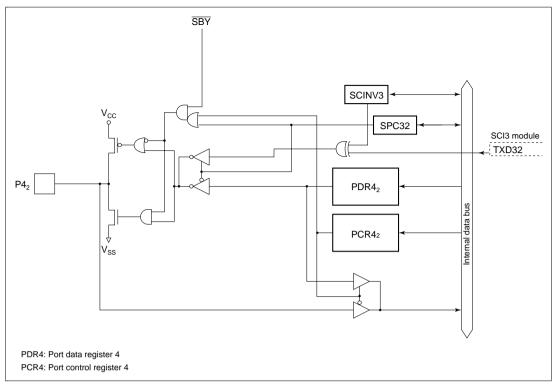

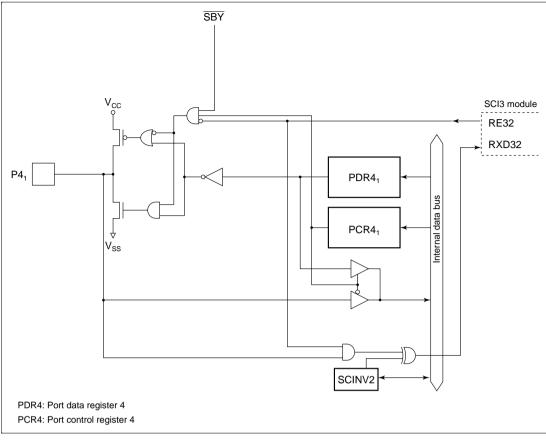

| 8.3   | Port 4 |                                        | 139 |

|       | 8.3.1  | Overview                               | 139 |

|       | 8.3.2  | Register Configuration and Description | 139 |

|       | 8.3.3  | Pin Functions                          | 141 |

|       | 8.3.4  | Pin States                             | 142 |

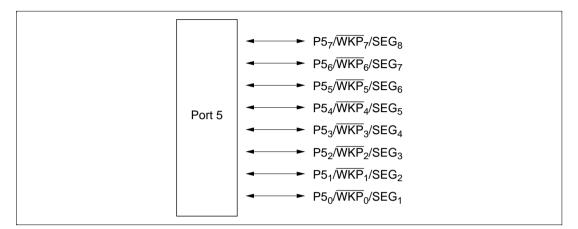

| 8.4   | Port 5 |                                        | 143 |

|       | 8.4.1  | Overview                               | 143 |

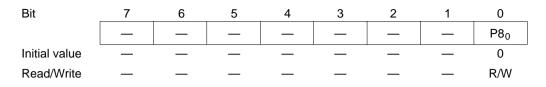

|       | 8.4.2  | Register Configuration and Description | 143 |

|       | 8.4.3  | Pin Functions                          | 146 |

|       | 8.4.4  | Pin States                             | 147 |

|       | 8.4.5  | MOS Input Pull-Up                      | 147 |

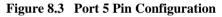

| 8.5   | Port 6 |                                        | 148 |

|       | 8.5.1  | Overview                               | 148 |

|       | 8.5.2  | Register Configuration and Description | 148 |

|       | 8.5.3  | Pin Functions                          | 150 |

|       | 8.5.4  | Pin States                             | 151 |

|       | 8.5.5  | MOS Input Pull-Up                      | 151 |

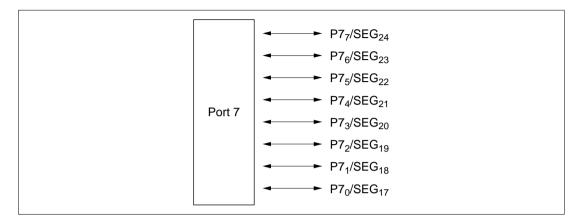

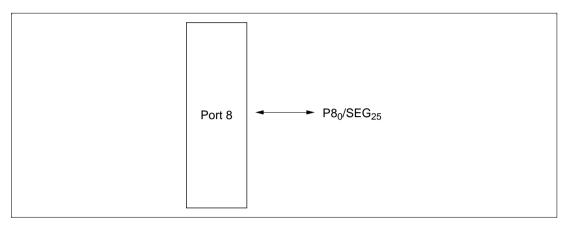

| 8.6   | Port 7 |                                        | 152 |

|       | 8.6.1  | Overview                               | 152 |

|       | 8.6.2  | Register Configuration and Description | 152 |

|       | 8.6.3  | Pin Functions                          | 154 |

|       | 8.6.4  | Pin States                             | 154 |

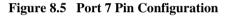

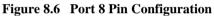

| 8.7   | Port 8 |                                        | 155 |

|       | 8.7.1  | Overview                               | 155 |

|       | 8.7.2  | Register Configuration and Description | 155 |

|       | 8.7.3  | Pin Functions                          | 157 |

|       | 8.7.4  | Pin States                             | 157 |

| 8.8   | Port 9 |                                        | 158 |

|       | 8.8.1  | Overview                               | 158 |

|       | 8.8.2  | Register Configuration and Description | 158 |

|       | 8.8.3  | Pin Functions                          | 160 |

|       | 8.8.4   | Pin States                                           | 160 |

|-------|---------|------------------------------------------------------|-----|

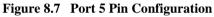

| 8.9   | Port A  |                                                      | 161 |

|       | 8.9.1   | Overview                                             | 161 |

|       | 8.9.2   | Register Configuration and Description               | 161 |

|       | 8.9.3   | Pin Functions                                        | 163 |

|       | 8.9.4   | Pin States                                           | 164 |

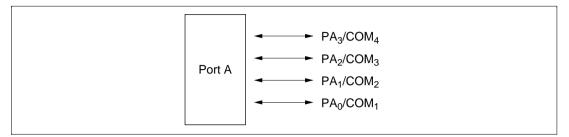

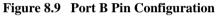

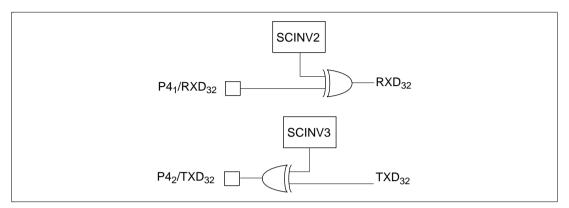

| 8.10  | Port B  |                                                      | 165 |

|       | 8.10.1  | Overview                                             | 165 |

|       | 8.10.2  | Register Configuration and Description               | 165 |

|       | 8.10.3  | Pin Functions                                        | 167 |

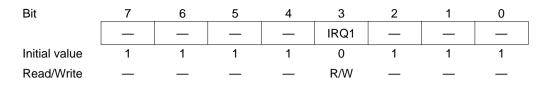

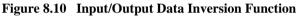

| 8.11  | Input/C | Output Data Inversion Function                       | 168 |

|       | 8.11.1  | Overview                                             | 168 |

|       | 8.11.2  | Register Configuration and Descriptions              | 168 |

|       | 8.11.3  | Note on Modification of Serial Port Control Register | 169 |

| 8.12  | Applic  | ation Note                                           | 170 |

|       | 8.12.1  | How to Handle an Unused Pin                          | 170 |

|       |         |                                                      |     |

| Secti | on 9 '  | Timers                                               | 171 |

| 9.1   | Overvi  | ew                                                   | 171 |

| 9.2   | Timer . | Α                                                    | 172 |

|       | 9.2.1   | Overview                                             | 172 |

|       | 9.2.2   | Register Descriptions                                | 174 |

|       | 9.2.3   | Timer Operation                                      | 177 |

|       | 9.2.4   | Timer A Operation States                             | 177 |

|       | 9.2.5   | Application Note                                     | 178 |

| 9.3   | Timer   | F                                                    | 178 |

|       | 9.3.1   | Overview                                             | 178 |

|       | 9.3.2   | Register Descriptions                                | 181 |

|       | 9.3.3   | CPU Interface                                        | 189 |

|       | 9.3.4   | Operation                                            | 192 |

|       | 9.3.5   | Application Notes                                    |     |

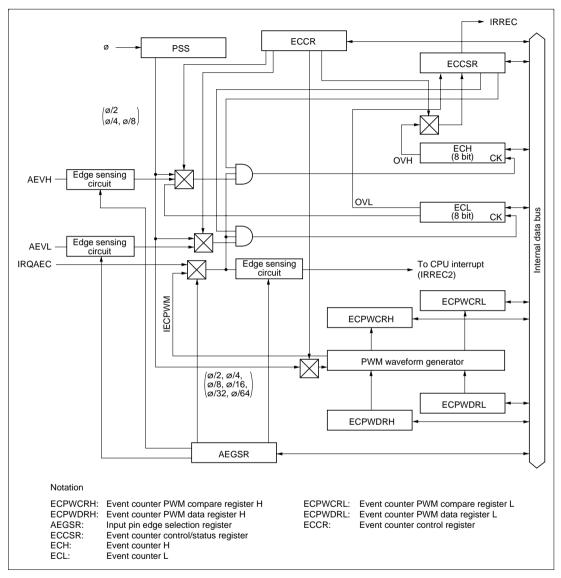

| 9.4   | Asynch  | rronous Event Counter (AEC)                          | 198 |

|       | 9.4.1   | Overview                                             | 198 |

|       | 9.4.2   | Register Configurations                              | 201 |

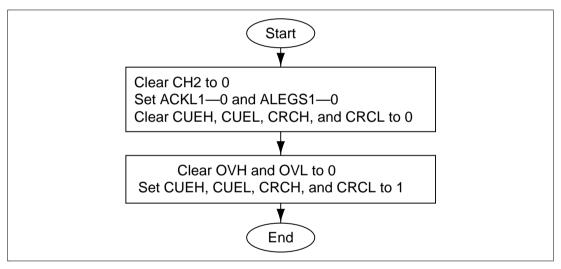

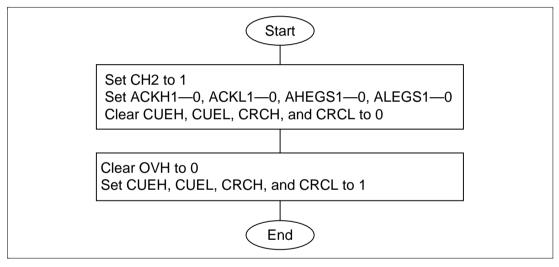

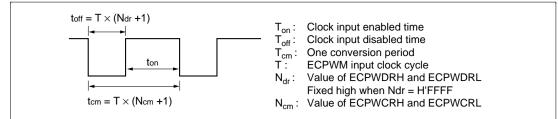

|       | 9.4.3   | Operation                                            | 210 |

|       | 9.4.4   | Asynchronous Event Counter Operation Modes           | 214 |

|       | 9.4.5   | Application Notes                                    | 215 |

| ~     |         |                                                      |     |

|       | on 10   | Serial Communication Interface                       |     |

| 10.1  |         | ew                                                   |     |

|       |         | Features                                             |     |

|       |         | Block diagram                                        |     |

|       | 10.1.3  | Pin configuration                                    | 220 |

|       |          | Register configuration                      |     |

|-------|----------|---------------------------------------------|-----|

| 10.2  | Registe  | r Descriptions                              | 221 |

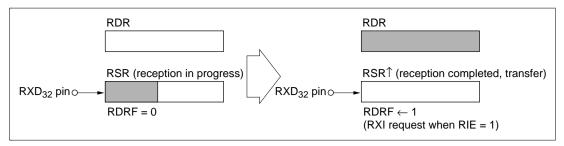

|       | 10.2.1   | Receive shift register (RSR)                | 221 |

|       | 10.2.2   | Receive data register (RDR)                 | 221 |

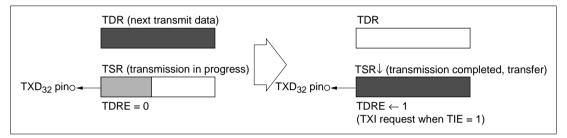

|       | 10.2.3   | Transmit shift register (TSR)               | 222 |

|       | 10.2.4   | Transmit data register (TDR)                | 222 |

|       | 10.2.5   | Serial mode register (SMR)                  | 223 |

|       | 10.2.6   | Serial control register 3 (SCR3)            | 226 |

|       | 10.2.7   | Serial status register (SSR)                | 230 |

|       | 10.2.8   | Bit rate register (BRR)                     | 234 |

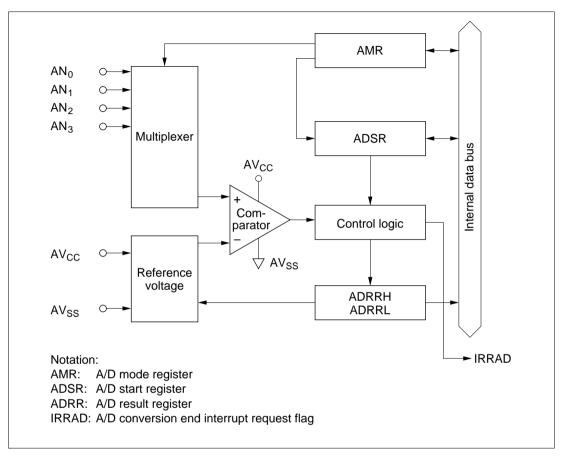

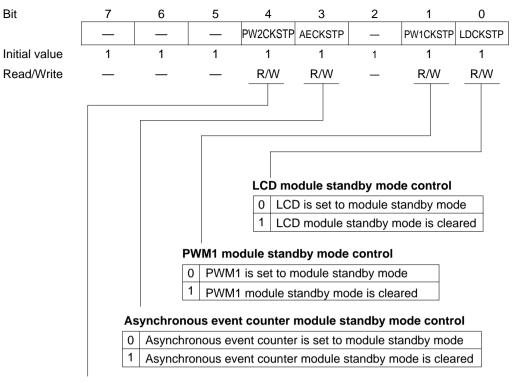

|       | 10.2.9   | Clock stop register 1 (CKSTPR1)             | 239 |

|       | 10.2.10  | Serial Port Control Register (SPCR)         | 240 |

| 10.3  | Operati  | on                                          | 241 |

|       | 10.3.1   | Overview                                    | 241 |

|       | 10.3.2   | Operation in Asynchronous Mode              | 245 |

|       | 10.3.3   | Operation in Synchronous Mode               | 254 |

|       | 10.3.4   | Multiprocessor Communication Function       | 261 |

| 10.4  | Interrup | ots                                         | 268 |

| 10.5  | Applica  | tion Notes                                  | 269 |

|       |          |                                             |     |

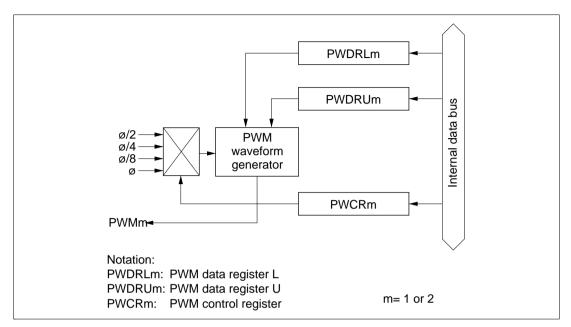

| Secti | on 11    | 10-Bit PWM                                  | 275 |

| 11.1  | Overvie  | 2W                                          | 275 |

|       | 11.1.1   | Features                                    | 275 |

|       | 11.1.2   | Block Diagram                               | 276 |

|       | 11.1.3   | Pin Configuration                           | 276 |

|       | 11.1.4   | Register Configuration                      | 277 |

| 11.2  | Registe  | r Descriptions                              | 278 |

|       | 11.2.1   | PWM Control Register (PWCRm)                | 278 |

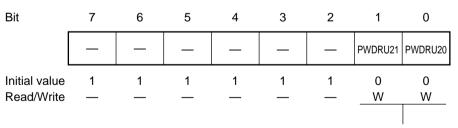

|       | 11.2.2   | PWM Data Registers U and L (PWDRUm, PWDRLm) | 279 |

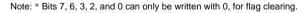

|       | 11.2.3   | Clock Stop Register 2 (CKSTPR2)             | 279 |

| 11.3  | Operati  | on                                          | 281 |

|       | 11.3.1   | Operation                                   | 281 |

|       | 11.3.2   | PWM Operation Modes                         | 282 |

|       |          |                                             |     |

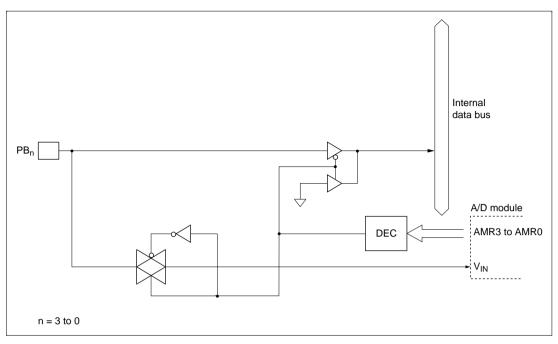

| Secti | on 12    | A/D Converter                               | 283 |

| 12.1  | Overvie  | 2W                                          | 283 |

|       | 12.1.1   | Features                                    | 283 |

|       | 12.1.2   | Block Diagram                               | 284 |

|       | 12.1.3   | Pin Configuration                           | 285 |

|       | 12.1.4   | Register Configuration                      | 285 |

| 12.2  | Registe  | r Descriptions                              | 286 |

|       | 12.2.1   | A/D Result Registers (ADRRH, ADRRL)         | 286 |

|       | 12.2.2   | A/D Mode Register (AMR)                     | 286 |

|       |          |                                             |     |

|       | 12.2.3   | A/D Start Register (ADSR)                | 288 |

|-------|----------|------------------------------------------|-----|

|       | 12.2.4   | Clock Stop Register 1 (CKSTPR1)          | 289 |

| 12.3  | Operati  | on                                       | 290 |

|       | 12.3.1   | A/D Conversion Operation                 | 290 |

|       | 12.3.2   | A/D Converter Operation Modes            | 290 |

| 12.4  | Interruj | pts                                      | 291 |

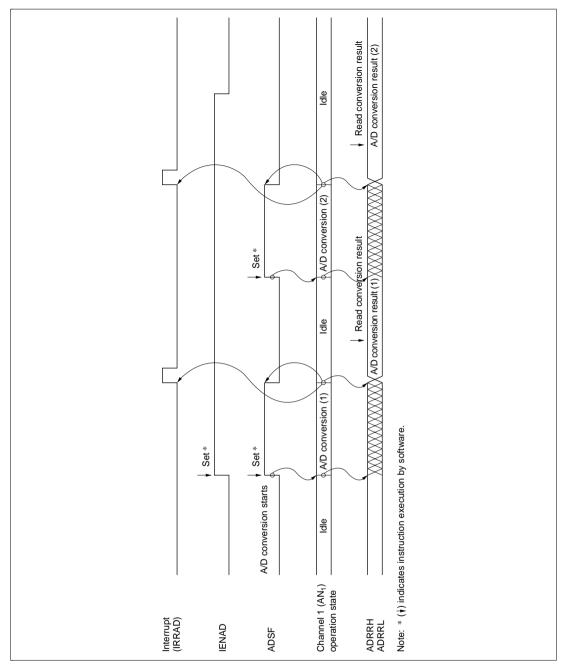

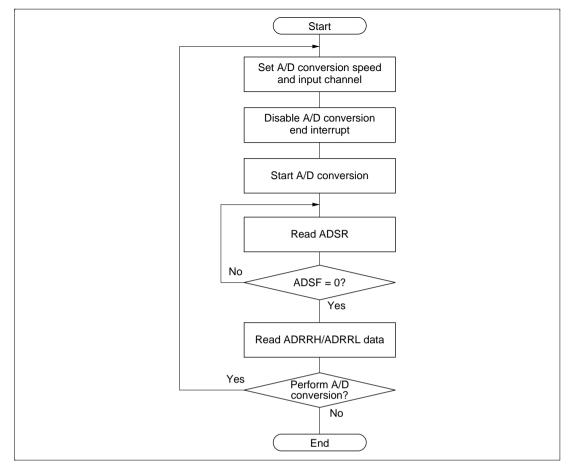

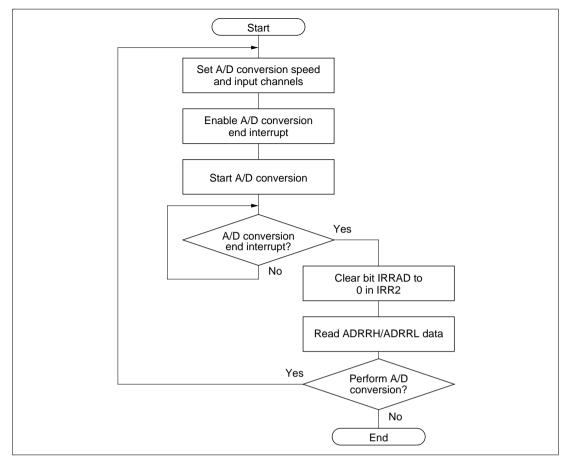

| 12.5  | Typica   | Use                                      | 291 |

| 12.6  | Applica  | ation Notes                              | 294 |

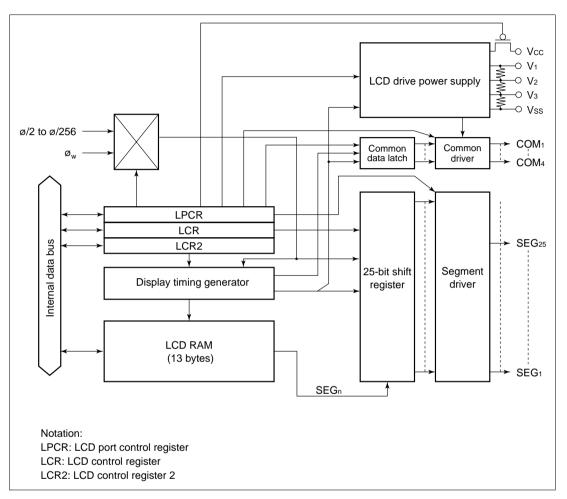

| Secti | on 13    | LCD Controller/Driver                    | 295 |

| 13.1  | Overvi   | ew                                       | 295 |

|       | 13.1.1   | Features                                 | 295 |

|       | 13.1.2   | Block Diagram                            | 296 |

|       |          | Pin Configuration                        |     |

|       |          | Register Configuration                   |     |

| 13.2  |          | r Descriptions                           |     |

|       | 13.2.1   | LCD Port Control Register (LPCR)         | 298 |

|       | 13.2.2   | LCD Control Register (LCR)               | 300 |

|       |          | LCD Control Register 2 (LCR2)            |     |

|       | 13.2.4   | Clock Stop Register 2 (CKSTPR2)          | 303 |

| 13.3  |          | on                                       |     |

|       | 13.3.1   | Settings up to LCD Display               | 304 |

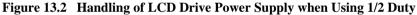

|       | 13.3.2   | Relationship between LCD RAM and Display | 306 |

|       | 13.3.3   | Operation in Power-Down Modes            | 311 |

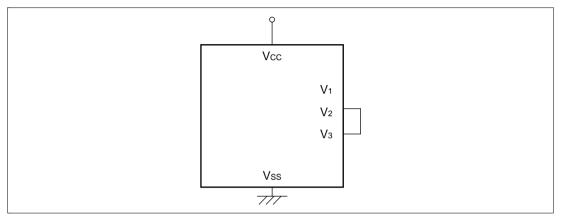

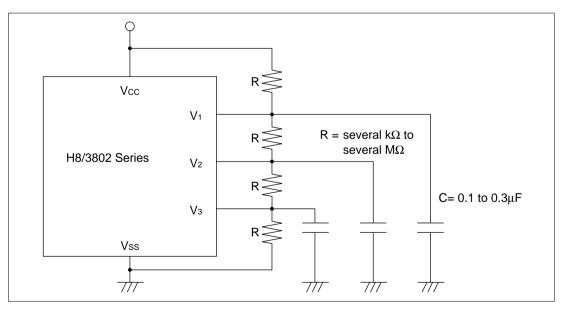

|       | 13.3.4   | Boosting the LCD Drive Power Supply      | 312 |

| Secti | on 14    | Electrical Characteristics               | 313 |

| 14.1  |          | 2 Series Absolute Maximum Ratings        |     |

| 14.2  | H8/380   | 2 Series Electrical Characteristics.     | 314 |

|       | 14.2.1   | Power Supply Voltage and Operating Range | 314 |

|       |          | DC Characteristics                       |     |

|       | 14.2.3   | AC Characteristics                       | 322 |

|       | 14.2.4   | A/D Converter Characteristics            | 325 |

|       | 14.2.5   | LCD Characteristics                      | 327 |

| 14.3  | Operati  | on Timing                                | 328 |

| 14.4  | Output   | Load Circuit                             | 330 |

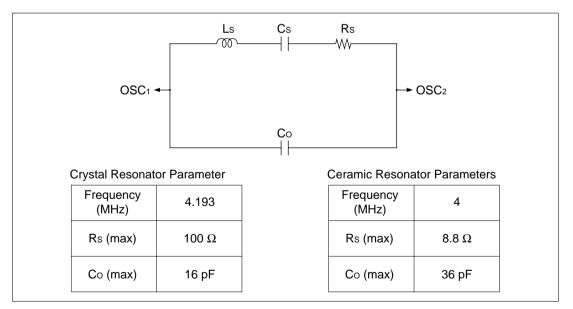

| 14.5  | Resona   | tor Equivalent Circuit                   | 330 |

| 14.6  | Usage 1  | Note                                     | 331 |

| App   | endix A  | CPU Instruction Set                      | 333 |

| A.1   |          | tions                                    |     |

| A.2   | Operati  | on Code Map                              | 341 |

| A.3   | -        | r of Execution States                    |     |

| Appe<br>B.1<br>B.2 | endix B Internal I/O Registers<br>Addresses<br>Functions | 349 |

|--------------------|----------------------------------------------------------|-----|

| Appe               | endix C I/O Port Block Diagrams                          | 397 |

| C.1                | Block Diagrams of Port 3                                 |     |

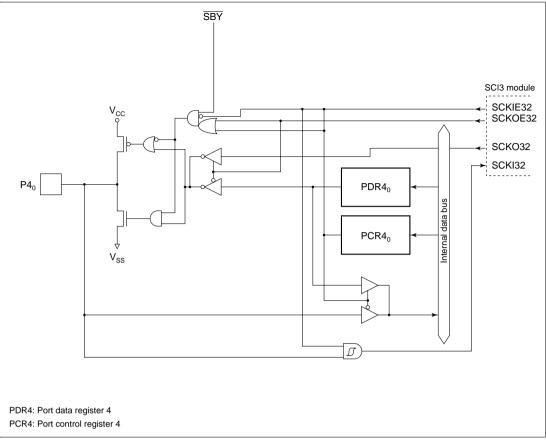

| C.2                | Block Diagrams of Port 4                                 |     |

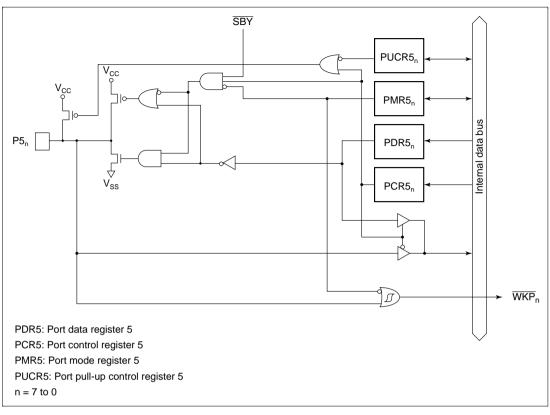

| C.3                | Block Diagram of Port 5                                  |     |

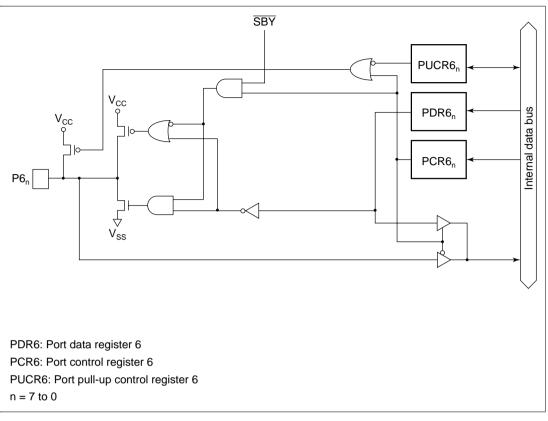

| C.4                | Block Diagram of Port 6                                  |     |

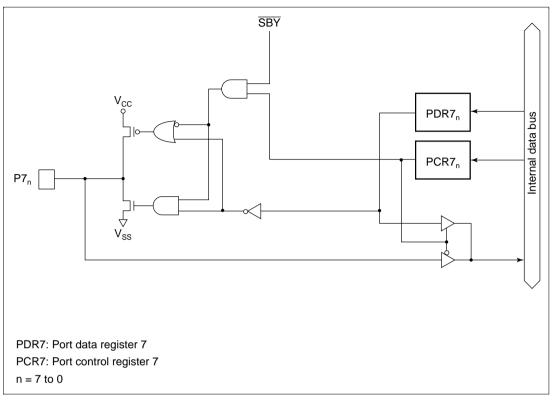

| C.5                | Block Diagram of Port 7                                  |     |

| C.6                | Block Diagrams of Port 8                                 | 408 |

| C.7                | Block Diagrams of Port 9                                 |     |

| C.8                | Block Diagram of Port A                                  |     |

| C.9                | Block Diagram of Port B                                  | 411 |

| Appe               | endix D Port States in the Different Processing States   | 412 |

| Appe               | endix E List of Product Codes                            | 413 |

| Appe               | endix F Package Dimensions                               | 414 |

## Section 1 Overview

#### 1.1 Overview

The H8/300L Series is a series of single-chip microcomputers (MCU: microcomputer unit), built around the high-speed H8/300L CPU and equipped with peripheral system functions on-chip.

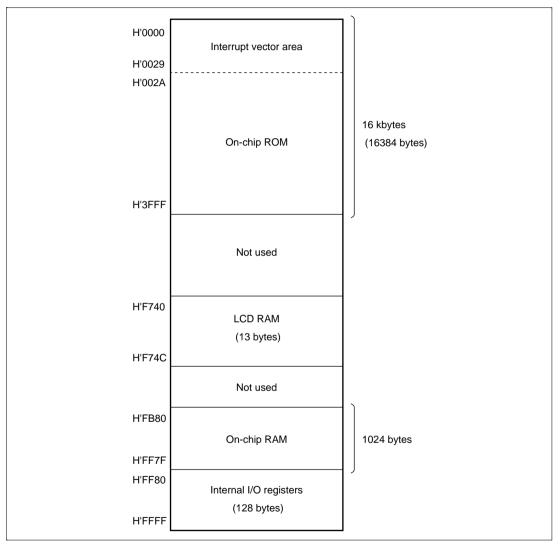

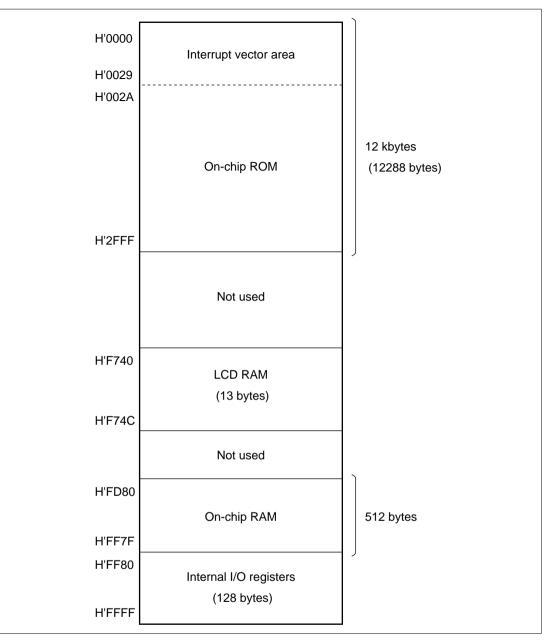

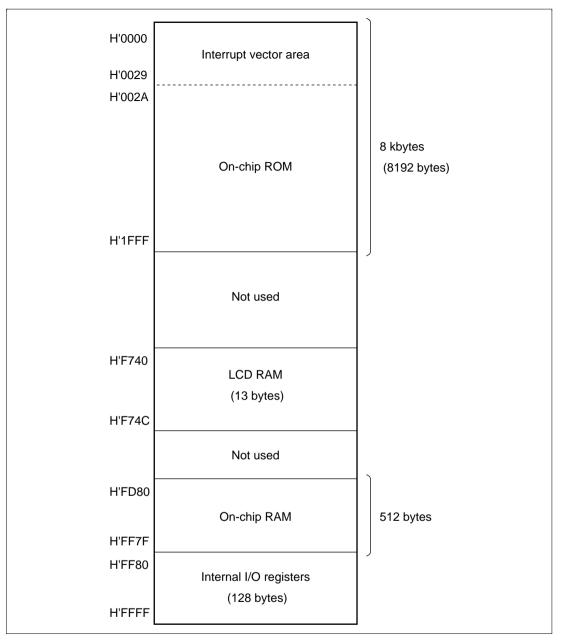

Within the H8/300L Series, the H8/3802 Series comprises single-chip microcomputers equipped with a controller/driver. Other on-chip peripheral functions include three timers, a two-channel 10-bit pulse width modulator (PWM), a serial communication interface, and an A/D converter. Together, these functions make the H8/3800 Series ideally suited for embedded applications in systems requiring low power consumption and LCD display. Models in the H8/3802 Series are the H8/3802, with on-chip 16-kbyte ROM and 1-kbyte RAM, the H8/3801, with 12-kbyte ROM and 512 byte RAM, and the H8/3800, with 8-kbyte ROM and 512 byte RAM.

The H8/3802 is also available in a ZTAT<sup>TM\*</sup> version with on-chip PROM which can be programmed as required by the user.

Table 1.1 summarizes the features of the H8/3802 Series.

Note: \* ZTAT (Zero Turn Around Time) is a trademark of Hitachi, Ltd.

#### Table 1.1 Features

| Item                   | Specification                                                                                                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| CPU                    | High-speed H8/300L CPU                                                                                                |

|                        | General-register architecture                                                                                         |

|                        | General registers: Sixteen 8-bit registers (can be used as eight 16-bit registers)                                    |

|                        | Operating speed                                                                                                       |

|                        | — Max. operating speed: 8 MHz                                                                                         |

|                        | — Add/subtract: 0.25 μs (operating at 8 MHz)                                                                          |

|                        | — Multiply/divide: 1.75 μs (operating at 8 MHz)                                                                       |

|                        | <ul> <li>Can run on 32.768 kHz or 38.4 kHz subclock</li> </ul>                                                        |

|                        | Instruction set compatible with H8/300 CPU                                                                            |

|                        | <ul> <li>Instruction length of 2 bytes or 4 bytes</li> </ul>                                                          |

|                        | <ul> <li>Basic arithmetic operations between registers</li> </ul>                                                     |

|                        | <ul> <li>MOV instruction for data transfer between memory and registers</li> </ul>                                    |

|                        | Typical instructions                                                                                                  |

|                        | — Multiply (8 bits $\times$ 8 bits)                                                                                   |

|                        | — Divide (16 bits ÷ 8 bits)                                                                                           |

|                        | — Bit accumulator                                                                                                     |

|                        | Register-indirect designation of bit position                                                                         |

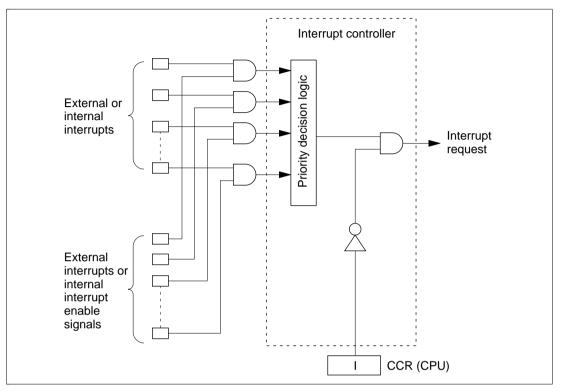

| Interrupts             | 18 interrupt sources                                                                                                  |

|                        | • 11 external interrupt sources (IRQ <sub>1</sub> , IRQ <sub>0</sub> , WKP <sub>7</sub> to WKP <sub>0</sub> , IRQAEC) |

|                        | 7 internal interrupt sources                                                                                          |

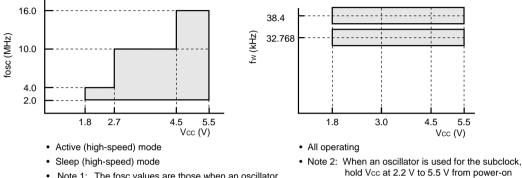

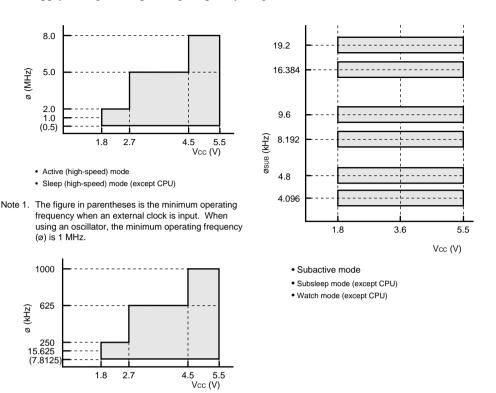

| Clock pulse generators | Two on-chip clock pulse generators                                                                                    |

|                        | System clock pulse generator: 1.0 to 16 MHz                                                                           |

|                        | Subclock pulse generator: 32.768 kHz, 38.4 kHz                                                                        |

| Power-down modes       | Seven power-down modes                                                                                                |

|                        | Sleep (high-speed) mode                                                                                               |

|                        | Sleep (medium-speed) mode                                                                                             |

|                        | Standby mode                                                                                                          |

|                        | Watch mode                                                                                                            |

|                        | Subsleep mode                                                                                                         |

|                        | Subactive mode                                                                                                        |

|                        | Active (medium-speed) mode                                                                                            |

| Item                 | Specification                                                                                                                                                                       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory               | Large on-chip memory                                                                                                                                                                |

|                      | H8/3802: 16-kbyte ROM, 1-kbyte RAM                                                                                                                                                  |

|                      | • H8/3801: 12-kbyte ROM, 512 byte RAM                                                                                                                                               |

|                      | • H8/3800: 8-kbyte ROM, 512 byte RAM                                                                                                                                                |

| I/O ports            | 50 pins                                                                                                                                                                             |

|                      | • 39 I/O pins                                                                                                                                                                       |

|                      | 5 input pins                                                                                                                                                                        |

|                      | 6 output pins                                                                                                                                                                       |

| Timers               | Three on-chip timers                                                                                                                                                                |

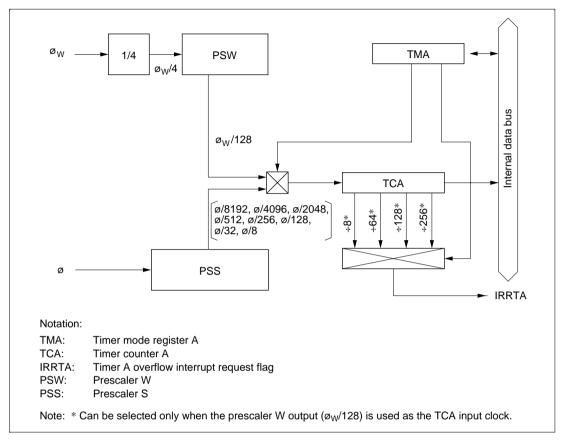

|                      | Timer A: 8-bit timer                                                                                                                                                                |

|                      | Count-up timer with selection of eight internal clock signals divided from the system clock ( $\emptyset$ )* and four clock signals divided from the watch clock ( $\emptyset_w$ )* |

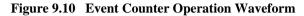

|                      | Asynchronous event counter: 16-bit timer                                                                                                                                            |

|                      | <ul> <li>Count-up timer able to count asynchronous external events<br/>independently of the MCU's internal clocks</li> </ul>                                                        |

|                      | Asynchronous external events can be counted (both rising and falling edge detection possible)                                                                                       |

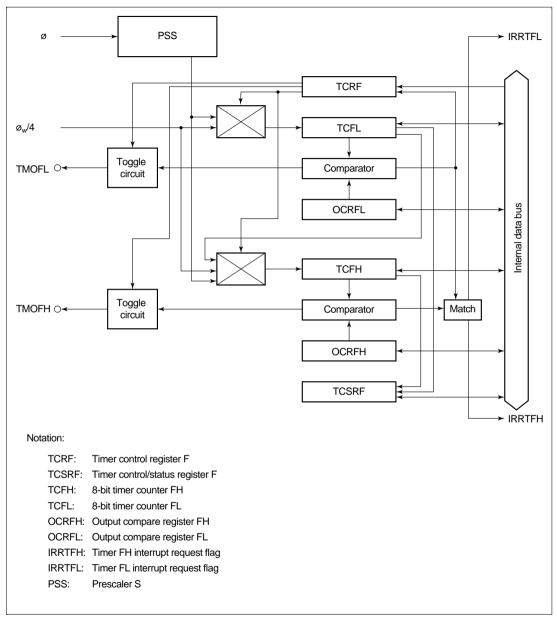

|                      | Timer F: 16-bit timer                                                                                                                                                               |

|                      | <ul> <li>Can be used as two independent 8-bit timers</li> </ul>                                                                                                                     |

|                      | <ul> <li>Count-up by an event input from the four internal clocks</li> </ul>                                                                                                        |

|                      | <ul> <li>Provision for toggle output by means of compare-match function</li> </ul>                                                                                                  |

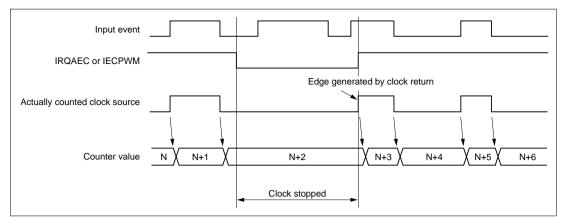

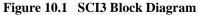

| Serial communication | SCI3: 8-bit synchronous/asynchronous serial interface                                                                                                                               |

| interface            | Incorporates multiprocessor communication function                                                                                                                                  |

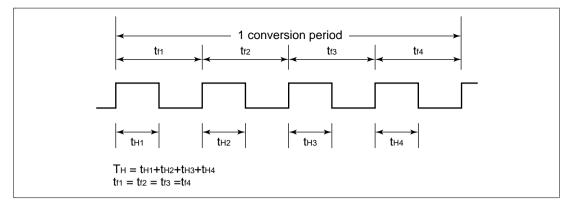

| 10-bit PWM           | Pulse-division PWM output for reduced ripple                                                                                                                                        |

|                      | <ul> <li>Can be used as a 10-bit D/A converter by connecting to an external<br/>low-pass filter.</li> </ul>                                                                         |

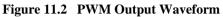

| A/D converter        | Successive approximations using a resistance ladder                                                                                                                                 |

|                      | 4-channel analog input pins                                                                                                                                                         |

|                      | Conversion time: 31/ø or 62/ø per channel                                                                                                                                           |

| Specification                                                                         |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

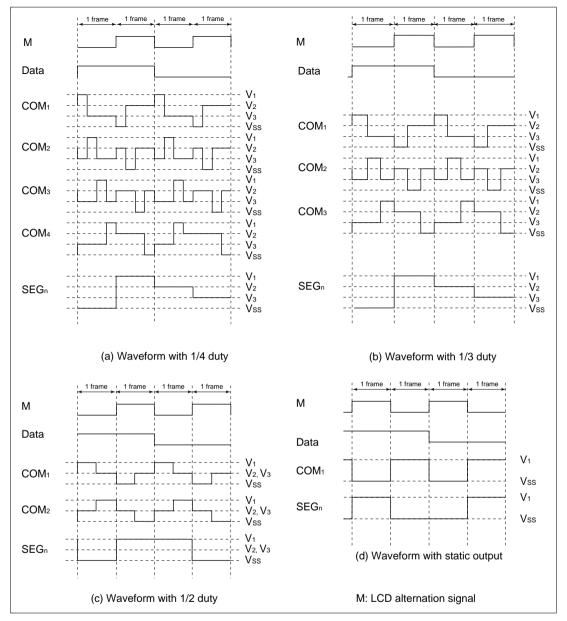

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| LCD controller/driver equipped with a maximum of 25 segment pins and four common pins |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| • Choice of four duty cycles (static, 1/2, 1/3, or 1/4)                               |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Segment pin                                                                           | s can be switched                                                                                                                                                           | to general-purpose port fu                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nction in 4-bit units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

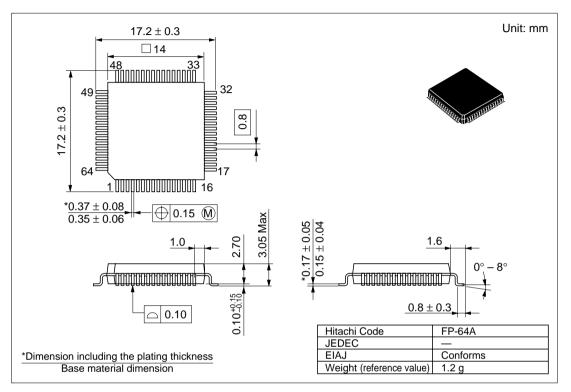

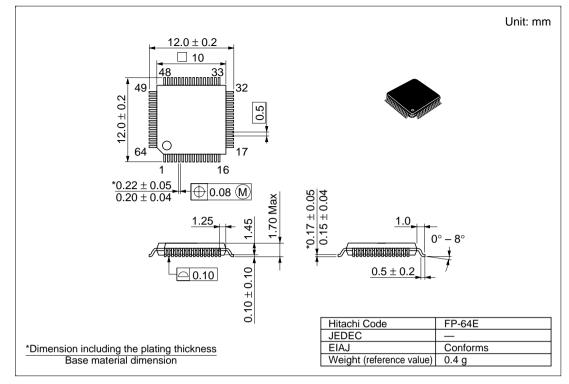

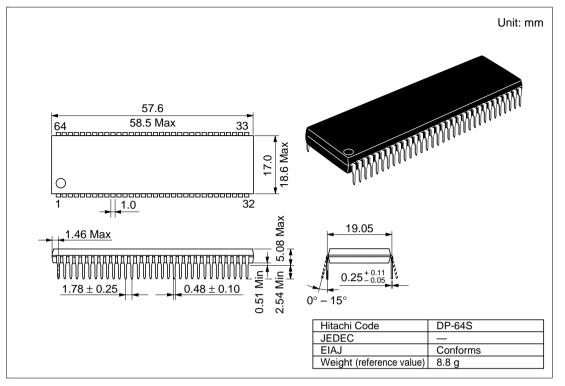

| Produ                                                                                 | ct Code                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Mask ROM<br>Version                                                                   | ZTAT Version                                                                                                                                                                | –<br>Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ROM/RAM Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| HD6433802H                                                                            | HD6473802H                                                                                                                                                                  | 64-pin QFP (FP-64A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ROM 16 kbytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| HD6433802FP                                                                           | HD6473802FP                                                                                                                                                                 | 8802FP 64-pin LQFP (FP-64E) RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| HD6433802P                                                                            | HD6473802P                                                                                                                                                                  | 64-pin DILP (DP-64S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

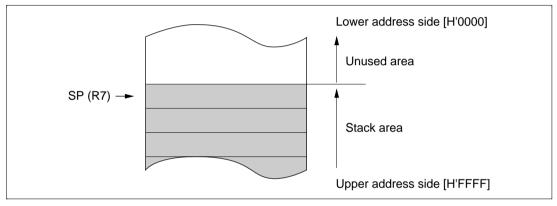

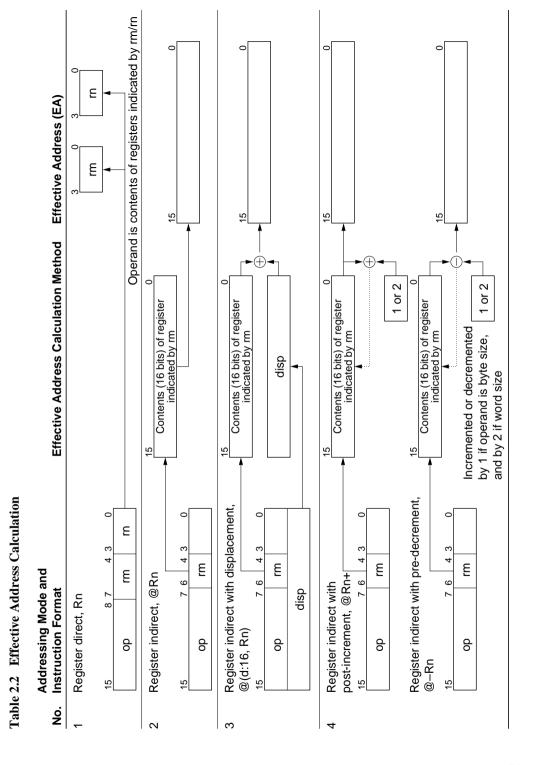

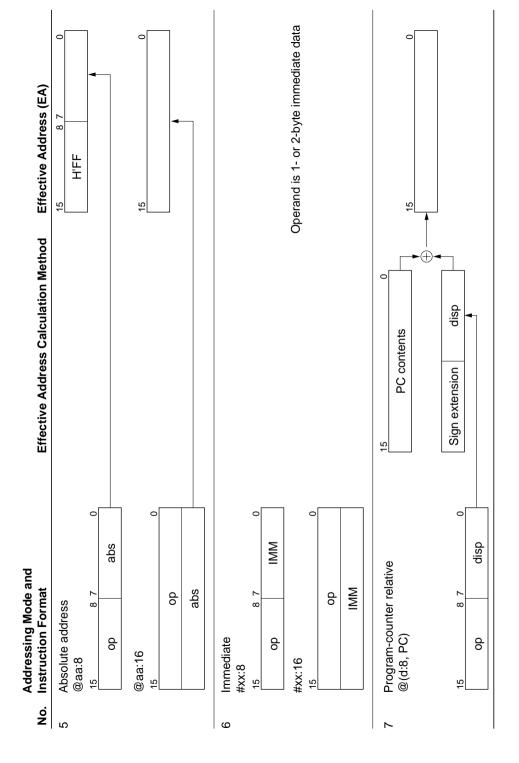

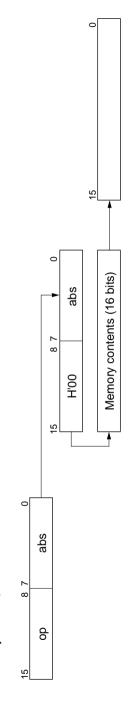

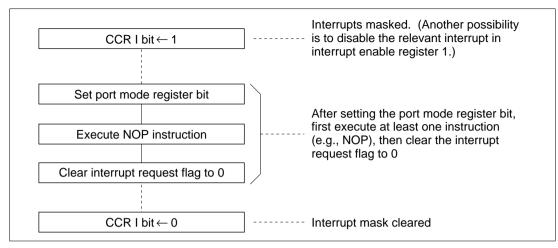

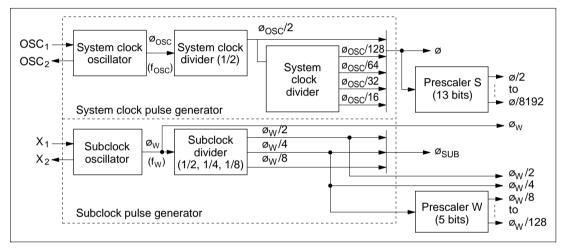

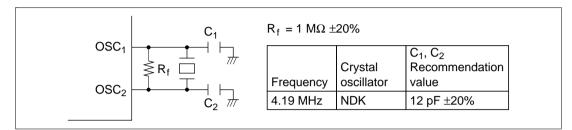

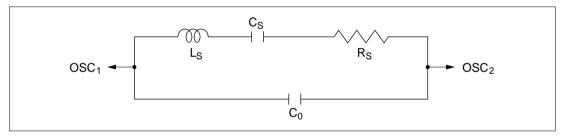

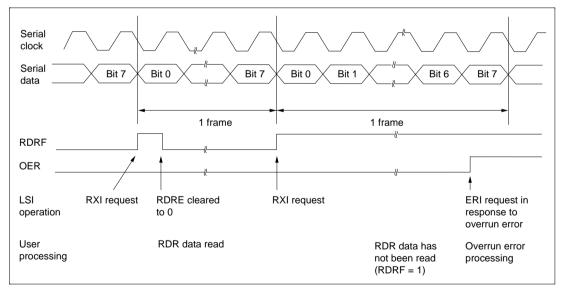

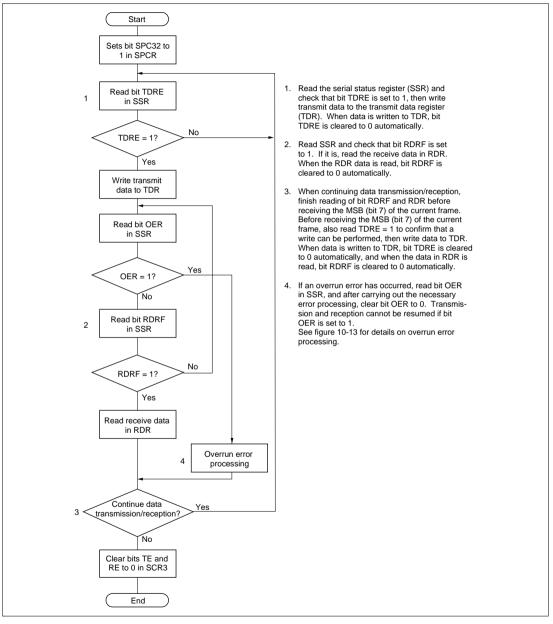

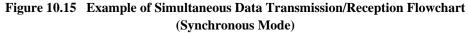

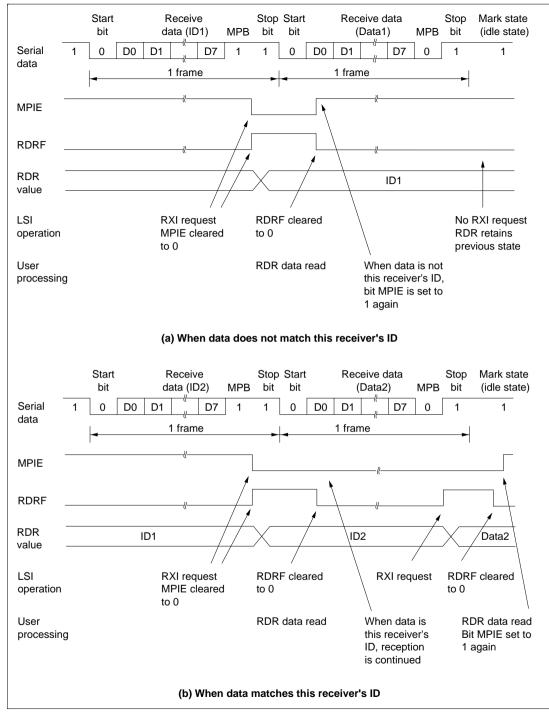

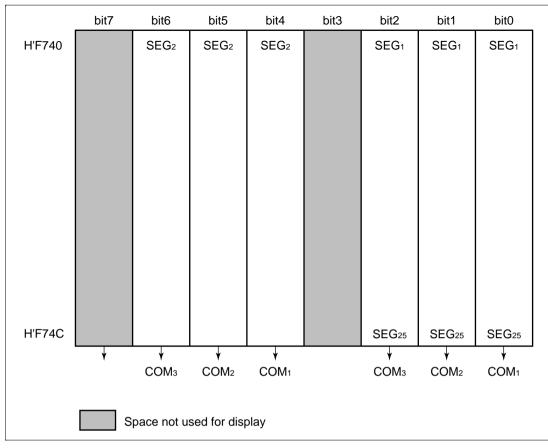

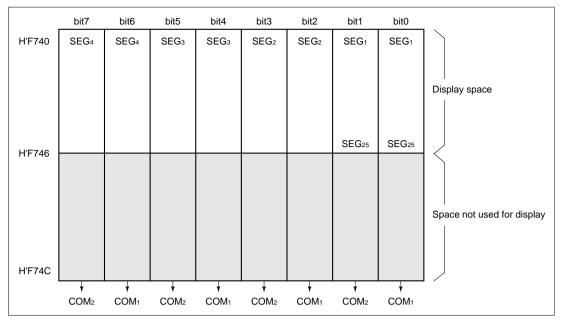

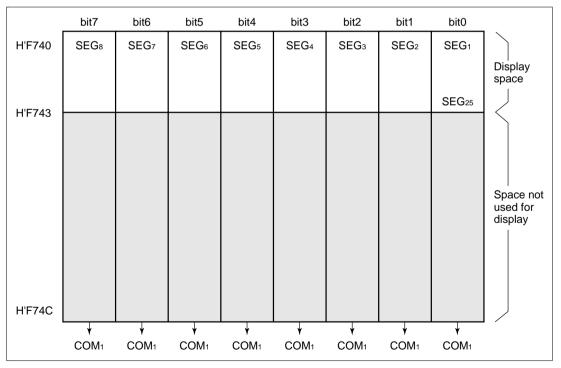

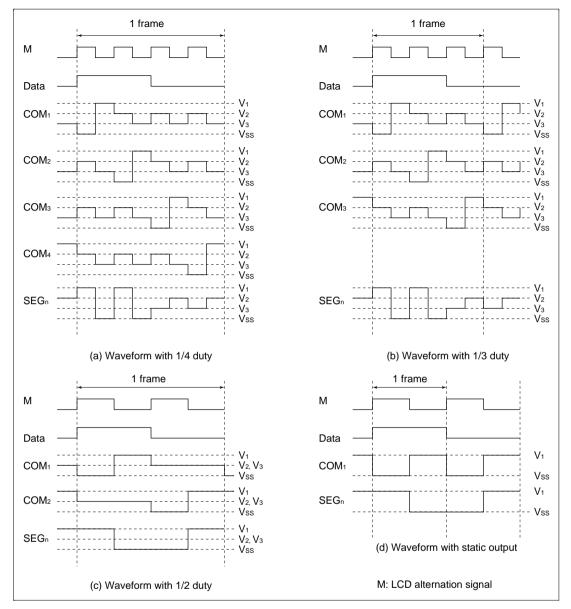

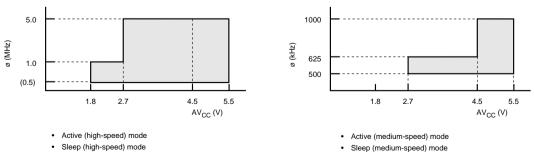

| HD6433801H                                                                            | —<br>—                                                                                                                                                                      | 64-pin QFP (FP-64A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ROM 12 kbytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |