**Genesis Microchip Publication**

## **Preliminary Data Sheet**

# gm6015

Publication number: C6015-DAT-01B Publication date: August 2002

**Genesis Microchip Inc.** 2150 Gold Street, P.O. Box 2150, Alviso, CA USA 95002 Tel: (408) 262-6599 Fax: (408) 262-6365 165 Commerce Valley Dr. West, Thornhill, ON Canada L3T 7V8 Tel: (905) 889-5400 Fax: (905) 889-5422 George Thangiah Complex(E), 2nd Flr, 80 Feet Road, Jeevan Bhima Nagar, Bangalore 560 075, India, Tel 91-80-526 3878 Fax 91-80-529 6245 4F, No. 57, Sing Jung Road, NeiHu Taipei, Taiwan 114, R.O.C Tel: 886-2-2791-0118 Fax: 886-2-2791-0196 143-37 Hyundai Tower, #902, Samsung-dong, Kangnam-gu, Seoul, Korea 135-090 Tel 82-2-553-5693 Fax 82-2-552-4942 Rm2614-2618 Shenzhen Office Tower, 6007 Shenana Blvd, 518040, Shenzhen, Guandong, P.R.C., Tel (0755)386-0101, Fax (0755)386-7874 2-9-5 Higashigotanda, Shinagawa-ku, Tokyo, 141-0022, Japan, Tel 81-3-5798-2758, Fax 81-3-5798-2759 www.genesis-microchip.com / info@genesis-microchip.com

#### **Document History:**

| Revision      | Description     | Date        |

|---------------|-----------------|-------------|

| C6015-DAT-01A | Initial Release | March 2002  |

| C6015-DAT-01B | Editorial       | August 2002 |

|               |                 |             |

#### **Related Documents:**

| Doc Number   | Title                           | Date |

|--------------|---------------------------------|------|

| C6010-DSR-01 | gm6010 / 6015 Programming Guide |      |

|              |                                 |      |

The following are Registered trademarks of Genesis Microchip Inc.:

| Genesis <sup>TM</sup>  | Genesis Display Perfection <sup>TM</sup>    | ESM <sup>TM</sup>                      | RealColor <sup>TM</sup>                 |

|------------------------|---------------------------------------------|----------------------------------------|-----------------------------------------|

|                        | Ultra-Reliable DVI <sup>TM</sup>            | Real Recovery <sup>TM</sup>            |                                         |

| Sage <sup>TM</sup>     | Smartset <sup>TM</sup>                      | Jag-ASM <sup>TM</sup>                  | SureSync <sup>TM</sup>                  |

|                        | Intelligent Picture Processing <sup>™</sup> | Adaptive Contrast Control <sup>™</sup> | Adaptive Backlight Control <sup>™</sup> |

| Faroudja <sup>TM</sup> | DCDi <sup>TM</sup>                          | TrueLife <sup>TM</sup>                 | IntelliComb <sup>TM</sup>               |

#### © Copyright 2002

Genesis Microchip Inc.

#### All Rights Reserved.

Genesis Microchip Inc. reserves the right to change or modify the information contained herein without notice. It is the customer's responsibility to obtain the most recent revision of the document. Genesis Microchip Inc. makes no warranty for the use of its products and bears no responsibility for any errors or omissions that may appear in this document.

## Table of Contents

| 1. OVE  | ERVIEW                            | 1  |

|---------|-----------------------------------|----|

| 1.1     | Applications                      | 1  |

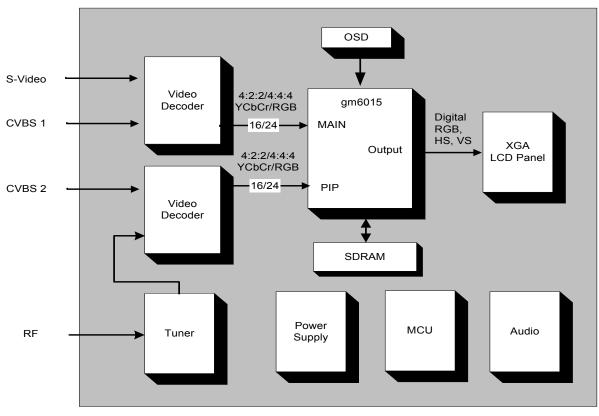

| 1.2     | System Design Example             | 1  |

| 1.3     | gm6015 Features                   | 2  |

| 2. PINO | OUT DIAGRAM                       | 4  |

| 3. PIN  | DESCRIPTION                       | 5  |

| 4. FUN  | ICTIONAL DESCRIPTION              | 11 |

| 4.1     | Reset                             | 12 |

| 4.1.1   | Hardware Reset                    | 12 |

| 4.1.2   | Software Reset                    | 12 |

| 4.2     | Bootstrap Configuration           | 12 |

| 4.3     | Clock Generation and Distribution | 13 |

| 4.3.1   | External Crystal / Oscillator     | 13 |

| 4.3.2   | PLL / DDS                         | 13 |

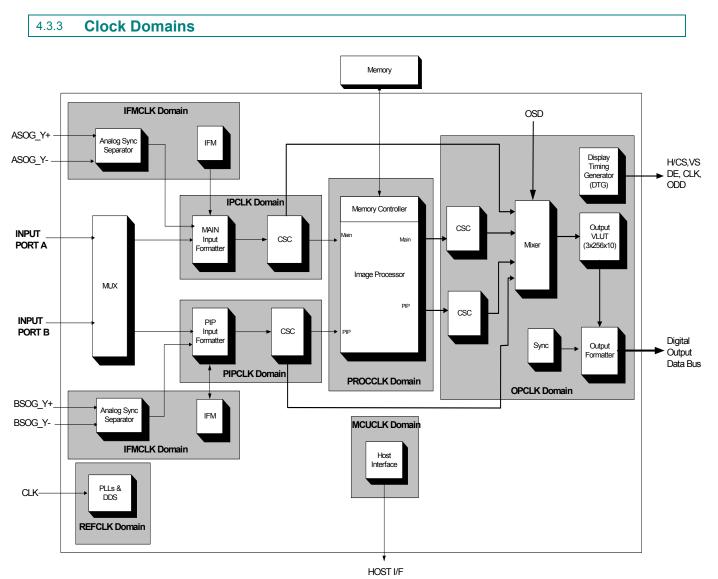

| 4.3.3   | Clock Domains                     | 15 |

| 4.4     | Input Interface                   | 16 |

| 4.4.1   | Input Port Selection              | 16 |

| 4.4.2   | Input Signals                     | 17 |

| 4.4.3   | Input Video Formats               | 20 |

| 4.4.4   | Input Sync Processing             | 21 |

| 4.4.5   | Input Capture Window              | 23 |

| 4.4.6   | Input Format Measurement          | 24 |

| 4.4.7   | Wide Screen Signal (WSS) decoding | 25 |

| 4.5     | Output Interface                  | 25 |

| 4.5.1   | Output Signals                    | 25 |

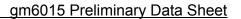

| 4.5.2   | 656 Encoder                       | 27 |

| 4.5.3   | VBI Data Insertion                | 28 |

| 4.5.4   | Output Video Formats              | 28 |

| 4.5.5   | Video Look Up Table               | 28 |

| 4.5.6   | Dithering                         |    |

| 4.5.7   | Output Configuration              | 30 |

| 4.6     | Color Space Conversion (CSC)      | 34 |

#### gm6015 Preliminary Data Sheet

| 4.6.1    | Input CSC               | 34 |

|----------|-------------------------|----|

| 4.6.2    | Output CSC              | 34 |

| 4.6.3    | Color Control           | 34 |

| 4.7      | Video Processing        | 35 |

| 4.7.1    | MAIN Channel            | 35 |

| 4.7.2    | PIP Channel             | 39 |

| 4.7.3    | Video Processing Bypass | 39 |

| 4.8      | Synchronization Modes   | 40 |

| 4.9      | Frame Store Interface   | 40 |

| 4.10     | Interrupt               | 41 |

| 4.11     | GPIO Pins               | 41 |

| 4.12     | Host Interface          | 42 |

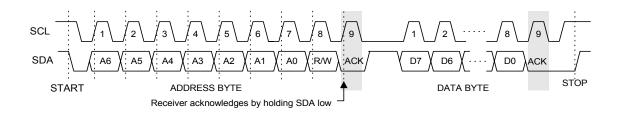

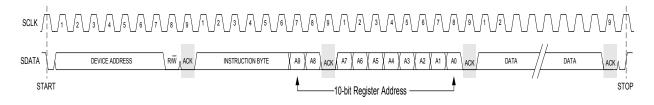

| 4.12.1   | 2-wire mode             | 42 |

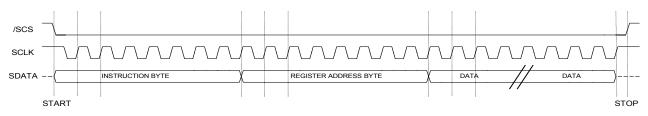

| 4.12.2   | 2 3-wire mode           | 45 |

| 5. Syste | em Layout Guideline     | 47 |

| 5.1      | Power / Ground          | 47 |

| 5.2      | Signals                 | 47 |

| 6. MEC   | CHANICAL SPECIFICATION  | 49 |

## List of Figures

| Figure 1.  | gm6015 System Design Example                                        | 1  |

|------------|---------------------------------------------------------------------|----|

| Figure 2.  | gm6015 Pinout Diagram                                               | 4  |

| Figure 3.  | gm6015 Functional Block Diagram                                     | 11 |

| Figure 4.  | Using crystal                                                       | 13 |

| Figure 5.  | Using oscillator                                                    | 13 |

| Figure 6.  | Clock Generation and Distribution                                   | 14 |

| Figure 7.  | Clock Domains                                                       | 15 |

| Figure 8.  | ITU-BT-656                                                          | 20 |

| Figure 9.  | 8-bit 4:2:2 YCbCr                                                   |    |

| Figure 10. | 16-bit 4:2:2 YCbCr                                                  |    |

| Figure 11. | 24-bit 4:4:4 YCbCr data                                             | 21 |

| Figure 12. | 24-bit RGB data                                                     | 21 |

| Figure 13. | Embedded Sync Extraction                                            |    |

| Figure 14. | Input Capture Window (HREF/DE enabled)                              | 23 |

| Figure 15. | Input Capture Window (HREF/DE disabled)                             | 24 |

| Figure 16. | Relationship between DHS_CS and DSYNCT                              | 27 |

| Figure 17. | Gamma correction                                                    |    |

| Figure 18. | 8-bit to 10-bit mapping                                             |    |

| Figure 19. | Pre-scale of data for sync insertion (with 8-bit to 10-bit mapping) |    |

| Figure 20. | 10-bit to 6-bit dithering                                           |    |

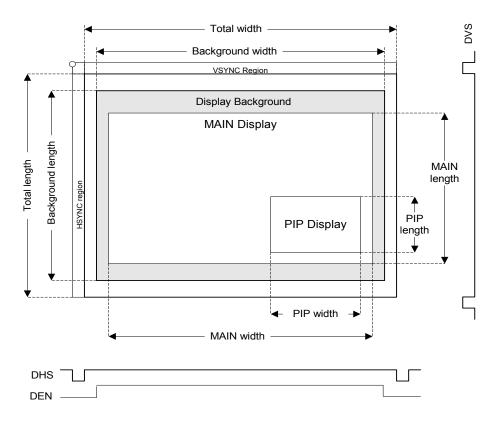

| Figure 21. | Output Display Windows                                              |    |

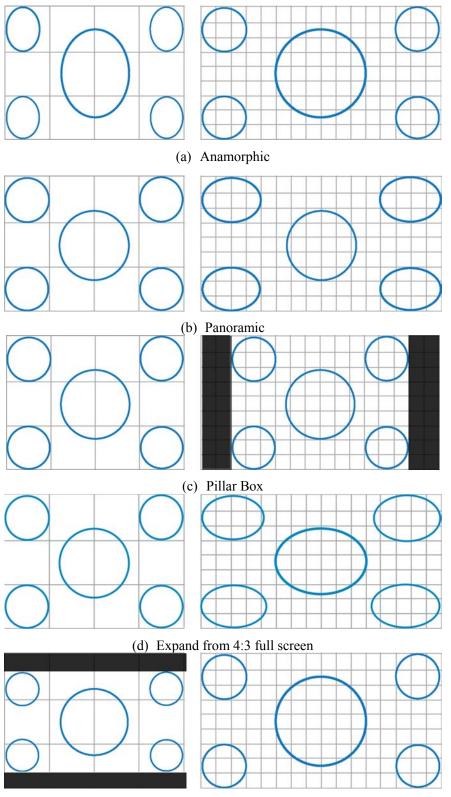

| Figure 22. | Examples of Different PIP Configurations                            |    |

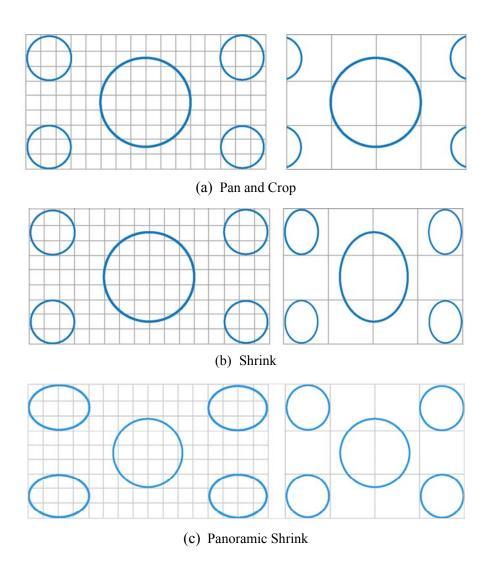

| Figure 23. | 4:3 to 16:9 aspect ratio conversion                                 |    |

| Figure 24. | 16:9 to 4:3 aspect ratio conversion                                 |    |

| Figure 25. | Inverse 3:2 pulldown processing                                     |    |

| Figure 26. | 2-wire protocol                                                     |    |

| Figure 27. | 10-bit Register Address                                             | 45 |

| Figure 28. | 3-wire protocol                                                     |    |

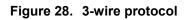

| Figure 29. | Typical SOY_G +/- connection                                        | 47 |

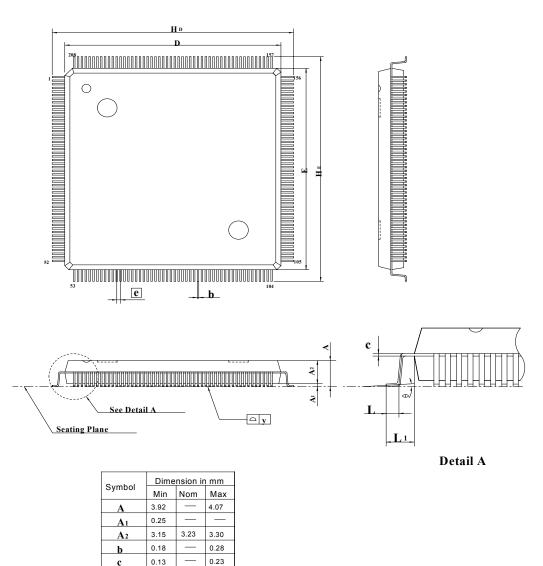

| Figure 30. | gm6015 208 pin PQFP dimension                                       |    |

## List of Tables

| Table 1.  | Input Port A                                        |

|-----------|-----------------------------------------------------|

| Table 2.  | Input Port B                                        |

| Table 3.  | Digital Display Port7                               |

| Table 4.  | Display Control7                                    |

| Table 5.  | SDRAM Interface Signals                             |

| Table 6.  | Host Interface                                      |

| Table 7.  | PLL / DDS                                           |

| Table 8.  | General Purpose I/O9                                |

| Table 9.  | Power and Ground                                    |

| Table 10. | Bootstrap Configuration                             |

| Table 11. | Input Video Data Bus Mapping On Port A and Port B16 |

| Table 12. | Input Port B bit[2318] used as output pins 19       |

| Table 13. | Input Port pins for OSD interface                   |

| Table 14. | Digital Output Port Pin Configuration               |

| Table 15. | Host Protocol Configuration                         |

| Table 16. | Instruction byte format                             |

|           |                                                     |

## 1. OVERVIEW

The Genesis Microchip gm6015 display processor is a low-cost, high-quality video processor for progressive TV (480p), digital TV (DTV) and high definition TV (HDTV) applications. The highly integrated gm6015 includes dual digital video inputs for MAIN and PIP display, dual bi-level / tri-level sync separators, "pixel-based" motion adaptive de-interlacing, 2:2/3:2 inverse pull-down film processing, diagonal processing, arbitrary shrink/zoom scaling on both MAIN and PIP channels, , "3D" noise reduction filter, SDRAM controller, color space conversion, color controls, video look up table (VLUT) and multi-image PIP display.

## **1.1 Applications**

- SDTV, HDTV and DTV

- Flat panel TV (LCD, PDP)

- Set-top box

- Scan converter box

## 1.2 System Design Example

Figure 1 below shows a XGA LCD TV system block diagram using gm6015. Designs based on gm6015 will benefit from its high integration and flexibility, which result in lower system cost and design for multi-platform approach.

## 1.3 gm6015 Features

#### • Dual Digital Input Port

- Interface compatible with common NTSC/PAL/SECAM video decoders, YPbPr/YUV/RGB digitizers, MPEG decoders and DVI receivers.

- Bi-level and tri-level sync strip / processing.

- Support for 8/16/24-bit 4:2:2/4:4:4 CCIR 656/601 YCbCr and RGB inputs.

- Programmable input capture size allows input of various SDTV / HDTV resolutions.

- Flexible input port configuration for various video format and data bus width.

- Clamp pulse generation for ADC interface.

- Progressive / Interlace input supported.

- Dual input format measurement units for input timing detection support

- Built-in Wide Screen Signal (WSS) decoder

#### • Digital Output Port

- Embedded (SOG) or separate syncs output.

- Programmable Y C delay (+ / 3 pixels)

- 4:2:2 / 4:4:4 YCbCr / RGB output formats

- ITU-R BT.656 output supported

- 6/8/10 bits per channel.

- Programmable MAIN and PIP display size for various VESA / SDTV / HDTV resolutions.

- Bi-level / tri-level sync support

- Progressive / Interlace output

#### Genesis Proprietary De-interlacing

- Auto detection of film or video source

- 2<sup>nd</sup> generation adaptive film mode (AFM) de-interlacing.

- Motion adaptive de-interlacing or inverse 3:2/2:2 pull-down de-interlacing on Main channel

- Diagonal processing in MAIN channel

- De-interlacing on PIP channel

- Advanced Arbitrary Scaling

- Programmable zoom/shrink scale on MAIN channel allows aspect ratio to be converted or preserved.

- Programmable zoom/shrink scale on PIP channel allows variable PIP size.

- Panoramic zoom / shrink are supported in MAIN channel

#### • Flexible MAIN / PIP Configuration

- Multiple PIPs supported. A maximum of 16 PIP windows can be displayed.

- Programmable MAIN and PIP positions

- Programmable MAIN background colors

- Programmable PIP border colors.

- Programmable blending levels of PIP display.

- Hi-light border eases active PIP selection in multi-PIP display

- Instantaneous MAIN / PIP swapping

#### • Others

- Integrated triple 256x10-bit video look up table.

- Integrated SDRAM controller. Typically only 1 2M x 32-bit SDRAM is needed.

- Integrated DDS and PLL for clock generation. Only a single low cost 14.31818 MHz crystal is needed externally.

- Arbitrary up/down frame rate conversion. (e.g. 50Hz to 60Hz, 50Hz to 100Hz, 60Hz to 50Hz, ....etc)

- Input and output color space conversion (CSC)

- Fully programmable color space coefficients and offsets in MAIN and PIP input CSC.

- Bypass channel available

- "3D" noise reduction filter in MAIN channel for standard definition video

- Sharpening filter in MAIN channel with selectable coefficients.

- Programmable interrupt

- Chip activity monitoring circuit.

- OSD interface

- 2-wire or 3-wire SPI host interface

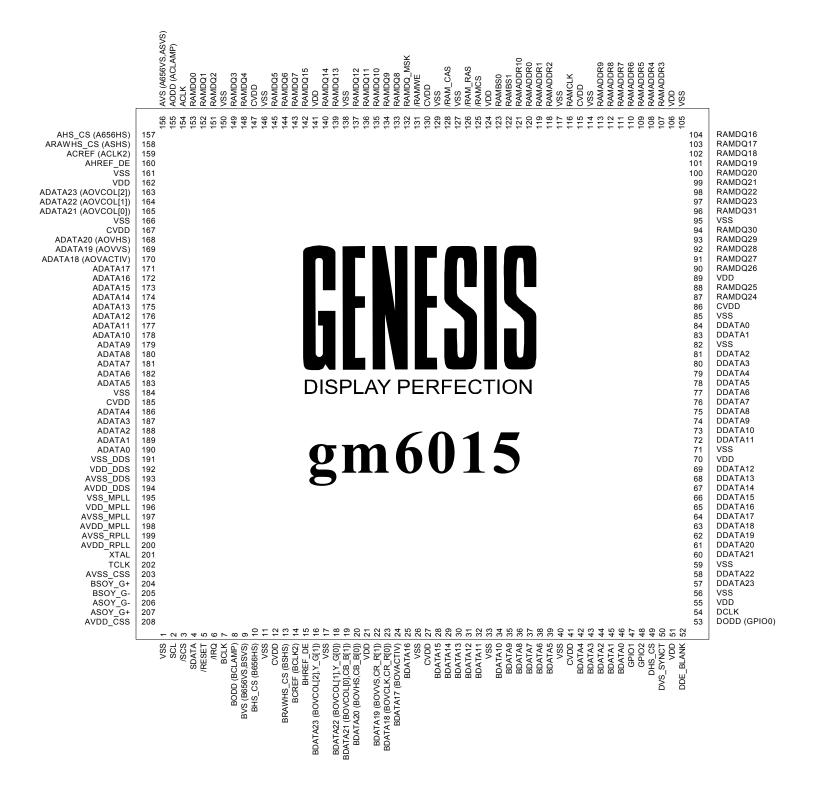

#### Figure 2. gm6015 Pinout Diagram

## 3. PIN DESCRIPTION

I/O Legend: I = Input

**O** = Output

**P** = Power **G** = Ground

Table 1. Input Port A

| Name                | I/O   | Pin# | Description                                                                            |

|---------------------|-------|------|----------------------------------------------------------------------------------------|

| ACLK1               | Ι     | 154  | Port A input clock 1                                                                   |

| AODD                | Ι     | 155  | 1. Port A odd/even field indicator input (Default)                                     |

| (ACLAMP)            | 0     |      | 2. Port A clamp pulse output                                                           |

| AVS                 | Ι     | 156  | 1. Port A input VS (Default)                                                           |

| (A656VS)            | 0     |      | 2. Port A VS extracted from 656 data                                                   |

| (ASVS)              | 0     |      | 3. Port A VS extracted from SOG / SOY                                                  |

| AHS CS              | Ι     | 157  | 1. Port A input HS or composite sync (Default)                                         |

| <br>(A656HS)        | 0     |      | 2. Port A HS extracted from 656 data                                                   |

| ASOY_G+             | Ι     | 207  | Port A bi-level / tri-level sync on green / Y                                          |

| ASOY_G-             | Ι     | 206  | Port A bi-level / tri-level sync on green / Y                                          |

| ARAWHS_CS           | Ι     | 158  | 1. Port A raw HS or composite sync (Default)                                           |

| (ASHS)              | 0     |      | 2. Port A HS extracted from SOG / SOY                                                  |

| ACREF               | Ι     | 159  | 1. Port A input clock qualifier (Default)                                              |

| (ACLK2)             | Ι     |      | 2. Port A input clock 2                                                                |

| AHREF_DE            | Ι     | 160  | Port A input HREF or DE (Data Enable) from DVI receiver                                |

| ADATA23 (AOVCOL[2]) | Ι     | 163  | 1. Port A input data or overlay interface. Please refer to Table 11 for bus selection. |

| ADATA22 (AOVCOL[1]) | I     | 164  | 2. Overlay interface                                                                   |

| ADATA21 (AOVCOL[0]) | Ι     | 165  |                                                                                        |

| ADATA20 (AOVHS)     | I (O) | 168  |                                                                                        |

| ADATA19 (AOVVS)     | I (O) | 169  |                                                                                        |

| ADATA18 (AOVCLK)    | I (O) | 170  |                                                                                        |

| ADATA17 (AOVACTIV)  | Ι     | 171  |                                                                                        |

| ADATA16             | Ι     | 172  |                                                                                        |

| ADATA15             | Ι     | 173  |                                                                                        |

| ADATA14             | Ι     | 174  |                                                                                        |

| ADATA13             | Ι     | 175  |                                                                                        |

| ADATA12             | Ι     | 176  |                                                                                        |

| ADATA11             | Ι     | 177  |                                                                                        |

| ADATA10             | Ι     | 178  |                                                                                        |

| ADATA9              | Ι     | 179  |                                                                                        |

| ADATA8              | Ι     | 180  |                                                                                        |

| ADATA7              | Ι     | 181  |                                                                                        |

| ADATA6              | Ι     | 182  |                                                                                        |

| ADATA5              | Ι     | 183  |                                                                                        |

| ADATA4              | Ι     | 186  |                                                                                        |

| ADATA3              | Ι     | 187  |                                                                                        |

| ADATA2              | Ι     | 188  |                                                                                        |

| ADATA1              | Ι     | 189  |                                                                                        |

| ADATA0              | Ι     | 190  |                                                                                        |

| Name                          | I/O      | Pin#     | Description                                                                      |

|-------------------------------|----------|----------|----------------------------------------------------------------------------------|

| BCLK1                         | I        | 7        |                                                                                  |

| BODD                          | I        | 8        | Port B input clock 1 1. Port B odd/even field indicator input (Default)          |

| (BCLAMP)                      | 0        | 0        | <ol> <li>Port B clamp pulse output</li> <li>Port B clamp pulse output</li> </ol> |

| BVS                           | I        | 9        | 1.     Port B input VS     (Default)                                             |

| (B656VS)                      | 0        | 2        | 2. Port B VS extracted from 656 data                                             |

| (BSVS)                        | 0        |          | <ol> <li>Port B VS extracted from SOG / SOY</li> </ol>                           |

| BHS_CS                        | I        | 10       | 1.     Port B input HS or composite sync     (Default)                           |

| (B656HS)                      | 0        | 10       | <ol> <li>Port B HS extracted from 656 data</li> </ol>                            |

| BSOY G+                       | I        | 204      | Port B bi-level / tri-level sync on green / Y                                    |

| BSOY_G-                       | I        | 204      | Port B bi-level / tri-level sync on green / Y                                    |

|                               | I        | 13       |                                                                                  |

| BRAWHS_CS<br>(BSHS)           |          | 15       |                                                                                  |

|                               | 0        | 14       |                                                                                  |

| BCREF                         | I        | 14       | 1. Port B input clock qualifier     (Default)       2. Port B input clock 2      |

| (BCLK2)                       | I        | 1.5      | 2. Port B input clock 2                                                          |

| BHREF_DE                      | I        | 15       | Port B HREF or DE (Data Enable) from TMDS receiver                               |

| BDATA23 (BOVCOL[2], Y_G[1])   | I (I, O) | 16       | 1. Port B input data. Please refer to Table 11 for bus selection.                |

| BDATA22 (BOVCOL[1], Y_G[0])   | I (I, O) | 18       | 2. Overlay interface.                                                            |

| BDATA21 (BOVCOL[0], CB_B[1])  | I (I, O) | 19       | 3. Output LSB bits of 10-bit per channel output data                             |

| BDATA20 (BOVHS, CB_B[0])      | I (O, O) | 20       | • 30-bit YCbCr 4:4:4                                                             |

| BDATA19 (BOVVS, CR_R[1])      | I (O, O) | 22       | BDATA[23:22] = Y[1:0]                                                            |

| BDATA18 (BOVCLK, CR_R[0])     | I (O, O) | 23       | BDATA[21:20] = Cb[1:0]                                                           |

| BDATA17 (BOVACTIV)<br>BDATA16 | I        | 24<br>25 | BDATA[19:18] = Cr[1:0]                                                           |

| BDATA16<br>BDATA15            | I        |          | • 30-bit RGB                                                                     |

| BDATA14                       | I<br>I   | 28<br>29 | BDATA[23:22] = G[1:0]<br>BDATA[21:20] = B[1:0]                                   |

| BDATA14<br>BDATA13            | I        | 29<br>30 | BDATA[19:18] = R[1:0]                                                            |

| BDATA12                       | I        | 30       | BDA1A[19.16] = K[1.0]                                                            |

| BDATA12<br>BDATA11            | I        | 32       |                                                                                  |

| BDATA10                       | I        | 32<br>34 |                                                                                  |

| BDATA9                        | I        | 35       |                                                                                  |

| BDATA8                        | I        | 35<br>36 |                                                                                  |

| BDATA7                        | I        | 30       |                                                                                  |

| BDATA6                        | I        | 38       |                                                                                  |

| BDATA5                        | I        | 39       |                                                                                  |

| BDATA4                        | I        | 42       |                                                                                  |

| BDATA3                        | I        | 43       |                                                                                  |

| BDATA2                        | I        | 44       |                                                                                  |

| BDATA1                        | I        | 45       |                                                                                  |

| BDATA0                        | I        | 46       |                                                                                  |

#### Table 2. Input Port B

#### gm6015 Preliminary Data Sheet

| Name      | I/O | Pin# | Description                                                                                  |

|-----------|-----|------|----------------------------------------------------------------------------------------------|

| DDATA[23] | 0   | 57   | Digital display data bus. Please refer to Input Port B for 10-bit RGB / YCbCr 4:4:4 LSB bits |

| DDATA[22] | 0   | 58   |                                                                                              |

| DDATA[21] | 0   | 60   | For pin assignment of various video formats please refer to Table 14.                        |

| DDATA[20] | 0   | 61   |                                                                                              |

| DDATA[19] | 0   | 62   |                                                                                              |

| DDATA[18] | 0   | 63   |                                                                                              |

| DDATA[17] | 0   | 64   |                                                                                              |

| DDATA[16] | 0   | 65   |                                                                                              |

| DDATA[15] | 0   | 66   |                                                                                              |

| DDATA[14] | 0   | 67   |                                                                                              |

| DDATA[13] | 0   | 68   |                                                                                              |

| DDATA[12] | 0   | 69   |                                                                                              |

| DDATA[11] | 0   | 72   |                                                                                              |

| DDATA[10] | 0   | 73   |                                                                                              |

| DDATA[9]  | 0   | 74   |                                                                                              |

| DDATA[8]  | 0   | 75   |                                                                                              |

| DDATA[7]  | 0   | 76   |                                                                                              |

| DDATA[6]  | 0   | 77   |                                                                                              |

| DDATA[5]  | 0   | 78   |                                                                                              |

| DDATA[4]  | 0   | 79   |                                                                                              |

| DDATA[3]  | 0   | 80   |                                                                                              |

| DDATA[2]  | 0   | 81   |                                                                                              |

| DDATA[1]  | 0   | 83   |                                                                                              |

| DDATA[0]  | 0   | 84   |                                                                                              |

#### Table 3.Digital Display Port

#### Table 4.Display Control

| Name      | I/O | Pin# | Description                                                                                              |

|-----------|-----|------|----------------------------------------------------------------------------------------------------------|

| DCLK      | 0   | 54   | Display output clock                                                                                     |

| DVS       | 0   | 50   | 1. Display VSYNC (Default)                                                                               |

| (DSYNCT)  | 0   |      | 2. Display tri-level sync control                                                                        |

| DHS_CS    | 0   | 49   | Display HSYNC / composite sync                                                                           |

| DODD      | 0   | 53   | 1. Display field indicator (Default)                                                                     |

| (GPIO 0)  | I/O |      | 2. General purpose I/O pin 0                                                                             |

|           |     |      | Note: This is a GPIO pin with DODD as default function. For other GPIO functions, refer to section 4.11. |

| DDE_BLANK | 0   | 52   | 1. Display data enable / blanking                                                                        |

| Name      | I/O | Pin# | Description                    |

|-----------|-----|------|--------------------------------|

|           |     |      |                                |

| RAMCLK    | 0   | 116  | SDRAM clock                    |

| RAMBS0    | 0   | 123  | SDRAM bank select 0            |

| RAMBS1    | 0   | 122  | SDRAM bank select 1            |

| RAMCS#    | 0   | 125  | SDRAM chip select              |

| RAMDQ_MSK | 0   | 132  | SDRAM data input / output mask |

| RAMWE#    | 0   | 131  | SDRAM write enable             |

| RAM_RAS#  | 0   | 126  | SDRAM row address strobe       |

| RAM_CAS#  | 0   | 128  | SDRAM column address strobe    |

| RAMADDR10 | 0   | 121  | SDRAM address bus              |

| RAMADDR9  | 0   | 113  |                                |

| RAMADDR8  | 0   | 112  |                                |

| RAMADDR7  | 0   | 111  |                                |

| RAMADDR6  | 0   | 110  |                                |

| RAMADDR5  | 0   | 109  |                                |

| RAMADDR4  | 0   | 108  |                                |

| RAMADDR3  | 0   | 107  |                                |

| RAMADDR2  | 0   | 118  |                                |

| RAMADDR1  | 0   | 119  |                                |

| RAMADDR0  | 0   | 120  |                                |

| RAMDQ31   | I/O | 96   | SDRAM data bus                 |

| RAMDQ30   | I/O | 94   |                                |

| RAMDQ29   | I/O | 93   |                                |

| RAMDQ28   | I/O | 92   |                                |

| RAMDQ27   | I/O | 91   |                                |

| RAMDQ26   | I/O | 90   |                                |

| RAMDQ25   | I/O | 88   |                                |

| RAMDQ24   | I/O | 87   |                                |

| RAMDQ23   | I/O | 97   |                                |

| RAMDQ22   | I/O | 98   |                                |

| RAMDQ21   | I/O | 99   |                                |

| RAMDQ20   | I/O | 100  |                                |

| RAMDQ19   | I/O | 101  |                                |

| RAMDQ18   | I/O | 102  |                                |

| RAMDQ17   | I/O | 103  |                                |

| RAMDQ16   | I/O | 104  |                                |

| RAMDQ15   | I/O | 142  |                                |

| RAMDQ14   | I/O | 140  |                                |

| RAMDQ13   | I/O | 139  |                                |

| RAMDQ12   | I/O | 137  |                                |

| RAMDQ11   | I/O | 136  |                                |

| RAMDQ10   | I/O | 135  |                                |

| RAMDQ9    | I/O | 134  |                                |

| RAMDQ8    | I/O | 133  |                                |

| RAMDQ7    | I/O | 143  |                                |

#### Table 5. SDRAM Interface Signals

#### gm6015 Preliminary Data Sheet

| Name   | I/O | Pin# | Descrip |

|--------|-----|------|---------|

| RAMDQ6 | I/O | 144  |         |

| RAMDQ5 | I/O | 145  |         |

| RAMDQ4 | I/O | 148  |         |

| RAMDQ3 | I/O | 149  |         |

| RAMDQ2 | I/O | 151  |         |

| RAMDQ1 | I/O | 152  |         |

| RAMDQ0 | I/O | 153  |         |

#### Table 6. Host Interface

| Name   | I/O | Pin# | Description                              |  |  |  |

|--------|-----|------|------------------------------------------|--|--|--|

| /SCS   | Ι   | 3    | Chip select for 3-wire mode. Active low. |  |  |  |

| SCLK   | Ι   | 2    | lock for host interface.                 |  |  |  |

| SDATA  | I/O | 4    | Serial data.                             |  |  |  |

| /RESET | Ι   | 5    | Reset. Active low                        |  |  |  |

| /IRQ   | 0   | 6    | Interrupt output. Active low, open drain |  |  |  |

#### Table 7. PLL / DDS

| Name | I/O | Pin# | Description                                                                                          |

|------|-----|------|------------------------------------------------------------------------------------------------------|

| TCLK | 0   | 202  | Feedback connection to 14.318 MHz crystal. If the reference clock source is a clock oscillator, this |

|      |     |      | pin should be grounded through a 2.7K pulldown resistor.                                             |

| XTAL | Ι   | 201  | Crystal oscillator input. Connect to 14.318 MHz crystal.                                             |

#### Table 8. General Purpose I/O

| Name  | I/O | Pin# | Description         |

|-------|-----|------|---------------------|

| GPIO1 | I/O | 47   | General Purpose I/O |

| GPIO2 | I/O | 48   | General Purpose I/O |

#### Table 9.Power and Ground

| Name      | I/O       | Pin# | Description                                    |  |  |

|-----------|-----------|------|------------------------------------------------|--|--|

|           |           |      | Composite Sync Separator                       |  |  |

| AVDD_CSS  | Р         | 208  | 3.3V analog power for composite sync separator |  |  |

| AVSS_CSS  | G         | 203  | Analog ground for composite sync separator     |  |  |

|           | PLL / DDS |      |                                                |  |  |

| AVDD_RPLL | Р         | 200  | 3.3V analog power for REFCLK PLL               |  |  |

| AVDD_MPLL | Р         | 198  | 3.3V analog power for PROCCLK PLL              |  |  |

| AVDD_DDS  | Р         | 194  | 3.3V Analog power for DCLK DDS                 |  |  |

| VDD_PLL   | Р         | 196  | 3.3V digital power for DCLK PLL                |  |  |

| VDD_DDS   | Р         | 192  | 3.3V digital power for DDS                     |  |  |

| AVSS_RPLL | G         | 199  | Analog ground for REFCLK PLL                   |  |  |

| AVSS_MPLL | G         | 197  | Analog ground for PROCCLK PLL                  |  |  |

| AVSS_DDS  | G         | 193  | Analog ground for DCLK DDS                     |  |  |

#### gm6015 Preliminary Data Sheet

| Name    | I/O | Pin#                                                                              | Pin# Description                      |  |  |  |  |

|---------|-----|-----------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

| VSS_PLL | G   | 195                                                                               | Digital ground for DCLK PLL           |  |  |  |  |

| VSS_DDS | G   | 191                                                                               | Digital ground for DDS                |  |  |  |  |

|         |     |                                                                                   | Others                                |  |  |  |  |

| VDD     | Р   | 21, 51, 7<br>106, 124<br>162,                                                     |                                       |  |  |  |  |

| CVDD    | Р   | 12, 27, 4<br>86, 115,<br>147, 167                                                 | 130,                                  |  |  |  |  |

| VSS     | G   | 1, 11, 17<br>33, 40, 5<br>71, 82,<br>95, 105,<br>117, 127<br>138, 146<br>161, 166 | 5, 59,<br>85,<br>114,<br>129,<br>150, |  |  |  |  |

## 4. FUNCTIONAL DESCRIPTION

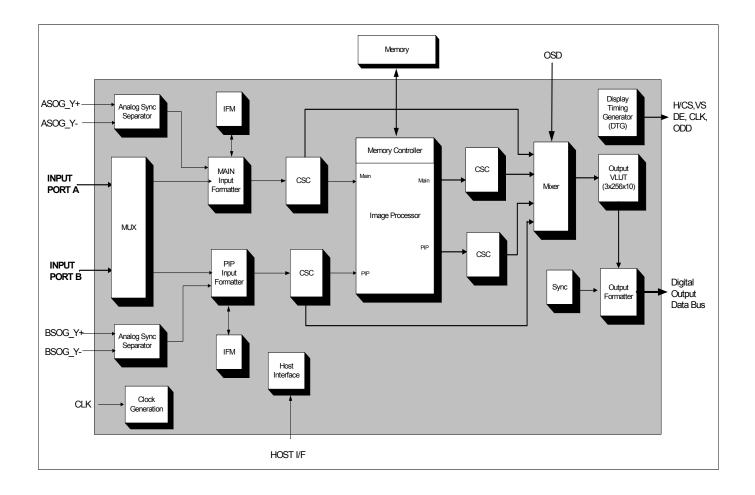

The block diagram below illustrates the internal functional blocks of gm6015. Each block will be described in the following sections.

Figure 3. gm6015 Functional Block Diagram

## 4.1 Reset

#### 4.1.1 Hardware Reset

Hardware reset is performed by holding the /RESET pin low for a minimum of 1µs. The clock from external clock source (typically 14.31818MHz, see Figure 3 and Figure 4) must be present during and after the reset. All registers will be reset to their default values.

#### 4.1.2 **Software Reset**

Software reset is performed by setting HOST\_CTRL register bit SOFT\_RESET to 1. This bit will be self-cleared to 0 upon completion of reset. The status of each clock domain after reset can be read from the RESET\_STATUS register. All active and status registers will be reset to their default state. Pending and read/write registers are not affected by software reset.

### 4.2 **Bootstrap Configuration**

During hardware reset, some SDRAM interface pins (RAMADDR [10:0], RAMBS[1..0], RAMDQ\_MSK) are configured as inputs. Pull high or pull low resistors ( $10K\Omega$ ) can be placed in these pins. On the falling edge of /RESET, the value on these lines is captured. This value is readable by the external microcontroller and is used to configure gm6015 host interface and other user defined options.

| Pin Name     | Description                                                           |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|--|--|--|--|--|

| RAMADDR[4:0] | 1. If 2-wire protocol is selected, this sets device address bit [51]. |  |  |  |  |  |

|              | 2. If 3-wire protocol is selected, this pins are ignored.             |  |  |  |  |  |

| RAMADDR[5]   | 1. If 2-wire protocol is selected, this sets device address bit [6].  |  |  |  |  |  |

|              | 2. If 3-wire protocol is selected :                                   |  |  |  |  |  |

|              | - pull high to select active drive on SDATA pin                       |  |  |  |  |  |

|              | - pull low to select open drain on SDATA pin                          |  |  |  |  |  |

| RAMADDR[6]   | 1. If 2-wire protocol is selected, this sets device address bit [7].  |  |  |  |  |  |

|              | 2. If 3-wire protocol is selected :                                   |  |  |  |  |  |

|              | - pull high to select transmit on SCLK falling edge and receive on    |  |  |  |  |  |

|              | SCLK rising edge                                                      |  |  |  |  |  |

|              | - pull low to select transmit on SCLK rising edge and receive on      |  |  |  |  |  |

|              | SCLK falling edge                                                     |  |  |  |  |  |

| RAMADDR[7]   | 1. Pull high to select 3-wire SPI protocol                            |  |  |  |  |  |

|              | 2. Pull low to select 2-wire I <sup>2</sup> C compatible protocol     |  |  |  |  |  |

| RAMADDR[8]   | User defined option 0                                                 |  |  |  |  |  |

| RAMADDR[9]   | User defined option 1                                                 |  |  |  |  |  |

| RAMADDR[10]  | User defined option 2                                                 |  |  |  |  |  |

| BS0          | User defined option 3                                                 |  |  |  |  |  |

| BS1          | User defined option 4                                                 |  |  |  |  |  |

| DQM          | TCLK frequency                                                        |  |  |  |  |  |

|              | 1. Pull high : TCLK frequency > 14.31818 MHz                          |  |  |  |  |  |

|              | 2. Pull low : TCLK frequency <= 14.31818 MHz                          |  |  |  |  |  |

Table 10.

Bootstrap Configuration

## **4.3 Clock Generation and Distribution**

gm6015 has built-in PLLs (Phase Locked Loops) and DDS (Direct Digital Synthesis) to generate all the clocks necessary for all the functional blocks. Each clock can be programmed to route to various functional blocks.

#### 4.3.1 External Crystal / Oscillator

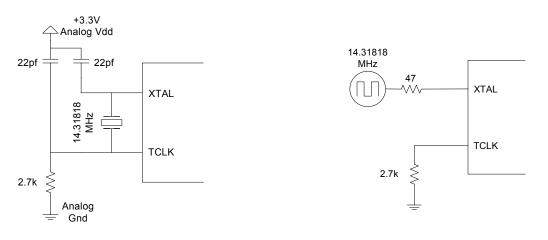

Externally a single crystal or TTL/CMOS level clock oscillator is needed. The following two figures illustrate the use in each case:

Figure 4. Using crystal

Figure 5. Using oscillator

In Figure 4 all components should be placed close to the chip, with a clean analog ground. In Figure 5 the  $47\Omega$  resistor should be placed close to the oscillator. The internal oscillating circuit will generate OSCCLK, which are used by the built-in PLLs to generate all internal clocks, as described in the next section.

#### 4.3.2 **PLL / DDS**

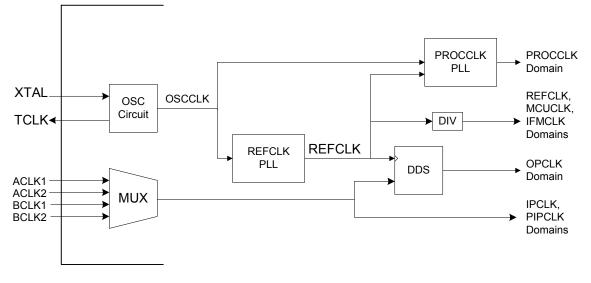

The built-in PLLs and DDS are used to generate all internal clocks as well as display clock. The following is a block diagram of the PLL/DDS block:

Figure 6. Clock Generation and Distribution

The REFCLK PLL is programmed to generate a 171MHz clock which is used by the PROCCLK PLL, the DDS and other clock domains, namely REFCLK, MCUCLK and IFMCLK domains. REFCLK will be further divided in MCUCLK and IFMCLK domains.

The PROCCLK PLL is programmed to generate a 100MHz clock to be used by other blocks. The DDS locks its output frequency (DDSCLK) to the selected input clock (normally the clock for the MAIN channel) and it can be programmed to generate a wide range of frequency (from 12MHz to 110MHz) for the display clock.

The following equation is used to calculate the output frequency of the 2 PLLs. MULT and DIV are 5bit numbers, with a valid range from 0 to 31 decimal. PDIV is a 2-bit number, with a value of 0 to 3 decimal.

$$f_{PLLCLK} = f_{OSCCLK} \times \frac{MULT + 1}{DIV + 1} \times \frac{1}{2^{PDIV}}$$

For details in PLL / DDS programming, please refer to "gm6010/6015 Register Programming Guide"

Figure 7. Clock Domains

Each functional block in gm6015 is driven by a clock which is programmable to come from different sources. The following is a list of the clock domains in gm6015:

- 1. IPCLK domain. This is the clock for the MAIN input channel. This will normally come from ACLK1/ACLK2 or BCLK1/BCLK2, depends on which port is selected as the MAIN channel.

- 2. PIPCLK domain. This is the clock for the PIP input channel. This will normally come from ACLK1/ACLK2 or BCLK1/BCLK2, depends on which port is selected as the PIP channel.

- 3. IFMCLK domain. This is the clock for the IFM and the Analog Sync Separator blocks. This will normally be driven by the REFCLK PLL divided by 4 (50 MHz clock).

- 4. REFCLK domain. This is the clock for the DDS. This comes from the output of the REFCLK PLL (200 MHz clock).

- 5. MCUCLK domain. This is the clock for the embedded microcontroller and the gm6015 host interface. Since this clock drives the host interface, it must have a stable source at reset. At reset, this clock will be driven by TCLK pin. After the PLLs have had time to lock and settle, the source of this clock will be automatically switched to REFCLK divided by 4 (50 MHz clock). This automatic switching can be disabled or overriden by the use of bootstrap inputs (RAMDQ\_MSK).

- 6. PROCCLK domain. This is the video processing and memory interface clock. The filters in MAIN channel and SDRAM interface run in this clock domain. This comes from the output of the PROCCLK PLL (100 MHz clock).

- 7. OPCLK domain. This is the display clock for the chip. This normally comes from the DDS (programmable frequency locked to IPCLK).

### 4.4 Input Interface

Two identical digital input ports (Port A and Port B) are provided as interfaces to input video. Each port can be programmed to accept various input video formats and provide glueless interface to most NTSC/PAL/SECAM video decoders, YCbCr/RGB digitizers (ADC/PLL), MPEG decoders and LVDS/TMDS receivers.

#### 4.4.1 **Input Port Selection**

Both Port A and Port B can be used as the source for MAIN or PIP display. All parameters in MAIN and PIP input registers (e.g. input capture window size, input lock event, ...etc.) need to be set according to the input video format in each port.

gm6015 allows a very flexible configuration on the data bus going into the input ports. Each 24-bit input port can be configured to be:

- Three 8-bit bus port

- One 8-bit bus port and one 16-bit bus port

- One 24-bit bus port

RGB or YCbCr data can be connected to any bus in each configuration. However, all the input timing signal pins (except pixel clock) will also be associated with the data bus selected.

2 input pixel clock pins are available for each input port. The pixel clock to be used can be selected to come from either Port A or Port B.

The data bus configuration of each input port can be selected by bit[2:0] of *MAIN\_IP\_SRC* and *PIP\_IP\_SRC* registers, as shown in the following table :

| bit[2:0] = | 000           | 001           | 010           | 011           | 100           | 101           |

|------------|---------------|---------------|---------------|---------------|---------------|---------------|

| 24 bit RGB | DATA[23:16]=G | DATA[23:16]=G | DATA[23:16]=R | DATA[23:16]=B | DATA[23:16]=R | DATA[23:16]=B |

#### Table 11. Input Video Data Bus Mapping On Port A and Port B

#### gm6015 Preliminary Data Sheet

|                  | DATA[15:8]=B    | DATA[15:8]=R    | DATA[15:8]=G     | DATA[15:8]=G     | DATA[15:8]=B    | DATA[15:8]=R     |

|------------------|-----------------|-----------------|------------------|------------------|-----------------|------------------|

|                  | DATA[7:0]=R     | DATA[7:0]=B     | DATA[7:0]=B      | DATA[7:0]=R      | DATA[7:0]=G     | DATA[7:0]=G      |

| 24 bit YUV 4:4:4 | DATA[23:16]=Y   | DATA[23:16]=Y   | DATA[23:16]=V    | DATA[23:16]=U    | DATA[23:16]=V   | DATA[23:16]=U    |

|                  | DATA[15:8]=U    | DATA[15:8]=V    | DATA[15:8]=Y     | DATA[15:8]=Y     | DATA[15:8]=U    | DATA[15:8]=V     |

|                  | DATA[7:0]=V     | DATA[7:0]=U     | DATA[7:0]=U      | DATA[7:0]=V      | DATA[7:0]=Y     | DATA[7:0]=Y      |

| 16 bit YUV 4:2:2 | DATA[23:16]=Y   | DATA[23:16]=Y   | DATA[23:16]= UV  | DATA[23:16]= 'X' | DATA[23:16]=UV  | DATA[23:16]= 'X' |

|                  | DATA[15:8]='X'  | DATA[15:8]= UV  | DATA[15:8]=Y     | DATA[15:8]=Y     | DATA[15:8]= 'X' | DATA[15:8]=UV    |

|                  | DATA[7:0]=UV    | DATA[7:0]='X'   | DATA[7:0]='X'    | DATA[7:0]=UV     | DATA[7:0]=Y     | DATA[7:0]=Y      |

| 8 bit YUV 4:2:2  | DATA[23:16]='X' | DATA[23:16]='X' | DATA[23:16]= YUV | DATA[23:16]= 'X' | DATA[23:16]=YUV | DATA[23:16]= 'X' |

|                  | DATA[15:8]='X'  | DATA[15:8]= YUV | DATA[15:8]='X'   | DATA[15:8]='X'   | DATA[15:8]= 'X' | DATA[15:8]=YUV   |

|                  | DATA[7:0]=YUV   | DATA[7:0]='X'   | DATA[7:0]='X'    | DATA[7:0]=YUV    | DATA[7:0]='X'   | DATA[7:0]='X'    |

#### NOTE :

i) bit[2:0] = '110' or '111' are invalid;

- ii) 'X' means not used

- iii) If output is set to 30-bit RGB or 30-bit 4:4:4 YCbCr, then BDATA[23:18] in input port B are used as 2 LSB bits of 10-bit output data. In such case the input format in port B will be limited. See section 4.4.2.9 for detail.

#### 4.4.2 Input Signals

The following sections describe in details all signals associated with the 2 input ports.

NOTE :

- Each section describes the pins for both Port A and Port B and both pin names will be shown ;

- Some pins have multiple functions and their corresponding pin names are listed for reference. Pin names in bracket are alternate pin functions which need to be enabled by registers.

#### 4.4.2.1 ACLK1 BCLK1

These are the input pixel clocks and they are qualified by ACREF / BCREF respectively. The sampling edge of ACLK / BCLK is programmable and the default is rising edge.

#### 4.4.2.2 ACREF (ACLK2) BCREF (BCLK2)

• ACREF / BCREF (Default)

These are the clock qualifiers for ACLK1 / BCLK1 respectively. All data during the sampling edge of ACLK1 / BCLK1 are ignored when ACREF / BCREF is inactive.

• ACLK2 / BCLK2

These serve as a second input pixel clock pins. When a input port is divided into 2 input data bus, these pins can be used as the input pixel clock for each of the data bus.

#### 4.4.2.3 AODD (ACLAMP) BODD (BCLAMP)

#### • AODD / BODD (Default)

These are the odd / even field indicator <u>input</u> pins and are usually driven by video decoder or MPEG decoder.

• ACLAMP / BCLAMP

These are the clamp pulse <u>output</u> pins and are usually connected to external ADC to restore the dc level of analog input signal. Location of the start and end of clamp pulse is programmable.

4.4.2.4 AVS (A656VS, ASVS) BVS (B656VS, BSVS)

- AVS / BVS (Default) These pins serve as <u>input</u> vsync pins and are usually connected to video decoder or MPEG decoder.

- A656VS / B656VS

These pins serve as <u>output</u> vsync pins that are extracted from input video in ITU-BT-656 format. They can be used by external devices which need vsync signal for other timing purposes.

• ASVS / BSVS

These pins serve as <u>output</u> vsync pins that are extracted from input video with embedded sync on green or Y channel (SOG or SOY). They can be used by external devices which need vsync signal for other timing purposes.

4.4.2.5 AHS\_CS (A656HS) BHS\_CS (B656HS)

• AHS\_CS / BHS\_CS (Default)

These pins serve as <u>input</u> hsync or composite sync pins and are usually connected from input video decoder or MPEG decoder. For composite sync input, the vsync and hsync will be extracted by the built-in sync separator and can be routed internally to the MAIN and PIP channels. See section 4.4.4.2 "Analog Sync Separator" for detail.

• A656HS / B656HS

These pins serve as <u>output</u> hyper pins that are extracted from input video in ITU-BT-656 format. They can be used by external devices which need hyper signal for other timing purposes.

4.4.2.6 ASOY\_G+, ASOY\_G-BSOY\_G+, BSOY\_G-

These are differential <u>input</u> sync pins for analog input video with sync signals embedded on green or Y channel. The embedded sync signals will be extracted by the built-in sync separator and can be routed internally to the ASHS / BSHS (for hsync) pins and ASVS / BSVS (for vsync) pins.

4.4.2.7 ARAWHS\_CS (ASHS) BRAWHS\_CS (BSHS)

• ARAWHS\_CS / BRAWHS\_CS (Default)

These pins serve as the raw (unprocessed)  $\underline{input}$  hsync / composite sync pins and they are used for input format measurement

• ASHS / BSHS

These pins serve as <u>output</u> hyper pins that are extracted from input video with embedded sync on green or Y channel (SOG or SOY).

#### 4.4.2.8 AHREF\_DE BHREF\_DE

These are <u>input</u> signals which indicate the presence of active video pixels in a line. HREF signals are usually present in video decoders and DE (Data Enable) signals are usually present in TMDS receivers. All pixels located at the inactive region of these signals are ignored and not processed.

#### 4.4.2.9 ADATA [23:0] BDATA [23:0]

These are the input video data bus for each port. Video data can be connected to different buses of the same input port. See "Input Port Selection" section for configuration.

ADATA [23:17] and BDATA[23:17] can also be used to interface with external character based OSD (On Screen Display) devices. See next section for details in OSD interface.

#### NOTE:

When the digital output port is set to output 10-bit per channel RGB or YCbCr 4:4:4 format, BDATA[23:18] will be used as the 2 LSB bits (bit 1 and bit 0) of 10-bit data, as follows:

| •         |            | • •                   |

|-----------|------------|-----------------------|

|           | 30-bit RGB | 30-bit 4:4:4<br>YCbCr |

| BDATA[23] | G[1]       | Y[1]                  |

| BDATA[22] | G[0]       | Y[0]                  |

| BDATA[21] | B[1]       | Cb[1]                 |

| BDATA[20] | B[0]       | Cb[0]                 |

| BDATA[19] | R[1]       | Cr[1]                 |

| BDATA[18] | R[0]       | Cr[0]                 |

#### Table 12. Input Port B bit[23..18] used as output pins

As a result, the input video format that can be applied to input port B is limited to a maximum of 16 bits wide data.

#### 4.4.2.10 AOVACTIV, AOVCLK, AOVVS, AOVHS, AOVCOL [2:0] BOVACTIV, BOVCLK, BOVVS, BOVHS, BOVCOL [2:0]

These are the pins used for interface to external character based OSD devices (such as Motorola MC141544, etc.). These pins are multiplexed with ADATA[23:17] / BDATA [23:17] and when they are used as OSD interface, the number of video format supported in the corresponding input port will be limited..

| Input Port A | Input Port B | OSD in Port A | OSD in Port B | OSD Function         |

|--------------|--------------|---------------|---------------|----------------------|

| ADATA[17]    | BDATA[17]    | AOVACTIV      | BOVACTIV      | OSD active indicator |

| ADATA[18]    | BDATA[18]    | AOVCLK        | BOVCLK        | OSD pixel clock      |

| ADATA[19]    | BDATA[19]    | AOVVS         | BOVVS         | OSD vsync            |

| ADATA[20]    | BDATA[20]    | AOVHS         | BOVHS         | OSD hsync            |

| ADATA[21]    | BDATA[21]    | AOVCOL[0]     | BOVCOL[0]     | OSD color data [0]   |

| ADATA[22]    | BDATA[22]    | AOVCOL[1]     | BOVCOL[1]     | OSD color data [1]   |

| ADATA[23]    | BDATA[23]    | AOVCOL[2]     | BOVCOL[2]     | OSD color data [2]   |

Table 13.

Input Port pins for OSD interface

Note that although both Port A and Port B have overlay interface, only one can be used at a time.

#### 4.4.3 Input Video Formats

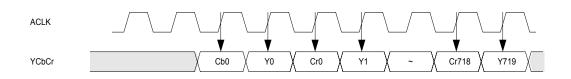

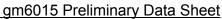

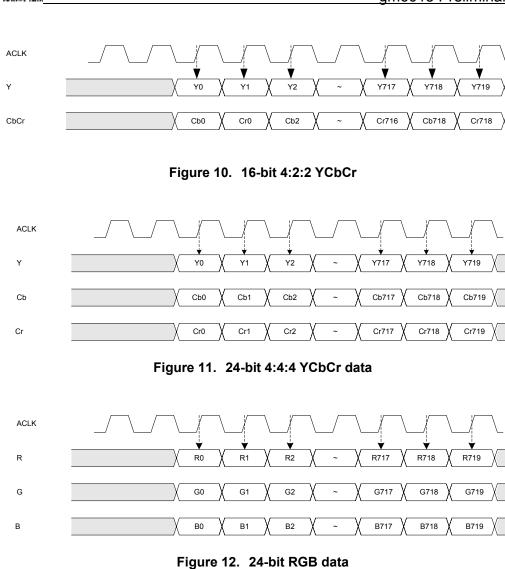

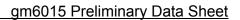

The following video formats are supported by gm6015 input ports :

- ITU-BT-656

- 8-bit 4:2:2 YCbCr

- 16-bit 4:2:2 YCbCr

- 24-bit 4:4:4 YCbCr

- 24-bit RGB

The timing of these video formats are shown in the following figures :

Figure 9. 8-bit 4:2:2 YCbCr

#### 4.4.4 Input Sync Processing

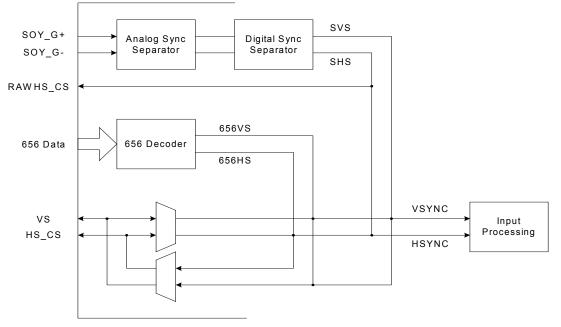

For input video without separate sync signals, gm6015 has built-in 656 decoder and sync separator to extract embedded sync information. These extracted sync signals can be routed to external pins to be used by external logic for other timing purposes. The figure below illustrates how embedded syncs are extracted and routed to external pins.

GENESIS

Figure 13. Embedded Sync Extraction

#### 4.4.4.1 **656 Decoder**

ITU-BT-656 video format consists of pixel clock and 8 bits of data. No separate hsync, vsync and odd signals are present. Timing data is embedded in the data stream. The internal 656 decoder will extract the hsync, vsync and odd signals from the embedded timing data. The extracted hsync and vsync can be routed internally to A656HS / B656HS and A656VS / B656VS pins.

#### 4.4.4.2 Analog Sync Separator

For video format with sync signals embedded on the analog video data, gm6015 built-in analog sync separator can extract the embedded sync signals. Bi-level and tri-level sync are supported. The analog sync separator acts as a "sync slicer" to the analog signal and generates digital composite sync signal to be processed by the digital sync separator.

For details in the operation of analog sync separator, please see "gm6010/6015 Hardware Theory of Operation"

#### 4.4.4.3 **Digital Sync Separator**

The digital sync separator takes the digital composite sync signal generated from analog sync separator and output separate hsync and vsync signals. The generated hsync signal is of constant period which means all equalization pulses are eliminated.

In addition, the digital sync separator also provides measurement and status on sync signals to the host interface.

For details in the operation of digital sync separator, please see "gm6010/6015 Hardware Theory of Operation"

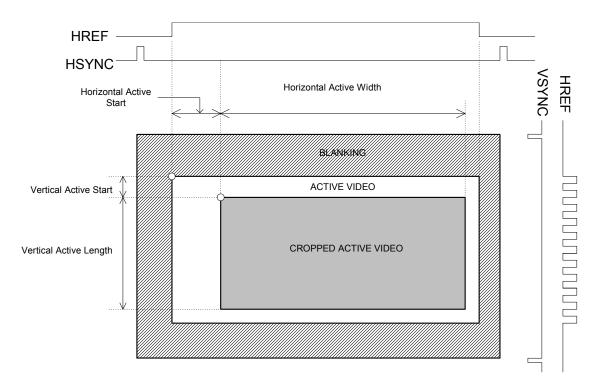

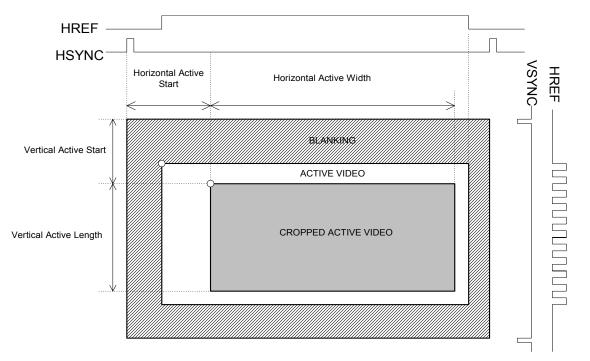

#### 4.4.5 Input Capture Window

Figure 14 and Figure 15 illustrate the input capture window with active and cropped video. Note that the horizontal and vertical start location is controlled by how bit 2 of *IP\_MISC\_CTRL* register is set:

• *IP\_MISC\_CTRL* bit 2 = 0 (HREF\_DE signal disabled)

The horizontal start location is the number of clocks (qualified by CREF) from the leading edge of HSYNC to the 1<sup>st</sup> active pixel.

The vertical start location is the number of lines from the leading edge of VSYNC to the 1<sup>st</sup> active line.

• *IP\_MISC\_CTRL* bit 2 = 1 (HREF\_DE signal enabled)

The horizontal start location is the number of clocks (qualified by CREF) from the leading edge of HREF to the 1<sup>st</sup> active pixel.

The vertical start location is the number of lines from the leading edge of the 1<sup>st</sup> HREF after VSYNC to the 1<sup>st</sup> active line.

Figure 14. Input Capture Window (HREF/DE enabled)

gm6015 Preliminary Data Sheet

Figure 15. Input Capture Window (HREF/DE disabled)

Input cropping is supported by means of programming the start location and active width/length. The video data that gm6015 will process is the portion named "Cropped Active Video" in Figure 14 and Figure 15.

#### 4.4.6 Input Format Measurement

The gm6015 has an Input Format Measurement block (IFM) providing the capability of measuring the horizontal and vertical timing parameters of the input video source. This information may be used to determine the video format and to detect a change in the input format.

Horizontal measurements are measured in terms of the selected IFM\_CLK, while vertical measurements are measured in terms of HSYNC pulses.

#### 4.4.6.1 Measurement

The IFM is able to measure the horizontal period and active high pulse width of the HSYNC signal, in terms of the selected clock. Horizontal measurements are performed on only a single line per frame (or field). The line used is programmable. It is able to measure the vertical period and VSYNC pulse width in terms of rising edges of HSYNC. When using composite sync input, these measurements use the internally synthesized HSYNC and VSYNC signals.

Once enabled, measurement begins on the rising VSYNC and is completed on the following rising VSYNC. The measurement will stop after it is completed unless enabled again.

#### 4.4.6.2 Format Change Detection

The IFM is able to detect changes in the input format relative to the last measurement and then alert the system microcontroller. The microcontroller can set a measurement difference threshold separately for horizontal and vertical timing. If the current field / frame timing is different from the previously captured measurement by an amount exceeding this threshold, a status bit is set. An interrupt can also be programmed to occur.

#### 4.4.6.3 Watchdog and Activity Monitoring

The watchdog monitors input VSYNC and HSYNC signals. When any HSYNC period exceeds the programmed timing threshold (in terms of the selected IFM\_CLK), a register bit is set. When any VSYNC period exceeds the programmed timing threshold (in terms HSYNC pulses), another register bit is set. An interrupt can also be programmed to occur.

In addition to the watchdog, there is an activity monitoring circuit that can detect presence of activity in MAIN input, PIP input, display, image processor and SDRAM.

#### 4.4.7 Wide Screen Signal (WSS) decoding

gm6015 has built-in WSS decoder that can extract the data encoded in the vertical blanking intervals (VBI) and store it in host registers. The decoder is programmable so that various standards of VBI data can be decoded. The following are VBI data standards that gm6015 supports:

- EIAJ-CPR 1204-1

- IEC 61880

- EIA-805

#### 4.5 **Output Interface**

gm6015 digital output port provides glueless interface to common DAC, video encoder and deflection processor. It can also interface directly to single width RGB LCD panels. gm6015 provides 24 bit output data bus for digital video output. It can also support a total of 30 bits data (such as 30-bit RGB and 30-bit YCbCr 4:4:4 formats) by using part of input port B (BDATA[23:18]) as output data bits.

#### 4.5.1 **Output Signals**

The following are data and control signals associated with the digital output port.

#### 4.5.1.1 **DDATA[23:0]**

These are the digital output data pins. Various output format uses different part of the data bus, as shown in the table below:

|           | 8-bit 4:2:2<br>YCbCr / 656 | 16-bit 4:2:2<br>YCbCr | 20-bit 4:2:2<br>YCbCr | 18-bit 4:4:4<br>RGB | 24-bit 4:4:4<br>YCbCr | 24bit 4:4:4<br>RGB | 30-bit 4:4:4<br>YCbCr | 30-bit 4:4:4<br>RGB |

|-----------|----------------------------|-----------------------|-----------------------|---------------------|-----------------------|--------------------|-----------------------|---------------------|

| DDATA[23] | Х                          | Х                     | Х                     | R[5]                | Cr[7]                 | R[7]               | Cr[9]                 | R[9]                |

| DDATA[22] | Х                          | Х                     | Х                     | R[4]                | Cr[6]                 | R[6]               | Cr[8]                 | R[8]                |

| DDATA[21] | Х                          | Х                     | Х                     | R[3]                | Cr[5]                 | R[5]               | Cr[7]                 | R[7]                |

| DDATA[20] | Х                          | Х                     | Х                     | R[2]                | Cr[4]                 | R[4]               | Cr[6]                 | R[6]                |

| DDATA[19] | Х                          | Х                     | CbCr[1]               | R[1]                | Cr[3]                 | R[3]               | Cr[5]                 | R[5]                |

| DDATA[18] | Х                          | Х                     | CbCr[0]               | R[0]                | Cr[2]                 | R[2]               | Cr[4]                 | R[4]                |

| DDATA[17] | Х                          | Х                     | Y[1]                  | Х                   | Cr[1]                 | R[1]               | Cr[3]                 | R[3]                |

| DDATA[16] | Х                          | Х                     | Y[0]                  | х                   | Cr[0]                 | R[0]               | Cr[2]                 | R[2]                |

| DDATA[15] | Х                          | CbCr[7]               | CbCr[9]               | B[5]                | Cb[7]                 | B[7]               | Cb[9]                 | B[9]                |

| DDATA[14] | Х                          | CbCr[6]               | CbCr[8]               | B[4]                | Cb[6]                 | B[6]               | Cb[8]                 | B[8]                |

| DDATA[13] | Х                          | CbCr[5]               | CbCr[7]               | B[3]                | Cb[5]                 | B[5]               | Cb[7]                 | B[7]                |

| DDATA[12] | Х                          | CbCr[4]               | CbCr[6]               | B[2]                | Cb[4]                 | B[4]               | Cb[6]                 | B[6]                |

| DDATA[11] | Х                          | CbCr[3]               | CbCr[5]               | B[1]                | Cb[3]                 | B[3]               | Cb[5]                 | B[5]                |

| DDATA[10] | Х                          | CbCr[2]               | CbCr[4]               | B[0]                | Cb[2]                 | B[2]               | Cb[4]                 | B[4]                |

| DDATA[9]  | Х                          | CbCr[1]               | CbCr[3]               | Х                   | Cb[1]                 | B[1]               | Cb[3]                 | B[3]                |

| DDATA[8]  | Х                          | CbCr[0]               | CbCr[2]               | х                   | Cb[0]                 | B[0]               | Cb[2]                 | B[2]                |

| DDATA[7]  | YCbCr[7]                   | Y[7]                  | Y[9]                  | G[5]                | Y[7]                  | G[7]               | Y[9]                  | G[9]                |

| DDATA[6]  | YCbCr[6]                   | Y[6]                  | Y[8]                  | G[4]                | Y[6]                  | G[6]               | Y[8]                  | G[8]                |

| DDATA[5]  | YCbCr[5]                   | Y[5]                  | Y[7]                  | G[3]                | Y[5]                  | G[5]               | Y[7]                  | G[7]                |

| DDATA[4]  | YCbCr[4]                   | Y[4]                  | Y[6]                  | G[2]                | Y[4]                  | G[4]               | Y[6]                  | G[6]                |

| DDATA[3]  | YCbCr[3]                   | Y[3]                  | Y[5]                  | G[1]                | Y[3]                  | G[3]               | Y[5]                  | G[5]                |

| DDATA[2]  | YCbCr[2]                   | Y[2]                  | Y[4]                  | G[0]                | Y[2]                  | G[2]               | Y[4]                  | G[4]                |

| DDATA[1]  | YCbCr[1]                   | Y[1]                  | Y[3]                  | х                   | Y[1]                  | G[1]               | Y[3]                  | G[3]                |

| DDATA[0]  | YCbCr[0]                   | Y[0]                  | Y[2]                  | х                   | Y[0]                  | G[0]               | Y[2]                  | G[2]                |

| BDATA[23] | Х                          | Х                     | Х                     | Х                   | Х                     | Х                  | Y[1]                  | G[1]                |

| BDATA[22] | Х                          | Х                     | Х                     | Х                   | Х                     | Х                  | Y[0]                  | G[0]                |

| BDATA[21] | Х                          | Х                     | Х                     | Х                   | Х                     | Х                  | Cb[1]                 | B[1]                |

| BDATA[20] | Х                          | Х                     | X                     | Х                   | Х                     | Х                  | Cb[0]                 | B[0]                |

| BDATA[19] | Х                          | х                     | Х                     | Х                   | Х                     | Х                  | Cr[1]                 | R[1]                |

| BDATA[18] | Х                          | Х                     | Х                     | Х                   | Х                     | Х                  | Cr[0]                 | R[0]                |

**Note:** The pin locations of 2 LSB bits for formats with 10 bits per channel. For 30-bit 4:4:4 YCbCr and RGB, the 2 LSB bits are located on the Input Port B BDATA[23:18].

#### 4.5.1.2 **DCLK**

This is the display pixel clock. The internal DDS can be programmed to generate a wide range of frequency for various output video format and resolution.

A secondary display clock (DCLK2) can be programmed to output at GPIO pins.

Both DCLK and DCLK2 can be programmed to be equal to or half of DDS output frequency. The polarity and delay of DCLK and DCLK2 are programmable.

#### 4.5.1.3 **DVS (DSYNCT)**

• DVS

This is the display vsync. It can be selected from the internal reference vsync or as a fully programmable vsync. Programmable vsync is recommended.

• DSYNCT

This is the tri-level sync control signal. It can be applied to external DACs which are able to generate tri-level sync.

Figure 16. Relationship between DHS\_CS and DSYNCT

#### 4.5.1.4 **DHS\_CS**

This is the display hypro or composite sync pin. It can be selected from the internal reference hypro or a fully programmable hypro / composite sync.

#### 4.5.1.5 **DODD (GPIO0)**

• DODD (Default)

The is the output odd / even field indicator.

• GPIO0

For progressive output, this pin can be configured to a general purpose I / O pin.

NOTE that this pin is a GPIO pin with default to the function of output field indicator.

4.5.1.6 **DDE\_BLANK**

This is the display data enable / blanking and it marks the active data in a line.

#### 4.5.2 656 Encoder

gm6015 has built-in 656 encoder which encode the display video data into format as described in ITU-R BT.656 specification. The timing signals are embedded into the data stream and are also available on the corresponding pins at the same time.

#### 4.5.3 VBI Data Insertion

Digital Data can be inserted into the VBI area at the output. Information of the data, such as line number, field (odd / even), start pixel number, data width (upto 24 bits)...etc, are programmable with host registers.

#### 4.5.4 **Output Video Formats**

gm6015 can output digital video data in the following formats :

- ITU-BT-656

- 8-bit 4:2:2 YCbCr (8-bit bus with Y, Cb and Cr)

- 12-bit 4:2:2 YCbCr (6-bit bus with Y, 6-bit bus with CbCr)

- 16-bit 4:2:2 YCbCr (8-bit bus with Y, 8-bit bus with CbCr)

- 20-bit 4:2:2 YCbCr (10-bit bus with Y, 10-bit bus with CbCr)

- 18-bit 4:4:4 YCbCr (6-bit bus with Y, 6-bit bus with Cb, 6-bit bus with Cr)

- 24-bit 4:4:4 YCbCr (8-bit bus with Y, 8-bit bus with Cb, 8-bit bus with Cr)

- 30-bit 4:4:4 YCbCr (10-bit bus with Y, 10-bit bus with Cb, 10-bit bus with Cr)

- 18-bit RGB (6-bit bus with R, 6-bit bus with G, 6-bit bus with B)

- 24-bit RGB (8-bit bus with R, 8-bit bus with G, 8-bit bus with B)

- 30-bit RGB (10-bit bus with R, 10-bit bus with G, 10-bit bus with B)

For output timing, the gm6015 display timing generator is fully programmable to generate arbitrary timing including (but not limit to) the following:

- All VESA VGA modes

- All VESA SVGA modes

- VESA XGA modes except XGA @ 85Hz

- All SDTV video modes (e.g. NTSC, PAL)

- All EDTV video modes (e.g. 720x480p, 720x576p)

- HDTV video modes except 1920x1080 progressive modes

- PDP modes (852x480p and 1366x768p)

- Others (e.g. 100Hz PAL, ...)

#### 4.5.5 Video Look Up Table

A video look up table (VLUT) is implemented as three 256 x 10-bit RAM tables, one for each color channel. The output of VLUT can be programmed to be 8-bit or 10-bit per color and loading of data into VLUT can be programmed to happen during blanking interval.

The look up table serves the purposes of :

Gamma correction

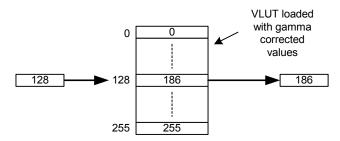

3 tables of non-linear (gamma corrected) values are loaded into the VLUT, one for each color. Pixel values from the mixer output is mapped to the corresponding tables and a gamma corrected value is output from the table. Figure 17 below is a simplified illustration of gamma correction of 8-bit input/output VLUT.

Figure 17. Gamma correction

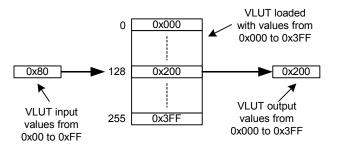

• Mapping of 8-bit data to 10-bit data

gm6015 processes data in 8 bits. VLUT can be used to map the 8-bit processed data to 10-bit output by loading the VLUT with values from 0x000 to 0x3FF.

Figure 18. 8-bit to 10-bit mapping

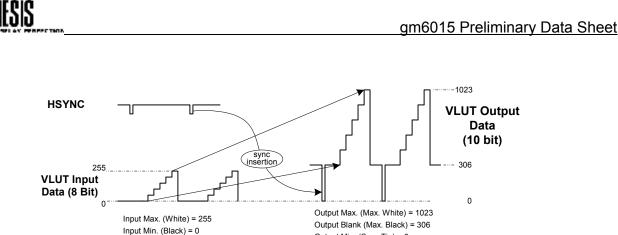

• Pre-scale of digital video data

If gm6015 output is connected to external device with sync insertion, the output data can be prescaled so as to ensure a correct output range after sync insertion.

Figure 19. Pre-scale of data for sync insertion (with 8-bit to 10-bit mapping)

Output Min. (Sync Tip) = 0

The 3 VLUT functions mentioned above can be achieved by a single set of VLUT values. Genesis provides a Window application program to help calculating the correct values needed.

For details of VLUT loading, please refer to "gm6010/6015 register programming guide".

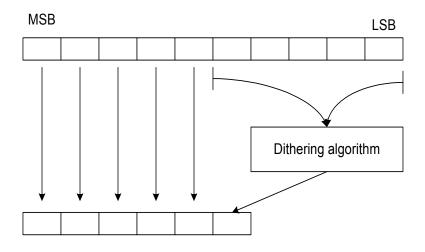

#### 4.5.6 **Dithering**

The output data from the VLUT can be dithered down to 8-bit / 6-bit per color. Dithering is done by processing the LSBs of data through a dithering algorithm and generates the LSB of the output (Figure 20). Both random dithering and programmable ordered dithering are supported.

Figure 20. 10-bit to 6-bit dithering

#### 4.5.7 **Output Configuration**

The MAIN and PIP channel (and OSD, if present) are mixed together at the output. Moreover, multiple PIP channels can be configured at the output. 16 levels of alpha blending is available for mixing of

MAIN and PIP display. gm6015 allows a very flexible multiple PIP display configuration as described below.

# 4.5.7.1 Output Timing

The output timing can be configured by programming the following parameters:

- 1. Total output resolution. This is the number of total horizontal pixel per line and the number of total vertical lines per field / frame. Blanking regions are included.

- 2. Background resolution. This is the area where programmable background color will be displayed to fill the gap between active display window and blanking region.

- 3. MAIN channel resolution. This is the number of horizontal active pixels per line and number of vertical active lines per field / frame of the MAIN channel.

- 4. PIP channel resolution. This is the number of horizontal active pixels per line and number of vertical active lines per field / frame of the PIP channel. For single PIP display, the size of PIP display can be configured to be any size up to a maximum of <sup>1</sup>/<sub>3</sub> of MAIN display size. For multiple PIP display, each PIP display window will have the same size.

Figure 21. Output Display Windows

#### 4.5.7.2 PIP Display

gm6015 allows a very flexible PIP display configuration. PIP display can be configured as single PIP or multiple PIPs. A PIP border with programmable color and size is available. Moreover, in the case of multiple PIPs, a hi-light border can be created so as to show the active PIP window. Figure 22 shows examples of various PIP configurations

Single PIP allows the PIP display to be placed arbitrarily in the display window. It can be placed within the MAIN display (Figure 22a), partially overlapped with MAIN display (Figure 22c) or fully detached from MAIN display (Figure 22d). The size of the PIP display is fully programmable. Also, single PIP display allows 16 levels of alpha blending within the PIP window.

A special case of single PIP display is side-by-side configuration (Figure 22b). In this case the MAIN and PIP are put side by side in the display

Multiple PIPs display allows a maximum of 16 PIP windows to be displayed at the same time. MAIN and one PIP window will be running at real time. In multiple PIP display each PIP window will be of the same size and is fully opaque. Figure 22(e) to (h) illustrate some examples of multiple PIP configurations.

If OSD interface is used, the OSD can be overlayed on top of the MAIN and PIP display windows.

# gm6015 Preliminary Data Sheet

(a) Fully overlapped

(c) Partially overlapped

(e) 2 x 2 multi PIPs

(g) Irregular multi PIPs

(b) Side-by-side

(d) Detached

(f) Ring-shaped multi PIPs

(h) Tiled multi PIPs

# Figure 22. Examples of Different PIP Configurations

# 4.6 Color Space Conversion (CSC)

All video data is processed internally in YCbCr 4:2:2 format. Input video data is converted to YCbCr 4:2:2 format, if necessary, for processing and then converted to the desired output video format.

## 4.6.1 Input CSC

Input color space conversion is provided in each input data path to convert input video data to YCbCr 4:2:2.

For input in RGB format, it is first converted to YCbCr 4:4:4 format using a transformation matrix and then downsampled to 4:2:2 by decimation filter.

For input in YCbCr 4:4:4 format, the transformation matrix is bypassed and the data is downsampled to 4:2:2 by decimation filter.

The equation used in the RGB to YCbCr transformation matrix is :

$YCbCr = (R\_COEFF * R + G\_COEFF * G + B\_COEFF * B + OFFSET) / 256$