# FLASH MEMORY cmos

# 128 M (16 M × 8) BIT NAND-type MBM30LV0128

### DESCRIPTION

The MBM30LV0128 device is a single 3.3 V 16 M × 8 bit NAND flash memory organized as 528 byte × 32 pages × 1024 blocks. Each 528 byte page contains 16 bytes of optionally selected spare area which may be used to store ECC code (Specifications indicated are on condition that ECC system would be combined) . Program and read data is transferred between the memory array and page register in 528 byte increments. A 528 byte page can be programmed in 200  $\mu$ s and an 16 K byte block can be erased in 2 ms under typical conditions. An internal controller automates all programs and erases operations including the verification of data margins. Data within a page can be read with a 50 ns cycle time per byte. The I/O pins are utilized for both address and data input/output as well as command inputs. The MBM30LV0128 is an ideal solution for applications requiring mass non-volatile storage such as solid state file storage, digital recording, image file memory for still cameras, and other uses which require high density and non-volatile storage.

### PRODUCT LINE UP

|                          | Part No.        | MBM30LV0128      |  |

|--------------------------|-----------------|------------------|--|

| Operating Temperature    |                 | −40 °C to +85 °C |  |

| Vcc                      |                 | +2.7 V to +3.6 V |  |

|                          | Read            | 72 mW            |  |

| Rower Dissipation (Max)  | Erase / Program | 72 mW            |  |

| Power Dissipation (Max.) | TTL Standby     | 3.6 mW           |  |

|                          | CMOS Standby    | 0.18 mW          |  |

### ■ FEATURES

- 3.3 V-only operating voltage (2.7 V to 3.6 V) Minimizes system level power requirements

- Organization Memory Cell Array : (16 M + 512 K) × 8 bit Data Register : (512 + 16) × 8 bit

- Automatic Program and Erase Page Program : (512 + 16) Byte Block Erase : (16 K + 512) Byte

- 528 Byte Page Read Operation Random Access : 10 μs (Max.) Serial Access : 35 ns (Max.)

- Fast Program and Erase Program Time : 200 µs (Typ.) / page Block Erase Time : 2 ms (Typ.) / block

- Command/Address/Data Multiplexed I/O Port

- Hardware Data Protection

- 1,000,000 write/erase cycles guaranteed (ECC system required)

- Command Register Operation

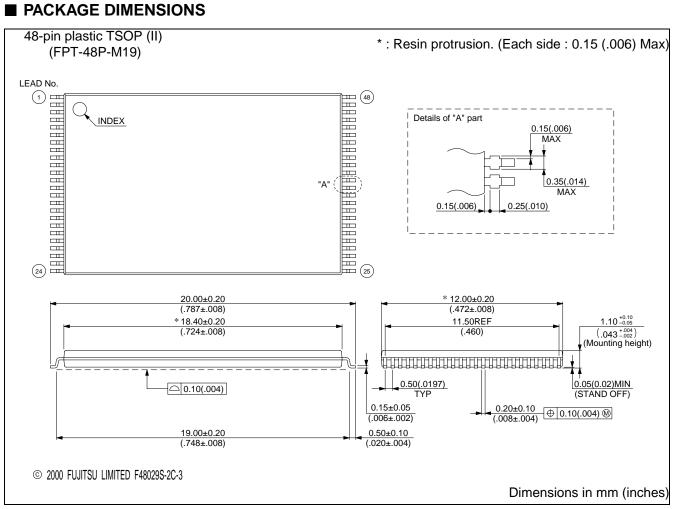

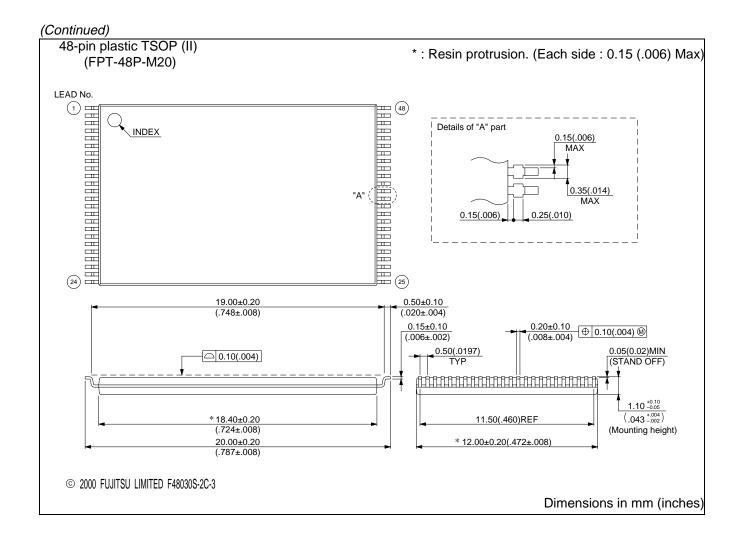

- Package

48-pin TSOP Type I (0.5 mm pitch)

Normal/Reverse Type

- Data Retention : 10 years

### PACKAGES

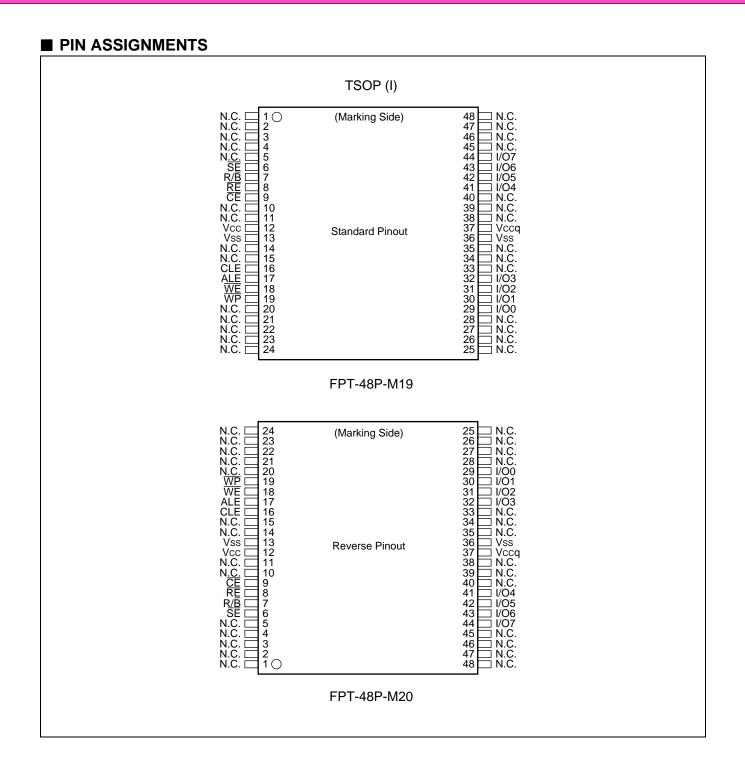

### ■ PIN FUNCTIONS

| PIN Number           | Pin Name     | Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29 to 32<br>41 to 44 | I/O0 to I/O7 | Data Input/Output :<br>The I/O ports are used for transferring command, address, and input/output data<br>into and out of the device. The I/O pins will be high impedance when the outputs<br>are disabled or the device is not selected.                                                                                                                                                                      |

| 16                   | CLE          | Command Latch Enable :<br>The CLE signal enables the acquisition of the mode command into the internal command register. When $CLE = "H"$ , command is latched into the command register from the I/O port upon the rising edge of the $\overline{WE}$ signal.                                                                                                                                                 |

| 17                   | ALE          | Address Latch Enable :<br>The ALE signal enables the acquisition of either addresses or data into the inter-<br>nal address/data register. The rising edge of $\overline{\text{WE}}$ will latch in addresses when<br>ALE is high and data when ALE is low.                                                                                                                                                     |

| 9                    | CE           | Chip Enable :<br>The $\overline{CE}$ signal is used to select the device. When $\overline{CE}$ is high, the device enters<br>a low power standby mode. If $\overline{CE}$ transitions are high during a read operation,<br>the standby mode will be entered. However, the $\overline{CE}$ signal is ignored if the device<br>is in a busy state ( $R/\overline{B}$ = "L") during a program or erase operation. |

| 8                    | RE           | Read Enable :<br>The $\overline{\text{RE}}$ signal controls the serial data output. The falling edge of $\overline{\text{RE}}$ drives the data onto the I/O bus and increments the column address counter by one.                                                                                                                                                                                              |

| 18                   | WE           | Write Enable : The $\overline{WE}$ signal controls write from the I/O port. Data, address, and commands on the I/O port are latched upon the rising edge of the $\overline{WE}$ pulse.                                                                                                                                                                                                                         |

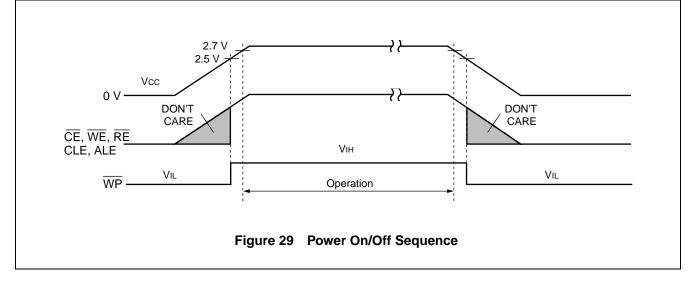

| 19                   | WP           | Write Protect :<br>The $\overline{WP}$ signal protects the device against accidental erasure or programming<br>during power up/down by disabling the internal high voltage generators. $\overline{WP}$<br>should be kept low when the device powers up until Vcc is above 2.5 V. During<br>power down, $\overline{WP}$ should be low when Vcc falls below 2.5 V.                                               |

| 6                    | SE           | Spare Area Enable :<br>The SE input enables the spare area during sequential data input, page program,<br>and Read 1.                                                                                                                                                                                                                                                                                          |

| 7                    | R/B          | Ready Busy Output :<br>The R/ $\overline{B}$ output signal is used to indicate the operating status of the device. Dur-<br>ing program, erase, or read, R/ $\overline{B}$ is low and will return high upon the completion<br>of the operation. The output buffer for this signal is an open drain.                                                                                                             |

| 37                   | Vccq         | Output Buffer Power Supply :<br>The $V_{ccq}$ input supplies the power to the I/O interface logic. This power line is<br>electrically isolated from $V_{cc}$ for the purpose of supporting 5 V tolerant I/O.                                                                                                                                                                                                   |

(Continued)

(Continued)

| PIN Number                                                                             | Pin Name | Pin Functions  |

|----------------------------------------------------------------------------------------|----------|----------------|

| 12                                                                                     | Vcc      | Power Supply   |

| 13, 36                                                                                 | Vss      | Ground         |

| 1 to 5<br>10, 11<br>14, 15<br>20 to 24<br>25 to 28<br>33 to 35<br>38 to 40<br>45 to 48 | N.C.     | Non Connection |

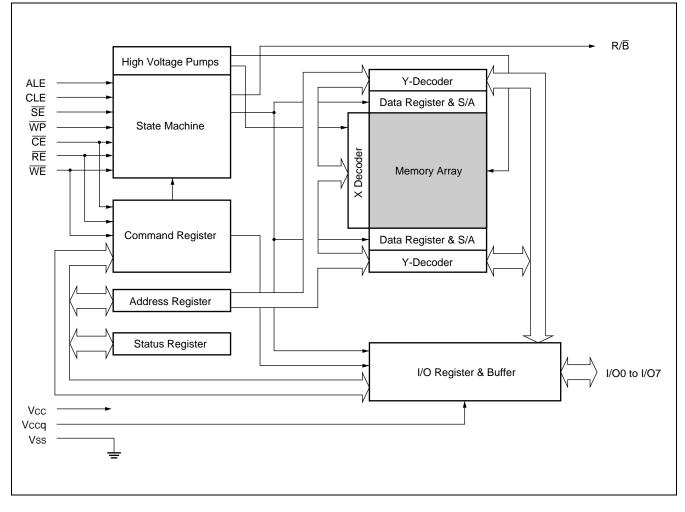

### BLOCK DIAGRAM

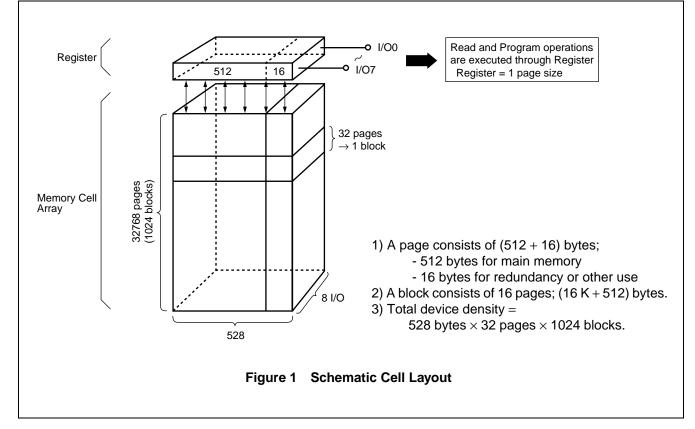

### ■ SCHEMATIC CELL LAYOUT AND ADDRESS ASSIGNMENT

The Program operation is implemented in page units while the Erase operation is carried out in block units.

| Table 1 | Addressing |

|---------|------------|

|---------|------------|

|              | I/O0 | I/O1            | I/O2            | I/O3            | I/O4            | I/O5           | I/O6           | I/07            |

|--------------|------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|-----------------|

| First Cycle  | Ao   | A1              | A <sub>2</sub>  | A3              | A4              | A <sub>5</sub> | A <sub>6</sub> | A7              |

| Second Cycle | A9   | A10             | A <sub>11</sub> | A <sub>12</sub> | A13             | A14            | A15            | A <sub>16</sub> |

| Third Cycle  | A17  | A <sub>18</sub> | A19             | A <sub>20</sub> | A <sub>21</sub> | A22            | A23            | Х*              |

A<sub>0</sub> to A<sub>7</sub> : column address

$A_9$  to  $A_{23}$ : page address  $\begin{cases} A_{14}$  to  $A_{23}$ : block address  $A_{23}$  is block address

$A_9$  to  $A_{13}$  : Page address in block

(As is automatically set to "Low" or "High" by the "00h" command or the "01h" command inside the device.) \* :  $X = V_{IH}$  or  $V_{IL}$

### DEVICE BUS OPERATIONS

|                               | Mode                          | CLE | ALE | CE | WE | RE | SE        | WP        |

|-------------------------------|-------------------------------|-----|-----|----|----|----|-----------|-----------|

| Read                          | Command Input                 | Н   | L   | L  | ٦£ | Н  | X *4      | Х         |

| Mode                          | Address Input (3 clocks)      | L   | Н   | L  | Ŀ  | Н  | X *4      | Х         |

| During Re                     | ad (Busy)                     | L   | L   | L  | Н  | Н  | L/H *3    | Х         |

| Sequential Read & Data Output |                               | L   | L   | L  | Н  | ₽Г | L/H *3    | Х         |

| Program/                      | Command Input                 | Н   | L   | L  | Ŀ  | Н  | X *4      | Н         |

| Erase<br>Mode                 | Address Input (2 or 3 clocks) | L   | н   | L  | Ŀſ | Н  | X *4      | Н         |

| Data Inpu                     | t                             | L   | L   | L  | זר | Н  | L/H *3    | Н         |

| During Pro                    | ogram (Busy)                  | Х   | Х   | Х  | Х  | Х  | L/H *3    | Н         |

| During Erase (Busy)           |                               | Х   | Х   | Х  | Х  | Х  | Х         | Н         |

| Write Protect                 |                               | Х   | Х   | Х  | Х  | Х  | Х         | L         |

| Stand-by                      |                               | Х   | Х   | Н  | Х  | Х  | 0 V/Vcc*2 | 0 V/Vcc*2 |

### Table 2 Operation Table \*1

\*1: H : VIH, L : VIL, X : VIH or VIL

\*2: WP should be biased to CMOS high or CMOS low for standby.

\*3: When  $\overline{SE}$  is high, spare area is deselected.

\*4: If 50h command is input and read/program operation is executed only for spare area,  $\overline{SE}$  must be low at the command/address input.

| Operation       | CLE | ALE | CE | WE | RE | I/O0 to I/O7   | Power Supply |

|-----------------|-----|-----|----|----|----|----------------|--------------|

| Output Select   | L   | L   | L  | Н  | L  | Data Output    | Active       |

| Output Deselect | L   | L   | L  | Н  | Н  | High Impedance | Active       |

| Standby         | Х   | Х   | Н  | Х  | Х  | High Impedance | Standby      |

Table 3 Read Mode Operation Status \*

\*:  $H: V_{IH}, L: V_{IL}, X: V_{IH} \text{ or } V_{IL}$

### ■ COMMAND OPERATION

| Function                                            | 1st Cycle | 2nd Cycle | Acceptable Command<br>During Busy State |

|-----------------------------------------------------|-----------|-----------|-----------------------------------------|

| Read (1)                                            | 00h *1    | —         |                                         |

| Read (2)                                            | 01h *2    |           |                                         |

| Read (3)                                            | 50h *3    | —         |                                         |

| Sequential Data Input                               | 80h       |           |                                         |

| Sequential Data<br>Imput for Double<br>Page Program | 82h       | _         |                                         |

| Page Program                                        | 10h       | —         |                                         |

| Block Erase                                         | 60h       | D0h       |                                         |

| Reset                                               | FFh       | —         | 0                                       |

| Status Read                                         | 70h       | —         | 0                                       |

| ID Read                                             | 90h       | —         |                                         |

### Table 4 Command Table

\*1: The 00h Command defines starting Address on the 1st half of the Page.

\*2: The 01h Command defines starting Address on the 2nd half of the Page.

\*3: The 50h Command is valid only When  $\overline{SE}$  is low level.

### FUNCTIONAL DESCRIPTION

### **READ MODE**

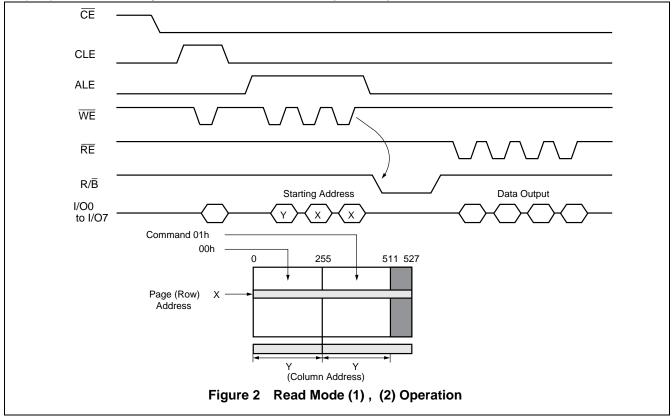

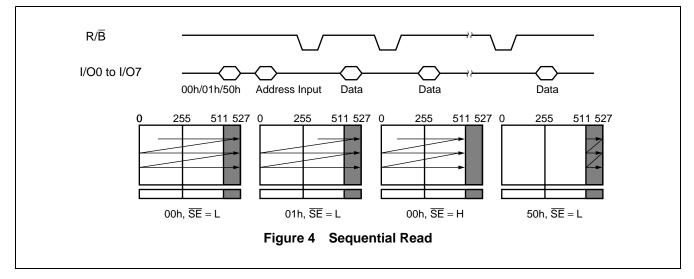

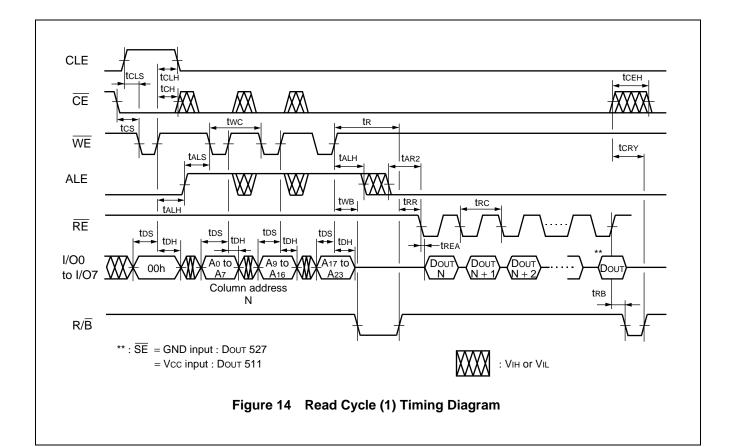

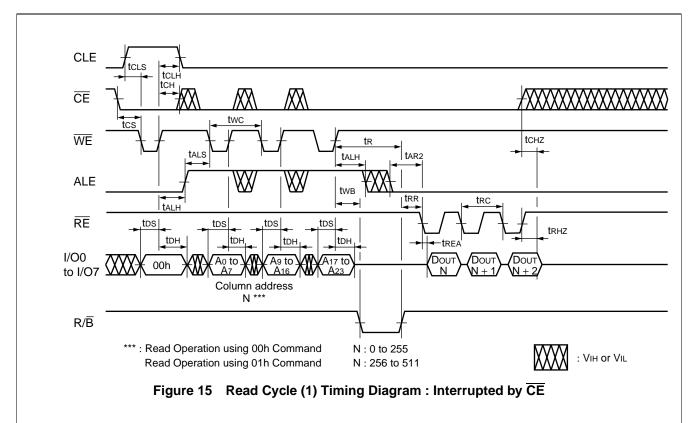

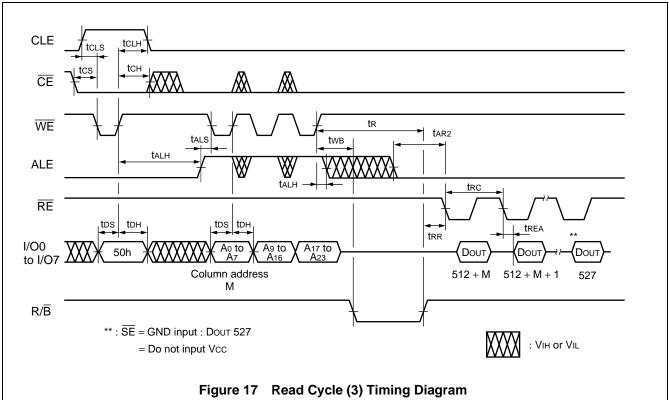

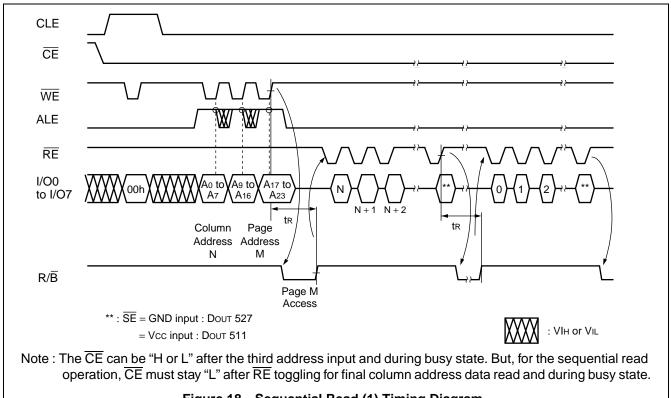

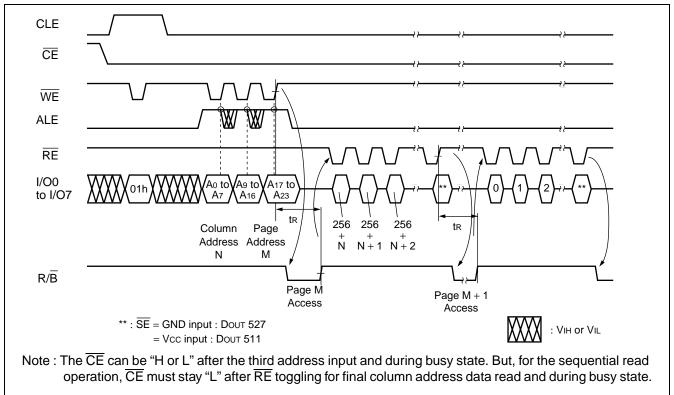

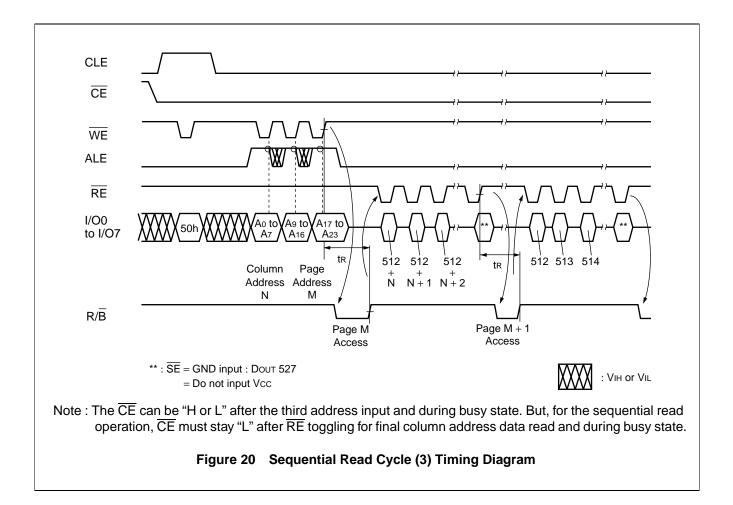

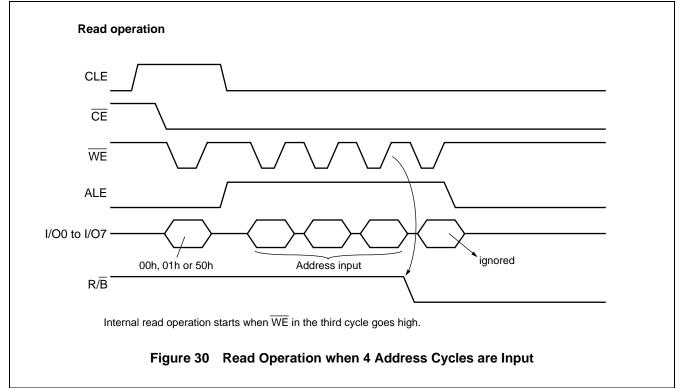

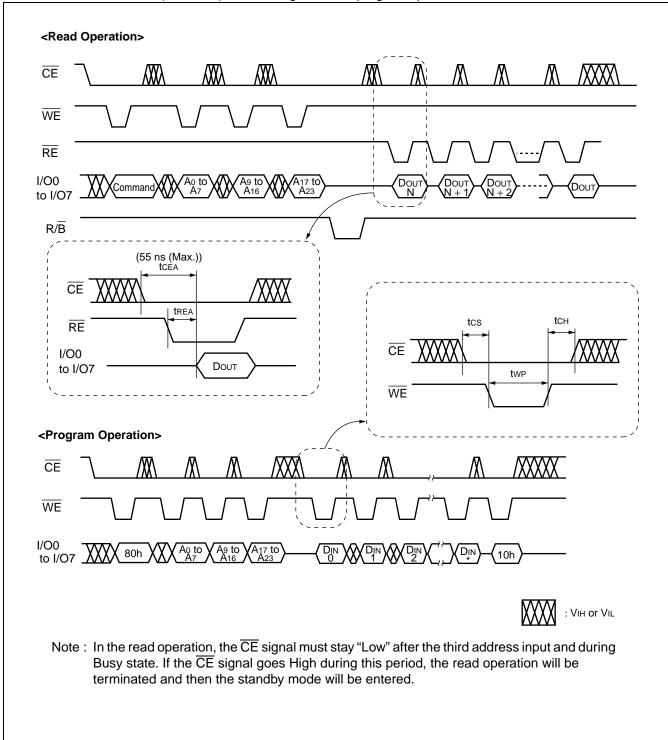

There are three distinct commands used for the read operation : 00h, 01h, and 50h. After the command cycle, three address cycles are used to input the starting address. Upon the rising edge of the final  $\overline{WE}$  pulse, there is a 10 µs latency in which the 528 byte page is transferred to the data register. The R/B signal may be used to monitor the completion of the data transfer. Once the data page has been loaded into the data register, it may be clocked out with consecutive 50 ns RE pulses. Each RE pulse will automatically advance the column address by one. Once the last column has been read, the page address will automatically increment by one and the data register will be updated with the new page after 10 µs. In this sequential read operation, the CE signal must stay "Low" after the third address input and during Busy state. If the CE signal goes High during this period, the read operation will be terminated and then the standby mode will be entered. (In the read operation, after read command and address input, the CE signal can be "Don't care" after the third address input and during Busy state.)

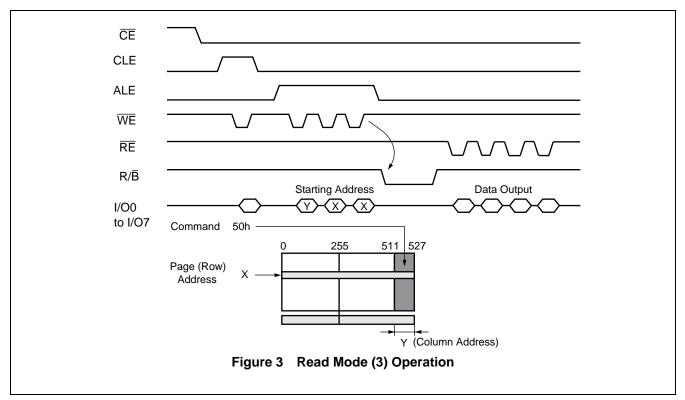

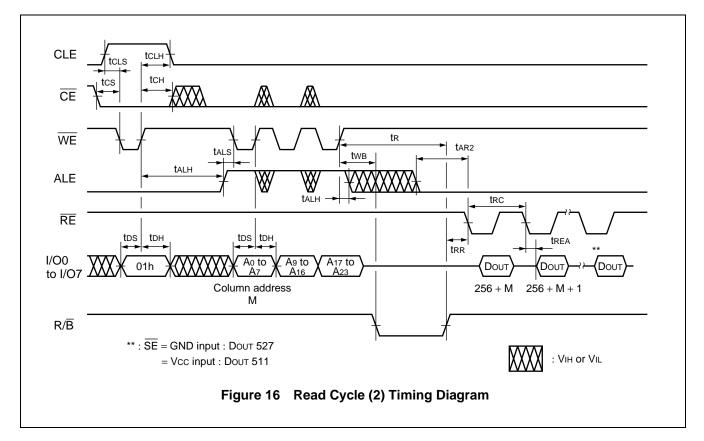

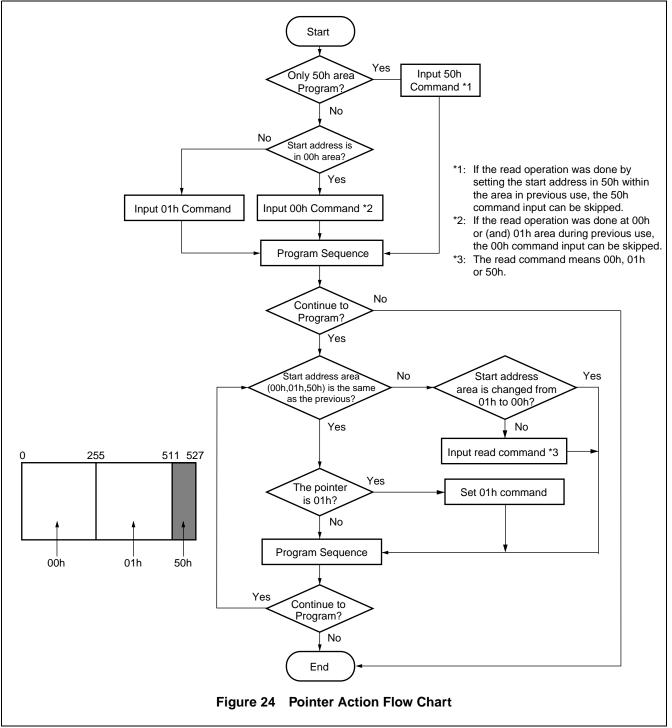

The 00h Read command will set the pointer to the first half of the page of the array while the 01h Read command sets it in the second half. It may be logical to think of 00h as a command which sets  $A_8 = 0$  while 01h sets  $A_8 = 1$ . The 50h command sets the pointer to the spare area, consisting of columns 512 to 527. During this read mode,  $A_3$  to  $A_0$  is used to set the starting address of the spare area. As with the 00h and 01h operations, once the spare area page is loaded into the data register, it may be read out by  $\overline{RE}$  pulses. Each  $\overline{RE}$  pulse will increment the column address until the final column (527) is reached. At this time, the pointer will be reset to column 512 while the page address is incriminated and the data register is updated. (In this sequential read operation also,  $\overline{CE}$  signal must stay "Low" after the third address input and during Busy state.) The 00h or 01h command is required to move the pointer back into the main array area.

#### Read (1), (2) : 00h/01h

The Read (1), (2) mode is invoked by latching the 00h or 01h command into the command register. This mode (00h) will automatically be selected when the device powers up.

### Read (3) : 50h

The Read (3) mode has identical timing to that of Read (1) and (2). However, while Read (1) and (2) are used to access the array, Read (3) is used to access the 16 byte spare area. When the 50h command is executed, the pointer will be set to an address space between columns 512 and 527. The values of Y will complete the address decoding. During this operation, only address bits  $A_3$  to  $A_0$  are used to determine the starting column address;  $A_7$  to  $A_4$  are ignored.  $A_{23}$  to  $A_9$  are used to determine the starting row address.

#### **Sequential Read**

Each  $\overline{RE}$  pulse used to output data from the data register will cause the column address pointer to increment by one. When the final column has been reached, the next page will be automatically loaded into the data register. The R/ $\overline{B}$  signal may be used to monitor the completion of the data transfer.

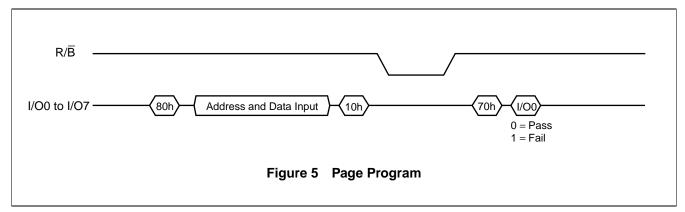

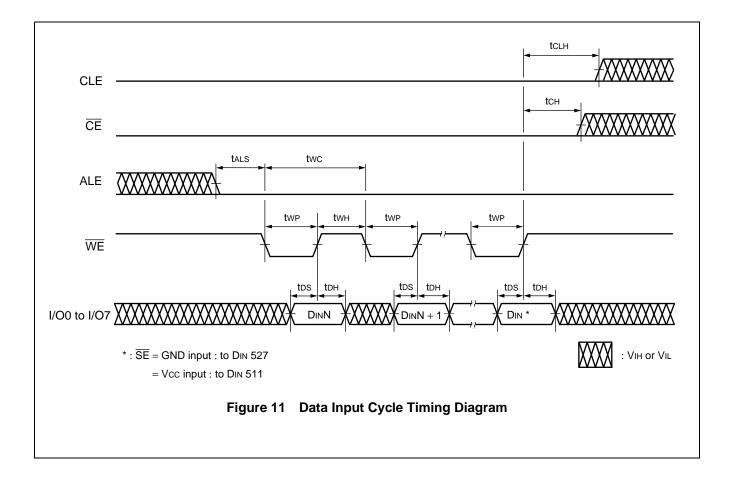

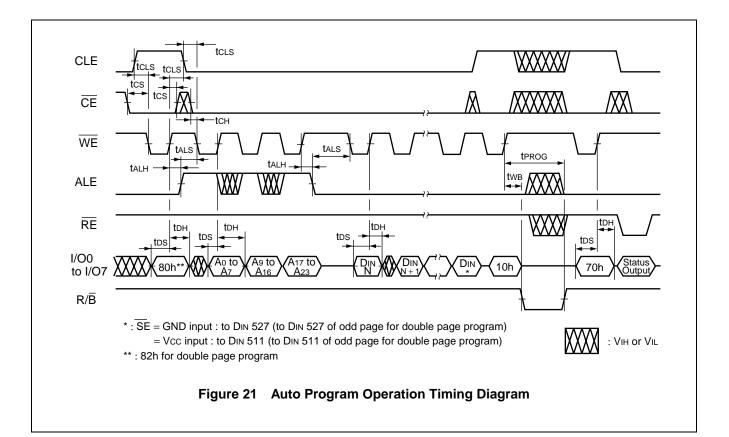

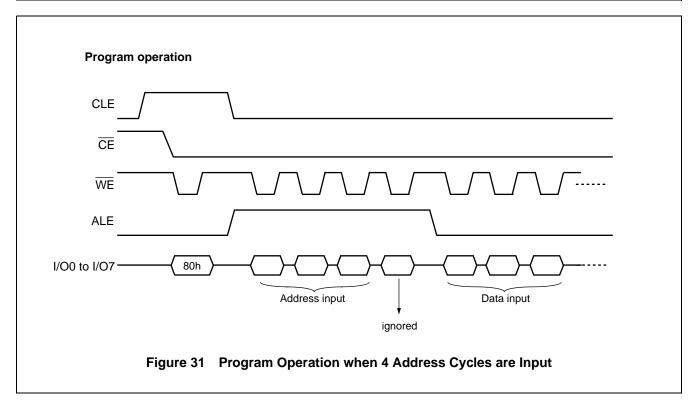

#### Page Program : 80h, 10h

The device is programmed either by the page or partial page. Programming is done by issuing the 80h command followed by three address cycles then serial data input. The 80h command may be preceded by either 00h, 01h or 50h to set the pointer to either the first half page, second half page, or spare area respectively. If the pointer command is not specifically issued, its location is determined by its previous use (see Application Note (2)). After the serial data input, any column address which did not receive new data will not be programmed. This enables a page to be partially programmed. After the data has been entered, the 10h command will initiate the embedded programming process. If the 10h command is issued without loading any new data, programming will not be initiated. A given page may not be partially programmed more than five consecutive times without an intervening erase operation. During the programming cycle, the R/B pin or Status Register bit I/O6 may be used to monitor the completion of the programming cycle. Only the Reset and Read Status commands are valid while programming is in progress. After programming, the Status Register bit I/O0 should be checked to verify whether the procedure was successful or not.

#### Double Page Progam : 82h, 10h

The device has a double page program function to program two consecutive pages of data in 2 Flash pages. The page must firstly be in the order of even page data (528 Bytes) followed by "odd page data" secondly (528 Bytes) .The 82h command may be preceded by 00h, 01h or 50h to set the pointer to the first half of even page, or to the second half of even page or to the spare area of even page respectively. If the pointer command is not specifically issued, its location is determined by its previous use. Other use or operations are the same as Page Program operations which use 80h command. (Partial Program, to input 10h command, R/B, Status register.)

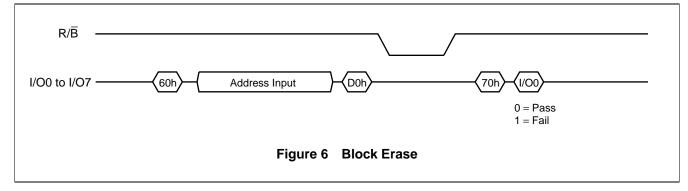

#### Block Erase : 60h, D0h

The device data is erased in a block consisting of sixteen pages. The erase operation begins with the 60h command followed by two address cycles in which the block to be erased is entered. While the two address cycles require  $A_{23}$  to  $A_9$  to be entered,  $A_{13}$  to  $A_9$  are "don't care" bits. Once the block address is successfully loaded, the D0h command is entered to initiate the erase operation. The R/B signal may be used to monitor the completion of the cycle. Upon completion, the Status Register bit I/O0 should be used to verify a successful erase.

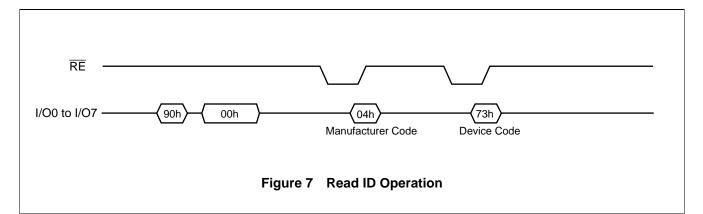

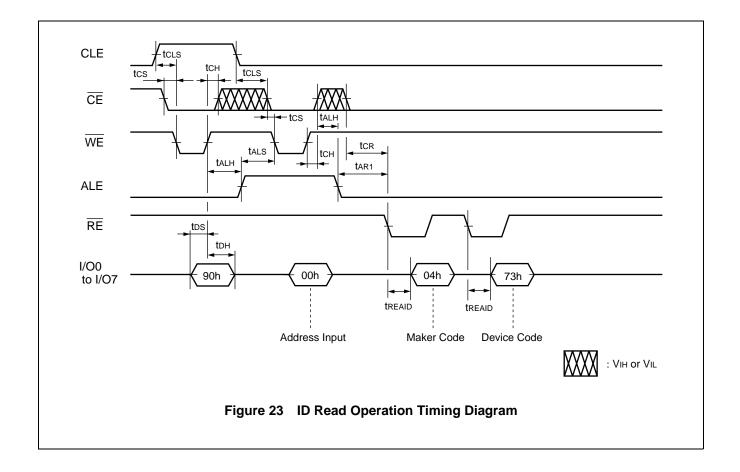

#### Read ID : 90h

This mode allows the identification of the manufacturer and product. After the 90h command cycle, one address cycle follows in which 00h is entered. The next two  $\overline{RE}$  pulses will output the manufacturer and device codes respectively.

| Table | 5 | Code | Table |

|-------|---|------|-------|

| TUDIC | • | oouc | TUDIC |

|              | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 | Code |

|--------------|------|------|------|------|------|------|------|------|------|

| Manufacturer | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 04h  |

| Device       | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 73h  |

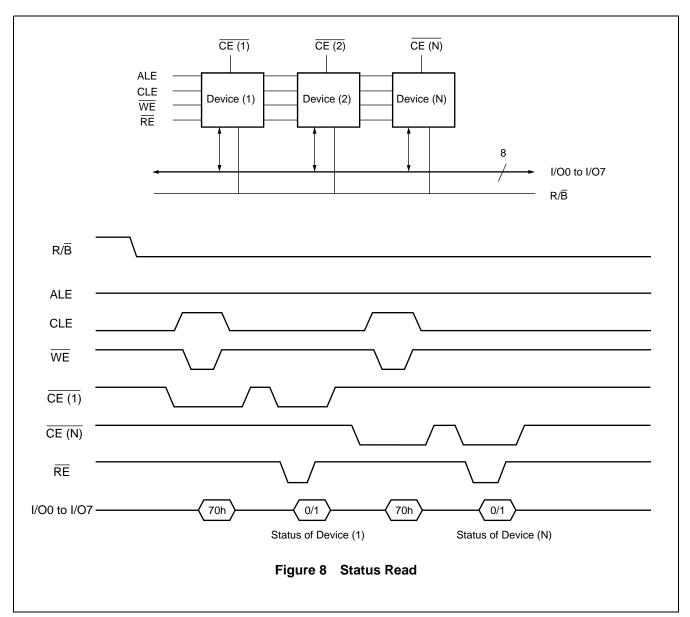

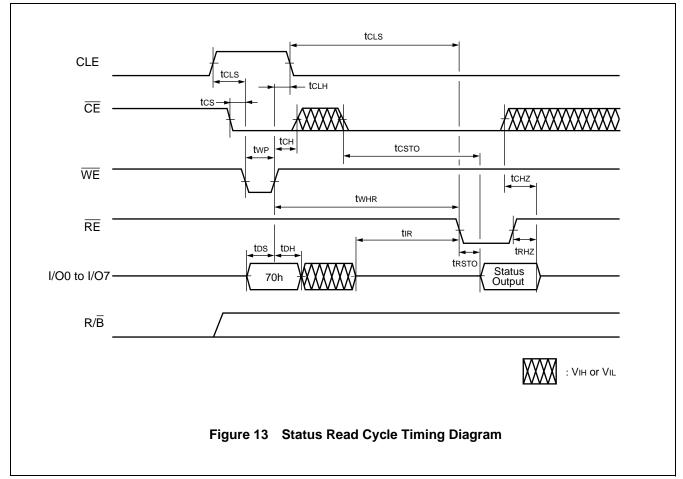

#### Status Read : 70h

The Status Register may be used to determine if the device is ready, in the write protect mode, or passed program/erase operations. After the 70h command is entered, the more recent falling edge of either  $\overline{CE}$  or  $\overline{RE}$  will output the contents of the status register to I/O0 to 7. The status register is continually updated and does not require either  $\overline{CE}$  or  $\overline{RE}$  to be toggled. By utilizing the  $\overline{CE}$  pin, multiple devices with R/B pins wired together may be polled to determine their specific status.

|      | Status        | Description                    |

|------|---------------|--------------------------------|

| I/O0 | Program/Erase | 0 = Pass; 1 = Fail             |

| I/O1 | Not Used      |                                |

| I/O2 | Not Used      |                                |

| I/O3 | Not Used      |                                |

| I/O4 | Not Used      |                                |

| I/O5 | Not Used      |                                |

| I/O6 | Ready/Busy    | 0 = Busy; 1 = Ready            |

| I/O7 | Write Protect | 0 = Protected; 1 = Unprotected |

| Table 6 | Status | Output | Table |

|---------|--------|--------|-------|

|         | Otatus | Output | Table |

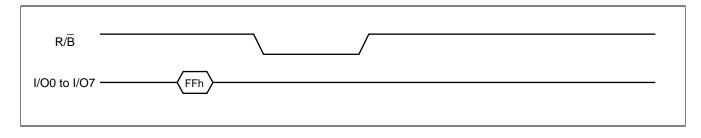

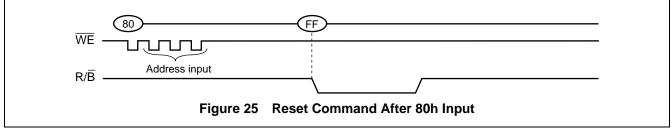

#### Reset

When the device is busy during program, erase, or read, it can be reset by entering the command FFh. If  $\overline{WP}$  equals 1, the Status Register will be set to C0h. If a reset command is issued while the device is in the reset state, the command will be ignored. If the device is reset during the program or erase operations, the internal high voltages will be discharged before R/B goes high.

### ABSOLUTE MAXIMUM RATINGS

| Parameter                                                 | Symbol | Rat  | Unit       |      |

|-----------------------------------------------------------|--------|------|------------|------|

| Falanielei                                                | Symbol | Min. | Max.       | Unit |

| Ambient Temperature with Power Applied                    | Та     | -40  | +85        | °C   |

| Storage Temperature                                       | Tstg   | -55  | +125       | °C   |

| Voltage on an I/O pin with Respect to Ground (Note)       | Vı/o   | -0.6 | Vccq + 0.5 | V    |

| Voltage on a pin Except I/O with Respect to Ground (Note) | VIN    | -0.6 | Vcc + 0.5  | V    |

| Power Supply Voltage                                      | Vcc    | -0.6 | +5.5       | V    |

| Power Supply Voltage                                      | Vccq   | -0.6 | +6.0       | v    |

Note: Minimum DC voltage on input or I/O pins are -0.5 V. During voltage transitons, inputs may undershoot Vss to -2.0 V for periods of up to 20 ns.

Maximum DC voltage on input pins are  $V_{CC}$  + 0.5 V and on I/O pins are  $V_{CC}q$  + 0.5 V. During voltage transitions, input pins may overshoot to  $V_{CC}$  + 2.0 V for periods of up to 20 ns and I/O pins may overshoot to  $V_{CC}q$  + 2.0 V for periods of up to 20 ns.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter           | Symbol      | Va        | Unit |      |

|---------------------|-------------|-----------|------|------|

|                     | Symbol      | Min.      | Max. | Unit |

| Supply Voltages     | Vcc         | +2.7 +3.6 |      | V    |

| Supply Voltages     | Vccq (Note) | +2.7      | +5.5 | V    |

| Voltages            | Vss         | 0         |      | V    |

| Ambient Temperature | Та          | -40       | +85  | °C   |

Note :  $V{\rm cc}q = 5.0~V \pm 10\%$  can be guaranteed on  $V{\rm cc} \geq 3.0~V$

Operating ranges define those limits between which the functionality of the device is guaranteed.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## ■ ELECTRICAL CHARACTERISTICS

### 1. DC Characteristics

| Parameter                     | Symbol | Conditions                                                                                                 |      | Value |            | Unit |

|-------------------------------|--------|------------------------------------------------------------------------------------------------------------|------|-------|------------|------|

| Farameter                     | Symbol | Conditions                                                                                                 | Min. | Тур.  | Max.       | Unit |

| Sequential Read Current       | Icc1   | $t_{CYCLE} = 50 \text{ ns}, \overline{CE} = V_{IL},$<br>lout = 0 mA                                        |      | 10    | 20         | mA   |

| Command Address Input Current | Іссз   | $t_{CYCLE} = 50 \text{ ns}, \ \overline{CE} = V_{IL}$                                                      |      | 10    | 20         | mA   |

| Data Input Current            | Icc4   | —                                                                                                          |      | 10    | 20         | mA   |

| Program Current               | Icc6   | —                                                                                                          |      | 10    | 20         | mA   |

| Erase Current                 | Icc7   | —                                                                                                          |      | 10    | 20         | mA   |

| Stand-by Current (TTL)        | Isb1   | $\frac{\overline{CE} = V_{IH}}{\overline{WP} = \overline{SE} = 0 \text{ V/V}_{CC}}$                        |      |       | 1          | mA   |

| Stand-by Current (CMOS)       | ISB2   | $\frac{\overline{CE}}{\overline{WP}} = \frac{V_{CC} - 0.2 \text{ V}}{\overline{SE}} = 0 \text{ V/ V_{CC}}$ |      | 10    | 50         | μA   |

| Input Leakage Current         | L      | V <sub>IN</sub> = 0 to 3.6 V                                                                               |      |       | ±10        | μA   |

| Output Leakage Current        | LO     | Vout = 0 to 3.6 V                                                                                          |      |       | ±10        | μA   |

|                               | ViH    | I/O pins                                                                                                   | 2.0  |       | Vccq + 0.3 | V    |

| Input High Voltage            | VIH    | Except I/O pins                                                                                            | 2.0  | _     | Vcc + 0.3  | V    |

| Input Low Voltage             | VIL    | —                                                                                                          | -0.3 | _     | 0.8        | V    |

| Output High Voltage Level     | Vон    | Іон = -400 μА                                                                                              | 2.4  |       |            | V    |

| Output Low Voltage Level      | Vol    | IoL = 2.1 mA                                                                                               |      |       | 0.4        | V    |

| Output Low Current (R/B)      | lol    | Vol = 0.4 V                                                                                                | 8    | 10    |            | mA   |

### 2. AC Characteristics (Note 1)

| Devemation                                                      | Cumb al          | Value |      |      |

|-----------------------------------------------------------------|------------------|-------|------|------|

| Parameter                                                       | Symbol           | Min.  | Max. | Unit |

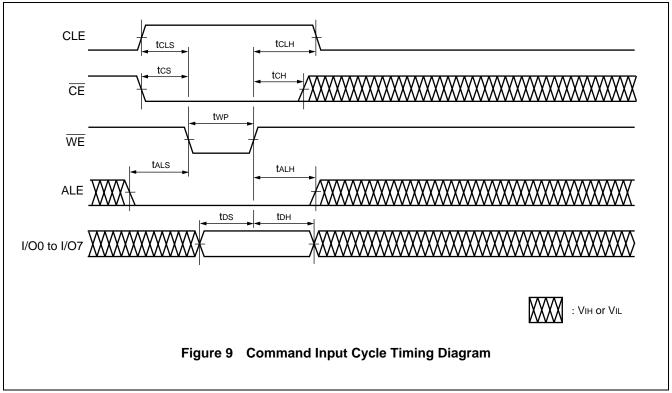

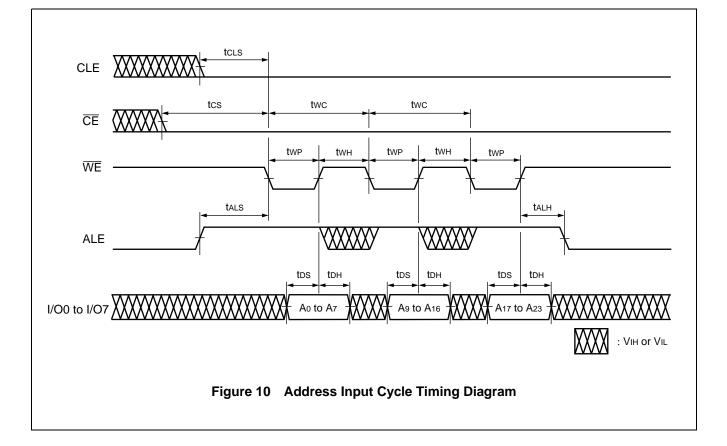

| CLE Setup Time                                                  | tcls             | 0     |      | ns   |

| CLE Hold Time                                                   | tсьн             | 10    | —    | ns   |

| CE Setup Time                                                   | tcs              | 0     |      | ns   |

| CE Hold Time                                                    | tсн              | 10    | —    | ns   |

| Write Pulse Width                                               | twp              | 25    |      | ns   |

| ALE Setup Time                                                  | <b>t</b> ALS     | 0     |      | ns   |

| ALE Hold Time                                                   | <b>t</b> alh     | 10    |      | ns   |

| Data Setup Time                                                 | tos              | 20    |      | ns   |

| Data Hold Time                                                  | tон              | 10    |      | ns   |

| Write Cycle Time                                                | twc              | 50    |      | ns   |

| WE High Hold Time                                               | twн              | 15    |      | ns   |

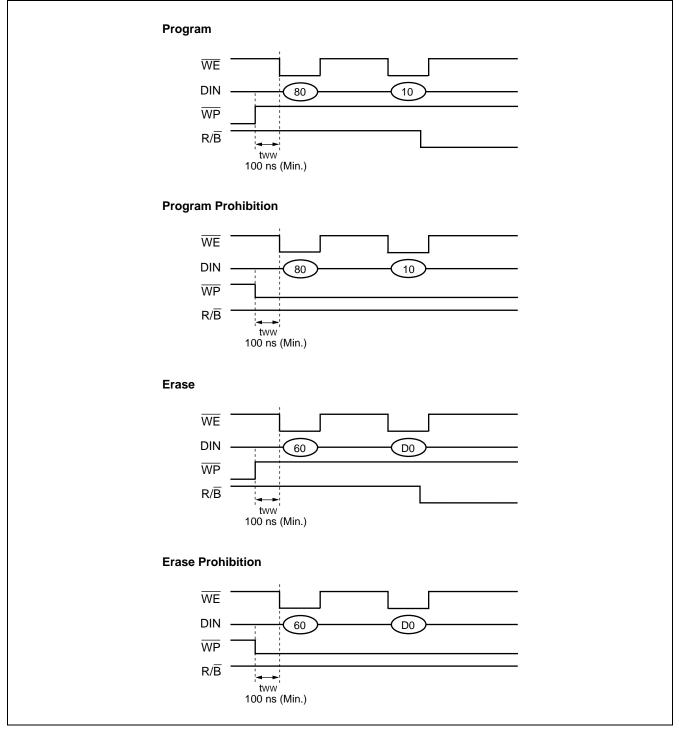

| WP High to WE Low                                               | tww              | 100   |      | ns   |

| Ready to RE Falling Edge                                        | <b>t</b> rr      | 20    |      | ns   |

| Read Pulse Width                                                | <b>t</b> RP      | 30    |      | ns   |

| Read Cycle Time                                                 | <b>t</b> RC      | 50    | —    | ns   |

| RE Access Time (Serial Data Access)                             | <b>t</b> rea     | —     | 35   | ns   |

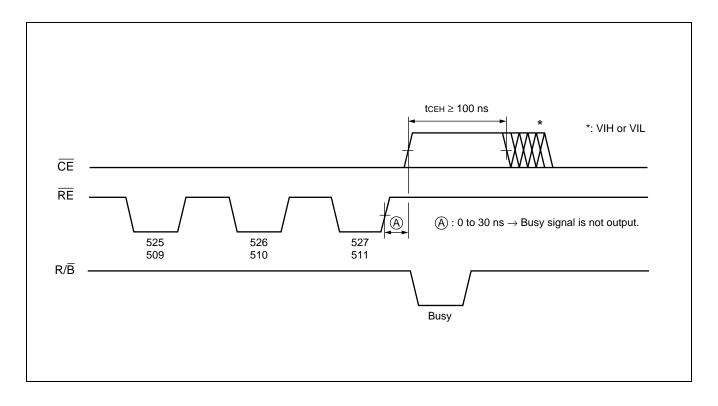

| CE High Time for the Last Address in Serial Read Cycle (Note 3) | tсен             | 100   | —    | ns   |

| RE Access Time (ID Read)                                        | <b>t</b> REAID   |       | 35   | ns   |

| RE High to Output High Impedance                                | <b>t</b> RHZ     | 15    | 30   | ns   |

| CE High to Output High Impedance                                | tснz             | —     | 20   | ns   |

| RE High Hold Time                                               | <b>t</b> REH     | 15    | —    | ns   |

| Output High Impedance to RE Falling Edge                        | tır              | 0     |      | ns   |

| RE Access Time (Status Read)                                    | <b>t</b> RSTO    | —     | 35   | ns   |

| CE Access Time (Status Read)                                    | <b>t</b> csto    |       | 45   | ns   |

| WE High to RE Low                                               | <b>t</b> whr     | 60    |      | ns   |

| ALE Low to RE Low (ID Read)                                     | t <sub>AR1</sub> | 100   |      | ns   |

| CE Low to RE Low (ID Read)                                      | <b>t</b> cr      | 100   |      | ns   |

| Data Transfer from Memory Cell Array to Register                | <b>t</b> R       |       | 7    | μs   |

| WE High to Busy                                                 | twв              |       | 100  | ns   |

| ALE Low to RE Low (Read Cycle)                                  | tar2             | 50    |      | ns   |

(Continued)

| Parameter                                                                                        | Symbol | Va   | Unit                       |      |

|--------------------------------------------------------------------------------------------------|--------|------|----------------------------|------|

| Farameter                                                                                        | Symbol | Min. | Max.                       | Onit |

| RE Last Clock Rising Edge to Busy (in Sequential Read)                                           | trв    |      | 100                        | ns   |

| $\overline{CE}$ High to Ready (in Case of Interception by $\overline{CE}$ in Read Mode) (Note 2) | tcry   |      | $50 + tr (R/\overline{B})$ | ns   |

| Device Resetting Time (Read/Program/Erase)                                                       | trst   |      | 5/10/500                   | μs   |

Notes : 1. AC Test Conditions :

| Operating range                   | Vcc = 2.7  to  3.6  V | Vcc = 3.0 to 3.6 V |  |  |  |

|-----------------------------------|-----------------------|--------------------|--|--|--|

| Input level                       | 2.4 V                 | //0.4 V            |  |  |  |

| Input comparison level            | 1.5 V/1.5 V           |                    |  |  |  |

| Output data comparison level      | 1.5 V/1.5 V           |                    |  |  |  |

| Output load                       | 1TTL                  |                    |  |  |  |

| Load capacitance (CL)             | 50 pF 100 pF          |                    |  |  |  |

| Transition time (t <sub>T</sub> ) | 5 ns                  |                    |  |  |  |

The time to go from CE high to Ready depends on the pull-up resister of the R/B pin (see Application Notes (6)) toward the end of this document.

3. If you toggle  $\overline{CE}$  to high after access to the last address (address 527) in the resister in the read mode (1), (2), and (3), the  $\overline{CE}$  high time must be held for 100 ns or more when the delay time of  $\overline{CE}$  with respect to  $\overline{RE}$  is 0 to 200 ns (see the figure below). When the  $\overline{CE}$  delay time is within 30 ns, the device is kept in the Ready state and will output no Busy signal.

### ERASE AND PROGRAMMING PERFORMANCE

| Parameter                                 | Symbol          | Value               |      |      | Unit | Note |

|-------------------------------------------|-----------------|---------------------|------|------|------|------|

| Falameter                                 | Symbol          | Min.                | Тур. | Max. | Unit | NOLE |

| Average Programming Time                  | <b>t</b> prog   | —                   | 200  | 1000 | μs   |      |

| Number of Programming Cycles on Same Page | N               |                     | _    | 5    |      | 1    |

| Block Erasing Time                        | <b>t</b> berase | —                   | 2    | 10   | ms   |      |

| Number of Program/Erase Cycles            | P/E             | 1 × 10 <sup>6</sup> |      |      |      | 2    |

Notes: 1. Refer to Application Note (10) toward the end of this document.

2. This specification is on conditions that ECC systems would be combined. Refer to Application Note (13) toward the end of this document.

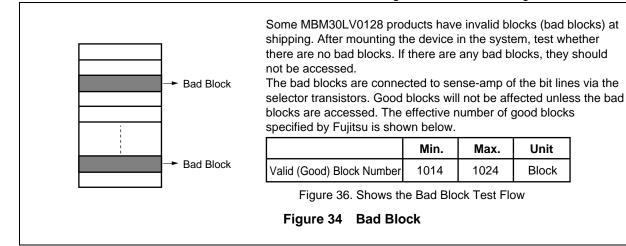

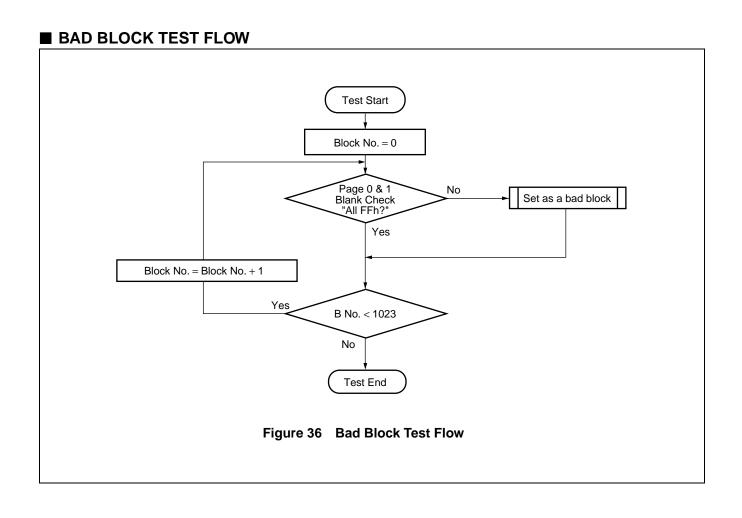

### ■ VALID BLOCKS

The MBM30LV0128 occasionally contains unusable blocks. Refer to Application Note (12) toward the end of this document.

| Parameter          | Symbol | Value |      |      | Unit  |

|--------------------|--------|-------|------|------|-------|

|                    | Symbol | Min.  | Тур. | Max. | Offic |

| Valid Block Number | Nvв    | 1014  | 1020 | 1024 | Block |

### ■ PIN CAPACITANCE

| Parameter Sy       | Symbol Condition |              | Value |      | Unit |

|--------------------|------------------|--------------|-------|------|------|

|                    | Symbol           | Condition    | Тур.  | Max. | Onic |

| Input Capacitance  | CIN              | $V_{IN} = 0$ |       | 10   | pF   |

| Output Capacitance | Соит             | Vout = 0     |       | 10   | pF   |

Notes : 1. Test conditions Ta = 25 °C, f = 1.0 MHz 2. Sampled, not 100% tested.

### TIMING DIAGRAMS

Figure 18 Sequential Read (1) Timing Diagram

### APPLICATION NOTES AND COMMENTS

### (1) Prohibition of unspecified commands

The operation commands are listed in Table 4. Data input as a command in other than the specified commands in Table 4 are prohibited. Stored data may be corrupted if an unspecified command is entered during the command cycle.

### (2) Pointer Action for Program Operation

The pointer action can be done for program operation as follows.

### (3) Acceptable commands after serial input command "80h"

When the serial input command (80h) is input for program execution, commands other than the program execution command (10h) or reset command (FFh) should not be input.

If a command other than "10h" or "FFh" is input, the program operation is not performed.

In case of this operation, the FFh command is needed.

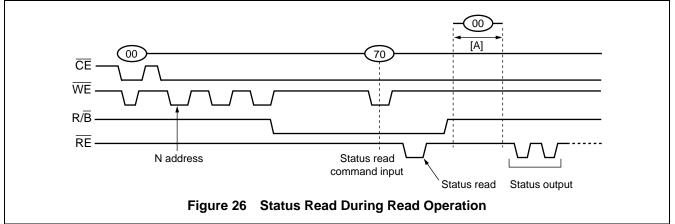

### (4) Status read during the read operation

When the status read command (70h) is input during reading, the next  $\overline{RE}$  clock signal can be input to read the value of the internal status register.

Since the internal operation mode is held in Status Read, read data will not be output even if the  $\overline{RE}$  clock signal is input after becoming ready. Status Read is therefore disabled at reading.

When the read command (00h) is input during the period [A], the internal operation mode of the device can be canceled, making it possible to read data at address N without inputting Add.

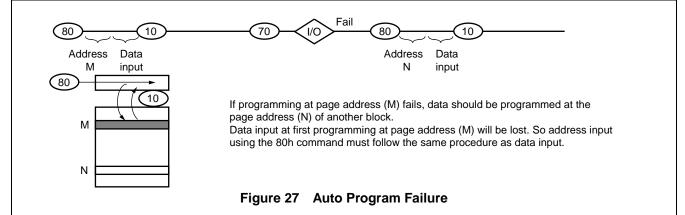

### (5) Auto program failure

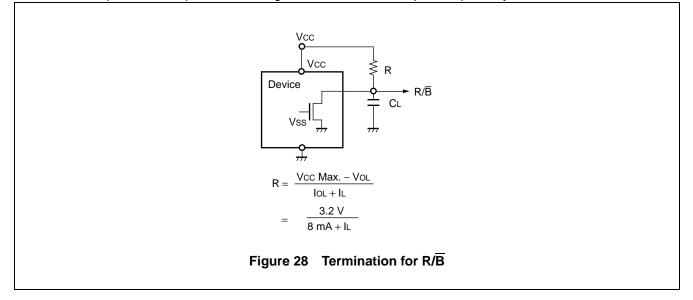

### (6) $R/\overline{B}$ : Termination of the Ready/Busy pin ( $R/\overline{B}$ )

The R/ $\overline{B}$  is open-drain output. When using the R/ $\overline{B}$ , R/ $\overline{B}$  must be pulled up V<sub>CC</sub> by a resistor.

### (7) Power On/Off Sequence :

After power-off, each input signal level may be undefined. Use the  $\overline{WP}$  signal as shown in the figure below.

### (8) Setup for $\overline{WP}$ Signal

A Low-level  $\overline{WP}$  signal will force erasing and programming to be reset. To control, use the  $\overline{WP}$  signal as shown below.

#### (9) Address input in 4 cycles

The device will get addresses in three cycles. If addresses are input in four cycles, address input in the fourth cycle will be ignored by the chip.

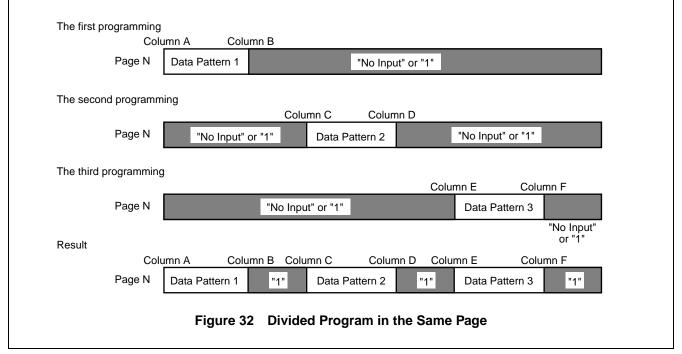

### (10) Divided programming on same page

The device uses a page programming method that allows programming for up to five times on the same page. The procedure for divided programming (programming on a part of one page) is shown below.

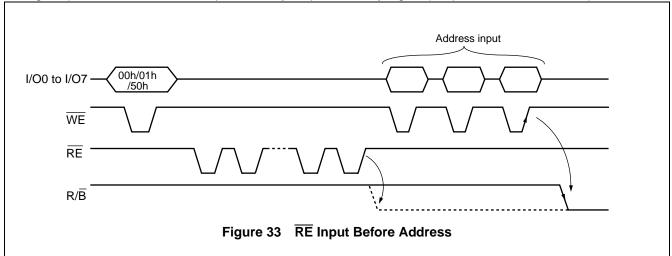

### (11) Notification for RE Signal

When the device is in the read mode, the  $\overline{RE}$  signal causes the internal column address counter to increment in synchronization with the  $\overline{RE}$  clock. If the 00h, 01h, or 50h command is input to the device in the read mode, the internal column address counter will count up even after the  $\overline{RE}$  signal is input prior to address input. At this mode, And at input of the  $\overline{RE}$  signal beyond the last column address, the device will start reading (Memory  $\rightarrow$ register) even without address input and may output the Busy signal (Sequential Read is started).

In this way, once the device enters the read mode, unintentional reading may be started after the  $\overline{RE}$  signal is input prior to addressing; therefore, the  $\overline{RE}$  signal should be input after the address input.

### (12) Invalid block (bad block)

The device contains unusable blocks. Therefore, the following issues must be recognized :

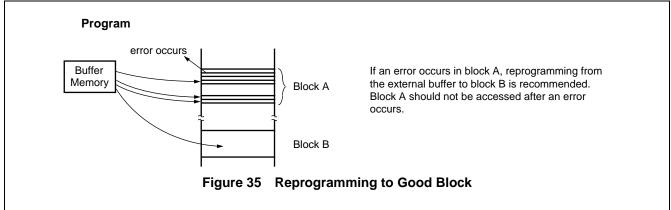

#### (13) Failure Phenomena for Program and Erase Operations

Repeated rewriting might cause an error at programming and erasing. Possible error modes, detection methods and remedies are listed in the following table. System-based remedies will provide a highly reliable system.

| Failure Mode |                 | Detection and Countermeasure Sequence                   |

|--------------|-----------------|---------------------------------------------------------|

| Block        | Erase Failure   | Status Read after Erase $\rightarrow$ Block Replacement |

| Page         | Program Failure | Status Read after Prog. $\rightarrow$ Block Replacement |

| Single Bit*  | Program Failure | (1) Block Verify after Prog. $\rightarrow$ Retry        |

|              | "1" → "0"       | (2) ECC                                                 |

\*: (1) or (2)

• ECC

: Error Correcting code  $\rightarrow$  Hamming Code etc.

- Example : 1 bit correction & 2 bit detection.

- Block Replacement

#### Erase

If an error occurs at erasing, like programming, remedies should be executed on a system basis to prevent access to blocks causing the error.

### (14) CE "don't care" timing for read and program operation

CE can be "don't-care" ("H" or "L") state during read and program operation as follows.

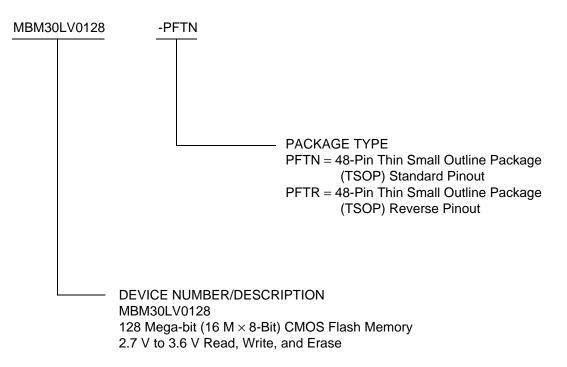

### ORDERING INFORMATION

### **Standard Products**

Fujitsu standard products are available in several packages. The order number is formed by a combination of :

| Valid Co    | ombinations    |  |

|-------------|----------------|--|

| MBM30LV0128 | -PFTN<br>-PFTR |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local Fujitsu sales office to confirm availability of specific valid combinations and to check on newly released combinations.

(Continued)

# FUJITSU LIMITED

For further information please contact:

#### Japan

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0721, Japan Tel: +81-3-5322-3347 Fax: +81-3-5322-3386

http://edevice.fujitsu.com/

#### North and South America

FUJITSU MICROELECTRONICS, INC. 3545 North First Street, San Jose, CA 95134-1804, U.S.A. Tel: +1-408-922-9000 Fax: +1-408-922-9179

Customer Response Center *Mon. - Fri.: 7 am - 5 pm (PST)* Tel: +1-800-866-8608 Fax: +1-408-922-9179

http://www.fujitsumicro.com/

#### Europe

FUJITSU MICROELECTRONICS EUROPE GmbH Am Siebenstein 6-10, D-63303 Dreieich-Buchschlag, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122

http://www.fujitsu-fme.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LTD. #05-08, 151 Lorong Chuan, New Tech Park, Singapore 556741 Tel: +65-281-0770 Fax: +65-281-0220

http://www.fmap.com.sg/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 1702 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu,Seoul 135-280 Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

F0101 © FUJITSU LIMITED Printed in Japan All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipments, industrial, communications, and measurement equipments, personal or household devices, etc.). CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.